DSP与AIC23B通信系统设计

基于TLV320AIC23的语音系统设计

摘要本设计采用的高速TMS320C5509DSP芯片,最高频率能达到160MIPS,能够很好的解决系统的实时性;采用的数字编解码芯片TLV320AIC23(以下简称AIC23)具有16~32位采样精度,采样频率范围从8kHz~96kHz。

因此,该音频编解码芯片与TMS320C5509DSP的结合是可移动数字音频录放系统、现场语音分析系统的理想解决方案。

本文首先介绍了基于TMS320C5509DSP芯片的语音分析系统的工作原理,给出了整体设计方案和工作框图,然后给出了系统的硬件设计方案;接着介绍了基于TMS320C5509DSP芯片的语音录放系统的软件设计。

在整个设计过程中,我们采用了TLV320AIC23DSP芯片为核心音频录放接口器件,结合TMS320C5509DSP芯片,语音数据存储FLASH存储器等进行了硬件设计。

软件部分则采用模块化的设计方法,用C语言来实现。

该语音录放器的设计能够完成语音采集,存储,滤波,频谱分析,基本实现了语音分析功能。

关键词:TMS320C5509芯片;TLV320AIC23音频编解码芯片;I2C总线;语音系统目录1 TLV320AIC23语音系统的设计任务及目的 (1)1.1 TLV320AIC23语音系统的设计任务 (1)1.2 TLV320AIC23语音系统的设计目的 (1)1.3 TLV320AIC23语音系统介绍 (1)2 语音系统的技术方案及硬件电路设计 (2)2.1 语音系统的性能指标 (2)2.1.1本设计实现的语音系统具有如下主要性能 (2)2.1.2语音系统具有如下优点 (2)2.2硬件设计方案 (2)2.2.1系统硬件电路设计 (3)2.2.2 C5509与音频编解码器的接口设计 (3)2.2.3 系统的存储器扩展 (5)2.2.4 C5509的电源与时钟电路设计 (5)3 芯片的硬件结构 (6)3.1 TLV320AIC23的硬件结构..................................................... .. (6)3.1 .1 AIC23的管脚及外围接口 (7)3.1.2 AIC23的控制接口 (8)3.2 TMS320C5509的硬件结构 (8)4 TLV320AIC23语音系统设计的CCS实现 (11)4.1.简述CCS环境................................................................................ (11)4.2 CCS配置......................................................... . (12)4.3 程序调试及运行结果 (14)5 结论............................................ (15)参考文献 (16)致谢 (17)附录A (18)附录B (25)基于TLV320AIC23的语音系统设计1 TLV320AIC23语音系统的设计任务及目的1.1 TLV320AIC23语音系统的设计任务课程设计是实践教学环节。

基于DSP的语音处理系统的设计【范本模板】

Cadence SPB基于DSP的语音处理系统的设计摘要近年来,随着DSP技术的普及和低价格、高性能DSP芯片的出现,DSP已越来越多地被广大的工程师所接受越来越广泛地被应用于各个领域,并且已日益显示出其巨大的优越性.DSP是利用专门或通用的数字信号处理芯片,以数字计算的方法对信号进行处理,具有处理速度快、灵活、精确、抗干扰能力强、体积小及可靠性高等优点,满足了对信号快速、精确、实时处理及控制的要求.本次设计基于TLV320AIC23和TMS320VC5416两种芯片设计并实现了一种语音录音、语音编码、语音解码、语音处理和回放的系统。

通过软件和硬件结合对该系统进行设计,使本次设计的语音处理系统具有强大的数据处理能力并配有灵活的接口电路,可以作为一种语音信号处理算法研究和实时实现的通用平台,对语音编码在DSP上的实时实现进行了简单的研究,从而掌握了算法移植的一般流程,为能够在高速DSP硬件平台设计及系统应用开发方面取得成功奠定基础.关键词:DSP;数据采集;TLV320AIC23;TMS320VC5416。

目录摘要I 第1章绪论 1 1.1 DSP的发展及应用 1 1。

2 语音信号处理系统概述 2 第2章DSP 芯片介绍3 2。

1 TLV320AIC23简介 3 2。

2 TMS320VC5416简介 3 第3章系统设计4 3。

1系统硬件设计 4 3.1.1系统结构框图 4 3。

1.2 DSP处理器 5 3.1.3 A/D电路5 3。

1.4 D/A电路7 3。

2系统软件设计10 3.2.1 TMS320VC5416初始化10 3。

2.2 TLV320AIC23初始化10 第4章总结11 参考文献12 致谢13附录14 第1章绪论近年来,在数字信号处理领域有着绝对优势的DSP技术得到了迅速发展,不仅在通信计算机领域大显身手,并已逐渐渗透到人们日常消费领域。

正因为如此,DSP应用越来越得到普遍重视。

DSP作为可编程数字信号处理专用芯片是微型计算机发展的一个重要分支,也是数字信号处理理论实用化过程的重要技术工具。

基于AIC23语音接口及AGC方法的设计

语音接口包括采集和播放两项功能,是语音处理系统中最基本、最关键的部分。

语音采集时,输入信号幅度动荡会影响后续处理;语音播放时,输出信号幅度不稳定会恶化收听效果。

所以,语音AGC(自动增益控制)是语音接口中不可或缺的功能单元。

TLV320AIC23(简称AIC23)是TI公司生产的集成了A/D,D/A转换器和可变增益放大器的高性能语音编解码芯片,是设计语音接口的理想选择。

文中介绍了AIC23的特点和结构,在此基础上给出语音接口及AGC的实现方法。

1AIC23介绍1.1主要特点(1)集成线输入可变增益放大器(VGA),增益范围-34.5~12dB,步进1.5dB;(2)集成线输出可变增益放大器(VGA),增益范围-73~6dB,步进1dB;(3)I/O电压、数据接口与TI公司的54系列DSP兼容。

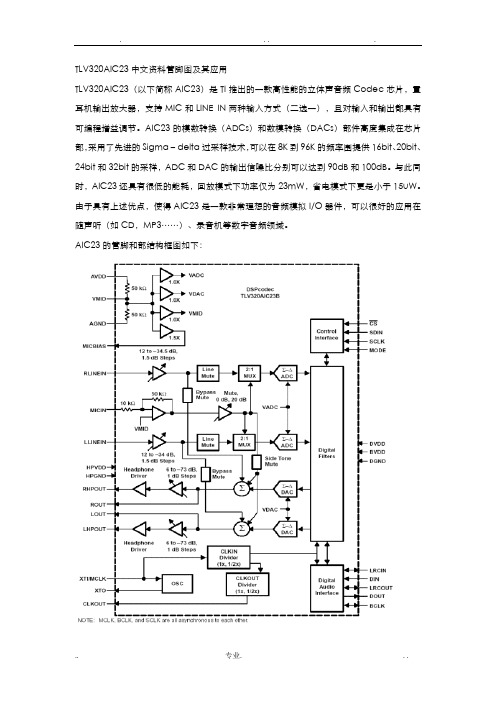

1.2基本结构和主要接口AIC23的基本结构和主要接口,如图1所示。

模拟语音信号从左、右声道线输入管脚或麦克信号输入管脚输入,分别经VGA、静音控制、多路选择器、A/D转换器、数字插值滤波器,得到特定采样率的数字语音信号;数字语音信号依次经过数字滤波器、D/A转换器、静音控制和VGA,最后从左、右声道线输出管脚输出;AIC23的工作状态由系统微处理器通过控制接口设置,控制接口模式为SPI/I2C可选(mode管脚置高为SPI模式,置低为I2C 模式);AIC23与微处理器通过数据接口进行数据交换,数据接口为左判断/右判断/I2C/DSP模式可选(由微处理器通过控制接口设置)。

TI公司生产的54系列DSP集成了多通道缓冲串口(McBSP),可与SPI模式的控制接口和DSP模式的数据接口无缝连接。

1.3控制方法AIC23是一款可编程芯片,内部有11个9位寄存器,可由微处理器通过控制接口进行配置,从而设定芯片的工作模式和状态。

主要寄存器内容,如表1所示。

2语音接口设计2.1硬件设计语音接口由TI公司的数字信号处理器TMS320VC5416与AIC23构成,如图2所示。

音频处理芯片AIC23完整中文资料

⾳频处理芯⽚AIC23完整中⽂资料TLV320AIC23中⽂资料管脚图及其应⽤TLV320AIC23(以下简称AIC23)是TI推出的⼀款⾼性能的⽴体声⾳频Codec芯⽚,内置⽿机输出放⼤器,⽀持MIC和LINE IN两种输⼊⽅式(⼆选⼀),且对输⼊和输出都具有可编程增益调节。

AIC23的模数转换(ADCs)和数模转换(DACs)部件⾼度集成在芯⽚内部,采⽤了先进的Sigma-delta过采样技术,可以在8K到96K的频率范围内提供16bit、20bit、24bit和32bit的采样,ADC和DAC的输出信噪⽐分别可以达到90dB 和100dB。

与此同时,AIC23还具有很低的能耗,回放模式下功率仅为23mW,省电模式下更是⼩于15uW。

由于具有上述优点,使得AIC23是⼀款⾮常理想的⾳频模拟I/O器件,可以很好的应⽤在随声听(如CD,MP3……)、录⾳机等数字⾳频领域。

AIC23的管脚和内部结构框图如下:从上图可以看出,AIC23主要的外围接⼝分为以下⼏个部分:⼀.数字⾳频接⼝:主要管脚为BCLK-数字⾳频接⼝时钟信号(bit时钟),当AIC23为从模式时(通常情况),该时钟由DSP产⽣;AIC23为主模式时,该时钟由AIC23产⽣;LRCIN-数字⾳频接⼝DAC⽅向的帧信号(I2S模式下word时钟)LRCOUT-数字⾳频接⼝ADC⽅向的帧信号DIN-数字⾳频接⼝DAC⽅向的数据输⼊DOUT-数字⾳频接⼝ADC⽅向的数据输出这部分可以和DSP的McBSP(Multi-channel buffered serial port,多通道缓存串⼝)⽆缝连接,唯⼀要注意的地⽅是McBSP 的接收时钟和AIC23的BCLK都由McBSP的发送时钟提供,连接⽰意图如下:⼆.麦克风输⼊接⼝:主要管脚为MICBIAS-提供麦克风偏压,通常是3/4 AVDDMICIN-麦克风输⼊,由AIC结构框图可以看出放⼤器默认是5倍增益连接⽰意图如下:三.LINE IN输⼊接⼝:主要管脚为LLINEIN-左声道LINE IN输⼊RLINEIN-右声道LINE IN输⼊连接⽰意图如下:四.⽿机输出接⼝:主要管脚为LHPOUT-左声道⽿机放⼤输出RHPOUT-右声道⽿机放⼤输出LOUT-左声道输出ROUT-右声道输出从框图可以看出,LOUT和ROUT没有经过内部放⼤器,所以设计中常⽤LHPOUT和RHPOUT,连接⽰意图如下:五.配置接⼝:主要管脚为SDIN-配置数据输⼊SCLK-配置时钟DSP通过该部分配置AIC23的内部寄存器,每个word的前7bit为寄存器地址,后9bit 为寄存器内容。

DSP与AIC23B通信系统设计

参考文献 [1] 曹与军.基于 DSP 的数字锁相技术.电源技术应用,2005,8: 13 ̄15. [2] 刘东华. 基于 T MS320VC 5402 McBSP 串口的 DMA 方式数据传 输的实现.力源电子工程,2001,5(3): 32 ̄35. [3] T exas Instruments.T MS320C 6000 McBSP Initialization,2002: 4 ̄8. [4] 谢 铿.基 于 DSP 的 数 字 音 频 系 统.广 东 工 业 大 学 硕 士 论 文,2002,4: 21 ̄27.

( 1) 将 SPCR 寄 存 器 中 的 XRST 和 RRST 置 为 1, 收 发 端 口复位;

( 2) 在 McBSP0 保持复位的状态下, 设置有关的寄存器为 需要的值, 先设置 CLKSTP=0xb, 禁止时钟停止模式;

基于定点DSP及AIC23的混沌信号源设计

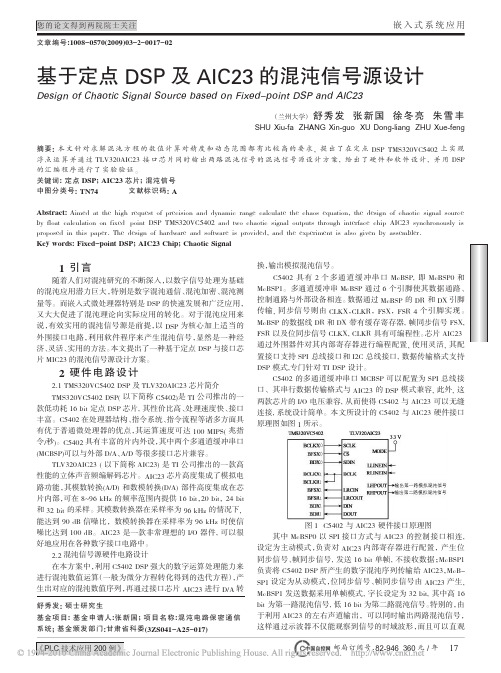

C5402 的多通道缓冲串口 MCBSP 可以配置为 SPI 总线接

口、其串行数据传输格式与 AIC23 的 DSP 模式兼容, 此外, 这

两款芯片的 I/O 电压兼容, 从而使得 C5402 与 AIC23 可以无缝

连接, 系统设计简单。本文所设计的 C5402 与 AIC23 硬件接口

原理图如图 1 所示。

软件程序设计主要包括三大部分:混沌信号产生程序,

DXR0,经过一定延时,McBSP0 通过查询方式即可完成对 A- IC23 的配置。

4 实验验证

以洛仑兹混沌为例,迭代方程为:

C5402 多通道串口 McBSP0、McBSP1 接口配置,AIC23 内部寄 存器配置。

?x ? x ? h?? ? (y ? x ) ?? y ? y ? h? (? ? x ? y ? x ? z )

创

·XPHASE=0, 发送数据每次传输为单相帧; ·XFRLEN1=0000000, 发送 数 据每 帧 的 传输 长 度 为 1 个

新 Word; ·XWDLEN1=010, 发送数据每 1 个字的字长为 16 bit;

·FSGM=0, 每次 DXR[1, 2]复制到 XSR[1, 2]后产生发送帧

1 引言

随着人们对混沌研究的不断深入,以数字信号处理为基础 的混沌应用潜力巨大,特别是数字混沌通信、混沌加密、混沌测 量等。而嵌入式微处理器特别是 DSP 的快速发展和广泛应用, 又大大促进了混沌理论向实际应用的转化。对于混沌应用来 说,有效实用的混沌信号源是前提,以 DSP 为核心加上适当的 外围接口电路,利用软件程序来产生混沌信号,显然是一种经 济、灵活、实用的方法。本文提出了一种基于定点 DSP 与接口芯 片 MIC23 的混沌信号源设计方案。

基于TLV320AIC23B的语音信号采集系统设计

MODE

控制口模式选择引脚。低电平时控制口配置成两线I2C模式,高电 I 平时配置成三线SPI模式。

控制口锁存/地址选择引脚。控制口工作在SPI模式时,作为数据输

CS

I 入锁存引脚;控制口工作在I2C模式时,作为I2C器件的地址选择引

脚。

SCLK

I 控制口串行时钟引脚。

SDIN

I 控制口串行数据输入引脚。

语音信号输入引脚

麦克风偏置电压输出引脚。在选择麦克风输入时,该引脚输出的

MICBIAS O 电压作为麦克风的偏置。其电压在正常模式下为3/4 的模拟电源

电压。

MICIN

I 麦克风输入引脚。该引脚为麦克风输出的模拟语音信号输入引脚。

LLINEIN

I 立体声的左声道模拟语音信号输入引脚。

RLINEIN

I 立体声的右声道模拟语音信号输入引脚。

图3 TLV320AIC23B音频信号输出电路

3.2 数字接口电路

数字接口电路主要是完成 TLV320AIC23B 与 DSP 芯片 TMS320VC5402 之间的数字接 口,以用于两者之间的数据传输。

TLV320AIC23B与微处理器的接口有两个,一个是控制口,用于设置TLV320AIC23B的 工作参数;另一个是数据口,用于传输TLV320AIC23B的A/D、D/A 数据。这两个口都是串 行口[2]。

4 语音信号处理系统的软件设计

本语音信号处理系统的主体由TMS320VC5402 和TLV320AIC23B构成,所以软件系统的 编程也主要是围绕这两颗芯片来的。在软件程序中要完成对TMS320VC5402 的初始化,尤 其是对两个McBSP的设置,还有TLV320AIC23B中控制寄存器的设置。然后让系统在设定的 方式下工作即可[5]。

音频处理芯片AIC23完整中文资料

TLV320AIC23中文资料管脚图及其应用TLV320AIC23(以下简称AIC23)是TI推出的一款高性能的立体声音频Codec芯片,置耳机输出放大器,支持MIC和LINE IN两种输入方式(二选一),且对输入和输出都具有可编程增益调节。

AIC23的模数转换(ADCs)和数模转换(DACs)部件高度集成在芯片部,采用了先进的Sigma-delta过采样技术,可以在8K到96K的频率围提供16bit、20bit、24bit和32bit的采样,ADC和DAC的输出信噪比分别可以达到90dB和100dB。

与此同时,AIC23还具有很低的能耗,回放模式下功率仅为23mW,省电模式下更是小于15uW。

由于具有上述优点,使得AIC23是一款非常理想的音频模拟I/O器件,可以很好的应用在随声听(如CD,MP3……)、录音机等数字音频领域。

AIC23的管脚和部结构框图如下:从上图可以看出,AIC23主要的外围接口分为以下几个部分:一.数字音频接口:主要管脚为BCLK-数字音频接口时钟信号(bit时钟),当AIC23为从模式时(通常情况),该时钟由DSP产生;AIC23为主模式时,该时钟由AIC23产生;LRCIN-数字音频接口DAC方向的帧信号(I2S模式下word时钟)LRCOUT-数字音频接口ADC方向的帧信号DIN-数字音频接口DAC方向的数据输入DOUT-数字音频接口ADC方向的数据输出这部分可以和DSP的McBSP(Multi-channel buffered serial port,多通道缓存串口)无缝连接,唯一要注意的地方是McBSP的接收时钟和AIC23的BCLK都由McBSP的发送时钟提供,连接示意图如下:二.麦克风输入接口:主要管脚为MICBIAS-提供麦克风偏压,通常是3/4 AVDDMICIN-麦克风输入,由AIC结构框图可以看出放大器默认是5倍增益连接示意图如下:三.LINE IN输入接口:主要管脚为LLINEIN-左声道LINE IN输入RLINEIN-右声道LINE IN输入连接示意图如下:四.耳机输出接口:主要管脚为LHPOUT-左声道耳机放大输出RHPOUT-右声道耳机放大输出LOUT-左声道输出ROUT-右声道输出从框图可以看出,LOUT和ROUT没有经过部放大器,所以设计中常用LHPOUT和RHPOUT,连接示意图如下:五.配置接口:主要管脚为SDIN-配置数据输入SCLK-配置时钟DSP通过该部分配置AIC23的部寄存器,每个word的前7bit为寄存器地址,后9bit为寄存器容。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

下面是完成对 Mc S 0初始化 的步骤 : BP

( )将 S C 1 P R寄 存器 中 的 霜 和雨 丁置为 1 收发端 ,

P L控 制器具 有可软件配 置的倍频 器 , L 分 口复位 ;

211 P L初始化 .. L

频器和复位控 制器 。倍频器的倍频系数可从 1 取至 3 , 2 分频器 的分频系数可从 13 /2取至 1 ,复 位控制器主要是延长R s T EE 输入管脚上的 R S T信号的时间 , EE 使输入时钟稳定 。

寄存器

P I JDⅣ O P LM L o S DⅣ l C P DⅣ l I J P Ⅳ2 U

P Ⅳ3 U

C L

l

I

C工 1

Cz n D, n

有 两 个 Mc S ,分 别 为 Mc S 0 BP B P 和 Mc S 1 B P 。在本系统中 , B P Mc S 0

寄存器设置值

D

做为单 向的控 制通道控制 AI 2 B C 3

初始 化 , B P Mc S 1做 为双 向的数 据

l l j N

D ,£ J l 丁 工 C0[r , M ODE 一… … …

J n 呱

D 1 一 + 脚 l

通道 与 AI 2 B进行数据 的传 输 。 C3

点 DS P芯 片和 T V 2 AI 2 B音频编解码 器, 出了系统硬件的设计方案和 系统软件 的设 计思路 , L 30 C 3 给 并通过 了实际测试 。

【 关键词 】D PAC 3 ; ; S ;I2B接口 初始化 【 中图分类号 】 T 99 N 2

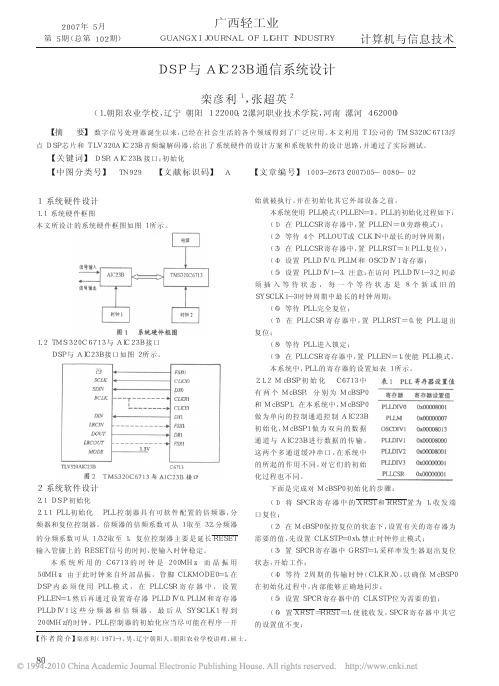

1 系统硬件 设计

11 系统硬件框图 .

本 系统 所 用 的 C 7 3的 时 钟 是 2 0 61 0 MHz ,而 晶 振 用

( )在 Mc S 0保持复位 的状态下 , 2 BP 设置有关 的寄存 器为 需要 的值 . 先设 置 C K T = x , L S P 0 b 禁止时钟停止模式 ; ( )置 S C 3 P R寄存 器中 G T 1采样率发 生器退 出复位 RS = , 状态 , 开始工作 ;

【 文献标识码 】 A

【 文章编号 】10 —63 07 5 08 - 2 03 27( 0) - 00 0 2 0

始就被执行 , 在初始化其它外部设备之前 。 并

本系统使用 P L L 模式( L E = ) P L的初始化过程如下 : P L N 1, L

本文所设计的系统 硬件框 图如 图 1 所示 。

Cs s L C K sD 咫 C工 丘

( )在 P L S 9 L C R寄存器中, P L 置 L EN=1使能 P L模式。 , L 本系统 中, L P L的寄存器 的设置如表 1 所示。

21 Mc S .2 . B P初 始 化 C 7 3中 61

表 1 P L寄存器设置值 L

( )在 P L S 7 L C R寄存器 中 , P L S 置 L R T=0 使 P L退 出 , L

图1 系统 硬 件 框 图

复位 ; ( )等待 P L进入锁定 ; 8 L

12 T 3 O 7 . MS 2 C6 1 3与 AI 3 C2 B接 口 DS P与 A C 3 I 2 B接 口如 图 2 示 。 所

这两 个多通道缓 冲串 口, 系统 中 在 的所起 的作用不 同 , 它们 的初 始 对

化过程也不 同。

T V ] . C23 L 20M B

C67 1 3

PL CS L R

图 2 T S 2 C6 3与 AI 3 M 3 0 71 C2 B接 口

一

2 系统 软件 设计

维普资讯

20 0 7年 5月

广 西 轻 工 业

第 5期( 总第 1 2期 ) 0

G A G Io A F I T D SR U N X 1 Lo G UTY J N LH

计 算机 与信 息技 术

D SP与 AI 2 B通 信 系统 设计 C 3

5 MHz 0 ,由于此时钟来 自外部 晶振 ,管脚 C K L MOD 0 I在 E=,

()等待 2 期 的传 输 时钟 ( L RX)以确保 M B P 4 周 CK / , c S0 在初始化过程 中, 能够正确地 同步 ; 内部 ( )设置 S C 5 P R寄存器中的 C K T L S P位为需要 的值 ; ()置雨 : 6 雨 : , 能收发 ,P R寄存器 中其 它 1使 SC

的设置值不变 ;

D P内必 须 使 用 P L模 式 ,在 P L S S L L C R寄 存 器 中 ,设 置

栾彦利 , 张超 英 z

(. 1朝阳农业学校, 辽宁 朝 阳 l 20 ;. 0 02漯河职业技术学院, 2 河南 漯河 4 2 0 ) 60 0

【 摘 要】数字 信号处理器 诞生以 已 在社会生活的 来, 经 各个领域得到了 广泛应用 本文利用T 公司的T 30 61浮 。 I MS2C 73

( )在 P L S 1 L C R寄存器 中 , P L N=0 旁路模式 ) 置 LE ( ;

( )等待 4个 P L T或 C K N中最 长的时钟周期 ; 2 L OU LI

( )在 P L S 3 L C R寄存器 中, P L S 置 L R T=1P L复位 ) (L ; ( )设置 P L V 、 L M和 O C I 寄存器 ; 4 L DI 0 P L S D V1

( )设置 P L V1 3 5 L DI — 。注意 : 在访问 P L I — 之 间必 L D V1 3

须 插 入 等 待 状 态 ,每 一 个 等 待 状 态 是 8个 新 或 旧 的

SS L — Y C K1 3时钟周期 中最长 的时钟周期 ; ( )等待 P L完全复ቤተ መጻሕፍቲ ባይዱ ; 6 L