MSP430主系统时钟以及430的低功耗设置

MSP430中文数据手册

MSP430混合信号微控制器数据手册产品特性●低电压范围:2.5V~5.5V 超低功耗●超低功耗——活动模式:330μA at 1MHz, 3V——待机模式:0.8μA——掉电模式(RAM数据保持):0.1μA ●从待机模式唤醒响应时间不超过6μs ●16位精简指令系统,指令周期200ns ●基本时钟模块配置基本时钟模块配置——多种内部电阻——多种内部电阻——单个外部电阻——单个外部电阻——32kHz晶振晶振——高频晶体——高频晶体——谐振器——谐振器——外部时钟源——外部时钟源●带有三个捕获/比较寄存器的16位定时器(Timer_A)串行在线可编程●串行在线可编程●采用保险熔丝的程序代码保护措施采用保险熔丝的程序代码保护措施该系列产品包括●该系列产品包括——MSP430C111:2K字节ROM,128字节RAM ——MSP430C112:4K字节ROM,256字节RAM ——MSP430P112:4K字节OTP,256字节RAM 原型●EPROM原型——PMS430E112:4KB EPROM, 256B RAM ●20引脚塑料小外形宽体(SOWB)封装,20引脚陶瓷双列直插式(CDIP)封装(仅EPROM)●如需完整的模块说明,请查阅MSP430x1xx系列用户指南(文献编号:SLAU049 产品说明TI公司的MSP43O系列超低功耗微控制器由一些基本功能模块按照不同的应用目标组合而成。

在便携式测量应用中,这种优化的体系结构结合五种低功耗模式可以达到延长电池寿命的目的。

以达到延长电池寿命的目的。

MSP430MSP430系列的CPU 采用16位精简指令系统,集成有16位寄存器和常数发生器,发挥了最高的代码效率。

它采用数字控制振荡器(DCO DCO)),使得从低功耗模式到唤醒模式的转换时间小于6μs.MSP430x11x 系列是一种超低功耗的混合信号微控制器,系列是一种超低功耗的混合信号微控制器,它拥有一个内置的它拥有一个内置的16位计数器和14个I/0引脚。

MSP430G2553学习笔记(数据手册)

MSP430G2553学习笔记(数据手册)MSP430G2553性能参数(DIP-20) 工作电压范围:1.8~3.6V。

5种低功耗模式。

16位的RISC结构,62.5ns指令周期。

超低功耗:运行模式-230µA;待机模式-0.5µA;关闭模式-0.1µA;可以在不到1µs的时间里超快速地从待机模式唤醒。

基本时钟模块配置:具有四种校准频率并高达16MHz的内部频率;内部超低功耗LF振荡器;32.768KHz晶体;外部数字时钟源。

两个16 位Timer_A,分别具有三个捕获/比较寄存器。

用于模拟信号比较功能或者斜率模数(A/D)转换的片载比较器。

带内部基准、采样与保持以及自动扫描功能的10位200-ksps 模数(A/D)转换器。

16KB闪存,512B的RAM。

16个I/O口。

注意:MSP430G2553无P3口!MSP430G2553的时钟基本时钟系统的寄存器DCOCTL-DCO控制寄存器DCOxDCO频率选择控制1MODxDCO频率校正选择,通常令MODx=0注意:在MSP430G2553上电复位后,默认RSEL=7,DCO=3,通过数据手册查得DCO频率大概在0.8~1.5MHz之间。

BCSCTL1-基本时钟控制寄存器1XT2OFF不用管,因为MSP430G2553内部没有XT2提供的HF时钟XTS不用管,默认复位后的0值即可DIV Ax设置ACLK的分频数00 /101 /210 /411 /8RSELxDCO频率选择控制2BCSCTL2-基本时钟控制寄存器2SELMxMCLK的选择控制位00 DCOCLK01 DCOCLK10 LFXT1CLK或者VLOCLK11 LFXT1CLK或者VLOCLK DIVMx设置MCLK的分频数00 /101 /210 /411 /8SELSSMCLK的选择控制位0 DCOCLK1 LFXT1CLK或者VLOCLK DIVSx设置SMCLK的分频数00 /101 /210 /411 /8DCORDCO直流发生电阻选择,此位一般设00 内部电阻1 外部电阻BCSCTL3-基本时钟控制寄存器3XT2Sx不用管LFXT1Sx00 LFXT1选为32.768KHz晶振01 保留10 VLOCLK11 外部数字时钟源XCAPxLFXT1晶振谐振电容选择00 1pF01 6pF10 10pF11 12.5pFmsp430g2553.h中基本时钟系统的内容/************************************************************* Basic Clock Module************************************************************/#define __MSP430_HAS_BC2__ /* Definition to show that Module is available */SFR_8BIT(DCOCTL); /* DCO Clock Frequency Control */SFR_8BIT(BCSCTL1); /* Basic Clock System Control 1 */SFR_8BIT(BCSCTL2); /* Basic Clock System Control 2 */SFR_8BIT(BCSCTL3); /* Basic Clock System Control 3 */#define MOD0 (0x01) /* Modulation Bit 0 */#define MOD1 (0x02) /* Modulation Bit 1 */#define MOD2 (0x04) /* Modulation Bit 2 */#define MOD3 (0x08) /* Modulation Bit 3 */#define MOD4 (0x10) /* Modulation Bit 4 */#define DCO0 (0x20) /* DCO Select Bit 0 */#define DCO1 (0x40) /* DCO Select Bit 1 */#define DCO2 (0x80) /* DCO Select Bit 2 */#define RSEL0 (0x01) /* Range Select Bit 0 */#define RSEL1 (0x02) /* Range Select Bit 1 */#define RSEL2 (0x04) /* Range Select Bit 2 */#define RSEL3 (0x08) /* Range Select Bit 3 */#define DIVA0 (0x10) /* ACLK Divider 0 */#define DIVA1 (0x20) /* ACLK Divider 1 */#define XTS (0x40) /* LFXTCLK 0:Low Freq. / 1: High Freq. */ #define XT2OFF (0x80) /* Enable XT2CLK */#define DIVA_0 (0x00) /* ACLK Divider 0: /1 */#define DIVA_1 (0x10) /* ACLK Divider 1: /2 */#define DIVA_2 (0x20) /* ACLK Divider 2: /4 */#define DIVA_3 (0x30) /* ACLK Divider 3: /8 */#define DIVS0 (0x02) /* SMCLK Divider 0 */#define DIVS1 (0x04) /* SMCLK Divider 1 */#define SELS (0x08) /* SMCLK Source Select 0:DCOCLK /1:XT2CLK/LFXTCLK */#define DIVM0 (0x10) /* MCLK Divider 0 */#define DIVM1 (0x20) /* MCLK Divider 1 */#define SELM0 (0x40) /* MCLK Source Select 0 */#define SELM1 (0x80) /* MCLK Source Select 1 */#define DIVS_0 (0x00) /* SMCLK Divider 0: /1 */#define DIVS_1 (0x02) /* SMCLK Divider 1: /2 */#define DIVS_2 (0x04) /* SMCLK Divider 2: /4 */#define DIVS_3 (0x06) /* SMCLK Divider 3: /8 */#define DIVM_0 (0x00) /* MCLK Divider 0: /1 */#define DIVM_1 (0x10) /* MCLK Divider 1: /2 */#define DIVM_2 (0x20) /* MCLK Divider 2: /4 */#define DIVM_3 (0x30) /* MCLK Divider 3: /8 */#define SELM_0 (0x00) /* MCLK Source Select 0: DCOCLK */#define SELM_1 (0x40) /* MCLK Source Select 1: DCOCLK */#define SELM_2 (0x80) /* MCLK Source Select 2: XT2CLK/LFXTCLK */#define SELM_3 (0xC0) /* MCLK Source Select 3: LFXTCLK */#define LFXT1OF (0x01) /* Low/high Frequency Oscillator Fault Flag */#define XT2OF (0x02) /* High frequency oscillator 2 fault flag */#define XCAP0 (0x04) /* XIN/XOUT Cap 0 */#define XCAP1 (0x08) /* XIN/XOUT Cap 1 */#define LFXT1S0 (0x10) /* Mode 0 for LFXT1 (XTS = 0) */#define LFXT1S1 (0x20) /* Mode 1 for LFXT1 (XTS = 0) */#define XT2S0 (0x40) /* Mode 0 for XT2 */#define XT2S1 (0x80) /* Mode 1 for XT2 */#define XCAP_0 (0x00) /* XIN/XOUT Cap : 0 pF */#define XCAP_1 (0x04) /* XIN/XOUT Cap : 6 pF */#define XCAP_2 (0x08) /* XIN/XOUT Cap : 10 pF */#define XCAP_3 (0x0C) /* XIN/XOUT Cap : 12.5 pF */#define LFXT1S_0 (0x00) /* Mode 0 for LFXT1 : Normal operation */ #define LFXT1S_1 (0x10) /* Mode 1 for LFXT1 : Reserved */#define LFXT1S_2 (0x20) /* Mode 2 for LFXT1 : VLO */#define LFXT1S_3 (0x30) /* Mode 3 for LFXT1 : Digital input signal */#define XT2S_0 (0x00) /* Mode 0 for XT2 : 0.4 - 1 MHz */#define XT2S_1 (0x40) /* Mode 1 for XT2 : 1 - 4 MHz */#define XT2S_2 (0x80) /* Mode 2 for XT2 : 2 - 16 MHz */#define XT2S_3 (0xC0) /* Mode 3 for XT2 : Digital input signal */基本时钟系统例程(DCO)MSP430G2553在上电之后默认CPU执行程序的时钟MCLK来自于DCO时钟。

2014MSP430选型手册

超低功耗性能 —— 模拟集成 —— 轻松启动设计工作

MSP430™ 16 位 RISC CPU

所有器件特性:

BOR $0.25

BOR

BOR

F1xx

速度:8 MHz

G2xx

ADC10,12 速度:16 MHz

ADC10

F4xx

速度:8/16 MHz

LCD

5xx

速度:25 MHz

• 16 位定时器

闪存:1-60KB Comp_A 闪存:0.5-8KB Comp A 闪存:4-120KB ADC10,12 闪存:8-256KB

参阅第 8 页和第 9 页,了解完整描述

轻松开展设计工作 MSP430 MCU 采用现代 16 位 RISC 架构以及简单的开发生态 系统,因而拥有极佳的易用性。

16 位正交架构 MSP430 MCU 采用的 16 位架构可提供 16 个高度灵活的、可 完全寻址的单周期操作 16 位 CPU 寄存器,以及 RISC 性能。 该 CPU 的现代设计不仅简洁,而且功能十分丰富,仅采用 了 27 条简单易懂的指令与 7 种统一寻址模式。

灵活的时钟系统 —— MSP430 MCU 时钟系统能启用和禁用 各种不同的时钟和振荡器,从而使器件能够进入不同的低 功耗模式 (LPM)。这种高度灵活的时钟系统可确保仅在适当 的时候启用所需时钟,从而能够显著优化总体能耗。

子系统时钟 (SMCLK) —— 用于各个较快速外设模块的源, 可由内部 DCO 驱动(频率最高达 25 MHz),也可采用外部 晶振驱动。

CPU 关闭,仅外设时钟可用。禁用 DC 生成 器。

无 RAM 保持,启用 RTC。(仅 MSP430F5xx 系列)

LPM4 关闭 CPU 且禁用所有时钟。

MSP430单片机实现时钟显示

MSP430单片机实现时钟显示MSP430单片机实现时钟显示MSP430系列振荡器是一种超低功耗存储器,它的每一系列根据不同的需要由不同的模块组成,其FLASH系列使高效电子系统变得轻巧。

FLASH驱动器同时也具有很强的灵活性。

同时为了在低控制器strong的驱动下得到较高的稳定频率,某些MSP430器件上使用了锁频技术FLL或增强型锁频环技术FLL+。

如MSP430F412的时钟模块中使用了FLL+技术,这样可以得到稳定的频率。

MSP430F413的典型工作电流为350uA(1MHz,3V)工作电压为1.8V;-;3.6V,由于它的程序代码熔丝保护,多次可擦写功能的FLASH 程序存储器,96字段的电阻电容可以直接驱动通常应用在测量频率上的字段型LCD,从而广泛应用于要求功耗低、时钟准确度高、进行实时时钟显示以及定时处理某些操作的仪表(如电子水表、电表、煤气表等)中。

本文介绍用MSP430F413实现实时时钟及其显示。

在驱动电路中,液晶可以等效为设备。

两个电极分别为公共极与段极。

公共极由CMOn信号驱动,段极由SEGn信号驱动。

由此可以得到4种驱动方法。

(1)静态驱动:使用一个引脚作为液晶公共端COM0,而每一段段极需要另一个引脚驱动。

(2)2MUX驱动:使用两个引脚作为液晶公共端COM0、COM1每两段段极需要另一引脚驱动。

(3)LCDUX驱动:使用三个引脚作为液晶公共端COM0、COM1、COM2,每3段段极需要另一引脚驱动。

(4)4MUX驱动:使用4个引脚作为液晶公共端COM0、COM1、COM2,每4段段极需要另一引脚驱动。

MSP430对液晶的驱动主要是通过液晶模块的寄存器LCD3ML和LCDMx来实现。

而驱动能力的不同也就是LCDMx寄存器的数量不同。

显示缓存器LCDMx越多,缓存越大,显示的内容就越多。

MSP430F413集成了96段液晶驱动器,具有较强的显示功能。

在本文中MSP430F413采用了4MUX方式,其显示缓存器中位与液晶段的对应关系如图1所示。

MSP430F169的时钟设置

MSP430F169的时钟设置MSP430F169的时钟设置1. 设置使⽤DCOCLK时钟源DCOCLK时钟源的配置DCOCTL = DCO0 + DCO1 + DCO2; // Max DCOBCSCTL1 = RSEL0 + RSEL1 + RSEL2; //设置成功DCOCLK时钟源,复位后MCLK默认是DCO//t = (32 - MODx) * t_DCO + MODx * t_DCO+1//f_t = (f_DCO * f_DCO+1)/(32 * f_DCO+1 + MODx *(f_DCO - f_DCO+1))DCOCTL = MOD0 + MOD1 + MOD2 + MOD3 + MOD4; //如果上述设置的频率不够就⽤该语句实现频率混合,MOD_N(1~31)SCSCTL2 |= DCOR //DCOR为0时,选择内部电阻,受温度影响⼤;DCOR为1时,选择外部精密电阻,受温度影响⼩MCLK信号使⽤DCOCLK时钟源,结合DCOCLK时钟源的配置//BCSCTL2 = SELM_(0,1,2,3); //SELM_0和SELM_1都是DCOCLK SELM_2是XT2CLK(⾼频) SELM_3是LFXT1CLK(低频)BCSCTL2 |= SELM_1; //MCLK信号选择时钟源为DCOCLK//BCSCTL2 = DIVM_(0,1,2,3); //DIVM_N就是对MCLK信号的频率进⾏2^N分频,依次为1、2、4、8分频BCSCTL2 |= DIVM_0; //对MCLK信号分频SMCLK信号使⽤DCOCLK时钟源,结合DCOCLK时钟源的配置//BCSCTL2 = SELS; //SELS为0时,选择DCOCLK时钟源;SELS为1时,选择外部时钟源,若XT2CLK时钟源,就为XT2CLK,否则就为LFXT1CLK时钟 BCSCTL2 &= ~SELS; //SMCLK信号选择时钟源为DCOCLK//BCSCTL2 = DIVS_(0,1,2,3); //DIVS_N就是对SMCLK信号的频率进⾏2^N分频,依次为1、2、4、8分频BCSCTL2 |= DIVS_0; //对SMCLK信号分频2. 设置使⽤XT2CLK时钟源XT2CLK时钟源的配置BCSCTL1 &= ~XT2OFF; //XT2OFF置位时关闭XT2CLK时钟源,XT2OFF复位时打开XT2CLK时钟//BCSCTL1 |= XTS; //XTS复位时LFXT1CLK为低频模式,置位时为⾼频模式,此时LFXT1CLK就可以替换XT2CLK时钟源volatile unsigned int i;do{IFG1 &= ~OFIFG; //复位后OFIFG为1,使⽤外部时钟源必须复位OFIFGfor (i = 0xFF; i > 0; i--); //等待复位}while ((IFG1 & OFIFG)); //如果还是置位则再次复位MCLK信号使⽤XT2CLK时钟源,结合XT2CLK时钟源的配置//BCSCTL2 = SELM_(0,1,2,3); //SELM_0和SELM_1都是DCOCLK SELM_2是XT2CLK(⾼频) SELM_3是LFXT1CLK(低频)BCSCTL2 |= SELM_2; //MCLK信号选择时钟源为XT2CLK//BCSCTL2 = DIVM_(0,1,2,3); //DIVM_N就是对MCLK信号的频率进⾏2^N分频,依次为1、2、4、8分频BCSCTL2 |= DIVS_0; //对SMCLK信号分频SMCLK信号使⽤XT2CLK时钟源,结合XT2CLK时钟源的配置//BCSCTL2 = SELS; //SELS为0时,选择DCOCLK时钟源;SELS为1时,选择外部时钟源,若XT2CLK时钟源村⼦,就为XT2CLK,否则就为LFXT1CLK时钟 BCSCTL2 = SELS; //SMCLK信号选择时钟源为XT2CLK//BCSCTL2 = DIVS_(0,1,2,3); //DIVS_N就是对SMCLK信号的频率进⾏2^N分频,依次为1、2、4、8分频BCSCTL2 |= DIVS_0; //对SMCLK信号分频3. 设置使⽤LFXT1CLK时钟源LFXT1CLK时钟源的配置//BCSCTL1 |= XTS; //XTS复位时LFXT1CLK为低频模式,置位时为⾼频模式,此时LFXT1CLK就可以替换XT2CLK时钟源volatile unsigned int i;do{IFG1 &= ~OFIFG; //复位后OFIFG为1,使⽤外部时钟源必须复位OFIFGfor (i = 0xFF; i > 0; i--); //等待复位}while ((IFG1 & OFIFG)); //如果还是置位则再次复位MCLK信号使⽤LFXT1CLK时钟源,结合LFXT1CLK时钟源的配置//BCSCTL2 = SELM_(0,1,2,3); //SELM_0和SELM_1都是DCOCLK SELM_2是XT2CLK(⾼频) SELM_3是LFXT1CLK(低频)BCSCTL2 |= SELM_3; //MCLK信号选择时钟源为LFXT1CLK//BCSCTL2 = DIVM_(0,1,2,3); //DIVM_N就是对MCLK信号的频率进⾏2^N分频,依次为1、2、4、8分频BCSCTL2 |= DIVS_0; //对SMCLK信号分频SMCLK信号使⽤LFXT1CLK时钟源,结合LFXT1CLK时钟源的配置,此时LFXT1CLK必须在⾼频模式下,LFXT1CLK时钟源的配置中的第1⾏不能注释//BCSCTL2 = SELS; //SELS为0时,选择DCOCLK时钟源;SELS为1时,选择外部时钟源,若XT2CLK时钟源存在,就为XT2CLK,否则就为LFXT1CLK时钟 BCSCTL2 = SELS; //SMCLK信号选择时钟源为LFXT1CLK⾼频//BCSCTL2 = DIVS_(0,1,2,3); //DIVS_N就是对SMCLK信号的频率进⾏2^N分频,依次为1、2、4、8分频BCSCTL2 |= DIVS_0; //对SMCLK信号分频ACLK信号使⽤LFXT1CLK时钟源,结合LFXT1CLK时钟源的配置//BCSCTL1 |= XTS; //XTS复位时LFXT1CLK为低频模式,置位时为⾼频模式,此时LFXT1CLK就可以替换XT2CLK时钟源//BCSCTL2 = DIVA_(0,1,2,3); //DIVA_N就是对ACLK信号的频率进⾏2^N分频,依次为1、2、4、8分频BCSCTL2 |= DIVA_0; //对SMCLK信号分频。

MPS430手册

T EXAS I NSTRUMENTSMPS430系列混合信号微控制器结构及模块用户指南目录1MSP430系列1.1特性与功能1.2系统关键性能1.3MSP430系列的各型号2结构概述2.1CPU2.2代码存储器2.3数据存储器(RAM)2.4运行控制2.5外围模块2.6振荡器、倍频器和时钟发生器3系统复位、中断和运行模式3.1系统复位和初始化3.2中断系统结构3.3中断处理3.3.1SFR中的中断控制位3.3.2外部中断3.4运行模式3.5低功耗模式3.5.1 低功耗模式0与模式1,LPM0和LPM1 3.5.2 低功耗模式2与模式3,LPM2和LPM3 3.5.3 低功耗模式4,LPM43.6 低功耗应用要点4 存储器组织4.1 存储器中的数据4.2 片内ROM组织4.2.1 ROM表的处理4.2.2 计算分支跳转和子程序调用4.3 RAM与外围模块组织4.3.1 RAM4.3.2 外围模块—地址定位4.3.3 外围模块--SFR5 16位CPU5.1 CPU寄存器5.1.1 程序计数器PC5.1.2 系统堆栈指针SP5.1.3 状态寄存器SR5.1.4 常数发生寄存器CG1与CG25.2 寻址模式5.2.1 寄存器模式5.2.2 变址模式5.2.3 符号模式5.2.4 绝对模式5.2.5 间接模式5.2.6 间接增量模式5.2.7 立即模式5.2.8 指令的时钟周期与长度5.3 指令组概述5.3.1 双操作数指令5.3.2 单操作数指令5.3.3 条件跳转5.3.4 模拟指令的短格式5.3.5 其它指令5.4 指令分布6 硬件乘法器6.1 硬件乘法器的操作6.2 硬件乘法器的寄存器6.3 硬件乘法器的SFR位6.4 硬件乘法器的软件限制6.4.1 硬件乘法器软件限制--寻址模式6.4.2 硬件乘法器软件限制--中断程序7 振荡器与系统时钟发生器7.1 晶体振荡器7.2 处理机时钟发生器7.3 系统时钟运行模式7.4 系统时钟控制寄存器7.4.1 模块寄存器7.4.2 与系统时钟发生器相关的SFR位7.5 DCO典型特性8 数字I/O配置8.1 通用端口P08.1.1 P0控制寄存器8.1.2 P0原理图8.1.3 P0中断控制功能8.2 通用端口P1、P28.2.1 P1、P2控制寄存器8.2.2 P1、P2原理图8.2.3 P1、P2中断控制功能8.3 通用端口P3、P48.3.1 P3、P4控制寄存器8.3.2 P3、P4原理图8.4 LCD端口8.5 LCD端口--定时器/端口比较器9 通用定时器/端口模块9.1 定时器/端口模块操作9.1.1 定时器/端口计数器TPCNT1,8位操作9.1.2 定时器/端口计数器TPCNT2,8位操作9.1.3 定时器/端口计数器,16位操作9.2 定时器/端口寄存器9.3 定时器/端口SFR位9.4 定时器/端口在A/D中的应用9.4.1 R/D转换原理9.4.2 分辨率高于8位的转换10 定时器10.1 Basic Timer110.1.1 BasicTimer1寄存器10.1.2 SFR位10.1.3 BasicTimer1操作10.1.4 BasicTimer1操作:LCD时钟信号f LCD 10.2 8位间隔(Interval)定时器/计数器10.2.1 8位定时器/计数器的操作10.2.2 8位定时器/计数器的寄存器10.2.3 与8位定时器/计数器有关的SFR 10.2.4 8位定时器/计数器在UART中的应用10.3 看门狗定时器10.3.1 看门狗定时器寄存器10.3.2 看门狗定时器中断控制功能10.3.3 看门狗定时器操作10.4 8位PWM定时器10.4.1 操作10.4.2 PWM寄存器11 Timer_A11.1 Timer_A的操作11.1.1 定时器操作11.1.2 捕获模式11.1.3 比较器模式11.1.4 输出单元11.2 Timer_A的寄存器11.2.1 Timer_A控制寄存器TACTL11.2.2 捕获/比较控制寄存器CCTL11.2.3 Timer_A中断向量寄存器11.3 Timer_A的应用11.3.1 Timer_A增计数模式应用11.3.2 Timer_A连续模式应用11.3.3 Timer_A增/减计数模式应用11.3.4 Timer_A软件捕获应用11.3.5 Timer_A处理异步串行通信协议11.4 Timer_A的特殊情况11.4.1 CCR0用作周期寄存器11.4.2 定时器寄存器的启/停11.4.3 输出单元Unit012 USART外围接口,UART模式12.1 异步操作12.1.1 异步帧格式12.1.2 异步通信的波特率发生器12.1.3 异步通信格式12.1.4 线路空闲多处理机模式12.1.5 地址位格式12.2 中断与控制功能12.2.1 USART接收允许12.2.2 USART发送允许12.2.3 USART接收中断操作12.2.4 USART发送中断操作12.3 控制与状态寄存器12.3.1 USART控制寄存器UCTL12.3.2 发送控制寄存器UTCTL12.3.3 接收控制寄存器URCTL12.3.4 波特率选择和调制控制寄存器12.3.5 USART接收数据缓存URXBUF12.3.6 USART发送数据缓存UTXBUF12.4 UART模式,低功耗模式应用特性12.4.1 由UART帧启动接收操作12.4.2 UART模式波特率与时钟频率12.4.3 节约MSP430资源的多处理机模式12.5 波特率的计算13 USART外围接口,SPI模式13.1 USART的同步操作13.1.1 SPI模式中的主模式,MM=1、SYNC=1 13.1.2 SPI模式中的从模式,MM=0、SYNC=1 13.2 中断与控制功能13.2.1 USART接收允许13.2.2 USART发送允许13.2.3 USART接收中断操作13.2.4 USART发送中断操作13.3 控制与状态寄存器13.3.1 USART控制寄存器13.3.2 发送控制寄存器UTCTL13.3.3 接收控制寄存器URCTL13.3.4 波特率选择和调制控制寄存器13.3.5 USART接收数据缓存URXBUF 13.3.6 USART发送数据缓存UTXBUF14 液晶显示驱动14.1 LCD驱动基本原理14.2 LCD控制器/驱动器14.2.1 LCD控制器/驱动器功能14.2.2 LCD控制及模式寄存器14.2.3 LCD显示存储器14.2.4 LCD操作软件例程14.3 LCD端口功能14.4 LCD与端口模式混合应用实例15 A/D转换器15.1 概述15.2 A/D转换操作15.2.1 A/D转换15.2.2 A/D中断15.2.3 A/D量程15.2.4 A/D电流源15.2.5 A/D输入端与多路切换15.2.6 A/D接地与降噪15.2.7 A/D输入与输出引脚15.3 A/D控制寄存器16 其它模块16.1 晶体振荡器16.2 上电电路16.3 晶振缓冲输出附录A 外围模块分布附录B 指令组说明附录C EPROM编程本书用途及表述约定MSP430用户指南以方便工程师及程序员使用的方式提供软件和硬件资料,以帮助开发应用MSP430系列的产品。

TI MSP430AFE2x3 2x2 2x1 微控制器说明书

MSP430AFE2x3MSP430AFE2x2MSP430AFE2x1 ZHCS136A–NOVEMBER2010–REVISED MARCH2011混合信号微控制器特性•低电源电压范围:1.8V至3.6V•多达3个具有差分可编程增益放大器(PGA)输入的24位三角积分模数(A/D)转换器•超低功耗•具有3个捕获/比较寄存器的16位Timer_A –激活模式:220μA(在1MHz频率和2.2V电压条件下)•串行通信接口(USART),可用软件来选择异步UART或同步SPI–待机模式:0.5μA•16位硬件乘法器–关闭模式(RAM保持):0.1μA•欠压检测器•5种节能模式•具有可编程电平检测功能的电源电压监控器/监视器•可在不到1μs的时间里超快速地从待机模式唤醒•串行板上编程,无需从外部进行电压编程,利用安•16位精简指令集(RISC)架构,高达12MHz系统时全熔丝实现可编程代码保护钟•片上仿真模块•基本时钟模块配置•系列成员汇总于表1。

–带有两个已校准频率的高达12MHz的内部频率•如需了解完整的模块说明,请参阅《MSP430x2xx –内部超低功耗低频(LF)振荡器系列用户指南》,文献编号SLAU144–高达16MHz的高频(HF)晶振–谐振器–外部数字时钟源说明德州仪器(TI)MSP430™系列超低功率微控制器包含几个器件,这些器件特有针对多种应用的不同的外设集。

这种架构与5种低功耗模式相组合,专为在便携式测量应用中延长电池使用寿命而优化。

该器件具有一个强大的16位RISC CPU,16位寄存器和有助于获得最大编码效率的常数发生器。

数字控制振荡器(DCO)可在不到1µs 的时间里完成从低功耗模式至运行模式的唤醒。

MSP430AFE2x3器件是超低功耗混合信号微控制器,集成了三个独立的24位三角积分A/D转换器、一个16位定时器、一个16位硬件乘法器、USART通信接口、安全装置定时器和11个I/O引脚。

msp430 时钟与休眠模式

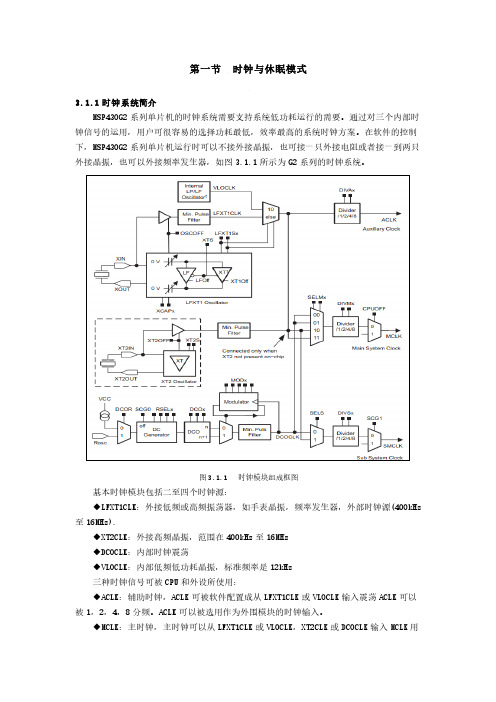

第一节时钟与休眠模式3.1.1 时钟系统简介MSP430G2系列单片机的时钟系统需要支持系统低功耗运行的需要。

通过对三个内部时钟信号的运用,用户可很容易的选择功耗最低,效率最高的系统时钟方案。

在软件的控制下,MSP430G2系列单片机运行时可以不接外接晶振,也可接一只外接电阻或者接一到两只外接晶振,也可以外接频率发生器,如图3.1.1所示为G2系列的时钟系统。

图3.1.1 时钟模块组成框图基本时钟模块包括二至四个时钟源:◆LFXT1CLK:外接低频或高频振荡器,如手表晶振,频率发生器,外部时钟源(400kHz 至16MHz).◆XT2CLK:外接高频晶振,范围在400kHz至16MHz◆DCOCLK:内部时钟震荡◆VLOCLK:内部低频低功耗晶振,标准频率是12kHz三种时钟信号可被CPU和外设所使用:◆ACLK:辅助时钟,ACLK可被软件配置成从LFXT1CLK或VLOCLK输入震荡ACLK可以被1,2,4,8分频。

ACLK可以被选用作为外围模块的时钟输入。

◆MCLK:主时钟,主时钟可以从LFXT1CLK或VLOCLK,XT2CLK或DCOCLK输入MCLK用在CPU系统之中。

◆SMCLK:辅助主时钟。

SMCLK可被选择从LFXT1CLK,VLOCLK,XT2CLK或DCOCLK输入。

SMCLK可以被1,2,4,8分频。

SMCLK可被选用为外围模块的时钟。

如图3.1.1所示为G2系列的时钟系统。

需要说明的是并非每一款G2系列的单片机都具有如上的时钟系统,以下做详细说明:MSP430G22x0:无LFXT1,无XT2,不支持ROSCMSP430G21x1,MSP430G2xx2,MSP430G2xx3:LFXT1不支持HF模式,无XT2,不支持ROSC。

MSP430x21x2:无XT23.1.2 时钟系统的操作在一个PUC信号之后,MCLK和SMCLK开始从DCO(大约在1.1MHz),ACLK从LFXT1CLK (内部电容为6pF)获取时钟。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

LPM3_EXIT;//退出低功耗模式

}

tips:感谢大家的阅读,本文由我司收集整编。仅供参阅!

BCSCTL1&=~XT2OFF;//~0x80

do

{

IFG1&=~OFIFG;//OFIFG为1表示外部晶体振荡器失效

for(i=0xff;i0;i--);//IFG1是InterruptFlag1

}

while((IFG1&OFIFG));//表示振荡器已经起振

BCSCTL2|=SELM_2;//#defineSELM_2(0x80)/*MCLKSourceSelect2:XT2CLK/LF

关闭外部中断:_DINIT();

430外部中断的模式

#include

main(void)

{

BCSCTL1=DIVA_2;//(0x20)/*ACLKDivider2:/4*/

WDTCTL=WDT_ADLY_1000;//直接将看门狗定时器变成定时器,定时

时间是1000毫秒

IE1=WDTIE;//打开定时器中断

P2DIR|=BIT3;

while(1)

{

unsignedinti;

_BIS_SR(LPM3_bits+GIE);//进入低功耗模式3,这种时候,cpu停止工

作,同时打开总的中断//_BIS_SR是一个本增函数,

//_BIS_SR()是一个本增函数,通过本函数可以对寄存器进行直接的操作

//这句话等价于_EINT();

//LPM3;

P2OUT&=~BIT3;//相当于把第五位输出0

for(i=180000;i0;i--);//延时

P2OUT|=BIT3;//p3.5输出1

}

}

#pragmavector=WDT_VECTOR

__interruptvoidwatchdag_timer(void)

{

//__BIC_SR_IRQ(LPM3_bits);//从中断中,将低功耗模式退出,将cpu从

XTCLK*/

while(1);

}

低功耗模式的设置:

msp430内部有4种低功耗模式,在进入低功耗模式的时候,cpu停止,

一般是由外部事件的响应才能唤醒cpu

由于IAR软件比较给力,所以进入低功耗模式的常用格式

比如:

进入低功耗模式2:LPM2;

退出低功耗模式2:LPM2_EXIT;

开启外部中断:_EINT():

MSP430主系统时钟以及430的低功耗设置

如何将系统时钟设置到外部高频晶体振荡器,430的MCLK默认的是

DCO的,如何安全的从DCO切换到外部晶体振荡器,这是一个很重要的步骤,

因为经过此步骤,可以极大地提高430的处理能力,DCO在内部,可以为cpu

提供强劲稳定的时钟

#include

voidmain(void)

{

//Stopwatchdogtimertopreventtimeoutreset

WDTCTL=WDTPW+WDTHOLD;

volatileunsignedinti;

P5DIR|=BIT4;//设置P5.4为输出

P5SEL|=BIT4;//设置片内主系统时钟的输出

//由这段代码设置如何将DCO切换到高频晶体振荡器