SDRAM读写测试

DDR3测试读写

DDR3测试读写(1)今天是重阳节,所以提前祝福重阳节快乐。

因为DDR3讲解内容比较多,所以分解成3节进行讲解。

一个做FPGA的人如果不懂DDR3,Serdes,那基本等于没学习fpga。

所以必须掌握ddr控制器才能深入fpga具体功能。

注意以后基本工具都是用的vivado2014.02版本。

用ise导致不一样,不要问我。

该工程参考的xilinx的文档xtp225。

首先是打开vivado,建完工程以后,然后点击IP catalog,打开ip库。

找到Memory Interface Generator IP核。

然后会出现图1.2页面图1.1图1.2的显示信息是当前工程设置的器件信息。

vivado不像以前的ISE,分离IP工程。

现在都是一个工程。

所以要注意观察该页面显示的器件是否正确。

经常有人选错速度等级而导致无法通过后期时序仿真。

图1.2图1.3是选择创建一个设计。

图1.3图1.4选择ddr3芯片。

图1.4图1.5显示的是兼容引脚。

选择next。

图1.5图1.6是选择选择DDR的时钟,记住,DDR是双边沿。

所以上面写的400MHz,也就是DDR 800M。

选额内存类型是SODIMMs。

内存类型是MT6JTF12864HZ-1G6类型。

Data Mask 数据掩码,可以选择或者不选择,类似于sdram的dqm信号。

有人问这有啥作用。

就等于内存中,你要改变其中几个bit而不是改变全部bit。

所以用掩码方式更好的。

否则你要读出来,然后再写入,这种方法太消耗时间。

图1.6图1.7是表示选择整个IP输入时钟多少,基本DDR3寄存器控制。

基本IP输入时钟在SPARTAN6的MIG核是没有选择,需要手动修改时钟文件。

这里有提供输入时钟选择。

读写burst的方式,一个顺序读取还有个strict 跳跃式读取。

除非你有特殊的要求,一般都是顺序读取。

输出驱动电阻控制RZQ/7和RTT电阻,这个电阻是从datasheet手册得到的。

用于测试SDRAM控制器的PDMA-设计应用

用于测试SDRAM控制器的PDMA-设计应用1引言现代电子信息设备往往需要保存和处理大量的数字信息,一个高性能的Memory控制器可以大大提高系统的性能。

在进行SDRAM 控制器的设计时,需要考虑很多因素,设计完成以后还要进行多项测试看是否完全满足所要求的各项性能,为此我们设计了一个PDMA (Programmable Direct Mem o ry Access)用于测试SDRAM控制器的性能。

在SoC中,SDRAM控制器往往跟多个IP模块(图形处理单元,音频处理单元等)交换数据,采用多个PDMA通道同时访问Memory 可以真实模拟SDRAM控制器在SoC环境中被多个IP随机访问的情形。

2 PDMA的结构及工作原理PDMA是可编程直接存储器存取的简称。

图1 虚中框内是PDMA的内部模块结构,它主要由寄存器组和控制器两大部分构成,寄存器组用于保存配置参数和PDMA对SDRMA控制器访问后的状态信息及接收、启动、停止等控制信息。

图2是PDMA寄存器组的内部结构。

寄存器组模块里包含了一个同步模块、控制寄存器、状态寄存器和各通道的寄存器组。

每一个子通道的寄存器组又包含访问基址寄存器、访问模式寄存器、周期计数器等三个寄存器。

各寄存器的功能描述如表1所示。

PDMA的控制器主要由:产生写数据的状态机、地址译码模块、FIFO以及读数据校验模块四部分构成。

各模块的功能由表2描述。

PDMA控制器的结构如图3所示,其逻辑是一个状态机,我们采用一个两层嵌套的状态机来实现控制功能,如图4所示。

3 测试系统的结构和工作原理在本设计中,PDMA用于仿真多个IP核对SDRAM控制器进行读写访问以验证SDRAM控制器的设计是否高效合理,性能是否稳定等指标。

PDMA整个测试系统由PCI接口模块、PDMA 以及SDRAM控制器三大部分构成(见图1)。

PCI接口模块与PDMA之间以内部IO总线相连接。

PDMA与SDRAM控制器之间以内部Memory总线连接。

SDRAM测试案例分析

DDR测试系列之三——某SDRAM时钟分析案例前个周末接到了一个朋友的电话,询问我如果内存有问题,需要测试哪些项目?对于这个很常见的问题,我习惯性的回答他先测量内存时钟和读写时序看看,然后结束了通话。

没过一会,我那朋友又打过来,告诉我他遇到一个怪事,他用探头点测内存时钟时,系统的程序不卡了,可以顺利启动并运行。

听到这个描述,我顿时感兴趣了,开始仔细询问待测试的电路和测试仪器。

待测试的电路板的内存控制器为A公司的ARM架构的MCU,内存为Micron的SDRAM,内存时钟频率为100MHz,测试仪器为某200M带宽示波器,探头为示波器标配的无源探头。

在以往的探头培训中,我曾多次给客户讲探头的重要性,在我的幻灯片中有以下几句话:在把探头连接到电路上时,可能会发生下面三种情况:1. 您可以把实际波形形状传送到示波器屏幕上。

2. 探头可能会改变波形形状,您会在示波器上观察到不同形状的信号。

3. 您可能会改变被测设备的运行(良好的设备可能会开始不能正确运行,或反之)显然,今天我这位朋友遇到的情况正好满足第三种的最后三个字,即探头使运行异常的设备变正常了。

如果这样的情况能经常发生,想必每位加班debug电路的工程师都可以不再苦恼,只需一个合适的探头就可以找到问题原因并解决问题了。

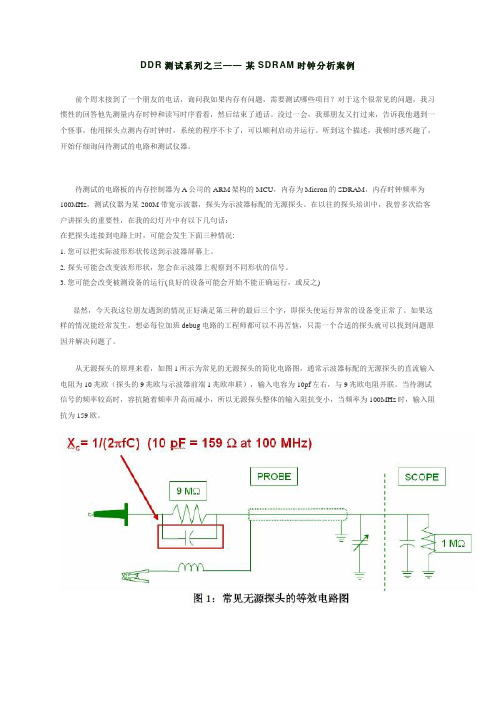

从无源探头的原理来看,如图1所示为常见的无源探头的简化电路图,通常示波器标配的无源探头的直流输入电阻为10兆欧(探头的9兆欧与示波器前端1兆欧串联),输入电容为10pf左右,与9兆欧电阻并联。

当待测试信号的频率较高时,容抗随着频率升高而减小,所以无源探头整体的输入阻抗变小,当频率为100MHz时,输入阻抗为159欧。

回到和朋友的对话,既然无源探头在100MHz时等效于100多欧的电阻,于是我建议他找个100欧的电阻并联端接到内存芯片的时钟上,即时钟信号接100欧电阻到地。

十多分钟后,朋友告诉我并联100欧电阻后系统正常工作了,可以结束加班了。

SDRAM测试

SDRAM使用

本发板使用的8MBYTE,16位SDRAM,型号为:现代, HY57V641620,可完全兼容于三星的K4S641632。

一般是用于基于NiosII CPU的SOPC系统中,因为altera已提供了SDRAM控制器的IP,在SOPC系统中使用SDRAM已变得非常的简单。

在程序中直接使用地址访问SDRAM即可。

1、SDRAM的测试

光盘中提供SDRAM的测试工程mem_test。

把此工程中的mem_test.sof通过JTAG口下载到开发板上,然后在开始菜单->程序->altera->NiosEDS中打开NiosII Command Shell,输入nios2-terminal命令,开发板通过JTAG将测试信息发送到PC机,如下图如示:

测试全部passed说明SDRAM正常,测试成功后开发板上LED轮流闪动。

2、SDRAM的使用

如果FPGA的开发过程中,不使用SDRAM,但是又要使用SDRAM的管脚时可以把SDRAM的片选信号在FPGA内部拉高,使SDRAM处于三态高阻态,不影响与其相连的FPGA管脚的使用,如下图把SDRAM片选拉高:。

SDRAM读写说明3

SF-EP1C开发板使用说明

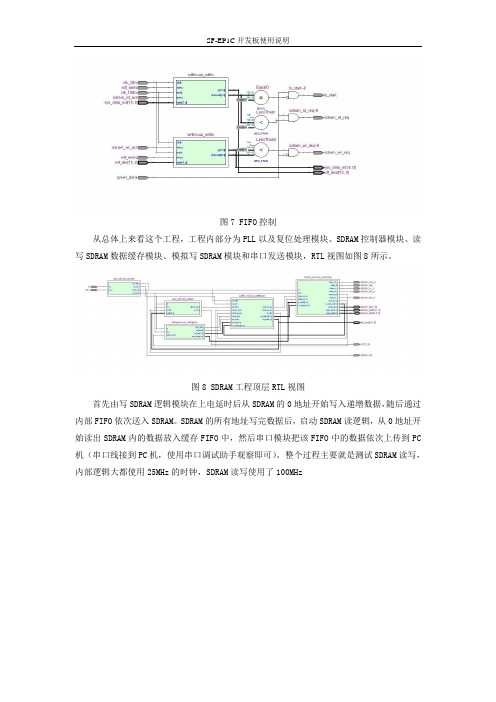

图7 FIFO控制

从总体上来看这个工程,工程内部分为PLL以及复位处理模块、SDRAM控制器模块、读写SDRAM数据缓存模块、模拟写SDRAM模块和串口发送模块,RTL视图如图8所示。

图8 SDRAM工程顶层RTL视图

首先由写SDRAM逻辑模块在上电延时后从SDRAM的0地址开始写入递增数据,随后通过内部FIFO依次送入SDRAM。

SDRAM的所有地址写完数据后,启动SDRAM读逻辑,从0地址开始读出SDRAM内的数据放入缓存FIFO中,然后串口模块把该FIFO中的数据依次上传到PC 机(串口线接到PC机,使用串口调试助手观察即可)。

整个过程主要就是测试SDRAM读写,内部逻辑大都使用25MHz的时钟,SDRAM读写使用了100MHz。

【黑金原创教程】【FPGA那些事儿-驱动篇I】实验二十二:SDRAM模块⑤—FIFO读写

【⿊⾦原创教程】【FPGA那些事⼉-驱动篇I】实验⼆⼗⼆:SDRAM模块⑤—FIFO读写经过漫长的战⽃以后,我们终于来到最后。

对于普通⼈⽽⾔,页读写就是⼀名战⼠的墓碑(最终战役) ... 然⽽,怕死的笔者想透过这个实验告诉读者,旅程的终点就是旅程的起点。

⼀直以来,笔者都在烦恼“SDRAM是否应该成为储存类?”SDRAM作为⼀介储存资源(储存器),它的好处就是⼤容量空间,坏处则就是⿇烦的控制规则,还有中规中矩的沟通速率。

相⽐之下,⽚上内存⽆论是控制的难度,还是沟通的速率,它都远远领先SDRAM。

俗语常说,愈是强⼒的资源愈是珍贵 ... 对此,⽚上内容的容量可谓是稀罕的程度。

实验⼆⼗⼆的要求⾮常单纯:”请问如何建⽴基于SDRAM储存资源的FIFO存储模块呢?“,笔者问道。

图22.1 SDRAM基础模块。

图22.1是基于实验⼗⼋修改⽽成的SDRAM基础模块,修改对象除了SDRAM控制模块以外,SDRAM功能模块保持实验⼗⼋的状态,即单字读写。

SDRAM控制模块,除了多出Tag以外,Addr的驱动也由该模块负责。

具体的内容,让我们来看代码吧:1. module sdram_ctrlmod2. (3. input CLOCK,4. input RESET,5. input [1:0]iCall, // [1]Write, [0]Read6. output [1:0]oDone,7. output [3:0]oCall,8. input iDone,9. output [23:0]oAddr,10. output [1:0]oTag11. );12. parameter WRITE = 4'd1, READ = 4'd4, REFRESH = 4'd7, INITIAL = 4'd8;13. parameter TREF = 11'd1040;14.以上内容为相关的出⼊端声明以及常量。

SDRAM的读写时序与突发长度

SDRAM的读写时序与突发长度在选定列地址后,就已经确定了具体的存储单元,剩下的事情就是数据通过数据I/O通道(DQ)输出到内存总线上了。

但是在CAS发出之后,仍要经过一定的时间才能有数据输出,从CAS与读取命令发出到第一笔数据输出的这段时间,被定义为CL(CAS Latency,CAS 潜伏期)。

由于CL只在读取时出现,所以CL又被称为读取潜伏期(RL,Read Latency)。

CL的单位与tRCD一样,为时钟周期数,具体耗时由时钟频率决定。

不过,CAS并不是在经过CL周期之后才送达存储单元。

实际上CAS与RAS一样是瞬间到达的,但CAS的响应时间要更快一些。

为什么呢?假设芯片位宽为n个bit,列数为c,那么一个行地址要选通n×c个存储体,而一个列地址只需选通n个存储体。

但存储体中晶体管的反应时间仍会造成数据不可能与CAS在同一上升沿触发,肯定要延后至少一个时钟周期。

由于芯片体积的原因,存储单元中的电容容量很小,所以信号要经过放大来保证其有效的识别性,这个放大/驱动工作由S-AMP负责,一个存储体对应一个S- AMP通道。

但它要有一个准备时间才能保证信号的发送强度(事前还要进行电压比较以进行逻辑电平的判断),因此从数据I/O总线上有数据输出之前的一个时钟上升沿开始,数据即已传向S-AMP,也就是说此时数据已经被触发,经过一定的驱动时间最终传向数据I/O总线进行输出,这段时间我们称之为tAC (Access Time from CLK,时钟触发后的访问时间)。

tAC的单位是ns,对于不同的频率各有不同的明确规定,但必须要小于一个时钟周期,否则会因访问时过长而使效率降低。

比如PC133的时钟周期为7.5ns,tAC则是5.4ns。

需要强调的是,每个数据在读取时都有tAC,包括在连续读取中,只是在进行第一个数据传输的同时就开始了第二个数据的tAC。

CL=2与tAC示意图CL的数值不能超出芯片的设计规范,否则会导致内存的不稳定,甚至开不了机(超频的玩家应该有体会),而且它也不能在数据读取前临时更改。

DE2 Nios II SDRAM调试总结

DE2 Nios II SDRAM调试总结首先定制CPU,由于是对SDRAM读写进行测试,添加了onchip-memory。

(测试正常之后便可重新建立工程在SDRAM中运行程序)DE2平台上的SDRAM时序,要求将DE2所提供的50MHz时钟延迟3ns或者延迟60度之后作为SDRAM的输入时钟(此处延迟3ns即可),可以用锁相环来产生这个时钟延迟。

按下列步骤生锁相环的代码:(1)用Tools>MegaWizard Plug-In Manager菜单建立一个新的Megafunction。

(2)在Installed Plug-Inz中的I/O中选中ALTPLL,并将输入的文件命名为SDRAM_CLK.(3)在向导的第3页中将inclock0的输入频率改为50MHz。

(4)取消向导第4页的所有选项。

(5)将向导第6页中的Clock Phase Shift项设为-3ns,其余参数保持不变,完成生成锁相环的配置。

最后生成的图如下:用来进行测试的程序(书上的参考程序):#include "system.h"#include "altera_avalon_pio_regs.h" int main(){IOWR(SDRAM_BASE,0,3);IOWR_ALTERA_AVALON_PIO_DATA(LED_BASE,IORD(SDRAM_BASE,0));return 0;}编译总是出错:**** Build of configuration Debug for project blank_project_0 **** make -s allCompiling SDRAM.c...../SDRAM.c: In function `main':../SDRAM.c:6: error: `SDRAM' undeclared (first use in this function) ../SDRAM.c:6: error: (Each undeclared identifier is reported only once ../SDRAM.c:6: error: for each function it appears in.)make: *** [obj/SDRAM.o] Error 1Build completed in 182.172 seconds即SDRAM未定义,但CPU中定义的名字是SDRAM。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SDRAM读写测试说明

首先,特权同学不想对SDRAM是什么以及SDRAM的工作原理等基础知识做太多叙述。

希望对这方面做深入了解(想玩转SDRAM当然要先对它的特性了如指掌)的朋友可以参考《高手进阶,终极内存技术指南——完整/进阶版》一文,据说该文章曾发表于《电脑高手》杂志2002年第12期。

好东西一般都是在网络上伸手可及,而且还有很多经过恩多后来人加工修订后的版本。

特权同学也是看着该文章入门的,但是要真正掌控SDRAM还是得在动手实践中多花时间琢磨。

SF-EP1C开发板上使用的是三星SDR SDRAM(K4S641632)。

由于控制SDRAM的读写不同于之前的很多简单接口实验(它们对时序的要求都不高,即便不做时序约束也无关紧要),SDRAM的时钟沿和数据总线、地址总线以及控制总线都存在严格的时序关系,尤其当频率较高(我们的设计中达到了100MHz,接近了该器件标称的133MHz的最高频率)时,稍有闪失就会造成通信的不正常。

该实例的核心是设计一个SDRAM控制器。

首先,设计者需要对这个控制器内部的逻辑功能做细分,将其划分为多个子模块来实现。

如图1所示,sdram_ctrl是SDRAM状态控制模块,该模块主要完成SDRAM的上电初始化以及定时刷新、读写控制等状态的变迁,内部设计了两个状态机,一个用于上电初始化的状态控制,另一个则用于正常工作时的状态控制;sdram_cmd是SDRAM命令模块,该模块根据sdram_ctrl模块的不同状态指示输出相应的SDRAM控制命令和地址(控制总线信号如sdram_cke、sdram_cs_n、sdram_we_n、sdram_ras_n、sdram_cas_n,地址总线信号sdram_addr);sdram_wr_data是SDRAM数据读写模块,该模块同样是根据sdram_ctrl模块的状态指示完成SDRAM数据总线的控制,SDRAM的数据读写都在该模块完成。

图1 SDRAM控制器RTL视图

SDRAM的上电初始化步骤一般是(相关的基本概念请参考前文推荐的参考文章):

●等待200us,这是SDRAM的输入稳定期;

●所有L-BANK预充电;

●至少8个预刷新周期;

●模式寄存器设置(MSR),完成SDRAM读写相关的配置。

Clock

图2 SDRAM初始化

如图3所示,SDRAM的初始化状态机有20个状态,最后到达I_DONE状态后停止,说明初始化完成,然后另一个用于指示SDRAM正常工作状态的状态机将被激活。

关于SDRAM正常工作的读写时序请读者参考相关datasheet《K4S641632C.pdf》,这里不花太多篇幅讨论。

SDRAM正常工作状态下的状态迁移如图4所示。

不操作SDRAM时处于W_IDLE状态,如果有读请求、写请求或者自刷新请求信号产生,则进入的相应的状态,在

这些不同的响应状态中,设计者需要协调好SDRAM的控制总线、地址总线、数据总线,从而

SDRAM的数据。

保证稳定可靠的读写

再说SDRAM的时钟信号产生,这个时钟信号主要是输出给SDRAM使用,用于同步FPGA

传输给SDRAM的信号。

如图5所示,这个时钟和信号间必须是中央对齐的,以保证传输信号在时钟的上升沿正确的被SDRAM接收。

SDRAM_CLK

DATA

图5 输出信号与SDRAM时钟

而系统时钟(FPGA内部的工作时钟)和输出信号的关系却如图6所示。

CLK

DATA

图6 输出信号与系统时钟

那么如何能够保证SDRAM的驱动时钟和信号的关系如图5所示呢?使用PLL来调整时钟频率和相位是不错的选择,因此特权同学根据调试和时序分析的结果,对传输到SDRAM的时钟信号添加了+3ns的偏移,从而保证了SDRAM在锁存数据时有可靠的建立时间和保持时间裕量。

这个相位偏移是必需的,但不是固定的,设计者需要具体问题具体分析。

说完这个SDRAM的底层控制方式,我们还要来看其它模块如何利用它达到有效的数据读写。

这里借助了两个存储器(异步FIFO)来达到这个目的,wrfifo用于写SDRAM数据,rdfifo 用于读SDRAM数据。

由于该工程中SDRAM读写都是以8个字(16bit)为单位,所以使用了FIFO当前数据量作为操作SDRAM的状态指示.当wrfifo数量超过8个则发出写SDRAM请求,在写选通期间,适当的时候就将相应的读出wrfifo中的8个数据。

同样,在rdfifo数据少于256个字节(rdfifo半空)时发出读SDRAM请求,适当的时候将读出8个新的数据写入rdfifo中,以保证后续电路总是持续的传输从rdfifo读出的数据。

图7 FIFO控制

从总体上来看这个工程,工程内部分为PLL以及复位处理模块、SDRAM控制器模块、读写SDRAM数据缓存模块、模拟写SDRAM模块和串口发送模块,RTL视图如图8所示。

图8 SDRAM工程顶层RTL视图

首先由写SDRAM逻辑模块在上电延时后从SDRAM的0地址开始写入递增数据,随后通过内部FIFO依次送入SDRAM。

SDRAM的所有地址写完数据后,启动SDRAM读逻辑,从0地址开始读出SDRAM内的数据放入缓存FIFO中,然后串口模块把该FIFO中的数据依次上传到PC 机(串口线接到PC机,使用串口调试助手观察即可)。

整个过程主要就是测试SDRAM读写,内部逻辑大都使用25MHz的时钟,SDRAM读写使用了100MHz。