Alisertib_1028486-01-2_DataSheet_MedChemExpress

KSZ8851-16MLL DEMO BOARD 48-PIN ETHERNET CONTROLLE

SD13

SD7 40

CPU_D14 3

6

SD14

SD8 39

CPU_D15 4

5

SD15

SD9 36

SD10 35

33

SD11 34

CPU_CMD

33

SD12 33

R10

SD13 32

CPU_CSN

33

SD14 31

R12

SD15 30

CPU_WRN

33

CMD

11

R14

CPU_RDN

33

CSN

12

R16

5 6 7 8

TANT

C27

R28 10uF

470pF 2.49K

Power 3.3V 0.1uF (red LED)

CSN CMD

4.7K R27 4.7K R29

GBLC03C_0 D3

GND 2 GND

VR 5 3.3VA

INTRN 4.7K R30

VOUT = 1.24 X [ 1 + ( 2.49k/ 1.5K ) ]

5

4

3

KSZ8851-16MLL (48-pin) Demo Board Black Diagram

D

Headers 20x2

RJ45

LAN1 T

KSZ8851-16MLL

Reset

Power

+1.8V

+2.5V

+3.3V

STATUS LEDs

OSC

EEPROM

C

MIC5209YM

25 MHz

AT93C46

x2

2

1

DATE:

ALC5621_DataSheet_1.0

ALC5621I2S AUDIO CODEC + 1.3W CLASS AB/D MONO SPEAKER AMPLIFIERDATASHEETRev. 1.027 December 2007Track ID: JATR-1076-21Realtek Semiconductor Corp.No. 2, Innovation Road II, Hsinchu Science Park, Hsinchu 300, TaiwanTel.: +886-3-578-0211. Fax: +886-3-577-6047I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifierii Track ID: JATR-1076-21 Rev. 1.0COPYRIGHT ©2007 Realtek Semiconductor Corp. All rights reserved. No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form or by any means without the written permission of Realtek Semiconductor Corp.DISCLAIMERRealtek provides this document “as is”, without warranty of any kind, neither expressed nor implied, including, but not limited to, the particular purpose. Realtek may make improvements and/or changes in this document or in the product described in this document at any time. This document could include technical inaccuracies or typographical errors.TRADEMARKSRealtek is a trademark of Realtek Semiconductor Corporation. Other names mentioned in this document are trademarks/registered trademarks of their respective owners.USING THIS DOCUMENTThis document is intended for the hardware and software engineer’s general information on the Realtek ALC5621 Audio Codec IC.Though every effort has been made to ensure that this document is current and accurate, more information may have become available subsequent to the production of this guide. In that event, please contact your Realtek representative for additional information that may help in the development process. REVISION HISTORYRevision Release Date Summary1.0 2007/12/27 First releaseTable of Contents1.GENERAL DESCRIPTION (1)2.FEATURES (2)3.SYSTEM APPLICATIONS (2)4.BLOCK DIAGRAMS (3)4.1.F UNCTION B LOCK (3)4.2.A UDIO M IXER P ATH (4)5.PIN ASSIGNMENTS (5)5.1.G REEN P ACKAGE AND V ERSION I DENTIFICATION (5)6.PIN DESCRIPTIONS (6)6.1.D IGITAL I/O P INS (6)6.2.A NALOG I/O P INS (6)6.3.F ILTER/R EFERENCE (7)6.4.P OWER/G ROUND (7)7.FUNCTIONAL DESCRIPTION (8)7.1.P OWER (8)7.2.R ESET (8)7.2.1.Power-On Reset (POR) (8)7.3.C LOCKING (9)7.3.1.Phase-Locked Loop (9)7.3.2.I2C and Stereo I2S (10)7.4.D IGITAL D ATA I NTERFACE (11)7.4.1.Stereo I2S/PCM Interface (11)7.5.A UDIO D ATA P ATH (14)7.5.1.Vref (14)7.5.2.Stereo ADC (14)7.5.3.Stereo DAC (14)7.6.M IXERS (15)7.6.1.Headphone Mixer (15)7.6.2.MONO Mixer (16)7.6.3.Speaker Mixer (16)7.6.4.ADC Record Mixer (17)7.7.A NALOG A UDIO I NPUT P ATH (18)7.7.1.Line Input (18)7.7.2.AUXiliary Input (18)7.7.3.Microphone Input (18)7.8.A NALOG A UDIO O UTPUT D ATA P ATH (19)7.8.1.Speaker Output (19)7.8.2.Headphone Output (20)7.8.3.MONO Output (20)7.9.AVC C ONTROL (21)7.10.H ARDWARE S OUND E FFECTS (23)7.10.1.Equalizer Block (23)7.10.2.Pseudo Stereo and Spatial 3D Sound (23)7.11.I2C C ONTROL I NTERFACE (24)7.11.1.Addressing Setting (24)I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier iii Track ID: JATR-1076-21 Rev. 1.0plete Data Transfer (24)7.12.O DD-A DDRESSED R EGISTER A CCESS (25)7.13.P OWER M ANAGEMENT (25)7.14.GPIO AND J ACK D ETECT F UNCTION (26)7.15.I NTERNAL E VENT S IGNAL I NTERRUPTS (27)7.16.H EADPHONE D EPOP (27)8.MIXER REGISTERS LIST (28)8.1.R EG-00H:R ESET (28)8.2.R EG-02H:S PEAKER O UTPUT V OLUME (28)8.3.R EG-04H:H EADPHONE O UTPUT V OLUME (29)8.4.R EG-06H:MONO_OUT/AUXOUT V OLUME (30)8.5.R EG-08H:AUXIN V OLUME (30)8.6.R EG-0A H:LINE_IN V OLUME (31)8.7.R EG-0C H:STEREO DAC V OLUME (31)8.8.R EG-0E H:MIC V OLUME (32)8.9.R EG-10H:MIC R OUTING C ONTROL (32)8.10.R EG-12H:ADC R ECORD G AIN (33)8.11.R EG-14H:ADC R ECORD M IXER C ONTROL (33)8.12.R EG-16H:A VOL S OFT V OLUME C ONTROL T IME (34)8.13.R EG-1C H:O UTPUT M IXER C ONTROL (34)8.14.R EG-22H:M ICROPHONE C ONTROL (35)8.15.R EG-34H:D IGITAL A UDIO I NTERFACE C ONTROL (35)8.16.R EG-36A H:S TEREO AD/DA C LOCK C ONTROL (36)8.17.R EG-38H:C OMPANDING C ONTROL (37)8.18.R EG-3A H:P OWER M ANAGEMENT A DDITION 1 (37)8.18.1.Headphone Output Amplifier Configuration (38)8.18.2.Auxiliary Output Amplifier Configuration (38)8.19.R EG-3C H:P OWER M ANAGEMENT A DDITION 2 (39)8.20.R EG-3E H:P OWER M ANAGEMENT A DDITION 3 (40)8.21.R EG-40H:A DDITIONAL C ONTROL R EGISTER (41)8.22.R EG-42H:G LOBAL C LOCK C ONTROL R EGISTER (42)8.23.R EG-44H:PLL C ONTROL R EGISTER (42)8.23.1.Reg-44h: PLL Control Register (42)8.23.2.PLL Clock Setting Table for 48K: (Unit: MHz) (43)8.23.3.PLL Clock Setting Table for 44.1K: (Unit: MHz) (43)8.24.R EG-4A H:GPIO_O UTPUT P IN C ONTROL (43)8.25.R EG-4C H:GPIO P IN C ONFIGURATION (44)8.26.R EG-4E H:GPIO P IN P OLARITY (44)8.27.R EG-50H:GPIO P IN S TICKY (45)8.28.R EG-52H:GPIO P IN W AKE-U P (45)8.29.R EG-54H:GPIO P IN S TATUS (46)8.30.R EG-56H:P IN S HARING (46)8.31.R EG-58H:O VER-C URRENT S TATUS (47)8.32.R EG-5A H:J ACK D ETECT C ONTROL R EGISTER (47)8.33.R EG-5E H:MISC C ONTROL (48)8.34.R EG-60H:S TEREO AND S PATIAL E FFECT B LOCK C ONTROL (49)8.35.R EG-62H:EQ C ONTROL (50)8.36.R EG-66H:EQ M ODE C HANGE E NABLE (51)8.37.R EG-68H:AVC C ONTROL (51)8.38.R EG-6A H:I NDEX A DDRESS (52)8.39.R EG-6C H:I NDEX D ATA (52)8.40.I NDEX-00H:EQ B AND-0C OEFFICIENT (LP0: A1) (52)8.41.I NDEX-01H:EQ B AND-0G AIN (LP0:H O) (52)8.42.I NDEX-02H:EQ B AND-1C OEFFICIENT (BP1: A1) (53)I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier iv Track ID: JATR-1076-21 Rev. 1.08.43.I NDEX-03H:EQ B AND-1C OEFFICIENT (BP1: A2) (53)8.44.I NDEX-04H:EQ B AND-1G AIN (BP1:H O) (53)8.45.I NDEX-05H:EQ B AND-2C OEFFICIENT (BP2: A1) (53)8.46.I NDEX-06H:EQ B AND-2C OEFFICIENT (BP2: A2) (54)8.47.I NDEX-07H:EQ B AND-2G AIN (BP2:H O) (54)8.48.I NDEX-08H:EQ B AND-3C OEFFICIENT (BP3: A1) (54)8.49.I NDEX-09H:EQ B AND-3C OEFFICIENT (BP3: A2) (54)8.50.I NDEX-0A H:EQ B AND-3G AIN (BP3:H O) (55)8.51.I NDEX-0B H:EQ B AND-4C OEFFICIENT (HPF: A1) (55)8.52.I NDEX-0C H:EQ B AND-4G AIN (HPF:H O) (55)8.53.I NDEX-11H:EQ I NPUT V OLUME C ONTROL (55)8.54.I NDEX-12H:EQ O UTPUT V OLUME C ONTROL (56)8.55.I NDEX-21H:A UTO V OLUME C ONTROL R EGISTER 1 (56)8.56.I NDEX-22H:A UTO V OLUME C ONTROL R EGISTER 2 (56)8.57.I NDEX-23H:A UTO V OLUME C ONTROL R EGISTER 3 (56)8.58.I NDEX-24H:A UTO V OLUME C ONTROL R EGISTER 4 (57)8.59.I NDEX-25H:A UTO V OLUME C ONTROL R EGISTER 5 (57)8.60.I NDEX-39H:D IGITAL I NTERNAL R EGISTER (57)8.61.I NDEX-46H:C LASS D I NTERNAL R EGISTER (58)8.62.R EG-7C H:VENDOR ID1 (58)8.63.R EG-7E H:VENDOR ID2 (58)9.ELECTRICAL CHARACTERISTICS (59)9.1.DC C HARACTERISTICS (59)9.1.1.Absolute Maximum Ratings (59)9.1.2.Recommended Operating Conditions (59)9.1.3.Static Characteristics (59)9.2.A NALOG P ERFORMANCE C HARACTERISTICS (60)9.3.S IGNAL T IMING (62)9.3.1.I2C Control Interface (62)9.3.2.I2S Master Mode (63)9.3.3.I2S Slave Mode (64)10.APPLICATION CIRCUIT (65)11.MECHANICAL DIMENSIONS (66)12.APPENDIX A: STEREO I2S CLOCK TABLE (68)13.ORDERING INFORMATION (69)I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier v Track ID: JATR-1076-21 Rev. 1.0List of TablesT ABLE 1.D IGITAL I/O P INS (6)T ABLE 2.A NALOG I/O P INS (6)T ABLE 3.F ILTER/R EFERENCE (7)T ABLE 4.P OWER/G ROUND (7)T ABLE 5.R ESET O PERATION (8)T ABLE 6.P OWER-O N R ESET V OLTAGE (8)T ABLE 7.C LOCK S ETTING T ABLE FOR 48K(U NIT:MH Z) (9)T ABLE 8.C LOCK S ETTING T ABLE FOR 44.1K(U NIT:MH Z) (10)T ABLE 9.MONO/AUXOUT O UTPUT S IGNAL T ABLE (20)T ABLE 10.A DDRESSING S ETTING (24)T ABLE 11.W RITE WORD P ROTOCOL (25)T ABLE 12.R EAD WORD P ROTOCOL (25)T ABLE 13.R EG-00H:R ESET (28)T ABLE 14.R EG-02H:S PEAKER O UTPUT V OLUME (28)T ABLE 15.R EG-04H:H EADPHONE O UTPUT V OLUME (29)T ABLE 16.R EG-06H:MONO_OUT/AUXOUT V OLUME (30)T ABLE 17.R EG-08H:AUXIN V OLUME (30)T ABLE 18.R EG-0A H:LINE_IN V OLUME (31)T ABLE 19.R EG-0C H:STEREO DAC V OLUME (31)T ABLE 20.R EG-0E H:MIC V OLUME (32)T ABLE 21.R EG-10H:MIC R OUTING C ONTROL (32)T ABLE 22.R EG-12H:ADC R ECORD G AIN (33)T ABLE 23.R EG-14H:ADC R ECORD M IXER C ONTROL (33)T ABLE 24.R EG-16H:A VOL S OFT V OLUME C ONTROL T IME (34)T ABLE 25.R EG-1C H:O UTPUT M IXER C ONTROL (34)T ABLE 26.R EG-22H:M ICROPHONE C ONTROL (35)T ABLE 27.R EG-34H:A UDIO I NTERFACE (35)T ABLE 28.R EG-36H:S TEREO AD/DA C LOCK C ONTROL (36)T ABLE 29.R EG-38H:C OMPANDING C ONTROL (37)T ABLE 30.R EG-3A H:P OWER M ANAGEMENT A DDITION 1 (37)T ABLE 31.H EADPHONE O UTPUT A MPLIFIER C ONFIGURATION (38)T ABLE 32.A UXILIARY O UTPUT A MPLIFIER C ONFIGURATION (38)T ABLE 33.R EG-3C H:P OWER M ANAGEMENT A DDITION 2 (39)T ABLE 34.R EG-3E H:P OWER M ANAGEMENT A DDITION 3 (40)T ABLE 35.R EG-40H:A DDITIONAL C ONTROL R EGISTER (41)T ABLE 36.R EG-42H:G LOBAL C LOCK C ONTROL R EGISTER (42)T ABLE 37.R EG-44H:PLL C ONTROL R EGISTER (42)T ABLE 38.PLL C LOCK S ETTING T ABLE FOR 48K:(U NIT:MH Z) (43)T ABLE 39.PLL C LOCK S ETTING T ABLE FOR 44.1K:(U NIT:MH Z) (43)T ABLE 40.R EG-4C H:GPIO_O UTPUT P IN C ONTROL (43)T ABLE 41.R EG-4C H:GPIO P IN C ONFIGURATION (44)T ABLE 42.R EG-4E H:GPIO P IN P OLARITY (44)T ABLE 43.R EG-50H:GPIO P IN S TICKY (45)T ABLE 44.R EG-52H:GPIO P IN W AKE-U P (45)T ABLE 45.R EG-54H:GPIO P IN S TATUS (46)T ABLE 46.R EG-56H:P IN S HARING (46)T ABLE 47.R EG-58H:O VER-C URRENT S TATUS (47)T ABLE 48.R EG-5A H:J ACK D ETECT C ONTROL R EGISTER (47)T ABLE 49.R EG-5E H:MISC C ONTROL (48)T ABLE 50.R EG-60H:S TEREO AND S PATIAL E FFECT B LOCK C ONTROL (49)T ABLE 51.R EG-62H:EQ C ONTROL (50)T ABLE 52.R EG-66H:EQ M ODE C HANGE E NABLE (51)I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier vi Track ID: JATR-1076-21 Rev. 1.0T ABLE 53.R EG-68H:AVC C ONTROL (51)T ABLE 54.R EG-6A H:I NDEX A DDRESS (52)T ABLE 55.R EG-6C H:I NDEX D ATA (52)T ABLE 56.I NDEX-00H:EQ B AND-0C OEFFICIENT (LP0: A1) (52)T ABLE 57.I NDEX-01H:EQ B AND-0G AIN (LP0:H O) (52)T ABLE 58.I NDEX-02H:EQ B AND-1C OEFFICIENT (BP1: A1) (53)T ABLE 59.I NDEX-03H:EQ B AND-1C OEFFICIENT (BP1: A2) (53)T ABLE 60.I NDEX-04H:EQ B AND-1G AIN (BP1:H O) (53)T ABLE 61.I NDEX-05H:EQ B AND-2C OEFFICIENT (BP2: A1) (53)T ABLE 62.I NDEX-06H:EQ B AND-2C OEFFICIENT (BP2: A2) (54)T ABLE 63.I NDEX-07H:EQ B AND-2G AIN (BP2:H O) (54)T ABLE 64.I NDEX-08H:EQ B AND-3C OEFFICIENT (BP3: A1) (54)T ABLE 65.I NDEX-09H:EQ B AND-3C OEFFICIENT (BP3: A2) (54)T ABLE 66.I NDEX-0A H:EQ B AND-3G AIN (BP3:H O) (55)T ABLE 67.I NDEX-0B H:EQ B AND-4C OEFFICIENT (HPF: A1) (55)T ABLE 68.I NDEX-0C H:EQ B AND-4G AIN (HPF:H O) (55)T ABLE 69.I NDEX-11H:EQ I NPUT V OLUME C ONTROL (55)T ABLE 70.I NDEX-12H:EQ O UTPUT V OLUME C ONTROL (56)T ABLE 71.I NDEX-21H:A UTO V OLUME C ONTROL R EGISTER 1 (56)T ABLE 72.I NDEX-22H:A UTO V OLUME C ONTROL R EGISTER 2 (56)T ABLE 73.I NDEX-23H:A UTO V OLUME C ONTROL R EGISTER 3 (56)T ABLE 74.I NDEX-24H:A UTO V OLUME C ONTROL R EGISTER 4 (57)T ABLE 75.I NDEX-25H:A UTO V OLUME C ONTROL R EGISTER 5 (57)T ABLE 76.I NDEX-39H:D IGITAL I NTERNAL R EGISTER (57)T ABLE 77.I NDEX-46H:C LASS D I NTERNAL R EGISTER (58)T ABLE 78.R EG-7C H:VENDOR ID1 (58)T ABLE 79.R EG-7E H:VENDOR ID2 (58)T ABLE 80.A BSOLUTE M AXIMUM R ATINGS (59)T ABLE 81.R ECOMMENDED O PERATING C ONDITIONS (59)T ABLE 82.S TATIC C HARACTERISTICS (59)T ABLE 83.A NALOG P ERFORMANCE C HARACTERISTICS (60)T ABLE 84.I2C T IMING (62)T ABLE 85.T IMING OF I2S M ASTER M ODE (63)T ABLE 86.I2S S LAVE M ODE T IMING (64)T ABLE 87.O RDERING I NFORMATION (69)I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier vii Track ID: JATR-1076-21 Rev. 1.0List of FiguresF IGURE 1.B LOCK D IAGRAM (3)F IGURE 2.A UDIO M IXER P ATH (4)F IGURE 3.P IN A SSIGNMENTS (5)F IGURE 4.A UDIO SYSCLK (9)F IGURE 5.PCM M ONO D ATA M ODE A F ORMAT (STEREO_I2S_BCLK_POLARITY_CTRL=0, PCM_MODE_SEL=0) (11)F IGURE 6.PCM M ONO D ATA M ODE A F ORMAT (STEREO_I2S_BCLK_POLARITY_CTRL=1, PCM_MODE_SEL=0) (11)F IGURE 7.PCM M ONO D ATA M ODE B F ORMAT (STEREO_I2S_BCLK_POLARITY_CTRL=0, PCM_MODE_SEL=1) (12)F IGURE 8.PCM S TEREO D ATA M ODE A F ORMAT (STEREO_I2S_BCLK_POLARITY_CTRL=0, PCM_MODE_SEL=0) (12)F IGURE 9.PCM S TEREO D ATA M ODE B F ORMAT (STEREO_I2S_BCLK_POLARITY_CTRL=0, PCM_MODE_SEL=1) (12)F IGURE 10.I2S D ATA F ORMAT (STEREO_I2S_BCLK_POLARITY_CTRL=0) (13)F IGURE 11.L EFT J USTIFIED D ATA F ORMAT (STEREO_I2S_BCLK_POLARITY_CTRL=0) (13)F IGURE 12.R IGHT J USTIFIED D ATA F ORMAT (STEREO_I2S_BCLK_POLARITY_CTRL=0) (13)F IGURE 13.A UTO V OLUME C ONTROL B LOCK D IAGRAM (22)F IGURE 14.AVC B EHAVIOR (22)F IGURE 15.D ATA T RANSFER O VER I2C C ONTROL I NTERFACE (24)F IGURE 16.GPIO I MPLEMENTATION (26)F IGURE 17.J ACK D ETECT AND IRQ L OGIC (27)F IGURE 18.P OWER C ONTROL TO MIC I NPUT (41)F IGURE 19.J ACK-I NSERT-D ETECT P ULL U P R ESISTER I MPLEMENTED VIA AN E XTERNAL C IRCUIT (49)F IGURE 20.I2C C ONTROL I NTERFACE (62)F IGURE 21.T IMING OF I2S M ASTER M ODE (63)F IGURE 22.I2S S LAVE M ODE T IMING (64)I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier viii Track ID: JATR-1076-21 Rev. 1.01.General DescriptionThe ALC5621 is a highly-integrated I2S/PCM interface audio codec with multiple input/output ports and is designed for mobile computing and communications. It provides a Stereo Hi-Fi DAC for playback and Stereo ADC for recording via the I2S/PCM interface.To reduce component count, the device can connect directly to:•MONO or stereo differential analog inputs•LINE_IN stereo Single-Ended analog inputs•AUX_IN Single-Ended analog inputs•Stereo Headphone Output•Single-end stereo configurable to AUXOUT or BTL MONO_OUT•MONO or Stereo Bridge-Tied Load (BTL) speakerMultiple analog input and output pins are provided for seamless integration with analog connected wireless communication devices. Differential input/output connections efficiently reduce noise interference, providing better sound quality. Class AB or Class D amplifiers are easily swapped via simple register configuration, and the 1.3 Watt Mono speaker removes the need for an additional amplifier, further cutting both cost and required board area. Additionally, a flexible hardware 5-band equalizer with configurable gain, bandwidth, and center frequency, enriches the sound experience.The ALC5621 AVDD operates at supply voltages from 2.3V to 3.6V. DVDD operates from 1.71 to 3.6V, and SPKVDD operates from 2.3 to 5V. To extend battery life, each section of the device can be powered down individually under software control. Leakage current in maximum power saving state is less than 10µA.The ALC5621 is available in a 5x5mm ‘Green’ QFN-32 package, making it ideal for use in handheld portable systems.I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 1Track ID: JATR-1076-21 Rev. 1.0I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 2Track ID: JATR-1076-21 Rev. 1.0 2. FeaturesDigital-to-Analog Converter with 92dB SNR and –85dB THD+N Analog-to-Digital Converter with 85dB SNR and –80dB THD+N Two analog stereo single-ended inputs, LINE-IN_L/R and AUXIN_L/R Stereo differential analog microphone inputs, with boost pre-amplifiers (+20/+30/+40dB) BTL (Bridge-Tied Load) Speaker output with on-chip 1.3W speaker driver (SPKVDD=5V, 4.7Ω load with THD+N=40dB) Mono Speaker output supports Class AB or Class D optional Stereo headphone output with on-chip 45mW headphone driver (AVDD=3.3V, 16Ω load) 25mW SE or 75mW BTL Single-Ended differential MONO_OUT configurable to AUXOUT (AVDD=3.3V, 32Ω load)Audio jack insert detection and microphoneswitch detectionPower management and enhanced powersavingSupports digital 5-band equalizer (EQ) Supports digital spatial sound and pseudostereo effectSupports pop noise suppressionInternal PLL can receive wide range of clockinputDigital power supplies from 1.71V to 3.6V;speaker amplifier power supplies from 2.3V to 5VAnalog power and headphone power suppliedfrom 2.3V to 3.6VSupports soft-mute function32-pin QFN package3. System Applications Tablet PC system/Ultra-Mobile PC (UMPC) Personal Digital Assistants (PDA) or PDA Phone Multimedia Phone ApplicationsPortable Navigation Device (PND)Bluetooth HeadphoneI S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier3Track ID: JATR-1076-21 Rev. 1.04.Block Diagrams4.1.Function BlockMICBIASSDAM C L KSCLK SPK_OUT_NSPK_OUT AUXOUT_RAUXOUT_L LINE_IN_R LINE_IN_L MIC1P MIC1N MIC2P MIC2N ALC5621D A C D A TA D C D A TB C L KL R C KAUXIN_L AUXIN_RG P I O /I R QPLL_OUTFigure 1. Block DiagramI S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 4Track ID: JATR-1076-21 Rev. 1.04.2.Audio Mixer Path)10[1210[4]5]L +R+RR+RFigure 2. Audio Mixer PathI S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 5Track ID: JATR-1076-21 Rev. 1.0M I C 1PM I C 2PM I C 1NL I N E _I N _L /J D 1M I C 2NL I N E _I N _R /J D 2L R C KB C L KADCDATDACDAT MCLK DGND DCVDD DBVDD GPIO/IRQ/PLL_OUT SCLKS D AC d e p o pA U X I N _LA U X I N _RA U X O U T _L /M O N O _O U TA U X O U T _R /M O N O _O U T _NS P K _O U TS P K G N DSPKVDD SPK_OUT_NVREF AGND HP_OUT_R HP_OUT_LAVDD MICBIASN C /Figure 3. Pin Assignments5.1. Green Package and Version IdentificationGreen package is indicated by a ‘G’ in the location marked ‘T’ in Figure 3. The version number is shownin the location marked ‘V’.6.1.Digital I/O PinsTable 1. Digital I/O PinsName Type Pin Description Characteristic DefinitionLRCK IO7DigitalAudioSynchronousSignal Master:V OL =0.1*DVDD, V OH =0.9*DVDDSlave: Schmitt triggerBCLK IO8DigitalAudioSerialClock Master:V OL =0.1*DVDD, V OH =0.9*DVDDSlave: Schmitt triggerADCDAT O 9 SerialADCDataOutput V OL =0.1*DVDD, V OH =0.9*DVDD DACDAT I 10 Serial DAC Data Input Schmitt triggerMCLK I 11 Master Clock Input Schmitt triggerGPIO/ IRQ/PLL_OUT IO/O/O15 General Purpose Input And Output/Interrupt Output/PLL OutputGPIO: Input/OutputIRQOUT: OutputPLL_OUT: OutputSCLK I16I2C Clock Schmitt triggerSDA IO17I2C Data Schmitt triggerTotal: 8 Pins6.2.Analog I/O PinsTable 2. Analog I/O PinsName Type Pin Description Characteristic Definition MIC1P I 1 First Mic Positive Input Analog Input (1Vrms) MIC1N I 2 First Mic Negative Input Analog Input (1Vrms) LINE_IN_L/JD1 I 3 Line Input Left Channel/Jack DetectInput_1Analog Input (1Vrms) MIC2P I 4 Second Mic Positive Input Analog Input (1Vrms) MIC2N I 5 Second Mic Negative Input Analog Input (1Vrms) LINE_IN_R/JD2 I 6 Line Input Right Channel/Jack DetectInput_2Analog Input (1Vrms) AUXIN_L I 19 Auxiliary Input Left Channel Analog Input (1Vrms) AUXIN_R I 20 Auxiliary Input Right Channel Analog Input (1Vrms)AUXOUT_L/ MONO_OUT O 21 Positive Mono Output/AuxiliaryOutput Left ChannelAnalog Output (1Vrms)AUXOUT_R/ MONO_OUT_N O 22 Negative Mono Output/AuxiliaryOutput Right ChannelAnalog Output (1Vrms)SPK_OUT O 23 Speaker Output Analog Output (1.5Vrms, SPKVDD=5V) SPK_OUT_N O 25 Negative Speaker Output Analog Output (1.5Vrms, SPKVDD=5V) HP_OUT_R O 29 Headphone Output Right Channel Analog Output (1Vrms)HP_OUT_L O 30 Headphone Output Left Channel Analog Output (1Vrms)Total: 14 PinsI S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 6Track ID: JATR-1076-21 Rev. 1.0I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 7Track ID: JATR-1076-21 Rev. 1.06.3. Filter/ReferenceTable 3. Filter/ReferenceName Type Pin Description Characteristic Definition NC/Cdepop IO 18 NC/De-Pop Capacitor 1µf capacitor to analog ground VREF O 27 Internal Reference V oltage 1µf capacitor to analog ground MICBIAS O 32 MIC BIAS V oltage Output Programmable Analog DC output with 3mA drive Total: 3 Pins6.4. Power/GroundTable 4. Power/Ground Name Type Pin Description Characteristic Definition DGND P 12 Digital GND - DCVDD P 13 Digital VDD 1.71V~3.6V (Core) DBVDD P 14 Digital VDD 1.71V~3.6V (IO Buffer) SPKGND P 24 Analog GND for Speaker Amps - SPKVDD P 26 Analog VDD for Speaker Amps 2.3V~5V AGND P 28 Analog GND - A VDD P 31 Analog VDD 2.3V~3.6V Total: 7 Pins7.Functional Description7.1.PowerThe ALC5621 has many power blocks. SPKVDD operates between 2.3V and 3.0V for weak Class AB amplifiers, and between 3.0V and 5V for strong Class AB amplifiers. The full range is available for ClassD amplifiers.AVDD operates between 2.3V and 3.6V. DBVDD and DCVDD operate between 1.71V and 3.6V. TheALC5621 must handle ratio control between the different power blocks. The power supplier limit conditions are DBVDD ≥ DCVDD, and SPKVDD ≥ AVDD ≥ DCVDD.7.2.ResetThere are two types of reset operation: Power-On Reset (POR) and Register reset.Table 5. Reset OperationReset Type Trigger Condition CODEC ResponsePOR Monitor digital power supply voltage reach V POR Reset all hardware logic and all registers to defaultvalues.Register Reset Write Reg-00h Reset all registers to default values except PLLrelated register7.2.1.Power-On Reset (POR)When powered on, DCVDD passes through the V POR band of ALC5621 (V PORH ~V PORL). A Power-On Reset (POR) will generate an internal reset signal (POR reset ‘LOW’) to reset the whole chip.Table 6. Power-On Reset VoltageSymbol Min Typical Max UnitV POR_ON 1.0 - 1.6 V V POR_OFF- 1.3 - V Note: V POR_OFF must be below V POR_ON.I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 8Track ID: JATR-1076-21 Rev. 1.0I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 9Track ID: JATR-1076-21 Rev. 1.07.3. ClockingThe Audio SYSCLK can be selected from MCLK or PLL. The clock source of PLL can be selected from MCLK or BCLK. The ALC5621 only supports 256Fs or 384Fs as Audio SYSCLK (used as Stereo I 2Sclock).Figure 4. Audio SYSCLK7.3.1. Phase-Locked LoopA Phase-Locked Loop (PLL) is used to provide a flexible input clock from 2.048MHz to 40MHz. Typicalchoices are 2.048MHz, 4.096MHz, and 13MHz. The source of the PLL can be set to MCLK or BCLK by setting pll_sour_sel (Reg42[14]).The source clock of MCLK must be able to drive I 2C, and F/W can setup PLL to output the desired frequency as the SYSCLK.The PLL transmit formula is: F OUT = (MCLK * (N+2)) / ((M+2) * (K+2)) {Typical K=2}Table 7. Clock Setting Table for 48K (Unit: MHz)MCLK N M F VCO K F OUT13 66 7 98.222 2 24.555 3.6864 78 1 98.304 2 24.576 2.048 94 0 98.304 2 24.576 4.096 70 1 98.304 2 24.576 12 80 8 98.4 2 24.6 15.36 81 11 98.068 2 24.517 16 78 11 98.462 2 24.615 19.2 80 14 98.4 2 24.6 19.68 78 14 98.4 2 24.6Table 8. Clock Setting Table for 44.1K (Unit: MHz)MCLK N M F VCO K F OUT13 68 8 91 2 22.753.6864 72 1 90.931 2 22.7332.048 86 0 90.112 2 22.5284.096 64 1 90.112 2 22.52812 66 7 90.667 2 22.66715.36 63 9 90.764 2 22.69116 66 10 90.667 2 22.66719.2 64 12 90.514 2 22.62919.68 67 13 90.528 2 22.632 After a Cold Reset, PLL related Registers are reset to default values, however, they are not reset to default values after a soft-reset (write Reg00).7.3.2.I2C and Stereo I2SThe ALC5621 supports the I2S digital interface for Stereo Audio. The stereo audio digital interface is used to input data to the stereo DAC or output data from the stereo ADC. The Stereo Audio Digital Interface can be configured as Master mode or Slave mode. For the Stereo I2S Interface, the source system clock is always input from MCLK. Refer to section 12 Appendix A: Stereo I2S Clock Table, page 68 for details.Master ModeIn master mode (stereo_i2s_mode_sel=0), BCLK and LRCK are configured as output. Whensel_sysclk=0, MCLK is used as Stereo SYSCLK. When PLL is enabled and sel_sysclk=1, MCLK is suggested to provide frequencies shown in Table 7 Clock Setting Table for 48K (Unit: MHz) and Table 8 Clock Setting Table for 44.1K (Unit: MHz). PLL can be configured to support 44.1K and 48K base sampling rate.Slave ModeIn slave mode (stereo_i2s_mode_sel=1), BCLK/LRCK is configured as input. MCLK should provide the BCLK synchronized clock externally as the Stereo_SYSCLK.Note: The ALC5621 does not support different sample rates between SDAC and ADC in Stereo_I2S/PCM.I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 10Track ID: JATR-1076-21 Rev. 1.0I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 11Track ID: JATR-1076-21 Rev. 1.07.4.Digital Data Interface7.4.1.Stereo I 2S/PCM InterfaceThe stereo I 2S/PCM interface can be configured as Master mode or Slave mode. Four audio data formats are supported: • PCM mode • Left justified mode • Right justified mode • I 2S modeFigure 5. PCM Mono Data Mode A Format (stereo_i2s_bclk_polarity_ctrl=0, pcm_mode_sel=0)Figure 6. PCM Mono Data Mode A Format (stereo_i2s_bclk_polarity_ctrl=1, pcm_mode_sel=0)I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 12Track ID: JATR-1076-21 Rev. 1.0Figure 7. PCM Mono Data Mode B Format (stereo_i2s_bclk_polarity_ctrl=0, pcm_mode_sel=1)Figure 8. PCM Stereo Data Mode A Format (stereo_i2s_bclk_polarity_ctrl=0, pcm_mode_sel=0)Figure 9. PCM Stereo Data Mode B Format (stereo_i2s_bclk_polarity_ctrl=0, pcm_mode_sel=1)I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier13Track ID: JATR-1076-21 Rev. 1.0Figure 10. I 2S Data Format (stereo_i2s_bclk_polarity_ctrl=0)Figure 11. Left Justified Data Format (stereo_i2s_bclk_polarity_ctrl=0)Figure 12. Right Justified Data Format (stereo_i2s_bclk_polarity_ctrl=0)7.5.Audio Data Path7.5.1.VrefVref is the reference voltage for all analog blocks. An external 1µF Capacitor connected to AGND is required. The default status of Vref is enabled after power on. Driver can set Index-39[11]=0b in order to enable power control bit of Reg-3C[13]:pow_vref.7.5.2.Stereo ADCThe stereo ADC is used for recording stereo sound. The sample rate of the stereo ADC is independent of the stereo DAC sample rate. In order to save power, the left and right ADC can be powered down separately by setting adc_l_vol & adc_r_volThe sample rate of the Stereo ADC is the same as the sample rate of Stereo DAC (described in the following section).7.5.3.Stereo DACThe stereo DAC can be configured to different sample rates by driving 256Fs/384Fs into audio SYSCLK with setting divider properly (Reg36). adda_osr is used to control the over sample rate clock divider of the DA filter to 128Fs or 64Fs.Performance of 128Fs is better than 64Fs but with much higher power consumption. Refer to section 12 Appendix A: Stereo I2S Clock Table, page 68 for detailed settings.dac_l_vol & dac_r_vol can be used to control the DAC output volume.I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 14Track ID: JATR-1076-21 Rev. 1.07.6.MixersThe ALC5621 supports four mixers for all audio function requirements:•Headphone mixer for 2 channels•MONO mixer•Speaker mixer•ADC record mixer7.6.1.Headphone MixerThe headphone mixer is used to drive stereo output, including HP_OUT_L/R, SPK_OUT, and MONO_OUT (AUXOUT_L/R). The output of the headphone mixer can be input to the ADC record mixer.The following signals can be mixed into the headphone mixer:•LINE-IN_L/R (Controlled by Reg0A)•PHONEP/N (Controlled by Reg08)•MIC1P/N and MIC2P/N (Controlled by Reg22 & Reg10)•Stereo DAC output (Controlled by Reg0C)•ADC record mixer output (Controlled by Reg12 & Reg14).When the SPK_OUT source is from the HP_mixer, SPK_OUT can be configured to L/R, L+R, and L/LN by setting spk_outn_source. The headphone mixer can be powered down by setting pow_mix_hp_l & pow_mix_hp_r.I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 15Track ID: JATR-1076-21 Rev. 1.0。

MagellanTM 8300 8400 Quick Reference Guide

Magellan TM 8300/8400Quick Reference GuideDatalogic ADC, Inc.959 Terry StreetEugene, OR 97402USATelephone: (541) 683-5700Fax: (541) 345-7140©2006-2013 Datalogic ADC, Inc.An Unpublished Work - All rights reserved. No part of the contents of this documentation or the procedures described therein may be reproduced or transmitted in any form or by any means without prior written permission of Datalogic ADC, Inc. or its subsidiaries or affiliates ("Datalogic" or “Datalogic ADC”). Owners of Datalogic products are hereby granted a non-exclusive, revocable license to reproduce and transmit this documentation for the purchaser's own internal busi-ness purposes. Purchaser shall not remove or alter any proprietary notices, including copyright notices, contained in this documentation and shall ensure that all notices appear on any reproductions of the documentation.Should future revisions of this manual be published, you can acquire printed versions by contacting your Datalogic repre-sentative. Electronic versions may either be downloadable from the Datalogic website () or provided on appropriate media. If you visit our website and would like to make comments or suggestions about this or other Dat-alogic publications, please let us know via the "Contact Datalogic" page.DisclaimerDatalogic has taken reasonable measures to provide information in this manual that is complete and accurate, however, Datalogic reserves the right to change any specification at any time without prior notice.Datalogic and the Datalogic logo are registered trademarks of Datalogic S.p.A. in many countries, including the U.S.A. and the E.U. All other brand and product names may be trademarks of their respective owners.Magellan is a registered trademark of Datalogic ADC, Inc. in many countries, including the U.S.A. and All-Weighs, First-Strike and SurroundScan are registered trademarks of Datalogic ADC, Inc. in the U.S.A. OmegaTek, Produce Rail, Produc-tivity Index Reporting and SmartSentry are all trademarks of Datalogic ADC, Inc.This product may be covered by one or more of the following patents:4603262 • 4639606 • 4652750 • 4672215 • 4699447 • 4709369 • 4749879 • 4786798 • 4792666 • 4794240 • 4798943 • 4799164 • 4820911 • 4845349 • 4861972 • 4861973 • 4866257 • 4868836 • 4879456 • 4939355 • 4939356 • 4943127 • 4963719 • 4971176 • 4971177 • 4991692 • 5001406 • 5015831 • 5019697 • 5019698 • 5086879 • 5115120 • 5144118 • 5146463 • 5179270 • 5198649 • 5200597 • 5202784 • 5208449 • 5210397 • 5212371 • 5212372 • 5214270 • 5229590 • 5231293 • 5232185 • 5233169 • 5235168 • 5237161 • 5237162 • 5239165 • 5247161 • 5256864 • 5258604 • 5258699 • 5260554 • 5274219 • 5296689 • 5298728 • 5311000 • 5327451 • 5329103 • 5330370 • 5347113 • 5347121 • 5371361 • 5382783 • 5386105 • 5389917 • 5410108 • 5420410 • 5422472 • 5426507 • 5438187 • 5440110 • 5440111 • 5446271 • 5446749 • 5448050 • 5463211 • 5475206 • 5475207 • 5479011 • 5481098 • 5491328 • 5493108 • 5504350 • 5508505 • 5512740 • 5541397 • 5552593 • 5557095 • 5563402 • 5565668 • 5576531 • 5581707 • 5594231 • 5594441 • 5598070 • 5602376 • 5608201 • 5608399 • 5612529 • 5629510 • 5635699 • 5641958 • 5646391 • 5661435 • 5664231 • 5666045 • 5671374 • 5675138 • 5682028 • 5686716 • 5696370 • 5703347 • 5705802 • 5714750 • 5717194 • 5723852 • 5750976 • 5767502 • 5770847 • 5786581 • 5786585 • 5787103 • 5789732 • 5796222 • 5804809 • 5814803 • 5814804 • 5821721 • 5822343 • 5825009 • 5834708 • 5834750 • 5837983 • 5837988 • 5852286 • 5864129 • 5869827 • 5874722 • 5883370 • 5905249 • 5907147 • 5923023 • 5925868 • 5929421 • 5945670 • 5959284 • 5962838 • 5979769 • 6000619 • 6006991 • 6012639 • 6016135 • 6024284 • 6041374 • 6042012 • 6045044 • 6047889 • 6047894 • 6056198 • 6065676 • 6069696 • 6073849 • 6073851 • 6094288 • 6112993 • 6129279 • 6129282 • 6134039 • 6142376 • 6152368 • 6152372 • 6155488 • 6166375 • 6169614 • 6173894 • 6176429 • 6188500 • 6189784 • 6213397 • 6223986 • 6230975 • 6230976 • 6244510 • 6259545 • 6260763 • 6266175 • 6273336 • 6276605 • 6279829 • 6290134 • 6290135 • 6293467 • 6303927 • 6311895 • 6318634 • 6328216 • 6332576 • 6332577 • 6343741 • 6454168 • 6478224 • 6568598 • 6578765 • 6705527 • 6857567 • 6974084 • 6991169 • 7051940 • 7170414 • 7172123 • 7201322 • 7204422 • 7215493 • 7224540 • 7234641 • 7243850 • 7374092 • 7407096 • 7490770 • 7495564 • 7506816 • 7527198 • 7527207 • 7537166 • 7562817 • 601 26 118.6 • AU703547 • D312631 • D313590 • D320011 • D320012 • D323492 • D330707 • D330708 • D349109 • D350127 • D350735 • D351149 • D351150 • D352936 • D352937 • D352938 • D352939 • D358588 • D361565 • D372234 • D374630 • D374869 • D375493 • D376357 • D377345 • D377346 • D377347 • D377348 • D388075 • D446524 • D606544 •EP0256296 • EP0260155 •EP0260156 • EP0295936 • EP0325469 • EP0349770 • EP0368254 • EP0442215 • EP0498366 • EP0531645 • EP0663643 • EP0698251 • EP01330772 • EP870761 • GB2252333 • GB2284086 • GB2301691 • GB2304954 • GB2307093 • GB2308267 • GB2308678 • GB2319103 • GB2333163 • GB2343079 • GB2344486 • GB2345568 • GB2354340 • ISR107546 • ISR118507 • ISR118508 • JP1962823 • JP1971216 •JP2513442 • JP2732459 • JP2829331 • JP2953593 • JP2964278 • MEX185552 • MEX187245 • RE37166 • RE40071Additional patents pendingDATALOGIC ADC, INC. MAGELLAN TM END USER LICENSE AGREEMENTNotice to End User: The Datalogic Product you have acquired contains embedded Software, which is integral to the product's operation. This Soft-ware is being provided to you under license, subject to the terms and conditions of this Agreement. If you use the Datalogic Product, you will be deemed to have accepted the terms and conditions of this Agreement. If you do not intend to be bound to the terms of this Agreement, Datalogic is not willing to license the Software to you, you may not use the Datalogic Product or the Software, and you must contact the party from whom you acquired the Datalogic Product for instructions.This End User Software License Agreement ("Agreement") is a legally binding agreement governing the licensing of the Software and Documentation by Data-logic Holdings, Inc. and its subsidiaries and affiliates ("Datalogic") to the entity or person who has purchased or otherwise acquired a Datalogic Product ("End User"). For purposes of this Agreement, any software that is associated with a separate end-user license agreement is licensed to you under the terms of that license agreement. Datalogic and End User hereby agree as follows:1. Definitions.1.1 "Documentation" means materials such as user's guides, program reference guides, quick reference guides, manuals, or similar materials associatedwith or related to the Datalogic Product, whether in printed, "online", or other form.1.2 "Proprietary Information" means: (a) source code, object code, software, documentation, and any related internal design, system design, data basedesign, algorithms, technology, technical data or information, implementation techniques, and trade secrets related to the Software, (b) any other trade secrets marked appropriately or identified as proprietary or confidential, and (c) any information that End User, under the circumstances, should recog-nize as confidential. Proprietary Information does not include any information that the receiving party can establish was (1) in the public domain, (2) already in the receiving party's possession or rightfully known prior to receipt, (3) rightfully learned from a third party not in violation of any other's propri-etary rights, or (4) independently developed without access to Proprietary Information.1.3 "Datalogic Product" means the Datalogic Magellan TM 800i, Magellan TM 1000i series, Magellan TM 1100i series, Magellan TM 1400i series, Magellan TM2200VS series, Magellan TM 2300HS series, Magellan TM 3200VSi series, Magellan TM 3300HSi series, Magellan TM 8100 series, Magellan TM 8200 series, Magellan TM 8300 series, Magellan TM 8400 series, Magellan TM 8500 series, Magellan TM 9500 series, Magellan TM 9800i series and/or Magellan SL TM series scanner and/or scanner/scale product, including all embedded Software in and all Documentation related to such product, which has been pur-chased or otherwise acquired by End User, whether obtained directly or indirectly from Datalogic.1.4 "Software" means any software or computer programs of Datalogic or its third party licensors in machine readable form which is embedded in the Data-logic Product, whether obtained directly or indirectly from Datalogic, including any replacement, update, upgrade, enhancement or modification.2. Scope Of License Granted.2.1 Datalogic grants to End User a non-exclusive, non-transferable, perpetual license to use the Software, solely on the Datalogic Product in which it isembedded ("designated Datalogic Product"), in machine-readable form only, solely for End User's internal business purposes. This Agreement does not convey ownership of the Software to End User. Title to the Software shall be and remain with Datalogic or the third party from whom Datalogic has obtained a licensed right. As used in this Agreement, the term "purchase" or its equivalents when applied to the Software shall mean "acquire under license." End User is not entitled to receipt or use of the source code to any Software.2.2 End User shall not copy, modify, decompile, disassemble, reverse engineer, or otherwise reproduce or remanufacture the Software, whether modified orunmodified, nor sell, assign, sublicense, distribute, lend, rent, give, or otherwise transfer the Software to any other person or organization, for purposes other than as expressly provided in this Agreement, without Datalogic's prior written consent.3. Transfers, Support.3.1 Any copying, installing, reproduction, remanufacture, reverse engineering, electronic transfer, or other use of the Software on other than the designatedDatalogic Product will be a material breach of this Agreement. However, Datalogic may elect not to terminate this Agreement or the granted licenses, but instead may elect to notify End User that End User is deemed to have ordered and accepted a license for each breaching use. End User shall pay Data-logic the applicable list price for such licenses as of the date of such breach.3.2 End User shall not sell, assign, sublicense, distribute, lend, rent, give, or otherwise transfer the Datalogic Product to any third party unless such third partyagrees with Datalogic in writing to be bound by the terms and conditions of this Agreement. Any such transfer of the Datalogic Product absent such agreement shall be null and void.3.3 End User may obtain support for Software from Datalogic at Datalogic's standard support fees and under Datalogic's standard support terms and condi-tions in effect at the time the support is requested.4. Intellectual Property.End User acknowledges that the Software constitutes valuable trade secrets of Datalogic or Datalogic's third party licensors and that the Software is protected by intellectual property laws and treaties. The license set forth in this Agreement does not transfer to End User any ownership of Datalogic's or its third party licensors' copyrights, patents, trademarks, service marks, trade secrets, or other intellectual property rights and End User shall have no right to commence any legal actions to obtain such rights. End User shall not remove, modify, or take any other action that would obscure any copyright, trademark, patent marking, or other intellectual property notices contained in or on the Datalogic Product.5. Proprietary Information.5.1 End User acknowledges that Proprietary Information is the confidential, proprietary, and trade secret property of Datalogic and Datalogic's third partylicensors and End User acquires no right or interest in any Proprietary Information.5.2 End User shall not disclose, provide, or otherwise make available the Proprietary Information of Datalogic or its third party licensors to any person otherthan End User's authorized employees or agents who are under confidentiality agreement, and End User shall not use the Proprietary Information other than in conjunction with use of the Datalogic Product exclusively for End User's internal business purposes. End User shall take steps to protect the Pro-prietary Information no less securely than if it were End User's own intellectual property.5.3 The provisions of this Proprietary Information Section shall survive and continue for five (5) years after the termination of this Agreement.6. Limited Warranty.6.1 Datalogic warrants that, under normal use and operation, the Datalogic Product will conform substantially to the applicable Documentation for the periodspecified in the Documentation. During this period, for all reproducible nonconformities for which Datalogic has been given written notice, Datalogic will use commercially reasonable efforts to remedy nonconformities verified by Datalogic. End User agrees to supply Datalogic with all reasonably requested information and assistance necessary to help Datalogic in remedying such nonconformities. For all defects reported to Datalogic within the warranty period, Datalogic's liability is limited to providing End User with one copy of corrections or responding to End User's problem reports according to Data-logic's standard assistance practices. Datalogic does not warrant that the product will meet End User's requirements or that use of the product will be uninterrupted or error free, or that Datalogic's remedial efforts will correct any nonconformance. This limited warranty does not cover any product that has been subjected to damage or abuse, whether intentionally, accidentally, or by neglect, or to unauthorized repair or unauthorized installation, and shall be void if End User modifies the product, uses the product in any manner other than as established in the Documentation, or if End User breaches any ofQuick Reference Guide ithe provisions of this Agreement.6.2 EXCEPT AS PROVIDED IN THIS AGREEMENT, THE DAT ALOGIC PRODUCT IS PROVIDED "AS IS" AND DAT ALOGIC MAKES NO WARRANTIESOF ANY KIND, EXPRESS OR IMPL IED, WRITTEN OR ORAL, WITH RESPECT TO THE PRODUCT, AND SPECIFICAL LY DISCL AIMS THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.7. Infringement.7.1 Datalogic will defend End User against any claim in a lawsuit that the Datalogic Product furnished hereunder infringe a United States patent or copy-right of a third party and Datalogic will pay any damages finally awarded against End User by a court of competent jurisdiction that are attributable to such claim or will pay End User's part of any settlement that is attributable to such claim, provided, that 1) End User notifies Datalogic promptly in writ-ing of the claim, 2) Datalogic controls the defense or settlement of the claim, and 3) End User cooperates fully with Datalogic in such defense or settle-ment. All notices of a claim should be sent to Datalogic Holdings, Inc., Legal Department, 959 Terry Street, Eugene, OR 97402.7.2 In the defense or settlement of any such claim, Datalogic may, at its option, 1) procure for End User the right to continue using the Datalogic Product,2) modify the Datalogic Product so that it becomes non-infringing, 3) replace the Datalogic Product with an equivalent product not subject to suchclaim, or 4) provide End User an opportunity to return the Datalogic Product and receive a refund of the purchase price paid, less a reasonable allow-ance for use.7.3 Datalogic shall have no liability to End User for claims of infringement based upon 1) the use of any Datalogic Product in combination with any productwhich Datalogic has not either furnished or authorized for use with such Datalogic Product 2) the use of any Datalogic Product designed, manufac-tured, or modified to the specifications of End User, or 3) End User's modification of the Datalogic Product without written authorization from Datalogic.7.4 THE FOREGOING ST ATES DAT ALOGIC'S COMPLETE AND ENTIRE OBLIGATION CONCERNING CLAIMS OF PATENT, COPYRIGHT, OR OTHERINTEL L ECTUAL PROPERTY INFRINGEMENT, CANCEL S AND SUPERSEDES ANY PRIOR AGREEMENTS, WHETHER ORAL OR WRITTEN, BETWEEN THE PARTIES CONCERNING SUCH CLAIMS, AND WILL NOT BE MODIFIED OR AMENDED BY ANY PAST, CONTEMPORANEOUS, OR FUTURE AGREEMENTS OR DEALINGS BETWEEN THE PARTIES, WHETHER ORAL OR WRITTEN, EXCEPT AS SET FORTH IN A FUTURE WRITING SIGNED BY BOTH PARTIES.8. Limitation Of Liability.EXCEPT AS PROVIDED IN SECTION 7, DAT ALOGIC SHALL NOT BE LIABLE FOR ANY CLAIMS AGAINST END USER BY ANY OTHER PARTY. IN NO EVENT SHALL DAT ALOGIC'S LIABILITY FOR DAMAGES, IF ANY, WHETHER BASED UPON CONTRACT, TORT (INCLUDING NEGLIGENCE), PROD-UCT LIABILITY, STRICT LIABILITY, WARRANTY, OR ANY OTHER BASIS, EXCEED THE PRICE OR FEE P AID BY END USER FOR THE DA T ALOGIC PRODUCT. UNDER NO CIRCUMST ANCES SHALL DAT ALOGIC BE LIABLE TO END USER OR ANY THIRD P ARTY FOR LOST PROFITS, LOST DAT A, INTERRUPTION OF BUSINESS OR SERVICE, OR FOR ANY OTHER SPECIAL, CONSEQUENTIAL, CONTINGENT, INDIRECT, INCIDENT AL, PUNITIVE, EXEMPLARY, OR OTHER SIMILAR DAMAGES, EVEN IF DA T ALOGIC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.9. Government Restricted Rights; International Use.9.1 Use, duplication, or disclosure of the Software by the U.S. Government is subject to the restrictions for computer software developed at privateexpense as set forth in the U.S. Federal Acquisition Regulations at FAR 52.227-14(g), or 52.227-19 or in the Rights in T echnical Data and Computer Software clause at DFARS 252.227-7013(c)(1)(ii), whichever is applicable.9.2 If End User is using the Datalogic Product outside of the United States, End User must comply with the applicable local laws of the country in which theDatalogic Product is used, with U.S. export control laws, and with the English language version of this Agreement. The provisions of the "United Nations Convention on International Sale of Goods" shall not apply to this Agreement.10. Termination.10.1 Either party may terminate this Agreement or any license granted under this Agreement at any time upon written notice if the other party breaches anyprovision of this Agreement.10.2 Upon termination of this Agreement, End User immediately shall cease using any non-embedded software and shall return to Datalogic or destroy allnon-embedded software covered by this Agreement, and shall furnish Datalogic with a certificate of compliance with this provision signed by an officer or authorized representative of End User. For embedded software, End User agrees to sign a waiver prepared by Datalogic concerning further use of the embedded Software. End User's resumed or continued use of the embedded Software after termination shall constitute End User's agreement to be bound by the terms and conditions of this Agreement for such use.11. General Provisions.11.1 Entire Agreement; Amendment. This document contains the entire agreement between the parties relating to the licensing of the Software and super-sedes all prior or contemporaneous agreements, written or oral, between the parties concerning the licensing of the Software. This Agreement may not be changed, amended, or modified except by written document signed by Datalogic.11.2 Notice. All notices required or authorized under this Agreement shall be given in writing, and shall be effective when received, with evidence of receipt.Notices to Datalogic shall be sent to the attention of Contract Administration, Datalogic Holdings, Inc., 959 T erry Street, Eugene, OR 97402, or such other address as may be specified by Datalogic in writing.11.3 Waiver. A party's failure to enforce any of the terms and conditions of this Agreement shall not prevent the party's later enforcement of such terms andconditions.11.4Governing Law; Venue: This Agreement and the rights of the parties hereunder shall be governed by and construed in accordance with the laws of theState of Oregon U.S.A, without regard to the rules governing conflicts of law. The state or federal courts of the State of Oregon located in either Mult-nomah or Lane counties shall have exclusive jurisdiction over all matters regarding this Agreement, except that Datalogic shall have the right, at its absolute discretion, to initiate proceedings in the courts of any other state, country, or territory in which End User resides, or in which any of End User's assets are located.11.5 Attorneys’ Fees. In the event an action is brought to enforce the terms and conditions of this Agreement, the prevailing party shall be entitled to reason-able attorneys' fees, both at trial and on appeal.- END -ii Magellan® 8300/8400Quick Reference Guide1Quick ReferenceThe object of this manual is to provide general operational information for the user. For more product details, including installation, set-up, programming and advanced user information, reference the Product Reference Guide (PRG), which is available for viewing and download from the website listed on the back cover of this manual.Controls and IndicatorsThe control panel consists of an indicator LED and two push buttons as shown in Figure 1. The bottom-most button also serves as an indicator LED for scale func-tions (scale models ONLY). The unit also includes a speaker (beeper) which can be configured to sound indications of scanning and weighing activities. Refer to LED and Beeper Indications for more information about the functions of the push buttons and indicators.Figure 1. Controls and IndicatorsSpea (BeePortScale Z Button & LVolume/TBu LED IndicatorPower Supply Array The scanner may require either a Listed Class 2 or Listed LPS powersource which supplies power directly to the unit. It is sometimes pos-sible for a scanner to receive power directly from the terminal(P.O.T.). See the current product data sheet for more informationabout P.O.T.Scanning ItemsPush or slide items through the 360° scan zone (shown here) in either a left-to-right or right-to-left motion. The scanner has the ability to “see” a bar codelocated on any side (left, right, front, back or bottom) of a product, so there’srarely a need to reorient an item in order to scan it.For best scanning results...•Move items through the scan zone in their natural orientation. It’s notnecessary to reorient the bar code toward either the horizontal or verticalscan window.•Sliding or pushing items rather than picking them up will avoid thegripping, twisting and rotating movements that can cause repetitivemotion injuries to hands and wrists. The strain of lifting potentiallythousands of pounds per day can also be relieved using this technique.2Magellan TM 8300/8400With the 360° scan pattern and advanced FirstStrike® decoding software, theMagellan® 8300/8400 can read most hard-to-read codes quickly and withoutexcess orientation.Weighing Items Using the All-Weighs® PlatterItems to be weighed can be placed anywhere on the L-shaped All-Weighs® platter(weigh platter) surface. Oversized items can even be accurately weighed whileleaned against the center of its vertical section as shown.The optional, raised Produce Bar or Produce Rail™ features conveniently ensurethat items do not rest on the counter or other non-weighing surfaces. Withweighed items in place, enter PLU (Price Look-Up) data as described in the POSinstructions for your system. Weight data will be displayed on the Remote ScaleDisplay and/or the host display.with the All-Weighs® PlatterFigure 3. Weighing ItemsLED IndicatorsThe scanner LED (top-most) indicates scanner status, and the scale button/LED(scale models ONLY) is used to show scale status. See Table 1 for a listing of LEDindications.Quick Reference Guide 3Table 1. Scanner and Scale Indicationsa.Certain functions of the Green and Y ellow LEDs are selectable to be enabled or disabled. Y our scannermay not be programmed to display all indications.4Magellan TM 8300/8400Volume/Tone Push ButtonThe Volume/Tone Push Button also performs multiple functions depend-ing upon the duration of time it is pressed:Table 2. Volume/Tone Push Button FunctionsPRESSDURATIONFUNCTION COMMENTMomentary (when scanner is in Sleep Mode)Wakes scanner fromSleep ModeAlternatively, the scanner can be awakened by:- Moving an object through the scan zone.- A weight change on the scale.- Scanning with an attached auxiliary scanner.Momentary (whenscanner is in Normal Operating Mode)Increments volumePress the push button momentarily to increase speaker vol-ume. When the loudest volume is reached, a repeated pressof the push button cycles volume back to the lowest setting,then volume increases on subsequent press(es). Four vol-ume levels are available.Hold, then releasewhen the beeper sounds Increments tonePress the push button for approximately 2 seconds, thenrelease. Each time this is done, the beeper will sound at oneof three tones. Stop when the desired tone (high, medium orlow) is sounded.4 Seconds Scanner DiagnosticsMode aThis mode allows system support personnel to troubleshootproblems with the scanner. Generally diagnostics are initiatedafter noting a Field Replaceable Unit (FRU) Warning (seeTable 1). Cycle power to exit Scanner Diagnostics Mode.8 Seconds Resets Scanner b Only system support personnel should perform a reset.a.By standard default, this function is normally disabled to prevent accidental activation by users.ers should not perform scanner resets except under the direction of trained systems support person-nel.Quick Reference Guide 56Magellan TM 8300/8400Scale Zero Push ButtonThe Scale Zero Push Button is used for two functions as described in Table 3. This button has no function on “scanner-only” models.Table 3. Scale Zero Push Button FunctionsEAS-Enabled SystemsElectronic Article Surveillance (EAS) systems are aftermarket options, and are installed by either Sensormatic ® or Checkpoint ® technicians at your site depending upon which EAS product package is purchased to use with your scanner.Once the system is activated, EAS security tags are automatically deactivated by passing items over the EAS antenna located beneath the scanner’s platter.PRESS DURATIONFUNCTION COMMENTMomentary Zero ScaleWhen programmed to do so, the yellow Scale LED should be lit when no weight is on the scale, indicating scale at zero. If it is not, press the switch to zero the scale. The unit will sound a “click” upon pressing the button.Momentary (when the scale’s primary indication shows an under zero condition)Scale power cycleWhen programmed to do so, and when certain conditions are met, pressing this button will initiate a scale power cycle. When the scale zero button is pushed and the weight on the scale is close to zero, the scale will zero normally like the zero scale function above. Otherwise, the scale will go through a power cycle. If the scale is able to find zero after the power cycle, the scale will perform normally. Otherwise, the scale’s primary indication will display a non-weight indication.4 SecondsScale Diag-nostics Mode aThis mode allows system support personnel to troubleshoot problems with the scale. Cycle power to exit Scale Diagnostics Mode.a.Diagnostics Mode is meant for use by trained systems support personnel. Users should not need to ini-tiate this function under normal circumstances.NOTE。

AT88SC0104CA-SU_datasheet

1.Features•One of a Family of Devices with User Memories from 1-Kbit to 8-Kbits •1-Kbit (128-byte) EEPROM User Memory–Four 256-bit (32-byte) Zones –Self-timed Write Cycle–Single Byte or 16-byte Page Write Mode–Programmable Access Rights for Each Zone •2-Kbit Configuration Zone–37-byte OTP Area for User-defined Codes–160-byte Area for User-defined Keys and Passwords •High Security Features–64-bit Mutual Authentication Protocol (Under License of ELVA)–Cryptographic Message Authentication Codes (MAC)–Stream Encryption–Four Key Sets for Authentication and Encryption –Eight Sets of Two 24-bit Passwords –Anti-Tearing Function–Voltage and Frequency Monitors •Smart Card Features–ISO 7816 Class B (3V) Operation–ISO 7816-3 Asynchronous T=0 Protocol (Gemplus ® Patent)–Multiple Zones, Key Sets and Passwords for Multi-application Use –Synchronous 2-wire Serial Interface for Faster Device Initialization –Programmable 8-byte Answer-To-Reset Register –ISO 7816-2 Compliant Modules •Embedded Application Features–Low Voltage Operation: 2.7V – 3.6V–Secure Nonvolatile Storage for Sensitive System or User Information –2-wire Serial Interface–1.0 MHz Compatibility for Fast Operation –Standard 8-lead Plastic Packages–Same Pin Configuration as AT24CXXX Serial EEPROM in SOIC and PDIP Packages •High Reliability–Endurance: 100,000 Cycles –Data Retention: 10 years –ESD Protection: 2,000V minTable 1-1.PadsPad Description ISO Module“SOIC, PDIP”TSSOP VCC Supply Voltage C188GND GroundC541SCL/CLK Serial Clock Input C366SDA/IO Serial Data Input/Output C753RSTReset InputC2NCNCCryptoMemory AT88SC0104CASummary5200AS–CRYPT–7/0825200AS–CRYPT–7/08AT88SC0104CA2.DescriptionThe AT88SC0104CA member of the CryptoMemory ® family is a high-performance secure mem-ory providing 1 Kbit of user memory with advanced security and cryptographic features built in.The user memory is divided into four 32-byte zones, each of which may be individually set with different security access rights or effectively combined together to provide space for 1 to 4 data files. The AT88SC0104CA features an enhanced command set that allows direct communica-tion with microcontroller hardware 2-Wire interface thereby allowing for faster firmware development with reduced code space requirements.3.Smart Card ApplicationsThe AT88SC0104CA provides high security, low cost, and ease of implementation without the need for a microprocessor operating system. The embedded cryptographic engine provides for dynamic, symmetric-mutual authentication between the device and host, as well as performing stream encryption for all data and passwords exchanged between the device and host. Up to four unique key sets may be used for these operations. The AT88SC0104CA offers the ability to communicate with virtually any smart card reader using the asynchronous T = 0 protocol (Gem-plus Patent) defined in ISO 7816-3.4.Embedded ApplicationsThrough dynamic, symmetric-mutual authentication, data encryption, and the use of crypto-graphic Message Authentication Codes (MAC), the AT88SC0104CA provides a secure place for storage of sensitive information within a system. With its tamper detection circuits, this informa-tion remains safe even under attack. A 2-wire serial interface running at speeds up to 1.0 MHz provides fast and efficient communications with up to 15 individually addressable devices. The AT88SC0104CA is available in industry standard 8-lead packages with the same familiar pin configuration as AT24CXXX serial EEPROM devices.Note:Does not apply to TSSOP pinout.35200AS–CRYPT–7/08AT88SC0104CAFigure 4-1.Block Diagram5.Pin Descriptions5.1Supply Voltage (VCC)The V CC input is a 2.7V to 3.6V positive voltage supplied by the host.5.2Clock (SCL/CLK)When using the asynchronous T = 0 protocol, the CLK (SCL) input provides the device with a carrier frequency f . The nominal length of one bit emitted on I/O is defined as an “elementary time unit” (ETU) and is equal to 372/f .When using the synchronous protocol, data clocking is done on the positive edge of the clock when writing to the device and on the negative edge of the clock when reading from the device.5.3Reset (RST)The AT88SC0104CA provides an ISO 7816-3 compliant asynchronous Answer-To-Reset (ATR)sequence. Upon activation of the reset sequence, the device outputs bytes contained in the 64-bit Answer-To-Reset register. An internal pull-up on the RST input pad allows the device to oper-ate in synchronous mode without bonding RST. The AT88SC0104CA does not support an Answer-To-Reset sequence in the synchronous mode of operation.5.4Serial Data (SDA/IO)The SDA/IO pin is bidirectional for serial data transfer. This pin is open-drain driven and may be wired with any number of other open-drain or open-collector devices. An external pull-up resistor should be connected between SDA/IO and V CC . The value of this resistor and the system capac-itance loading the SDA/IO bus will determine the rise time of SDA/IO. This rise time will determine the maximum frequency during read operations. Low value pull-up resistors will allow higher frequency operations while drawing higher average power supply current. SDA/IO infor-mation applies to both asynchronous and synchronous protocols.45200AS–CRYPT–7/08AT88SC0104CA6.Absolute Maximum RatingsStresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the oper-ational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability.Absolute Maximum RatingsOperating T emperature.....................................-40⋅C to +85⋅C Storage T emperature ..........................................−65⋅C to +150⋅C Voltage on Any Pinwith Respect to Ground ....................................−0.7 to V cc +0.7V Maximum Operating Voltage.............................................6.0V DC Output Current........................................................5.0 mATable 6-1.DC Characteristics Applicable over recommended operating range from V CC = +2.7 to 3.6V, T AC = -40⋅C to +85⋅C(unless otherwise noted)Symbol Parameter Test ConditionMin TypMax Units V CC Supply Voltage 2.73.6V I CC Supply Current Async READ at 3.57MHz 5mA I CC Supply Current Async WRITE at 3.57MHz 5mA I CC Supply Current Synch READ at 1MHz 5mA I CC Supply Current Synch WRITE at 1MHz 5mA I SB Standby CurrentVIN = VCC or GND100uA V IL SDA/IO Input Low Voltage 0VCC x 0.2V V IL CLK Input Low Voltage 0VCC x 0.2V V IL RST Input Low Voltage 0VCC x 0.2V V IH SDA/IO Input High Voltage VCC x 0.7VCC V V IH SCL/CLK Input High Voltage VCC x 0.7VCC V V IH RST Input High Voltage VCC x 0.7VCC V I IL SDA/IO Input Low Current 0 < VIL < VCC x 0.1515uA I IL SCL/CLK Input Low Current 0 < VIL < VCC x 0.1515uA I IL RST Input Low Current 0 < VIL < VCC x 0.1550uA I IH SDA/IO Input High Current VCC x 0.7 < VIH < VCC 20uA I IH SCL/CLK Input High Current VCC x 0.7 < VIH < VCC 100uA I IH RST Input High Current VCC x 0.7 < VIH < VCC 150uA V OH SDA/IO Output High Voltage 20K ohm external pull-up VCC x 0.7VCC V V OL SDA/IO Output Low Voltage IOL = 1mA 0VCC x 0.15V I OH SDA/IO Output High Current VOH 20uA I OLSDA/IO Output Low CurrentVOL10mA55200AS–CRYPT–7/08AT88SC0104CA7.Device Operations for Synchronous Protocols7.1Clock and Data TransitionsThe SDA pin is normally pulled high with an external device. Data on the SDA pin may changeonly during SCL low time periods (see Figure 7-3 on page 6). Data changes during SCL high periods will indicate a start or stop condition as defined below.7.1.1Start ConditionA high-to-low transition of SDA with SCL high defines a START condition which must precede all commands (see Figure 7-4 on page 7).7.1.2Stop ConditionA low-to-high transition of SDA with SCL high defines a STOP condition. After a read sequence,the STOP condition will place the EEPROM in a standby power mode (see Figure 7-4 on page 7).7.1.3ACKNOWLEDGEAll addresses and data words are serially transmitted to and from the EEPROM in 8-bit words.The EEPROM sends a zero to acknowledge that it has received each word. This happens dur-ing the ninth clock cycle (see Figure 7-5 on page 7).Table 6-2.AC CharacteristicsApplicable over recommended operating range from V CC = +2.7 to 3.6V , T AC = -40⋅C to +85⋅C, CL = 30pF (unless otherwise noted)ParameterMin Max Units f CLKAsync Clock Frequency14MHz f CLK SynchClock Frequency 01MHz Clock Duty cycle4060%t R “Rise Time - SDA/IO, RST”1uS t F “Fall Time - SDA/IO, RST”1uS t R Rise Time - SCL/CLK 9% x period uS t F Fall Time - SCL/CLK 9% x perioduS t AA Clock Low to Data Out Valid 250nS t HD.ST A Start Hold Time 200nS t SU.ST A Start Set-up Time 200nS t HD.DA T Data In Hold Time 10nS t SU.DAT Data In Set-up Time 100nS t SU.STO Stop Set-up Time 200nS t DH Data Out Hold Time 20nS t WRWrite Cycle Time5mS65200AS–CRYPT–7/08AT88SC0104CA7.2Memory ResetAfter an interruption in communication due protocol errors, power loss or any reason, perform "Acknowledge Polling" to properly recover from the condition. Acknowledge polling consists of sending a start condition followed by a valid CryptoMemory command byte and determining if the device responded with an ACKNOWLEDGE.Figure 7-1.Bus Time for 2-Wire Serial Communications. SCL: Serial Clock, SDA: Serial Data I/OFigure 7-2.Write Cycle Timing. SCL: Serial Clock, SDA: Serial Data I/ONote:The Write Cycle time t wr is the time from a valid stop condition of a write sequence to the end of the internal clear/write cycle.Figure 7-3.Data Validity75200AS–CRYPT–7/08AT88SC0104CAFigure 7-4.START and STOP DefinitionsFigure 7-5.Output Acknowledge85200AS–CRYPT–7/08AT88SC0104CA8.Device Architecture8.1User ZonesThe EEPROM user memory is divided into 4 zones of 256 bits each. Multiple zones allow for storage of different types of data or files in different zones. Access to user zones is permitted only after meeting proper security requirements. These security requirements are user definable in the configuration memory during device personalization. If the same security requirements are selected for multiple zones, then these zones may effectively be accessed as one larger zone.Figure 8-1.User ZonesZONE$0$1$2$3$4$5$6$7User 0$00-32 Bytes-$18User 1$00-32 Bytes-$18User 2$00-32 Bytes-$18User 3$00-32 Bytes-$1895200AS–CRYPT–7/08AT88SC0104CA9.Control LogicAccess to the user zones occur only through the control logic built into the device. This logic is configurable through access registers, key registers and keys programmed into the configuration memory during device personalization. Also implemented in the control logic is a cryptographic engine for performing the various higher-level security functions of the device.10.Configuration MemoryThe configuration memory consists of 2048 bits of EEPROM memory used for storage of pass-words, keys, codes, and also used for definition of security access rights for the user zones.Access rights to the configuration memory are defined in the control logic and are not alterable by the user after completion of personalization.Figure 10-1.Configuration Memory$0$1$2$3$4$5$6$7$00Answer To ResetIdentification $08Fab Code MTZCard Manufacturer Code$10Lot History CodeRead Only$18DCR Identification Number NcAccess Control$20AR0PR0AR1PR1AR2PR2AR3PR3$28Reserved$30$38$40Issuer Code$48$50For Authentication and Encryption use Cryptography$58$60$68$70$78$80$88$90For Authentication and Encryption use Secret$98$A0$A8$B0P ACWrite 0P AC Read 0Password$B8P AC Write 1P AC Read 1$C0P AC Write 2P AC Read 2$C8P AC Write 3P AC Read 3$D0P AC Write 4P AC Read 4$D8P AC Write 5P AC Read 5$E0P AC Write 6P AC Read 6$E8P AC Write 7P ACRead 7$F0ReservedForbidden$F8105200AS–CRYPT–7/08AT88SC0104CA10.1Security FusesThere are three fuses on the device that must be blown during the device personalization pro-cess. Each fuse locks certain portions of the configuration zone as OTP (One-Time Programmable) memory. Fuses are designed for the module manufacturer, card manufacturer and card issuer and should be blown in sequence, although all programming of the device and blowing of the fuses may be performed at one final step.munication Security ModesCommunications between the device and host operate in three basic modes. Standard mode is the default mode for the device after power-up. Authentication mode is activated by a successful authentication sequence. Encryption mode is activated by a successful encryption activation fol-lowing a successful authentication.Note:1.Configuration data include viewable areas of the Configuration Zone except the passwords:MDC: Modification Detection Code.MAC: Message Authentication Code.12.Security Options12.1Anti-TearingIn the event of a power loss during a write cycle, the integrity of the device’s stored data is recov-erable. This function is optional: the host may choose to activate the anti-tearing function,depending on application requirements. When anti-tearing is active, write commands take longer to execute, since more write cycles are required to complete them, and data is limited to a maxi-mum of eight bytes for each write request.Data is written first into a buffer zone in EEPROM instead of the intended destination address,but with the same access conditions. The data is then written in the required location. If this sec-ond write cycle is interrupted due to a power loss, the device will automatically recover the data from the system buffer zone at the next power-up. Non-volatile buffering of the data is done automatically by the device.During power-up in applications using Anti-Tearing, the host is required to perform ACK polling in the event that the device needs to carry out the data recovery process.Table 11-1.Communication Security Modes (1)Mode Configuration DataUser Data Passwords Data Integrity CheckStandardClear Clear Clear MDC (1)Authentication Clear Clear Encrypted MAC (1)Encryption ClearEncryptedEncryptedMAC (1)AT88SC0104CA12.2Write LockIf a user zone is configured in the write lock mode, the lowest address byte of an 8-byte pageconstitutes a write access byte for the bytes of that page. For example, the write lock byte at$080 controls the bytes from $081 to $087.Figure 12-1.Write Lock ExampleAddress$0$1$2$3$4$5$6$7 $08011011001xxxx xxxx xxxx xxxx xxxx xxxx xxxx xxxx xxxx xxxx xxxx xxxx xxxx xxxxlocked locked lockedThe Write-Lock byte itself may be locked by writing its least significant (rightmost) bit to “0”.Moreover, when write lock mode is activated, the write lock byte can only be programmed – thatis, bits written to “0” cannot return to “1”.In the write lock configuration, write operations are limited to writing only one byte at a time.Attempts to write more than one byte will result in writing of just the first byte into the device.12.3Password VerificationPasswords may be used to protect READ and/or WRITE access of any user zone. When a validpassword is presented, it is memorized and active until power is turned off, unless a new pass-word is presented or RST becomes active. There are eight password sets that may be used toprotect any user zone. Only one password is active at a time.Presenting the correct WRITE password also grants READ access privileges.12.4Authentication ProtocolThe access to a user zone may be protected by an authentication protocol. Any one of four keysmay be selected to use with a user zone.Authentication success is memorized and active as long as the chip is powered, unless a newauthentication is initialized or RST becomes active. If the new authentication request is not vali-dated, the card loses its previous authentication which must be presented again to gain access.Only the latest request is memorized.11Figure 12-2.Password and Authentication OperationsNote:Authentication and password verification may be attempted at any time and in any order. Exceeding corresponding authentica-tion or password attempts trial limit renders subsequent authentication or password verification attempts futile.12.5Cryptographic Message Authentication CodesAT88SC0104CA implements a data validity check function in the standard, authentication orencryption modes of operation.In the standard mode, data validity check is done through a Modification Detection Code (MDC),in which the host may read an MDC from the device in order to verify that the data sent wasreceived correctly.In authentication and encryption modes, the data validity check becomes more powerful since itprovides a bidirectional data integrity check and data origin authentication capability in the formof a Message Authentication Codes (MAC). Only the host/device that carried out a valid authen-tication is capable of computing a valid MAC. While operating in the authentication or encryptionmodes, the use of MAC is required. For an ingoing command, if the device calculates a MAC dif-ferent from the MAC transmitted by the host, not only is the command abandoned but thesecurity privilege is revoked. A new authentication and/or encryption activation will be requiredto reactivate the MAC.12AT88SC0104CAAT88SC0104CA12.6EncryptionThe data exchanged between the device and the host during read, write and verify passwordcommands may be encrypted to ensure data confidentiality.The issuer may choose to require encryption for a user zone by settings made in the configura-tion memory. Any one of four keys may be selected for use with a user zone. In this case,activation of the encryption mode is required in order to read/write data in the zone and onlyencrypted data will be transmitted. Even if not required, the host may still elect to activateencryption provided the proper keys are known.12.7Supervisor ModeEnabling this feature allows the holder of one specific password to gain full access to all eightpassword sets, including the ability to change passwords.12.8Modify ForbiddenNo write access is allowed in a user zone protected with this feature at any time. The user zonemust be written during device personalization prior to blowing the security fuses.12.9Program OnlyFor a user zones protected by this feature, data can only be programmed (bits change from a “1”to a “0”), but not erased (bits change from a “0” to a “1”).13.Protocol SelectionThe AT88SC0104CA supports two different communication protocols.Smartcard Applications:Smartcard applications use ISO 7816-B protocol in asynchronous T = 0 mode for compatibil-ity and interoperability with industry standard smartcard readers.Embedded Applications:A 2-wire serial interface provides fast and efficient connectivity with other logic devices ormicrocontrollers.The power-up sequence determines establishes the communication protocol for use within thatpower cycle. Protocol selection is allowed only during power-up.13.1Synchronous 2-Wire Serial InterfaceThe synchronous mode is the default mode after power up. This is due to the presence of aninternal pull-up on RST. For embedded applications using CryptoMemory in standard plasticpackages, this is the only available communication protocol.Power-up V CC, RST goes high also.After stable V CC, SCL(CLK) and SDA(I/O) may be driven.13Once synchronous mode has been selected, it is not possible to switch to asynchronous modewithout first powering off the device.Figure 13-1.Synchronous 2-Wire ProtocolNote:Five clock pulses must be sent before the first command is issued.13.2Asynchronous T = 0 ProtocolThis power-up sequence complies to ISO 7816-3 for a cold reset in smart card applications.V CC goes high; RST, I/O (SDA) and CLK (SCL) are low.Set I/O (SDA) in receive mode.Provide a clock signal to CLK (SCL).RST goes high after 400 clock cycles.The device will respond with a 64-bit ATR code, including historical bytes to indicate the memorydensity within the CryptoMemory family.Once asynchronous mode has been selected, it is not possible to switch to synchronous modewithout first powering off the device.Figure 13-2.Asynchronous T = 0 Protocol (Gemplus Patent)14.Initial Device ProgrammingEnabling the security features of CryptoMemory requires prior personalization. Personalizationentails setting up of desired access rights by zones, passwords and key values, programmingthese values into the configuration memory with verification using simple WRITE and READcommands, and then blowing fuses to lock this information in place.Gaining access to the configuration memory requires successful presentation of a secure (ortransport) code. The initial signature of the secure (transport) code for the AT88SC0104CA 14AT88SC0104CA15AT88SC0104CAdevice is $DD 42 97. This is the same as the WRITE 7 password. The user may elect to change the signature of the secure code anytime after successful presentation.After writing and verifying data in the configuration memory, the security fuses MUST be blown to lock this information in the device. For additional information on personalizing CryptoMemory,please see the application notes Programming CryptoMemory for Embedded Applications and Initializing CryptoMemory for Smart Card Applications from the product page at /products/securemem .15.Ordering InformationNote:1.Formal drawings may be obtained from an Atmel sales office.Ordering Code Package Voltage Range Temperature Range A T88SC0104CA-MJ A T88SC0104CA-MP M2 – J Module M2 – P Module 2.7V–3.6VCommercial (0°C to 70°C)A T88SC0104CA-PU A T88SC0104CA-SU A T88SC0104CA-TU 8P38S18A2 2.7V–3.6V Lead-free/Halogen-free/Industrial(−40°C to 85°C)A T88SC0104CA-WI7 mil wafer2.7V–3.6VIndustrial (−40°C to 85°C)Package Type (1)DescriptionM2 – J Module M2 ISO 7816 Smart Card ModuleM2 – P Module M2 ISO 7816 Smart Card Module with Atmel ® Logo 8P38-lead, 0.300” Wide, Plastic Dual Inline Package (PDIP)8S18-lead, 0.150” Wide, Plastic Gull Wing Small Outline Package (JEDEC SOIC)8A28-lead, 4.4mm Body, Plastic Thin Shrink Small Outline Package (TSSOP)16.Packaging Information.16AT88SC0104CAAT88SC0104CA 17.Ordering Code: SU17.18-lead SOIC1718.Ordering Code: PU 18.18-lead PDIP18AT88SC0104CAAT88SC0104CA 18.28-lead TSSOP19Headquarters InternationalAtmel Corporation 2325 Orchard Parkway San Jose, CA 95131 USATel: 1(408) 441-0311 Fax: 1(408) 487-2600Atmel AsiaRoom 1219Chinachem Golden Plaza77 Mody Road TsimshatsuiEast KowloonHong KongTel: (852) 2721-9778Fax: (852) 2722-1369Atmel EuropeLe Krebs8, Rue Jean-Pierre TimbaudBP 30978054 Saint-Quentin-en-Yvelines CedexFranceTel: (33) 1-30-60-70-00Fax: (33) 1-30-60-71-11Atmel Japan9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTel: (81) 3-3523-3551Fax: (81) 3-3523-7581Product ContactWeb Site/products/securememTechnical Supportcryptomemory@Sales Contact/contactsLiterature Requests/literatureDisclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise,to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL’S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL’S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel’s products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.© 2008 Atmel Corporation. All rights reserved. Atmel®, logo and combinations thereof, Cryptomemory® and others, are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.。

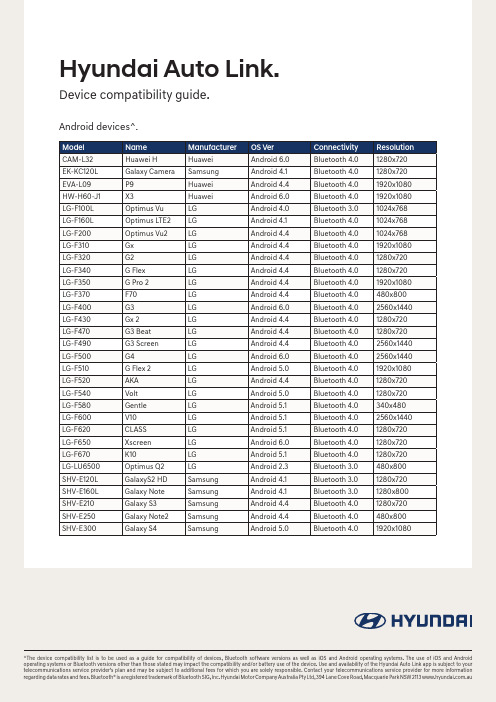

华特自动链接设备兼容性指南说明书

2560x1440

iOS devices^.

Model A1429 A1586 A1522 A1660

Name iPhone5 iPhone6 iPhone6+ iPhone7

Manufacturer Apple Apple Apple Apple

OS Ver 8.1.3 10.2.1 10.2.1 10.2.1

Connectivity Bluetooth 4.2 Bluetooth 4.2 Bluetooth 4.2 Bluetooth 4.2

Resolution 1136x640 1334x750 1920x1080 1334x750

Guide current as at 17 May2017.

Samsung

Galaxy S4 Zoom Samsung

Galaxy On7

Samsung

Galaxy ALPHA Samsung

Galaxy S5