verilog同步复位PK异步复位

异步复位同步化的方法

异步复位同步化的方法引言:在现代信息技术发展的浪潮中,异步复位同步化成为了一种重要的数据处理方法。

异步复位同步化通过合理的设计和控制,能够有效解决异步复位过程中的数据不一致问题,保证数据处理的正确性和可靠性。

本文将介绍异步复位同步化的原理、方法和应用领域。

一、异步复位的问题在数字电路中,异步复位是指通过外部信号将整个电路系统复位到初始状态。

然而,由于异步复位信号的传输延迟和不确定性,可能导致电路内部不同部分的复位时间不一致,进而产生数据不一致的问题。

例如,当某个部分已经复位完成,而其他部分还未复位时,数据传输可能会导致未复位部分的数据被错误地传递或处理。

这种数据不一致可能会导致系统崩溃、数据丢失或错误的计算结果。

二、异步复位同步化的原理为了解决异步复位带来的数据不一致问题,可以采用异步复位同步化的方法。

异步复位同步化的原理是通过引入同步化过程,确保所有部分在复位完成之前都处于同步的状态。

具体来说,异步复位同步化的过程可以分为以下几个步骤:1. 引入同步信号:在异步复位信号到达之前,引入一个同步信号,用于同步整个电路系统的状态。

2. 同步化过程:在同步信号的作用下,各个部分按照预定的顺序和时间间隔进行复位操作,确保复位过程的同步性。

3. 数据传输控制:在复位过程中,需要对数据传输进行控制,确保只有在所有部分都完成复位后,才能开始正常的数据传输。

4. 状态确认:在复位过程完成后,需要进行状态确认,确保所有部分都已经复位完成,可以正常开始数据处理。

三、异步复位同步化的方法异步复位同步化的方法可以根据具体的应用场景和需求进行选择。

以下是一些常见的异步复位同步化方法:1. 分阶段同步化:根据系统的具体结构和复位要求,将复位过程分为多个阶段,每个阶段都有确定的时间间隔和顺序。

通过引入同步信号和控制逻辑,确保每个阶段的同步性,避免数据不一致问题。

2. 时序控制同步化:通过设计和控制时序信号,确保各个部分在特定的时钟周期内进行复位操作,从而达到同步化的效果。

Verilog笔记.5.同步、异步

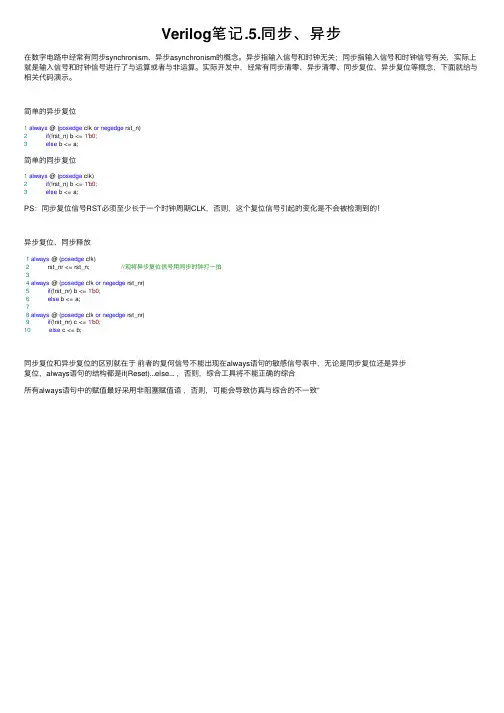

Verilog笔记.5.同步、异步在数字电路中经常有同步synchronism、异步asynchronism的概念。

异步指输⼊信号和时钟⽆关;同步指输⼊信号和时钟信号有关,实际上就是输⼊信号和时钟信号进⾏了与运算或者与⾮运算。

实际开发中,经常有同步清零、异步清零、同步复位、异步复位等概念,下⾯就给与相关代码演⽰。

简单的异步复位1always @ (posedge clk or negedge rst_n)2if(!rst_n) b <= 1'b0;3else b <= a;简单的同步复位1always @ (posedge clk)2if(!rst_n) b <= 1'b0;3else b <= a;PS:同步复位信号RST必须⾄少长于⼀个时钟周期CLK,否则,这个复位信号引起的变化是不会被检测到的!异步复位、同步释放1always @ (posedge clk)2 rst_nr <= rst_n; //现将异步复位信号⽤同步时钟打⼀拍34always @ (posedge clk or negedge rst_nr)5if(!rst_nr) b <= 1'b0;6else b <= a;78always @ (posedge clk or negedge rst_nr)9if(!rst_nr) c <= 1'b0;10else c <= b;同步复位和异步复位的区别就在于前者的复何信号不能出现在always语句的敏感信号表中,⽆论是同步复位还是异步复位,always语句的结构都是if(Reset)...else... ,否则,综合⼯具将不能正确的综合所有always语句中的赋值最好采⽤⾮阻塞赋值语,否则,可能会导致仿真与综合的不⼀致”。

异步复位还是同步复位?

altera的LE是没有latch的结构的

又查了sp3和sp2e,别的不查了,手册上说支持这种配置。有关altera的表述wangdian说的对,altera的ff不能配置成latch,它使用查找表来实现latch,

latch的最大缺点就是没有时钟端,和当前我们尽可能采用时序电路的设计思路不符。

latch是电平触发,相当于有一个使能端,且在激活之后(在使能电平的时候)相当于导线了,随输出而变化,在非使能状态下是保持原来的信号,这就可以看出和flip-flop的差别,其实很多时候latch是不能代替ff的

一般的设计规则是:在绝大多数设计中避免产生LATCH.

它会让您设计的时序完蛋,并且它的隐蔽性很强,非老手不能查出.

latch最大的危害在于不能过滤毛刺。这对于下一级电路是极其危险的。

所以,只要能用D触发器的地方,就不用latch。

有些地方没有时钟,也只能用latch了。

很简单一个例子来说明:

关于latch的讨论

latch和flip-flop都是时序逻辑,区别为:latch同其所有的输入信号相关,当输入信号变化时latch就变化,没有时钟端;flip-flop受时钟控制,只有在时钟触发时才采样当前的输入,产生输出。当然因为二者都是时序逻辑,所以输出不但同当前的输入相关还同上一时间的输出相关。

比如现在用一个clk接到latch的使能端(假设是高电平使能),这样需要的setup时间,就是数据在时钟的下降沿之前需要的时间,但是如果是一个DFF,那么setup时间就是在时钟的上升沿需要的时间.这就说明如果数据晚于控制信号的情况下,只能用latch,这种情况就是,前面所提到的latch timing borrow.基本上相当于借了一个高电平时间.也就是说,latch借的时间也是有限的.

复位电路异步复位同步释放

复位电路异步复位同步释放异步复位和同步释放是数字电路设计中常见的两种复位方式。

复位电路的作用是将电路的各个元件状态恢复到初始状态,以确保电路在启动时的可靠性和正确性。

异步复位是指在电路中引入一个异步信号,当该信号为高电平时,电路内部的各个元件都被强制复位为初始状态。

异步复位信号可以是外部输入信号,例如按键、开关等,也可以是内部产生的信号,例如定时器溢出信号等。

异步复位的优点是简单直接,可以快速将电路恢复到初始状态。

但是,异步复位也存在一些问题,例如在复位信号引入时可能导致冲突和干扰,还可能引起时序问题和电路不稳定等。

同步释放是指在电路中采用同步信号来释放复位状态。

同步信号通常是由时钟信号和其他状态信号共同产生的,只有在满足特定条件时才会触发复位释放。

同步释放可以有效地解决异步复位的问题,使电路在复位时更加稳定可靠。

同步释放的实现通常需要借助于锁存器、触发器等元件,通过时序控制和状态判定来实现复位释放的精确控制。

在实际的电路设计中,异步复位和同步释放常常结合使用,以实现对电路的可靠复位和平稳释放。

例如,可以使用异步复位电路将电路初始化为初始状态,然后通过同步信号来控制复位释放的时机,确保电路在启动时的稳定性。

此外,还可以根据具体的应用场景和需求,灵活选择异步复位或同步释放的方式。

异步复位和同步释放是数字电路设计中常用的复位方式,它们通过引入异步信号和同步信号来实现对电路的复位和释放。

在电路设计中,需要根据具体的需求和应用场景选择合适的复位方式,以确保电路的可靠性和正确性。

同时,还需要注意复位信号的引入时机和释放时机,避免引发冲突、干扰和时序问题。

通过合理设计和优化,可以实现高性能、高可靠性的复位电路,提高电路的工作效率和稳定性。

EDA技术与Verilog_HDL(潘松)第6章习题答案

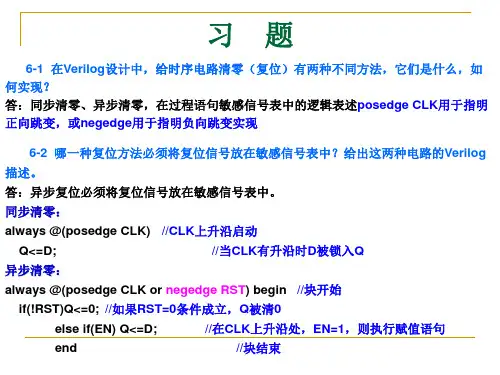

6-1 在Verilog设计中,给时序电路清零(复位)有两种不同方法,它们是什么,如何实现?答:同步清零、异步清零,在过程语句敏感信号表中的逻辑表述posedge CLK用于指明正向跳变,或negedge用于指明负向跳变实现6-2 哪一种复位方法必须将复位信号放在敏感信号表中?给出这两种电路的Verilog 描述。

答:异步复位必须将复位信号放在敏感信号表中。

同步清零:always @(posedge CLK) //CLK上升沿启动Q<=D; //当CLK有升沿时D被锁入Q异步清零:always @(posedge CLK or negedge RST) begin //块开始if(!RST)Q<=0; //如果RST=0条件成立,Q被清0else if(EN) Q<=D;//在CLK上升沿处,EN=1,则执行赋值语句end//块结束6-3 用不同循环语句分别设计一个逻辑电路模块,用以统计一8位二进制数中含1的数量。

module Statistics8(sum,A); output[3:0]sum;input[7:0] A;reg[3:0] sum;integer i;always @(A)beginsum=0;for(i=0;i<=8;i=i+1) //for 语句if(A[i]) sum=sum+1;else sum=sum;endendmodule module Statistics8(sum,A); parameter S=4;output[3:0]sum;input[7:0] A;reg[3:0] sum;reg[2*S:1]TA;integer i;always @(A)beginTA=A; sum=0;repeat(2*S)beginif(TA[1])sum=sum+1;TA=TA>>1;endendendmodulerepeat循环语句for循环语句module Statistics8(sum,A);parameter S=8;output[3:0]sum;input[7:0] A;reg[S:1] AT;reg[3:0] sum;reg[S:0] CT;always @(A) beginAT={{S{1'b0}},A}; sum=0; CT=S;while(CT>0) beginif(AT[1])sum=sum+1;else sum=sum;begin CT= CT-1; AT=AT>>1; end end endendmodule6-3 用不同循环语句分别设计一个逻辑电路模块,用以统计一8位二进制数中含1的数量。

同步复位和异步复位的优缺点

同步复位和异步复位的优缺点Advantages of synchronous resets1. Synchronous reset logic will synthesize to smaller flip-flops, paticularly if the reset if gated with the logic generating the d-input.2. Synchronous resets generally insure that the circuit is 100% synchronous.3. In some designs, the reset must be generated by a set of internal conditions. A synchronous reset is recommended for these types of designs because it will filter the logic equation glitches between clocks.Disadvantages of synchronous resets1. Not all ASIC libraries have flip-flops with built-in synchronous resets. However since synchronous reset is just another data input, you don't really neea a special flop. The reset logic can easily be synthesized outside the flop itself.2. Synchronous resets may need a pulse stretcher to guarantee a reset pulse width wide enough to ensure reset is present during an active edge of the clock.3. By its very nature, a synchronous reset will require a clock in order to reset the circuit. This may not be a disadvantage to some design styles but to others, it may be an annoyance.Advantages of asynchronous resets1. The beggest advantage to using asynchronous resets is that, as long as the vendor library has asynchronously reset-able flip-flops, the data path is guaranteed to be clean.2. Another advantage favoring asynchronous resets is that the circuit can be reset with or without a clock present. Disadvantages of asynchronous resets1. The Reuse Methodology Manual(RMM) syggests that asynchronous resets are not be used because they cannot be used with cycle based simulators.2. For DFT, if the asynchronous reset is not directly driven from an I/O pin, then the reset net from the reset driver must be disabled for DFT scanning and testing. This is required for the synchronizer circuit.3. The beggest problem with asynchronous resets is that they are asynchronous, both at the assertion and at the de-assertion of the reset. The assertion is a non issue, the de-assertion is the issue. If the asynchronous reset is released at or near the active clock edge of a flip-flop, the output of the flip-flop could go metastable and thus the reset state of the ASIC could be lost.4. Another problem that an asynchronous reset can have, depending on its source, is spurious resets due to noise or glitches on the board or system reset.。

FPGA设计异步复位同步释放有讲究

FPGA设计异步复位同步释放有讲究异步复位同步释放首先要说一下同步复位与异步复位的区别。

同步复位是指复位信号在时钟的上升沿或者下降沿才能起作用,而异步复位则是即时生效,与时钟无关。

异步复位的好处是速度快。

再来谈一下为什么FPGA 设计中要用异步复位同步释放。

复位信号的释放是有讲究的:我们知道,DFF 的D 端和clk 端之间时序关系是有约束的,这种约束我们通过setup time 和hold time 来check。

即D 端的data 跳变的时刻要与clk 端的时钟上升沿(或者下降沿)跳变要错开,如果这两个跳变撞到一起,我们无法保证DFF 能够sample 到正确的data,这时候不满足setup/hold time 要求,就会发生亚稳态,我们sample 到的data 可能是不稳定的中间态的值,并不是我们原本想要的data。

与此类似,异步复位端与clk 端之间也存在着类似的时序约束关系,为了准确稳定地sample 到异步复位端的reset 信号,我们要求reset 信号在clk 上升沿(或者下降沿)跳变的前后一段时间内保持稳定,不要跳变。

clk 跳变沿之前必须保持稳定的最短时间叫做recovery time,clk 跳变沿之后需要保持稳定的最短时间叫做removal time。

如果在此时间窗口内reset 信号发生跳变,不确定reset 到底有没有释放成功(类似setup+hold 时间窗口内,data 跳变,发生亚稳态,sample 到的值是不稳定的中间态值)。

在IC 设计过程中我们是会check recovery 和removal time 的,如果不满足,我们会通过布局布线的调整(后端的调整)让电路满足这个条件(实质就是让reset 跳变沿和clk 跳变沿错开);但是对于FPGA设计而言,我们一般不采用异步释放的方法,因为FPGA 的布局布线可以调整。

IC设计中同步复位与

IC设计中同步复位与异步复位的区别异步复位是不受时钟影响的,在一个芯片系统初始化(或者说上电)的时候需要这么一个全局的信号来对整个芯片进行整体的复位,到一个初始的确定状态。

而同步复位需要在时钟沿来临的时候才会对整个系统进行复位。

请注意,如果芯片是有多个时钟的系统,那么如何保证不同时钟域的电路能够“同时”复位将会是一个重要的问题,此外,如果你的时钟是一个低频时钟,那么在这个系统(包括其他芯片)上电时如何保证能和其他芯片同时复位?硬件全局异步复位是必要的,请注意这里加上了“全局”,这是因为异步复位既然要对整个芯片“同时”复位,那么布线延时绝不能不考虑,使用FPGA设计时芯片的异步复位必须要走全局网络。

再提醒一点,芯片中最好不要出现多个异步复位。

一个关键原因是对于FPGA而言,多个异步复位信号难以实现前面要求的“全局网络”。

异步复位最大的优点是, 数据通路就可以不依赖于时钟而确保清洁可控。

然而, 异步复位也有其固有的缺陷。

异步复位设计的DFT (可测性设计) 与STA (静态时序分析) 的复杂性要高于同步复位设计; 但异步复位中最严重的问题是, 如果异步复位信号在触发器时钟有效沿附近“释放”(复位信号从有效变为无效) 的话, 可能会导致触发器输出的亚稳态。

同步复位和异步复位的比较(转载)无论同步还是异步复位,在对触发器时序进行分析的时候,都要考虑复位端与时钟的相位关系。

对于同步复位,复位信号可以理解为一个普通的数据信号,它只有在时钟的跳变沿才会其作用,一般只要复位信号持续时间大于一个时钟周期,就可以保证正确复位。

对于异步复位,复位可以在任何时候发生,表面上看跟时钟没有关系,但真实情况是异步复位也需考虑时钟跳变沿,因为时钟沿变化和异步复位都可以引起Q端数据变化,如果异步复位信号跟时钟在一定时间间隔内发生变化,Q值将无法确定,即亚稳态现象。

这个时候既是异步复位信号持续时间再长都没有办法,因为不定态已经传递下去。

verilog 复位赋值

Verilog 复位赋值详解

Verilog是一种硬件描述语言,用于描述数字电路和系统。

在Verilog中,复位是一个重要的概念,它用于将电路或模块的状态初始化为特定的值。

复位通常在系统启动时或出现异常情况时使用。

在Verilog中,有两种常见的复位方式:异步复位和同步复位。

1.异步复位

异步复位是一种立即生效的复位方式,它不需要时钟信号的配合。

当异步复位信号为高电平时,电路或模块的状态将被立即清零或置为特定的初始值。

异步复位通常用于一些不需要时钟的简单电路或模块。

例如,以下代码实现了一个简单的异步复位逻辑:

在这个例子中,reset是异步复位信号,当它为高电平时,counter_reg将被清零。

2.同步复位

同步复位是一种需要时钟信号配合的复位方式。

当同步复位信号为高电平时,电路或模块的状态将被清零或置为特定的初始值。

只有在时钟信号的上升沿到来时,同步复位才会生效。

同步复位通常用于一些需要时钟的复杂电路或模块。

例如,以下代码实现了一个简单的同步复位逻辑:

在这个例子中,reset是同步复位信号,当它为高电平时,count将被清零。

只有在时钟信号的上升沿到来时,count才会被清零。

需要注意的是,在实现复位逻辑时,应该考虑一些特殊情况,例如异步复位的延迟和同步复位的时序要求。

此外,还应该注意复位的稳定性和可靠性,以确保系统能够正常工作。

异步复位与同步释放

异步复位与同步释放很多时候,我们都希望系统一上电以及在仿真开始的时候所有寄存器都有一个已知的状态。

复位有两种方式,即同步复位和异步复位。

同步复位:“同步”的意思是和工作时钟同步。

也就是说当时钟的上升沿(下降沿)来到时检测到按键的复位操作才有效,否则无效。

如下图所示为同步低复位波形。

异步复位:“异步”的意思是和工作时钟不同步。

也就是说寄存器的复位不关心时钟的上升沿(下降沿)是否到来,只要有检测到按键被按下,就立刻执行复位操作。

如下图所示为同步低复位波形。

同步复位还是异步复位我们以D触发器为例来说明Inter(Altera)的器件是用同步复位好还是异步复位好。

先来看一下同步复位D触发器的RTL代码,如下所示://---------------------------------01module test(02 input wire sclk ,03 input wire rst_syncn ,04 input wire d ,0506 outputreg q07);0809always@(posedge sclk)10 if(rst_sync_n ==1'b0)11 q <=1'b0;12 else13 q <= d;1415endmodule//--------------------------------在Quartus工具中编写完RTL后点击“Start Analysis & Synthesis”图标进行分析和综合。

然后双击“Netlist Viewers”下的“RTL Viewer”查看RTL视图。

如下图所示,可以看到一个 D触发器的结构,也可以称为寄存器,但是还附加了一个选择器,用于同步复位的控制。

点击“Start Compilation”图标全编译进行布局布线,完成后我们可以看到“Flow Summary”资源使用量,如下图所示,可以看到使用了LE中的一个组合逻辑资源和一个时序逻辑资源。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

verilog同步复位PK异步复位

时钟和复位是FPGA中关键,下面是特权写的,复制以备找工作~~~

同步复位:

1.复位信号只有在时钟上升沿到来时,才能有效。

2.代码为:

always@(posedge clk)

if ( !rst_n )

....

else

....

异步复位:

1.无论时钟沿是否来到,只要复位信号有效就对系统复位。

2.代码为:

always@ ( posedge clk or negedge rst_n ) if ( !rst_n )

....

else

....

优缺点:

同步复位优点:

1. 有利于仿真

2. 100%为同步电路

3. 可以滤除高于时钟的毛刺

缺点:

1. 复位信号有效时长要大于时钟周期,同时还要考虑电路延时

2. 大多数的逻辑器件只有异步复位接口,使用同步复位需要耗费较多的逻辑资源

异步复位优点:

1. 节省资源

2. 设计简单

3. 可以使用专用的复位端口CLR

缺点:

1. 在复位信号释放时,如果在时钟沿附近容易导致寄存器输出出现亚稳态

2. 复位信号容易受毛刺的影响

同时获得两者的优点:异步复位,同步释放

代码为:

always@(poseedge clk or negedge rst_in)

if ( ! rst_in )

begin

rst_buf <= 1'b0;

rst_n <= 1'b0;

end

else

begin

rst_buf <= 1'b1;

rst_n <= rst_buf ; end。