实验二 异步清零和同步使能的4位计数器

实验五 含异步清零和同步使能4位加法计数器的VHDL设计

实验五含异步清零和同步使能4位加法计数器的VHDL设计一、实验目的1掌握计数器的VHDL设计方法;2掌握异步复位和同步复位和使能的概念;3掌握寄存器性能的分析方法(即分析芯片所能达到的最高时钟频率)。

二、实验内容1异步复位4位加法计数器的设计;2同步复位4位加法计数器的设计。

3异步清0和同步时钟使能的4位加法计数器三、实验原理复位:给计数器一个初值叫复位,如果所给初值为0,则称复位为清零。

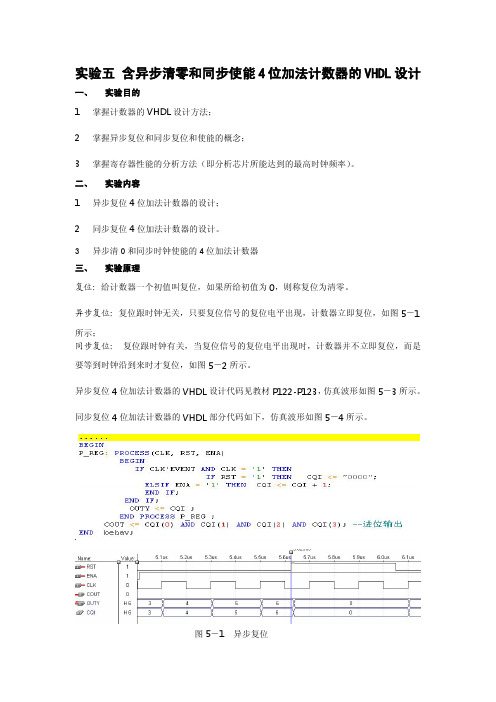

异步复位:复位跟时钟无关,只要复位信号的复位电平出现,计数器立即复位,如图5-1所示;同步复位:复位跟时钟有关,当复位信号的复位电平出现时,计数器并不立即复位,而是要等到时钟沿到来时才复位,如图5-2所示。

异步复位4位加法计数器的VHDL设计代码见教材P122-P123,仿真波形如图5-3所示。

同步复位4位加法计数器的VHDL部分代码如下,仿真波形如图5-4所示。

.图5-1异步复位图5-2同步复位图5-3异步复位计数器仿真波形图5-4同步复位计数器仿真波形四、实验步骤(一)异步复位4位加法计数器的设计1建立一个设计工程,工程名为CNT4B;2打开文本编辑器,建立一个VHDL设计文件,其VHDL代码见教材P164中的例6-20,文件名存为CNT4B.VHD。

注意文件的扩展名要选为.vhd,而且要求工程名、文件名和设计实体名必须相同。

3选器件:ACEX1K,EP1K30TC144-3(旧)或Cyclone,EP3C40Q240C8目标芯片。

4编译;5建立波形文件,然后保存,其文件名必须与工程名一致;【波形设置:①设置仿真时间为10us:②设置输入信号的波形:时钟周期设置为200ns,其他输入信号的波形设置参看图6-3。

】6仿真,观察输出波形是否正确;7时序分析:分析芯片所能达到的最高时钟频率。

【打开时序分析器,然后执行菜单命令:analysis/register performance/start,可以看到最高时钟频率为100.00MHZ】(二)同步复位4位加法计数器的设计8建立一个设计工程,工程名为CNT4B_SYS;9打开文本编辑器,建立一个VHDL设计文件,其VHDL代码参看异步计数器代码和实验原理中的参考代码,文件名存为CNT4B_SYS.VHD。

实验4:同步计数器及其应用实验报告

实验4:同步计数器及其应用实验报告

一、实验目的

1、了解可编程数字系统设计的流程

2、掌握Quartus II 软件的使用方法

3、掌握原理图输入方式设计数字系统的方法和流程

4、掌握74LS161同步16进制计数器的特点及其应用

二、实验设备

1、计算机:Quartus II 软件

2、Altera DE0 多媒体开发平台

3、集成电路:74LS10

4、集成电路:74LS161

三、实验内容

1、74LS161逻辑功能的测试

2、用74LS161实现12进制计数(异步清零)

3、用74LS161实现12进制计数(同步置数)

四、实验原理

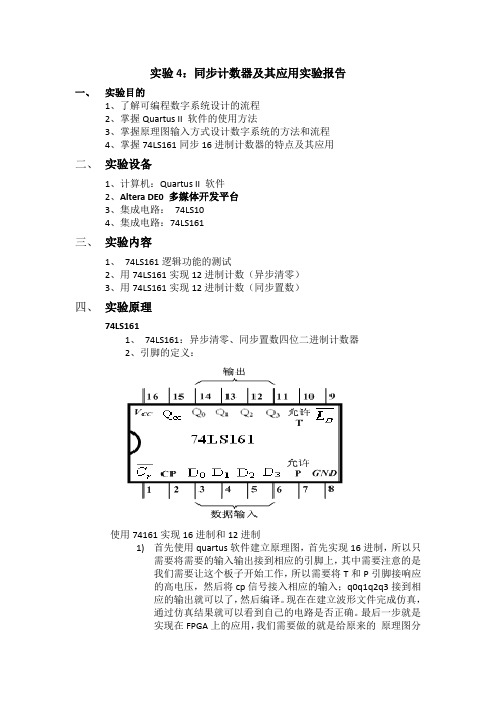

74LS161

1、74LS161:异步清零、同步置数四位二进制计数器

2、引脚的定义:

使用74161实现16进制和12进制

1)首先使用quartus软件建立原理图,首先实现16进制,所以只

需要将需要的输入输出接到相应的引脚上,其中需要注意的是

我们需要让这个板子开始工作,所以需要将T和P引脚接响应

的高电压,然后将cp信号接入相应的输入;q0q1q2q3接到相

应的输出就可以了,然后编译。

现在在建立波形文件完成仿真,

通过仿真结果就可以看到自己的电路是否正确。

最后一步就是

实现在FPGA上的应用,我们需要做的就是给原来的原理图分

配相应的引脚,然后重新编译后,插入线就可以看到仿真结果

了。

2)12进制可以采取两种方式,也就是同步置数和异步清零两种

方式,我使用的异步清零,从而只需要对q0q1q2q3在12的时

候执行清零的动作就可以了,也就是加一个而输入的与非门就

可以了。

五、实验结果。

实验一2 含异步清0

1)根据DE2_pin_assignments文件内容、格式 已制作本设计引脚对应文件的引脚锁定文 件:CNT4B.csv 2) 由Assignments->Import Assignment,打开 对话框,调入引脚对应文件即可。

• 进行编译、下载,通过实验,检查引脚锁定是 否正确。

• 将波形文件存盘为CNT4B.vwf

• 设定CNT4B.v是目前的顶层文件

• 由Processing->start->start annlysis & elaboration对程序进行初步的分析

• 由view->utility window->node finder,得到 如下对话框,

Filter中选择Pins: all 然后按List得到输 入输出端口列表, 用鼠标将它们拖到 波形编辑窗口

• 将instance框中的名字改为CNT4B(选中右击选择Rename Instance)

• 为看清楚,按

,将窗口浮动

• 在CNT4B框双击(Double-click to add node), 弹出节点(noder)对话框,Filter项选择all, 然后点击List

选中要观察的端口COUT、OUTY然后单击>加 入,点OK。

功能仿真

• 由Processing->generate functional simulation netlist,提取功能仿真的网表 • 由assigments->settings,对仿真工具设定为 功能仿真,并将激gt; start simulation 进行功能仿 真,并对结果进行分析。

• 锁好引脚,进行全编译(compile),重新布 局布线,时序仿真 引脚锁定,仿真结果核对无误后,准备下载

如何使用QuartusII7.0

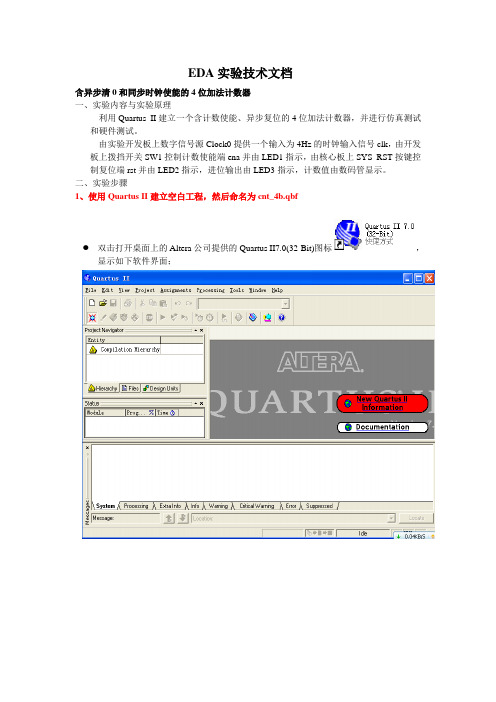

EDA实验技术文档含异步清0和同步时钟使能的4位加法计数器一、实验内容与实验原理利用Quartus II建立一个含计数使能、异步复位的4位加法计数器,并进行仿真测试和硬件测试。

由实验开发板上数字信号源Clock0提供一个输入为4Hz的时钟输入信号clk,由开发板上拨挡开关SW1控制计数使能端ena并由LED1指示,由核心板上SYS_RST按键控制复位端rst并由LED2指示,进位输出由LED3指示,计数值由数码管显示。

二、实验步骤1、使用Quartus II建立空白工程,然后命名为cnt_4b.qbf双击打开桌面上的Altera公司提供的Quartus II7.0(32-Bit)图标,显示如下软件界面;●选择菜单栏中File>>New Project Wizard来新建工程,点击后弹出新建工程向导对话框如下分别提示完成五项工作1)项目名称与保存路径2)顶层设计实体名称3)加入已有文件和相关库4)指定目标Altera器件封装和型号5)设置项目的其他EDA工具●单击Next进入如下图所示界面,并按图新建工程路径、名称、顶层实体在这里,工程名与顶层文件的实体名同名为cnt_4,文件夹所在路径名和文件夹名中不能用中文,不能用空格,不能用括号(),可以用下划线_或英文字母或数字,但最好也不要以数字开头。

●单击Next进入如下图所示界面,这里是添加已有相关工程文件,这里我们是建立空白工程,所以不需要添加任何文件●单击Next进入如下图所示界面,这一步是对所用实验核心板中FPGA器件进行设置,以确保代码顺利编译和下载。

MagicSOPC实验箱上的FPGA标配为:Altera公司CycloneII系列的EP2C35F672。

设置相关参数如图所示。

设置完成后,单击Next, 进入如下图所示界面,这里不需要设置其他EDA工具●再单击Next,出现如下图所示的工程信息报告对话框,提示设计者看到工程文件配置信息报告。

设计含异步使能清0和同步时钟使能的加法计数器

综合课程设计实验设计含异步使能清0和同步时钟使能的加法计数器1.实验目的1.计数器的设计2.QUARTUS 2中SIGNALTAP 2实时测试技术3.FPGA配置芯片的使用4.继续熟悉实验的软硬件平台2.实验步骤与结果1.设计含异步使能清0和同步时钟使能的加法计数器源代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT10 ISPORT(CLK,RST,EN:IN STD_LOGIC;CQ:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);COUT: OUT STD_LOGIC);END CNT10;ARCHITECTURE BEHAV OF CNT10 ISBEGINPROCESS(CLK,RST,EN )VARIABLE CQI :STD:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINIF RST=’1’ THEN CQI:=(OTHERS=>’0’); --复位信号ELSIF CLK’EVENT AND CLK=’1’ THENIF EN=’1’ THEN --使能信号IF CQI<9 THEN CQI:=CQI+1;ELSE CQI:=(O THERS=>’0’);END IF;END IF;IF CQI=9 THEN COUT<=’1’; --进位ELSE COUT<=’0’;END IF;CQ<=CQI;END PROCESS;END BEHAV;实验结果:键2低电平时允许计数,键1高电平时允许计数,数码管最后一位正确计数0到9,当有进位时,发光管D1显示进位信号。

2.使用嵌入式逻辑分析仪SIGNALTAP2 进行实时测试按如图设置SIGNALTAP 2获得实验波形:可以看到CQ的波形为锯齿状的3.将计数器设计文件烧到实验板上FPGA的配置器件EPCS1中,实现掉电保护实验结果:掉电重启以后实验板上程序的功能正常。

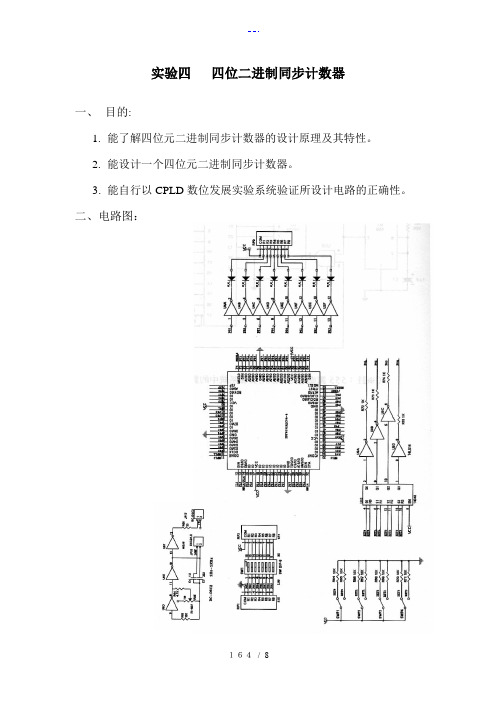

实验四四位二进制同步计数器

实验四四位二进制同步计数器一、目的:1.能了解四位元二进制同步计数器的设计原理及其特性。

2.能设计一个四位元二进制同步计数器。

3.能自行以CPLD数位发展实验系统验证所设计电路的正确性。

二、电路图:三、实验器配置图:四、实验步骤与画面:1.建立一个名为count16.vhd的新文件,并在QuartusⅡ文字编辑器中,以VHDL语言来设计程式,图为四位二进制计数器的VHDL代码。

其中clk为时钟端口,clk为异步清零端,Q为计数输出端口,co为进位输出端口。

2.存储、检查及编译。

3.创建元件符号。

4.创建波形文件,设定合适的端口信号,仿真元件的波形。

观察波形图可以看出当芯片可以实现16进制计数功能。

五、相关说明:1.同步计数器的意义是将所有正反器的时脉连接在一起,当时脉进来时,所有的正反器同时被触发而动作,因此传递延迟时间就可以大为缩短,计数的速度就会增快。

2.我们可以利用MAX+plusⅡ的Timing Analyzer来比较同步计数器与非同步计数器(单元十)的传递延迟状况,图U12-3(a)与图U12-3(b)为分析所得结果,从图中可以发现,同步计数器从时脉输入到各级的输出,其传递延迟时间皆相同,而非同步计数器则越到后级传递延迟时间越长。

3.图U12-2的程式设计方法,也可以改用D型正反器来设计,如图U12-4所示,您可以发现此种设计同步计数器的方法较简洁。

4.若要将图U12-4改成下数计数器,只要将叙述ff[].d=ff[].q+1;改成ff[].d=ff[].q-l;即可。

5.图U12-5为四位元含致能及清除的模10上下数计数器,其中的设计重点为:(1)为了能在高频计数电路应用,本电路的清除方式采同步清除式设计,并不利用正反器本身的elrn脚,而是当clr脚输入为鬲态时,令所有正反器的D输入脚为o,达到清除的目的。

(2)程式中使用了巢状的IF THEN叙述,须注意每一层的IF THEN、 ELSIF、ELSE及END IF的对应,不要弄乱了,否则会很麻烦。

实验二-异步清零和同步使能的4位计数器

西南科技大学实验报告FPGA现代数字系统设计实验题目:含异步清零和同步使能的4位加法计数器专业班级:学生姓名:学生学号:实验时间:指导教师:实验二含异步清0和同步使能的4位加法计数器一、实验目的:学习时序电路的设计、仿真和硬件测试,进一步熟悉VHDL技术。

二、原理说明:图2.1是一含计数使能、异步复位和计数值并行预置功能4位加法计数器,例2.1是其VHDL描述。

由图2-1所示,4位锁存器;rst是异步清0信号,高电平有效;clk是锁存信号;D[3..0]是4位数据输入端。

ENA是使能信号,当ENA为'1'时,多路选择器将加1器的输出值加载于锁存器的数据端;当ENA为'0'时将"0000"加载于锁存器。

图2-1含计数使能、异步复位和计数值并行预置功能4位加法计数器三、实验内容:1、在QuartusII上对例2-1进行编辑、编译、综合、适配、仿真。

说明例中各语句的作用,详细描述示例的功能特点,给出其所有信号的时序仿真波形。

【例2-1】module CNT4B(CLK,RST,ENA,CLK_1,RST_1,ENA_1,OUTY,COUT);//端口声明input CLK,RST,ENA;output CLK_1,RST_1,ENA_1;output[3:0] OUTY;output COUT;reg[3:0] OUTY;reg COUT;//寄存器变量OUTY,位宽为1wire CLK_1;wire RST_1;wire ENA_1;assign CLK_1 = CLK;assign RST_1 = RST;assign ENA_1 = ENA;always@(posedge CLK or negedge RST) /*当CLK上升沿或者RST上升沿时,触发always模块执行*/beginif(!RST)beginOUTY<=4'b0000;COUT<=1'b0;/*当复位信号等于0时,计数OUTY、COUT置0*/endelseif(ENA) /*当使能信号为1时,计数器计数工作*/beginOUTY<=OUTY+1;COUT<=OUTY[0] & OUTY[1] & OUTY[2] & OUTY[3]; /*计数显示*/endendendmodule2保存计数器程序为CNT4B.vhd,进行功能仿真、全编译、时序仿真,如出现错误请按照错误提示进行修改,保证设计的正确性。

四位全加器

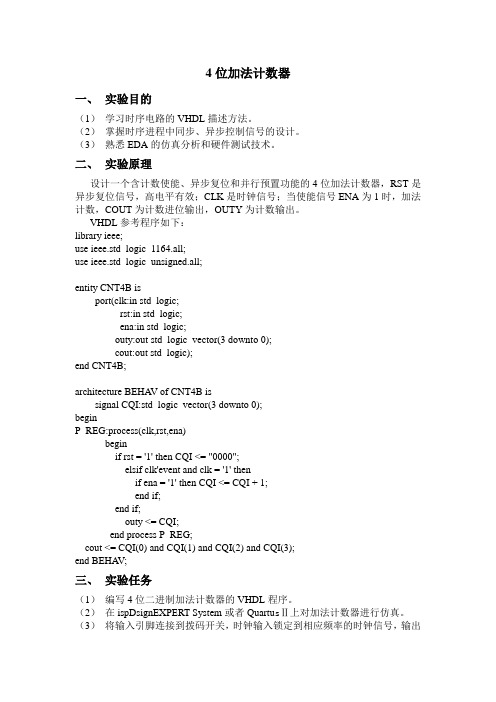

4位加法计数器一、实验目的(1)学习时序电路的VHDL描述方法。

(2)掌握时序进程中同步、异步控制信号的设计。

(3)熟悉EDA的仿真分析和硬件测试技术。

二、实验原理设计一个含计数使能、异步复位和并行预置功能的4位加法计数器,RST是异步复位信号,高电平有效;CLK是时钟信号;当使能信号ENA为1时,加法计数,COUT为计数进位输出,OUTY为计数输出。

VHDL参考程序如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity CNT4B isport(clk:in std_logic;rst:in std_logic;ena:in std_logic;outy:out std_logic_vector(3 downto 0);cout:out std_logic);end CNT4B;architecture BEHA V of CNT4B issignal CQI:std_logic_vector(3 downto 0);beginP_REG:process(clk,rst,ena)beginif rst = '1' then CQI <= "0000";elsif clk'event and clk = '1' thenif ena = '1' then CQI <= CQI + 1;end if;end if;outy <= CQI;end process P_REG;cout <= CQI(0) and CQI(1) and CQI(2) and CQI(3);end BEHA V;三、实验任务(1)编写4位二进制加法计数器的VHDL程序。

(2)在ispDsignEXPERT System或者Quartu sⅡ上对加法计数器进行仿真。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

西南科技大学

实验报告FPGA现代数字系统设计

实验题目:含异步清零和同步使能的4位加法计数器专业班级:

学生姓名:

学生学号:

实验时间:

指导教师:

实验二含异步清0和同步使能的4位加法计数器

一、实验目的:

学习时序电路的设计、仿真和硬件测试,进一步熟悉VHDL技术。

二、原理说明:

图2.1是一含计数使能、异步复位和计数值并行预置功能4位加法计数器,例2.1是其VHDL描述。

由图2-1所示,

4位锁存器;

rst是异步清0信号,高电平有效;

clk是锁存信号;

D[3..0]是4位数据输入端。

ENA是使能信号,当ENA为'1'时,多路选择器将加1器的输出值加载于锁存器的数据端;当ENA为'0'时将"0000"加载于锁存器。

图2-1含计数使能、异步复位和计数值并行预置功能4位加法计数器

三、实验内容:

1、在QuartusII上对例2-1进行编辑、编译、综合、适配、仿真。

说明例中各语句

的作用,详细描述示例的功能特点,给出其所有信号的时序仿真波形。

【例2-1】

module CNT4B(CLK,RST,ENA,CLK_1,RST_1,ENA_1,OUTY,COUT);//端口声明

input CLK,RST,ENA;

output CLK_1,RST_1,ENA_1;

output[3:0] OUTY;

output COUT;

reg[3:0] OUTY;

reg COUT;//寄存器变量OUTY,位宽为1

wire CLK_1;

wire RST_1;

wire ENA_1;

assign CLK_1 = CLK;

assign RST_1 = RST;

assign ENA_1 = ENA;

always@(posedge CLK or negedge RST) /*当CLK上升沿或者RST上升沿时,触发always模块执行*/

begin

if(!RST)

begin

OUTY<=4'b0000;

COUT<=1'b0;/*当复位信号等于0时,计数OUTY、COUT置0*/

end

else

if(ENA) /*当使能信号为1时,计数器计数工作*/

begin

OUTY<=OUTY+1;

COUT<=OUTY[0] & OUTY[1] & OUTY[2] & OUTY[3]; /*计数显示*/

end

end

endmodule

2保存计数器程序为CNT4B.vhd,进行功能仿真、全编译、时序仿真,如出现错误请按照错误提示进行修改,保证设计的正确性。

3锁定引脚

pin location DE2上的名称

ENA PIN_N25SW[0]

CLK PIN_G26KEY0

RST PIN_N23KEY1

OUTY[0]PIN_AC21LEDR[7]

OUTY[1]PIN_AA14LEDR[8]

OUTY[2]PIN_Y13LEDR[9]

OUTY[3]PIN_AA13LEDR[10]

COUT PIN_Y12LEDG[8]

CLK_1PIN_AE22LEDG[0]

RST_1PIN_AF22LEDG[1]

ENA_1PIN_AE23LEDR[0]

4下载

采用JATG方式进行下载,通过ENA,CLK,RST输入,观察的LEDR[0],LEDR[7],LEDR[8],LEDR[9],LEDR[10],LEDG[0],LEDG[1],LEDG[8]亮灭验证计数器的

逻辑功能。

5使用SIGNALTAP II对CNT4B计数器中的COUT, OUTY进行实时测试。

四、实验结果与分析

功能仿真:

时序编译:

时序仿真:

下载情况:

最终结果:

五、思考题

1、改写例2-1,用两个always语句实现模块功能?

答:module CNT4B(CLK,RST,ENA,CLK_1,RST_1,ENA_1,OUTY,COUT);

input CLK,RST,ENA;

output CLK_1,RST_1,ENA_1;

output[3:0] OUTY;

output COUT;

reg[3:0] OUTY;

reg COUT;

wire CLK_1;

wire RST_1;

wire ENA_1;

assign CLK_1 = CLK;

assign RST_1 = RST;

assign ENA_1 = ENA;

always@(posedge CLK or negedge RST)

begin

if(!RST)

begin

OUTY<=4'b0000;

COUT<=1'b0;

end

else

OUTY= OUTY+1;

always@(OUTY)

if(ENA)

begin

OUTY<=OUTY+2’b1;

COUT<=OUTY[0] & OUTY[1] & OUTY[2] & OUTY[3];

end

end

assign COUT<=OUTY[0] & OUTY[1] & OUTY[2] & OUTY[3];

endmodule

2、逻辑分析仪的功能是什么?它在FPGA设计中的作用是什么?简述SIGNALTAP II的使用流程。

答:逻辑分析仪可以监测硬件电路工作时的逻辑电平(高或低),并加以存储,用图形的方式直观地表达出来,便于用户检测,分析电路设计(硬件设计和软件设计) 中的错误。

逻辑分析仪在FPGA的作用主要是用于调试。

SIGNALTAP II的使用流程:设计人员在完成设计并编译工程后,建立SignalTap II (.stp)文件并加入工程、配置STP文件、编译并下载设计到FPGA、在Quartus II软件中显示被测信号的波形;在测试完毕后将该逻辑分析仪从项目中删除。