异步清零和同步时钟使能的4位加法计数器 实验报告

实验五 含异步清零和同步使能4位加法计数器的VHDL设计

实验五含异步清零和同步使能4位加法计数器的VHDL设计一、实验目的1掌握计数器的VHDL设计方法;2掌握异步复位和同步复位和使能的概念;3掌握寄存器性能的分析方法(即分析芯片所能达到的最高时钟频率)。

二、实验内容1异步复位4位加法计数器的设计;2同步复位4位加法计数器的设计。

3异步清0和同步时钟使能的4位加法计数器三、实验原理复位:给计数器一个初值叫复位,如果所给初值为0,则称复位为清零。

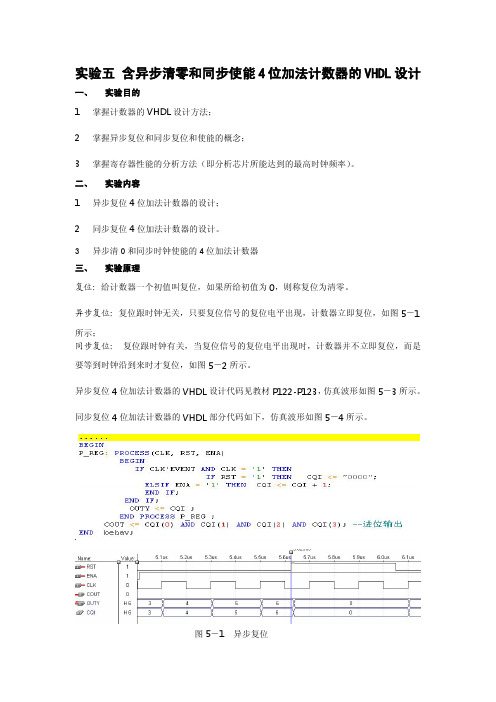

异步复位:复位跟时钟无关,只要复位信号的复位电平出现,计数器立即复位,如图5-1所示;同步复位:复位跟时钟有关,当复位信号的复位电平出现时,计数器并不立即复位,而是要等到时钟沿到来时才复位,如图5-2所示。

异步复位4位加法计数器的VHDL设计代码见教材P122-P123,仿真波形如图5-3所示。

同步复位4位加法计数器的VHDL部分代码如下,仿真波形如图5-4所示。

.图5-1异步复位图5-2同步复位图5-3异步复位计数器仿真波形图5-4同步复位计数器仿真波形四、实验步骤(一)异步复位4位加法计数器的设计1建立一个设计工程,工程名为CNT4B;2打开文本编辑器,建立一个VHDL设计文件,其VHDL代码见教材P164中的例6-20,文件名存为CNT4B.VHD。

注意文件的扩展名要选为.vhd,而且要求工程名、文件名和设计实体名必须相同。

3选器件:ACEX1K,EP1K30TC144-3(旧)或Cyclone,EP3C40Q240C8目标芯片。

4编译;5建立波形文件,然后保存,其文件名必须与工程名一致;【波形设置:①设置仿真时间为10us:②设置输入信号的波形:时钟周期设置为200ns,其他输入信号的波形设置参看图6-3。

】6仿真,观察输出波形是否正确;7时序分析:分析芯片所能达到的最高时钟频率。

【打开时序分析器,然后执行菜单命令:analysis/register performance/start,可以看到最高时钟频率为100.00MHZ】(二)同步复位4位加法计数器的设计8建立一个设计工程,工程名为CNT4B_SYS;9打开文本编辑器,建立一个VHDL设计文件,其VHDL代码参看异步计数器代码和实验原理中的参考代码,文件名存为CNT4B_SYS.VHD。

实验一2 含异步清0

1)根据DE2_pin_assignments文件内容、格式 已制作本设计引脚对应文件的引脚锁定文 件:CNT4B.csv 2) 由Assignments->Import Assignment,打开 对话框,调入引脚对应文件即可。

• 进行编译、下载,通过实验,检查引脚锁定是 否正确。

• 将波形文件存盘为CNT4B.vwf

• 设定CNT4B.v是目前的顶层文件

• 由Processing->start->start annlysis & elaboration对程序进行初步的分析

• 由view->utility window->node finder,得到 如下对话框,

Filter中选择Pins: all 然后按List得到输 入输出端口列表, 用鼠标将它们拖到 波形编辑窗口

• 将instance框中的名字改为CNT4B(选中右击选择Rename Instance)

• 为看清楚,按

,将窗口浮动

• 在CNT4B框双击(Double-click to add node), 弹出节点(noder)对话框,Filter项选择all, 然后点击List

选中要观察的端口COUT、OUTY然后单击>加 入,点OK。

功能仿真

• 由Processing->generate functional simulation netlist,提取功能仿真的网表 • 由assigments->settings,对仿真工具设定为 功能仿真,并将激gt; start simulation 进行功能仿 真,并对结果进行分析。

• 锁好引脚,进行全编译(compile),重新布 局布线,时序仿真 引脚锁定,仿真结果核对无误后,准备下载

实验二含异步清0和同步使能的4位加法计数器

实验二含异步清0和同步使能的4位加法计数器一、实验目的:学习时序电路的设计、仿真和硬件测试,进一步熟悉VHDL技术。

二、原理说明:图2.1是一含计数使能、异步复位和计数值并行预置功能4位加法计数器,例2.1是其VHDL描述。

由图2-1所示,4位锁存器;rst是异步清0信号,高电平有效;clk是锁存信号;D[3..0]是4位数据输入端。

ENA是使能信号,当ENA为'1'时,多路选择器将加1器的输出值加载于锁存器的数据端;当ENA为'0'时将"0000"加载于锁存器。

图2-1含计数使能、异步复位和计数值并行预置功能4位加法计数器三、实验内容:1、在QuartusII上对例2-1进行编辑、编译、综合、适配、仿真。

说明例中各语句的作用,详细描述示例的功能特点,给出其所有信号的时序仿真波形。

【例2-1】module CNT4B(CLK,RST,ENA,CLK_1,RST_1,ENA_1,OUTY,COUT);input CLK,RST,ENA;output CLK_1,RST_1,ENA_1;output[3:0] OUTY;output COUT;reg[3:0] OUTY;reg COUT;wire CLK_1;wire RST_1;wire ENA_1;assign CLK_1 = CLK;assign RST_1 = RST;assign ENA_1 = ENA;always@(posedge CLK or negedge RST)beginif(!RST)beginOUTY<=4'b0000;COUT<=1'b0;endelseif(ENA)beginOUTY<=OUTY+1;COUT<=OUTY[0] & OUTY[1] & OUTY[2] & OUTY[3];endendendmodule2保存计数器程序为CNT4B.vhd,进行功能仿真、全编译、时序仿真,如出现错误请按照错误提示进行修改,保证设计的正确性3锁定引脚4下载采用JATG方式进行下载,通过ENA,CLK,RST输入,观察的LEDR[0],LEDR[7],LEDR[8],LEDR[9],LEDR[10],LEDG[0],LEDG[1],LEDG[8]亮灭验证计数器的逻辑功能。

含异步清规和同步使能的加法计数器

实验三含异步清零和同步使能的加法计数器一、实验目的1、了解二进制计数器的工作原理。

2、进一步熟悉QUARTUSII软件的使用方法和VHDL输入。

3、时钟在编程过程中的作用。

二、实验原理二进制计数器中应用最多、功能最全的计数器之一,含异步清零和同步使能的加法计数器的具体工作过程如下:在时钟上升沿的情况下,检测使能端是否允许计数,如果允许计数(定义使能端高电平有效)则开始计数,否则一直检测使能端信号。

在计数过程中再检测复位信号是否有效(低电平有效),当复位信号起作用时,使计数值清零,继续进行检测和计数。

其工作时序如图3-1所示:图3-1 计数器的工作时序三、实验内容本实验要求完成的任务是在时钟信号的作用下,通过使能端和复位信号来完成加法计数器的计数。

实验中时钟信号使用数字时钟源模块的1HZ信号,用一位拨动开关K1表示使能端信号,用复位开关S1表示复位信号,用LED模块的LED1~LED11来表示计数的二进制结果。

实验LED亮表示对应的位为‘1’,LED灭表示对应的位为‘0’。

通过输入不同的值模拟计数器的工作时序,观察计数的结果。

实验箱中的拨动开关、与FPGA的接口电路,LED灯与FPGA的接口电路以及拨动开关、LED与FPGA的管脚连接在实验一中都做了详细说明,这里不在赘述。

数字时钟信号模块的电路原理如图3-2所示,表3-1是其时钟输出与FPGA的管脚连接表。

图3-2 数字时钟信号模块电路原理表3-1 数字时钟输出与FPGA的管脚连接表按键开关模块的电路原理如图3-3所示,表3-2是按键开关的输出与FPGA的管脚连接表。

图3-3 按键开关模块电路原理信号名称FPGA I/O名称核心板接口管脚号功能说明S[0] Pin_AF5 JP1_91 ‘S1’SwitchS[1]Pin_AH6 JP1_93 ‘S2’SwitchS[2]Pin_AH7 JP1_95 ‘S3’SwitchS[3]Pin_AH8 JP1_97 ‘S4’SwitchS[4]Pin_AG10 JP1_99 ‘S5’SwitchS[5]Pin_AG11 JP1_101 ‘S6’SwitchS[6]Pin_AH14 JP1_90 ‘S7’SwitchS[7] Pin_AG7 JP1_92 ‘S8’SwitchS[8]Pin_AG8 JP1_94 ‘S9’SwitchS[9]Pin_AF9 JP1_96 ‘S10’SwitchS[10]Pin_AH10 JP1_98 ‘S11’SwitchS[11] Pin_AH11 JP1_100 ‘S12’Switch表3-2 按键开关与FPGA的管脚连接表四、实验步骤1、打开QUARTUSII软件,新建一个工程。

四位全加器

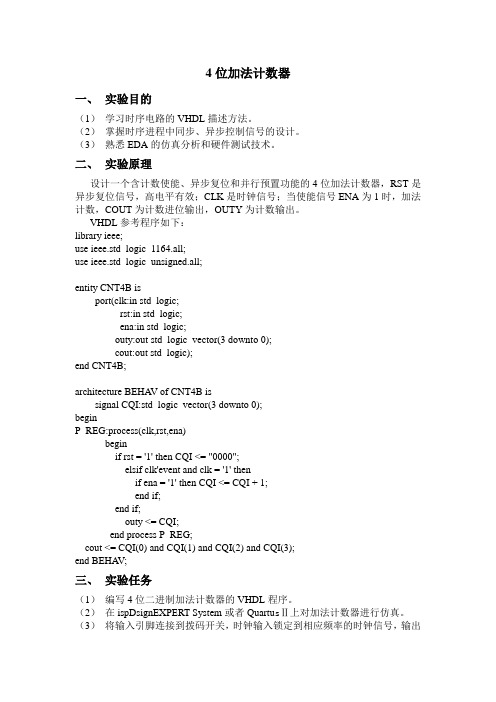

4位加法计数器一、实验目的(1)学习时序电路的VHDL描述方法。

(2)掌握时序进程中同步、异步控制信号的设计。

(3)熟悉EDA的仿真分析和硬件测试技术。

二、实验原理设计一个含计数使能、异步复位和并行预置功能的4位加法计数器,RST是异步复位信号,高电平有效;CLK是时钟信号;当使能信号ENA为1时,加法计数,COUT为计数进位输出,OUTY为计数输出。

VHDL参考程序如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity CNT4B isport(clk:in std_logic;rst:in std_logic;ena:in std_logic;outy:out std_logic_vector(3 downto 0);cout:out std_logic);end CNT4B;architecture BEHA V of CNT4B issignal CQI:std_logic_vector(3 downto 0);beginP_REG:process(clk,rst,ena)beginif rst = '1' then CQI <= "0000";elsif clk'event and clk = '1' thenif ena = '1' then CQI <= CQI + 1;end if;end if;outy <= CQI;end process P_REG;cout <= CQI(0) and CQI(1) and CQI(2) and CQI(3);end BEHA V;三、实验任务(1)编写4位二进制加法计数器的VHDL程序。

(2)在ispDsignEXPERT System或者Quartu sⅡ上对加法计数器进行仿真。

四位加法器实验报告

四位加法器实验报告四位加法器实验报告一、引言在数字电路的学习中,加法器是一个非常重要的基础电路。

本次实验旨在通过设计和实现四位加法器,加深对数字电路原理的理解,并掌握加法器的设计方法和实现过程。

二、实验目的1. 理解加法器的原理和工作方式;2. 掌握加法器的设计方法和实现过程;3. 学会使用逻辑门电路和触发器构建加法器;4. 验证加法器的正确性和稳定性。

三、实验原理1. 半加器半加器是最基本的加法器,用于实现两个一位二进制数的相加。

其逻辑电路如下:(插入半加器电路图)2. 全加器全加器是由两个半加器和一个或门构成,用于实现三个一位二进制数的相加。

其逻辑电路如下:(插入全加器电路图)3. 四位加法器四位加法器是由四个全加器和一些其他逻辑门组成,用于实现四个四位二进制数的相加。

其逻辑电路如下:(插入四位加法器电路图)四、实验步骤1. 按照电路图连接逻辑门和触发器,搭建四位加法器电路;2. 使用开关设置输入数据,观察输出结果;3. 验证加法器的正确性,将不同的输入数据相加,并手动计算结果进行对比;4. 测试加法器的稳定性,观察输出结果是否随着时间稳定。

五、实验结果与分析通过实验,我们成功搭建了四位加法器电路,并进行了多组数据的测试。

实验结果表明,加法器能够正确地进行四个四位二进制数的相加,并输出正确的结果。

同时,实验中观察到输出结果在一段时间后稳定下来,验证了加法器的稳定性。

六、实验总结本次实验通过设计和实现四位加法器,加深了对数字电路原理的理解,并掌握了加法器的设计方法和实现过程。

通过实验验证了加法器的正确性和稳定性,提高了实际操作能力和解决问题的能力。

同时,实验中还发现了一些问题,比如电路连接错误、输入数据设置错误等,这些问题在实验中及时发现和解决,也对实验结果的准确性起到了保障作用。

在今后的学习中,我们将进一步深入研究数字电路的原理和应用,不断提高自己的实验技能和创新能力。

希望通过这次实验,能够为我们的学习和未来的工作打下坚实的基础。

EDA技术与FPGA应用设计实验报告--4位二进制加法计数器

本科实验报告课程名称:EDA技术与FPGA应用设计实验项目:4位二进制加法计数器实验地点:跨越机房专业班级:学号:学生姓名:指导教师:2012年6 月20 日一、实验目的:1.学习时序电路的VHDL描述方法。

2.掌握时序进程中同步、异步控制信号的设计。

3.熟悉EDA的仿真分析和硬件测试技术。

二、实验原理:设计一个含计数使能、异步复位和并行预置功能的4位加法计数器,RST是异步复位信号,高电平有效;CLK是时钟信号;当使能信号ENA为“1”'时,加法计数,COUT为计数进位输出,OUTY为计数输出。

三、实验内容:1.编写4位二进制加法计数器的VHDL程序。

2.在ispDesignEXPERT System上对编码器进行仿真。

3.将输入引脚连接到拨码开关,时钟输入锁定到相应频率的时钟信号,输出连接到发光二极管,下载后在实验板上验证其功能,记录实验结果。

四、实验程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALLUSE IEEE.STD_LOGIC_UNSIGNED.ALLENTITY CNT4B ISPORT(CLK:IN STD_LOGIC;RST:IN STG_LOGIC;ENA:IN STD_LOGIC;OUTY:OUT STD_LODGIC_VECTOR(3 DOWNTO 0);COUT:OUT STD_LOGIC);END CNT4B;ARCHITECTURE BEHAV OF CNT4B ISSIGNAL CQI:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINP_REG: PROCESS(CLK,RST,ENA)BEGINIF RST=’1’THEN CQI<=”0000”;ELSIF CLK’EVENT AND CLK=’1’THENIF ENA= ’1’THEN CQI<=CQI+1;ENG IF;END IF;OUTY <= CQI;END PROCESS P_REG;COUT<= CQI(0) AND CQI(1) AND CQI(2) AND CQI(3); END BEHAV;五、仿真结果:1.时序图:2.功能图:六、心得体会:通过本实验,让我对VHDL编程有了一定的了解和认识,让我初步学习了VHDL的编写及调试过程,实验中有错误产生,但是经过细心的改正,解决了问题,希望下次实验能有更大的提高。

含异步清零和同步时钟使能的4位加法器

含异步清零和同步时钟使能的4位加法器宁波⼯程学院电信学院EDA系统设计与实践实验报告实验名称含异步清零和同步时钟使能的4位加法器班级电科(系统设计)08-2 姓名学号 0840*******组员姓名实验⽇期2011-5-12指导⽼师实验四含异步清零和同步时钟使能的4位加法器⼀.实验⽬的学习计数器的设计,仿真和硬件测试。

进⼀步熟悉VHDL的编程⽅法。

⼆.实验内容本实验的内容是Quartus 11建⽴⼀个含计数使能、异步复位的4位加分计数器,SmartSOPC试验箱上进⾏硬件测试,由KEY1控制技术使能端ena并由LED指⽰,KEY2控制复位端rst并由LED2指⽰。

计数值由数码管指⽰。

三.实验原理Rst是异步清零信号,⾼电平有效。

Ema为是能端,能开始与暂停程序,当ena为0时,能所存信号。

四.实验步骤(1)破解Quartus 11;(2)建⽴⼯程:启动Quartus 11,建⽴空⽩⼯程。

命名为giui;(3)创建源程序⽂件:新建VHDL源程序⽂件giui,输⼊程序代码并保存,进⾏编译,若在编译过程中发现错误,则找出并更正,直⾄编译成功。

(4)编译并运⾏:编译并运⾏程序或者原理图,编译⽆误后,进⾏引脚锁定;(5)外部连接⽅式跟第2节相似。

五.实验程序⼀.在⼀个数码管上显⽰0~Flibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity giui isport(clk48:in std_logic;key_2bit:in std_logic;dig_4bit:out std_logic_vector(3 downto 0);seg:out std_logic_vector(7 downto 0));end giui;architecture m1 of giui issignal num1:std_logic_vector(3 downto 0);signal cnt:std_logic_vector(23 downto 0);signal t: std_logic;signal q:std_logic;beginfre:process(clk48,cnt)beginif clk48'event and clk48='1' thencnt<=cnt+1;end if;q<=cnt(23);end process fre;coun:process(q)beginif q'event and q='1' thenif t='1' then num1<="0000";elsenum1<=num1+1;end if;end if;end process;SEG<= "11000000" when num1="0000" else "11111001" when num1="0001" else "10100100" when num1="0010" else"10110000" when num1="0011" else"10011001" when num1="0100" else"10010010" when num1="0101" else"10000010" when num1="0110" else"11111000" when num1="0111" else"10000000" when num1="1000" else"10010000" when num1="1001" else"10001000" when num1="1010" else"10000011" when num1="1011" else"01000110" when num1="1100" else"10100001" when num1="1101" else"10000110" when num1="1110" else"11111111";dig_4bit<="1110" when t='1' else"1111" when t='0';end m1;⼆.4位加法器Library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity sun_adder isport(clk:in std_logic;key:in std_logic;led1:out std_logic;dig:out std_logic_vector(3 downto 0);seg:out std_logic_vector(7 downto 0)); end sun_adder;architecture a of sun_adder issignal tmp:std_logic_vector(23 downto 0); signal tmp1:std_logic_vector(10 downto 0); signal address,pp:std_logic_vector(3 downto 0); signal p:std_logic_vector(1 downto 0);signal tt,t,q,q1: std_logic;signal num1,num2,num3,num4:std_logic_vector(3 downto 0);beginprocess(clk)beginif clk'event and clk='1' then tmp<=tmp+1;tmp1<=tmp1+1;end if;end process;q<=tmp(23);q1<=tmp1(10);process(q1)beginif q1'event and q1='1' then case p iswhen "00"=>pp<="1110";when "01"=>pp<="1101";when "10"=>pp<="1011";when others=>pp<="0111";end case;dig<=pp;case pp iswhen "1110"=>address<=num1;when "1101"=>address<=num2;when "1011"=>address<=num3;when others=>address<=num4;end case;p<=p+1;end if;end process;process(key)beginIf key'event and key='1' thent<= not t;end if;end process;process(q)beginif q'event and q='1' thenif t='1' then num1<="0000";num2<="0000";num3<="0000";num4<="0000";else num1<=num1+1;if num1="1001" then num1<="0000";tt<='1';if num2="1001" then num2<="0000";if num3="1001" then num3<="0000";if num4="1001" then num4<="0000";else num4<=num4+1; end if;else num3<=num3+1; end if;else num2<=num2+1; `1212212345123451233123`12341234123412341312end if; else num1<=num1+1;tt<='0'; end if; end if;end if;end process;seg<= "11000000" when address="0000" else"11111001" when address="0001" else"10100100" when address="0010" else"10110000" when address="0011" else"10011001" when address="0100" else"10010010" when address="0101" else"10000010" when address="0110" else "11111000" when address="0111" else "10000000" when address="1000" else "10010000" when address="1001" else "11111111";led1<='0' when tt='1' else'1' when tt='0';end a;六.实验现象。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

异步清零和同步时钟使能的4位加法计数器

一、实验目的:

学习计数器的设计、仿真和硬件测试,进一步熟悉VHDL设计技术。

二、实验原理

本试验中所要设计的计数器,由4位带异步清零的加法计数器和一个4位锁存器组成。

其中,rst是异步清零信号,高电平有效;clk是计数时钟,同时也是锁存信号;ENA为计数器输出使能控制。

当ENA为‘1’时,加法计数器的输出值加载于锁存器的数据端,;当ENA为‘0’时锁存器输出为高阻态。

当计数器输出“1111”时,进位信号COUT为“1”。

三、实验内容

1)画出该计数器的实体框图0

2)用VHDL语言完成上述计数器的行为级设计。

------------------------------------------------------------------------------------------------------- 程序:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT4 IS

PORT (RST,CLK,ENA:IN STD_LOGIC;

COUT: OUT STD_LOGIC;

OUTY :OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END CNT4;

ARCHITECTURE behv OF CNT4 IS

BEGIN

PROCESS (RST,ENA,CLK)

VARIABLE CQI :STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

IF RST='1' THEN CQI :=(OTHERS =>'0');

ELSIF CLK'EVENT AND CLK='1' THEN

IF ENA ='1' THEN

IF CQI < 15 THEN CQI:=CQI+1;

ELSE CQI :=(OTHERS =>'0');

END IF;

END IF;

END IF;

IF CQI =15 THEN COUT<='1';

ELSE COUT <='0';

END IF;

OUTY <=CQI;

END PROCESS;

END behv;

3)用QuartusII对上述设计进行编译、综合、仿真,给出其所有信号的仿真波形和时序分析数据。

--------------------------------------------------------------------------------------------------

仿真波形:

引脚锁定:

信号旧试验箱新试验箱No.5

管脚号连接的器件管脚号连接的器件clk 43 Clk1 153 CLK2

rst 35 开关2 234 键2

ena 30 开关1 233 键1

Outy(3) 29 LED12 1 LED1

Outy(2) 28 LED11 2 LED2

Outy(1) 27 LED10 3 LED3

Outy(0) 25 LED9 4 LED4

cout 23 LED7 6 LED6

实验结果

RST拨到高电平时,计数器清0,拨到低电平时可以计数。

ENA使能端为高电平时计数器工作,为低电平时置数。

当计数器工作时,数码管依次显示0、1、2、3、4、5、6、7、8、9、A、B、C、D、E、F,满位时LED灯闪亮一下,然后数码管自动清0.。