异步复位,同步释放的方式,而且复位信号低电平有效

FPGA复位的可靠性设计方法

对F P G A芯 片而 言 , 在 给 芯片 加 电工 作 前 , 芯 片 内 部 各个 节点 电位 的变 化情 况均 不确 定 、 不可 控 , 而 这种 不确 定且 不 可控 的情 况会使 芯 片在 上 电后 的工 作状 态 出现错误 。 因此 , 在 F P G A的设 计 中 , 为保 证 系统 能可

,

位端 口 则在实 现 同步 复位 电路 时可 直 接调 用 同步 复

,

复 位 设 计 方 法 分 类

复 位 的 目的是在 仿真 时将 设计 强 制定位 在 一个 可 知状 态 , 合理 选 择 复 位 方式 是 电路 设 计 的 关 键 。根 据 与 系统 时钟域 的关 系 , 复 位 电路 可 分 为 同 步 复位 和 异 步复 位 。 同步复 位是 指复 位信 号只 在 时钟沿 到来 时, 才有 效 。否则 , 无 法完 成对 系统 的复位 工作 。异步 复位 是指 无论 时钟 沿 是否 到来 , 只要 复 位信 号有 效 , 便

T N 7 9 文献标识码 A 文章编 号 1 0 0 7— 7 8 2 0 ( 2 0 1 3 ) 1 0—1 2 5— 0 3 中图分类号

Re s e a r c h o n Re l i a bi l i t y De s i g n Me t ho d s o f FPGA Re s e t Lo g i c

,

除电源开关过程 中引起 的抖动影 响 , 复位信号需在 电 源稳定后经过一定的延时才能撤销¨ , F P G A 的复 位

Verilog笔记.5.同步、异步

Verilog笔记.5.同步、异步在数字电路中经常有同步synchronism、异步asynchronism的概念。

异步指输⼊信号和时钟⽆关;同步指输⼊信号和时钟信号有关,实际上就是输⼊信号和时钟信号进⾏了与运算或者与⾮运算。

实际开发中,经常有同步清零、异步清零、同步复位、异步复位等概念,下⾯就给与相关代码演⽰。

简单的异步复位1always @ (posedge clk or negedge rst_n)2if(!rst_n) b <= 1'b0;3else b <= a;简单的同步复位1always @ (posedge clk)2if(!rst_n) b <= 1'b0;3else b <= a;PS:同步复位信号RST必须⾄少长于⼀个时钟周期CLK,否则,这个复位信号引起的变化是不会被检测到的!异步复位、同步释放1always @ (posedge clk)2 rst_nr <= rst_n; //现将异步复位信号⽤同步时钟打⼀拍34always @ (posedge clk or negedge rst_nr)5if(!rst_nr) b <= 1'b0;6else b <= a;78always @ (posedge clk or negedge rst_nr)9if(!rst_nr) c <= 1'b0;10else c <= b;同步复位和异步复位的区别就在于前者的复何信号不能出现在always语句的敏感信号表中,⽆论是同步复位还是异步复位,always语句的结构都是if(Reset)...else... ,否则,综合⼯具将不能正确的综合所有always语句中的赋值最好采⽤⾮阻塞赋值语,否则,可能会导致仿真与综合的不⼀致”。

编码规范——精选推荐

编码规范编码规范整理初稿1命名规范1.1顶层⽂件命名规范级别: 规定说明: 采⽤芯⽚型号名+top的命名⽅式⽰例:xxxx_top.v1.2⼦系统顶层命名规范级别: 规定说明: 采⽤⼦系统缩写+top的命名⽅式⽰例:xxxx_top.v1.3存储器模块命名规范级别: 规定说明: RAM存储器模块的⽂件命名采⽤下⾯的形式:时钟类型_Ram类型_深度x位宽[w_深度x位宽r][_reg].v时钟类型:读写时钟同步⽤com,异步⽤diffRam类型:对于双⼝ram为dpram,对于单端⼝ram为ram,对于单端⼝rom为rom,对于FIFO为fifo,对于移位寄存器为shift;_深度x位宽:⽤于描述写端⼝的位宽以及该位宽对应的深度;[w_深度x位宽r]:可选字段,⽤于描述读端⼝的位宽以及该位宽度对应的深度,若存储器读写端⼝位宽⼀致,或存储器只读,该字段可省略;[_reg]:可选字段,采⽤寄存器输出的使⽤需要以_reg为结尾进⾏标⽰,输出不采⽤寄存器输出的则不使⽤.⽰例:1.4模块命名规范其他约束级别: 规定说明: ⼀个设计⽂件只包含⼀个模块,为了⽅便阅读查找,⽂件名应与⾥⾯的模块(module)名相同⽰例:1.5⽂件名应由字母、数字及下划线组成,⾸字符应为字母级别: 规定说明: 命名只能由26个英⽂字母(a-z,A-Z)、数字(0-9)或者下划线( _ )组成。

不允许使⽤破折号和连续的下划线。

第⼀个字符只能使⽤字母,不能使⽤下划线。

⽰例:1.6信号名使⽤有意义的名字,不宜超过32个字符级别: 规定说明: ⽂件名和信号名应尽量做到望⽂⽣义,⾔简意赅,同时不宜超过32个字符。

⽰例:1.7⽤下划线分开多个单词级别: 规定说明: 由多个字符串组成的⽂件名或者信号名,每个字之间要⽤下划线分开说明:可读性⽰例:1.8常量应⽤⼤写字母表⽰,推荐以“C_”打头级别: 规定说明: 常量应⼤写。

包括参量(parameter)名、⽂本宏名都要⼤写说明:提⾼可读性⽰例:1.9模块内部的信号以“S_”打头,其他字母建议⼩写级别: 规定说明: 对内部定义的信号,命名以”S_”打头,其他字母⼩写。

IC设计中同步复位与

IC设计中同步复位与异步复位的区别异步复位是不受时钟影响的,在一个芯片系统初始化(或者说上电)的时候需要这么一个全局的信号来对整个芯片进行整体的复位,到一个初始的确定状态。

而同步复位需要在时钟沿来临的时候才会对整个系统进行复位。

请注意,如果芯片是有多个时钟的系统,那么如何保证不同时钟域的电路能够“同时”复位将会是一个重要的问题,此外,如果你的时钟是一个低频时钟,那么在这个系统(包括其他芯片)上电时如何保证能和其他芯片同时复位?硬件全局异步复位是必要的,请注意这里加上了“全局”,这是因为异步复位既然要对整个芯片“同时”复位,那么布线延时绝不能不考虑,使用FPGA设计时芯片的异步复位必须要走全局网络。

再提醒一点,芯片中最好不要出现多个异步复位。

一个关键原因是对于FPGA而言,多个异步复位信号难以实现前面要求的“全局网络”。

异步复位最大的优点是, 数据通路就可以不依赖于时钟而确保清洁可控。

然而, 异步复位也有其固有的缺陷。

异步复位设计的DFT (可测性设计) 与STA (静态时序分析) 的复杂性要高于同步复位设计; 但异步复位中最严重的问题是, 如果异步复位信号在触发器时钟有效沿附近“释放”(复位信号从有效变为无效) 的话, 可能会导致触发器输出的亚稳态。

同步复位和异步复位的比较(转载)无论同步还是异步复位,在对触发器时序进行分析的时候,都要考虑复位端与时钟的相位关系。

对于同步复位,复位信号可以理解为一个普通的数据信号,它只有在时钟的跳变沿才会其作用,一般只要复位信号持续时间大于一个时钟周期,就可以保证正确复位。

对于异步复位,复位可以在任何时候发生,表面上看跟时钟没有关系,但真实情况是异步复位也需考虑时钟跳变沿,因为时钟沿变化和异步复位都可以引起Q端数据变化,如果异步复位信号跟时钟在一定时间间隔内发生变化,Q值将无法确定,即亚稳态现象。

这个时候既是异步复位信号持续时间再长都没有办法,因为不定态已经传递下去。

数字化设计与制造技术面试基本问题有哪些

数字化设计与制造技术面试基本问题有哪些1.描述对芯片设计流程的理解目前主要接触的是前端设计,主要包括规格制定,客户向芯片设计公司提出设计要求;芯片公司根据客户需求进行方案设计和架构实现,划分具体模块;然后就是HDL编码,使用硬件描述原因呢将模块功能使用代码描述实现,也就是将实际的硬件电路通过HDL 语言编写出来,形成RTL级代码;接着就是仿真验证,检验编码设计的正确性,检验的标准是前面设计的规格;逻辑综合,仿真验证通过,进行逻辑综合。

结果是把HDL代码翻译成门级网表netlist,综合后需要再次进行仿真验证;STA静态时序分析,主要再时序上对电路进行验证,检车电路上是否存在建立时间和保持时间的违例;形式验证,这个不是很懂。

后端的就没怎么接触了,验证完之后就开始板调了。

2.谈谈你所了解的低功耗设计的方法和思路在CMOS技术中,动态功耗与门和金属引线的寄生电容充放电有关,在电容中消耗电流的一般方程式I=V*C*F其中I是电流,v是电压,C是电容,F是频率。

在FPGA设计中,电压通常是固定的,只留下电容C和频率f对电流的操纵,电容直接与随时被触发的门的数量以及连接这些门的布线长度有关,频率f直接与时钟频率有关。

为了是输入器件的功耗最小化,最小化驱动输入的信号上升和下降的时间,动态功耗随着电压的平方减弱,但是降低电压对性能有负面的影响。

3.何为同步复位和异步复位,怎么理解同步复位异步释放?与时钟同步的复位就是同步复位,与时钟无关的就是异步复位,在FPGA中的器件有不同的同步或异步器件,设计时根据具体情况具体分析。

所谓异步复位和同步释放,是指复位信号是异步有效的,即复位的发生与clk无关。

后半句“同步释放”是指复位信号的撤除(释放)则与clk相关,即同步的。

异步复位与同步释放

异步复位与同步释放很多时候,我们都希望系统一上电以及在仿真开始的时候所有寄存器都有一个已知的状态。

复位有两种方式,即同步复位和异步复位。

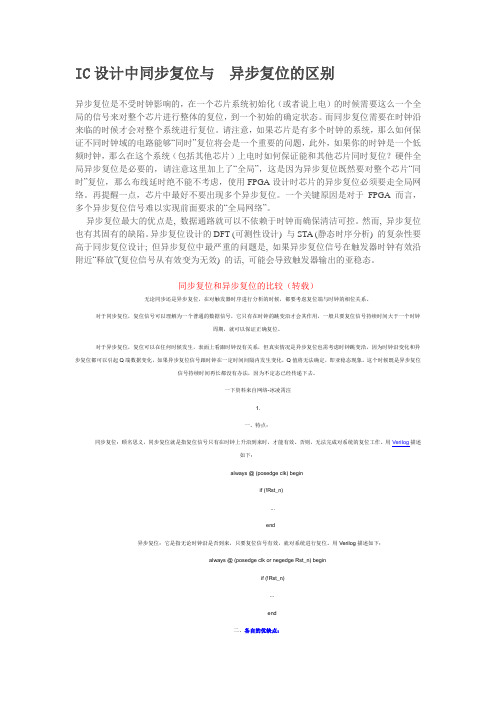

同步复位:“同步”的意思是和工作时钟同步。

也就是说当时钟的上升沿(下降沿)来到时检测到按键的复位操作才有效,否则无效。

如下图所示为同步低复位波形。

异步复位:“异步”的意思是和工作时钟不同步。

也就是说寄存器的复位不关心时钟的上升沿(下降沿)是否到来,只要有检测到按键被按下,就立刻执行复位操作。

如下图所示为同步低复位波形。

同步复位还是异步复位我们以D触发器为例来说明Inter(Altera)的器件是用同步复位好还是异步复位好。

先来看一下同步复位D触发器的RTL代码,如下所示://---------------------------------01module test(02 input wire sclk ,03 input wire rst_syncn ,04 input wire d ,0506 outputreg q07);0809always@(posedge sclk)10 if(rst_sync_n ==1'b0)11 q <=1'b0;12 else13 q <= d;1415endmodule//--------------------------------在Quartus工具中编写完RTL后点击“Start Analysis & Synthesis”图标进行分析和综合。

然后双击“Netlist Viewers”下的“RTL Viewer”查看RTL视图。

如下图所示,可以看到一个 D触发器的结构,也可以称为寄存器,但是还附加了一个选择器,用于同步复位的控制。

点击“Start Compilation”图标全编译进行布局布线,完成后我们可以看到“Flow Summary”资源使用量,如下图所示,可以看到使用了LE中的一个组合逻辑资源和一个时序逻辑资源。

基于FPGA的洗衣机控制器设计

课题:基于FPGA的洗衣机控制器前言一、洗衣机控制器主要内容l.任务要求和内容设计制作一个洗衣机的正反转定时控制线路。

1)控制洗衣机的电机作如下运转定时开始――正转10S――暂停5S――反转10S――暂停5S――定时到停止定时未到2)用2位七段数码管显示定时时间(S)。

2.洗衣机控制器的使用步骤:(1)电路上电后,在Start拨码开关未闭合前可以由UpKey和DownKey按键开关“+”“-”设置总的工作时间,确定洗衣机控制器工作允许时间。

(2)设定好允许工作时间后,闭合Start开关,洗衣机控制器开始工作。

(3)可以看见指示正转LED灯亮10s,停转LED灯亮5S,反转LED灯亮10s,停转LED亮5s,如此反复直至工作允许时间为0,蜂鸣器发出警报。

二、设计原理简介洗衣机控制器的设计主要是时序控制和定时器的设计,由一片FPGA和外围电路构成电器控制部分。

FPGA接收键盘的控制命令,控制洗衣机的正转、反转、停机和定时时间为0报警的工作状态、控制并显示工作状态以及显示定时时间。

对FPGA芯片的编程采用模块化的Verilog HDL (硬件描述语言)进行设计,设计由分频模块,按键消抖模块,定时时间自减模块,时序中心控制模块,数码管显示模块组成,顶层实现整个芯片的功能。

顶层使用原理图实现,底层由Verilog HDL语句实现。

FPGA的输入时钟为20M hz,因此使用了分频模块输出1hz的方波给定时器设定自减模块提供每1s自减1的信号,定时器模块输出的自减值输入给数码管显示译码模块和时序控制模块,通过译码模块定时器的值可以在数码管上显示,同时定时器的值输入到时序控制模块由此可以控制洗衣机的正转、反转、停机和报警工作方式。

通过按键消抖模块可以准确无抖动的设定定时器的工作时间。

目录一、前言 (2)二、目录 (3)三、正文 (4)3.1洗衣机控制器的整体框图及原理 (4)3.2洗衣机控制电路单元模块设计和仿真 (5)3.2.1按键消抖模块的设计 (5)3.2.2时钟分频模块的设计 (6)3.2.3定时器设定和自减模块的设计 (7)3.2.4时序中心控制模块的设计 (8)3.2.5数码管显示译码模块的设计 (9)四、电路调试 (11)五、结束语和心得体会 (12)六、参考文献 (13)七、附录 (13)7.1 FPGA系统板部分原理图 (13)7.2 FPGA系统板PCB图 (15)三、正文3.1 洗衣机控制器的整体框图及原理:基于fpga的洗衣机控制器电路主要由五大模块组成,分别为按键消抖模块,时钟分频模块,定时器设定和自减模块,时序中心控制模块,数码管显示译码模块。

数字IC面试题

注:红色为不会数字部分逻辑同步复位和异步复位:同步复位:同步复位仅在有效的时钟沿时对触发器复位,该复位信号经过组合逻辑馈送到触发器的D输入端。

同步复位优缺点:1)、优点:同步复位可以保证100%同步,可以对小的复位毛刺滤波;同步复位可以在时钟周期之间,对逻辑等式产生的毛刺进行滤波;a、有利于仿真器的仿真b、可以使所设计的系统成为100%的同步时序电路,这便大大有利于时序分析,而且综合出来的fmax一般较高。

c、因为他只有在时钟有效电平到来时才有效,所以可以滤除高于时钟频率的毛刺2)、缺点:同步复位有时需要脉冲展宽,用以保证时钟有效期间有足够的复位宽度;同步复位将复位信号经过组合逻辑馈送到数据输入端,从而增加了数据通道使用组合逻辑门数和相应的时延;a、复位信号的有效时长必须大于时钟周期,才能真正被系统识别并完成复位任务。

同时还要考虑,诸如:clk skew,组合逻辑路径延时,复位延时等因素。

b、由于大多数的逻辑器件的目标库内的DFF都只有异步复位端口,所以,倘若采用同步复位的话,综合器就会在寄存器的数据输入端口插入组合逻辑,这样就会耗费较多的逻辑资源。

C. An active clock is essential for a synchronous reset design. Hence you can expect more power consumption.异步复位:它是指无论时钟沿是否到来,只要复位信号有效,就对系统进行复位异步复位优点:1)、最大优点是只要综合工具工艺库有可异步复位的触发器,那么该触发器的数据输入通道就不需要额外的组合逻辑;2)、电路在任何情况下都能复位而不管是否有时钟出现。

a、大多数目标器件库的dff都有异步复位端口,因此采用异步复位可以节省资源b、设计相对简单。

c、异步复位信号识别方便d、Clocking scheme is not necessary for an asynchronous design. Hence design consumes less power. Asynchronous design style isalso one of the latest design options to achieve low power. Design community is scrathing their head over asynchronous design possibilities.异步复位缺点:1)、最大的问题在于它属于异步逻辑,问题出现在复位释放时,而不是有效时,如果复位释放接近时钟有效沿,则触发器的输出可能进入亚稳态,从而使复位失败。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

异步复位,同步释放的方式,而且复位信号低电平有效

一、特点:同步复位:顾名思义,同步复位就是指复位信号只有在时钟上升沿到来时,才能有效。

否则,无法完成对系统的复位工作。

用Verilog描述如下:always @ (posedge clk) beginif (!Rst_n)...end异步复位:它是指无论时钟沿是否到来,只要复位信号有效,就对系统进行复位。

用Verilog描述如下:always @ (posedge clk,negedge Rst_n) beginif (!Rst_n)...end

二、各自的优缺点:1、总的来说,同步复位的优点大概有3条:a、有利于仿真器的仿真。

b、可以使所设计的系统成为100%的同步时序电路,这便大大有利于时序分析,而且综合出来的fmax一般较高。

c、因为他只有在时钟有效电平到来时才有效,所以可以滤除高于时钟频率的毛刺。

他的缺点也有不少,主要有以下几条:a、复位信号的有效时长必须大于时钟周期,才能真正被系统识别并完成复位任务。

同时还要考虑,诸如:clk skew,组合逻辑路径延时,复位延时等因素。

b、由于大多数的逻辑器件的目标库内的DFF都只有异步复位端口,所以,倘若采用同步复位的话,综合器就会在寄存器的数据输入端口插入组合逻辑,这样就会耗费较多的逻辑资源。

2、对于异步复位来说,他的优点也有三条,都是相对应的:a、大多数目标器件库的dff都有异步复位端口,因此采用异步复位可以节省资源。

b、设计相对简单。

c、异步复位信号识别方便,而且可以很方便的使用FPGA的全局复位端口GSR。

缺点:a、在复位信号释放(release)的时候容易出现问题。

具体就是说:倘若复位释放时恰恰在时钟有效沿附近,就很容易使寄存器输出出现亚稳态,从而导致亚稳态。

b、复位信号容易受到毛刺的影响。

三、总结:所以说,一般都推荐使用异步复位,同步释放的方式,而且复位信号低电平有效。

这样就可以两全其美了。

always @(posedge clk or negedge rst_n)

if(!rst_n) b = 1b0;

else b = a;。