AT28LV010-20JU;AT28LV010-20TU;中文规格书,Datasheet资料

ATTINY28L-4PC,ATTINY28L-4PI,ATTINY28L-4AC,ATTINY28L-4AU,ATTINY28L-4AI,规格书,Datasheet 资料

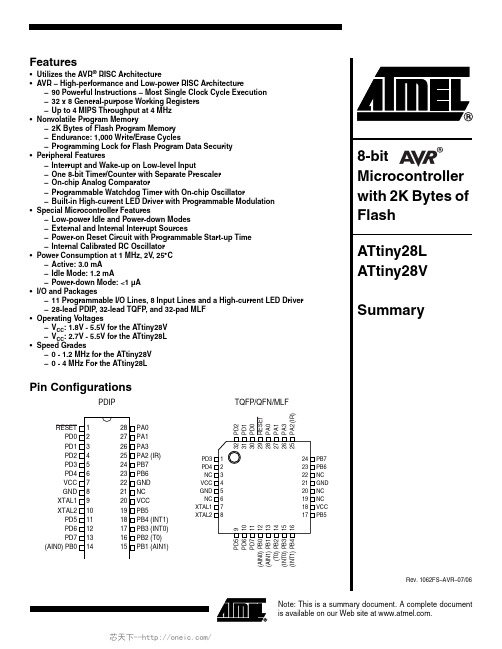

1Features•Utilizes the AVR ® RISC Architecture•AVR – High-performance and Low-power RISC Architecture–90 Powerful Instructions – Most Single Clock Cycle Execution –32 x 8 General-purpose Working Registers –Up to 4 MIPS Throughput at 4 MHz •Nonvolatile Program Memory–2K Bytes of Flash Program Memory –Endurance: 1,000 Write/Erase Cycles–Programming Lock for Flash Program Data Security •Peripheral Features–Interrupt and Wake-up on Low-level Input–One 8-bit Timer/Counter with Separate Prescaler –On-chip Analog Comparator–Programmable Watchdog Timer with On-chip Oscillator–Built-in High-current LED Driver with Programmable Modulation •Special Microcontroller Features–Low-power Idle and Power-down Modes –External and Internal Interrupt Sources–Power-on Reset Circuit with Programmable Start-up Time –Internal Calibrated RC Oscillator •Power Consumption at 1 MHz, 2V , 25°C –Active: 3.0 mA –Idle Mode: 1.2 mA–Power-down Mode: <1 µA •I/O and Packages–11 Programmable I/O Lines, 8 Input Lines and a High-current LED Driver –28-lead PDIP , 32-lead TQFP , and 32-pad MLF •Operating Voltages–V CC : 1.8V - 5.5V for the ATtiny28V –V CC : 2.7V - 5.5V for the ATtiny28L •Speed Grades–0 - 1.2 MHz for the ATtiny28V –0 - 4 MHz For the ATtiny28LPin ConfigurationsPDIPTQFP/QFN/MLF8-bit Microcontroller with 2K Bytes of ATtiny28L ATtiny28V SummaryNote: This is a summary document. A complete documentis available on our Web site at .2ATtiny28L/V1062FS–AVR–07/06DescriptionThe ATtiny28 is a low-power CMOS 8-bit microcontroller based on the AVR RISC archi-tecture. By executing powerful instructions in a single clock cycle, the ATtiny28 achieves throughputs approaching 1 MIPS per MHz, allowing the system designer to optimize power consumption versus processing speed. The AVR core combines a rich instruction set with 32 general-purpose working registers. All the 32 registers are directly con-nected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architec-ture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.Block DiagramFigure 1. The ATtiny28 Block DiagramThe ATtiny28 provides the following features: 2K bytes of Flash, 11 general-purpose I/O lines, 8 input lines, a high-current LED driver, 32 general-purpose working registers, an 8-bit timer/counter, internal and external interrupts, programmable Watchdog Timer with internal oscillator and 2 software-selectable power-saving modes. The Idle Mode stops the CPU while allowing the timer/counter and interrupt system to continue functioning.The Power-down mode saves the register contents but freezes the oscillator, disabling all other chip functions until the next interrupt or hardware reset. The wake-up or inter-3ATtiny28L/V1062FS–AVR–07/06rupt on low-level input feature enables the ATtiny28 to be highly responsive to external events, still featuring the lowest power consumption while in the power-down modes.The device is manufactured using Atmel’s high-density, nonvolatile memory technology.By combining an enhanced RISC 8-bit CPU with Flash on a monolithic chip, the Atmel ATtiny28 is a powerful microcontroller that provides a highly flexible and cost-effective solution to many embedded control applications. The ATtiny28 AVR is supported with a full suite of program and system development tools including: macro assemblers, pro-gram debugger/simulators, in-circuit emulators and evaluation kits.Pin DescriptionsVCC Supply voltage pin.GNDGround pin.Port A (PA3..PA0)Port A is a 4-bit I/O port. PA2 is output-only and can be used as a high-current LED driver. At V CC = 2.0V, the PA2 output buffer can sink 25 mA. PA3, PA1 and PA0 are bi-directional I/O pins with internal pull-ups (selected for each bit). The port pins are tri-stated when a reset condition becomes active, even if the clock is not running.Port B (PB7..PB0)Port B is an 8-bit input port with internal pull-ups (selected for all Port B pins). Port B pins that are externally pulled low will source current if the pull-ups are activated.Port B also serves the functions of various special features of the ATtiny28 as listed on page 27. If any of the special features are enabled, the pull-up(s) on the corresponding pin(s) is automatically disabled. The port pins are tri-stated when a reset condition becomes active, even if the clock is not running.Port D (PD7..PD0)Port D is an 8-bit I/O port. Port pins can provide internal pull-up resistors (selected for each bit). The port pins are tri-stated when a reset condition becomes active, even if the clock is not running.XTAL1Input to the inverting oscillator amplifier and input to the internal clock operating circuit.XTAL2Output from the inverting oscillator amplifier.pulses longer than 50 ns will generate a reset, even if the clock is not running. Shorter pulses are not guaranteed to generate a reset.4ATtiny28L/V1062FS–AVR–07/06Notes:1.For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addressesshould never be written.2.Some of the status flags are cleared by writing a logical “1” to them. Note that the CBI and SBI instructions will operate on allbits in the I/O register, writing a one back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers $00 to $1F only.Register SummaryAddressNameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Page$3F SREG ITHSVNZCpage 6$3E Reserved ...Reserved $20Reserved $1F Reserved $1E Reserved $1D Reserved $1C Reserved $1B PORTA ----PORTA3PORTA2PORTA1PORTA0page 32$1A PACR ----DDA3PA2HCDDA1DDA0page 32$19PINA ----PINA3-PINA1PINA0page 32$18Reserved $17Reserved $16PINB PINB7PINB6PINB5PINB4PINB3PINB2PINB1PINB0page 32$15Reserved $14Reserved $13Reserved $12PORTD PORTD7PORTD6PORTD5PORTD4PORTD3PORTD2PORTD1PORTD0page 33$11DDRD DDD7DDD6DDD5DDD4DDD3DDD2DDD1DDD0page 33$10PIND PIND7PIND6PIND5PIND4PIND3PIND2PIND1PIND0page 33$0F Reserved $0E Reserved $0D Reserved $0C Reserved $0B Reserved $0A Reserved $09Reserved $08ACSR ACD -ACO ACI ACIE -ACIS1ACIS0page 44$07MCUCS PLUPB -SE SM WDRF -EXTRF PORF page 19$06ICR INT1INT0LLIE TOIE0ISC11ISC10ISC01ISC00page 22$05IFR INTF1INTF0-TOV0----page 23$04TCCR0FOV0--OOM01OOM00CS02CS01CS00page 35$03TCNT0Timer/Counter0 (8-bit)page 36$02MODCR ONTIM4ONTIM3ONTIM2ONTIM1 ONTIM0MCONF2MCONF1MCONF0page 43$01WDTCR ---WDTOEWDEWDP2WDP1WDP0page 37$00OSCCALOscillator Calibration Registerpage 95ATtiny28L/V1062FS–AVR–07/06Instruction Set SummaryMnemonicOperandsDescriptionOperationFlags# ClocksARITHMETIC AND LOGIC INSTRUCTIONSADD Rd, Rr Add Two RegistersRd ← Rd + Rr Z,C,N,V,H 1ADC Rd, Rr Add with Carry Two Registers Rd ← Rd + Rr + C Z,C,N,V,H 1SUB Rd, Rr Subtract Two Registers Rd ← Rd - Rr Z,C,N,V,H 1SUBI Rd, K Subtract Constant from Register Rd ← Rd - K Z,C,N,V,H 1SBC Rd, Rr Subtract with Carry Two Registers Rd ← Rd - Rr - C Z,C,N,V,H 1SBCI Rd, K Subtract with Carry Constant from Reg.Rd ← Rd - K - C Z,C,N,V,H 1AND Rd, Rr Logical AND RegistersRd ← Rd • Rr Z,N,V 1ANDI Rd, K Logical AND Register and Constant Rd ← Rd • K Z,N,V 1OR Rd, Rr Logical OR RegistersRd ← Rd v Rr Z,N,V 1ORI Rd, K Logical OR Register and Constant Rd ← Rd v K Z,N,V 1EOR Rd, Rr Exclusive OR Registers Rd ← Rd ⊕ Rr Z,N,V 1COM Rd One’s Complement Rd ← $FF - Rd Z,C,N,V 1NEG Rd Two’s Complement Rd ← $00 - Rd Z,C,N,V,H 1SBR Rd, K Set Bit(s) in Register Rd ← Rd v K Z,N,V 1CBR Rd, K Clear Bit(s) in Register Rd ← Rd • (FFh - K)Z,N,V 1INC Rd Increment Rd ← Rd + 1Z,N,V 1DEC Rd DecrementRd ← Rd - 1 Z,N,V 1TST Rd Test for Zero or Minus Rd ← Rd • Rd Z,N,V1CLR Rd Clear Register Rd ← Rd ⊕ Rd Z,N,V 1SER Rd Set Register Rd ← $FF None 1BRANCH INSTRUCTIONSRJMP k Relative JumpPC ← PC + k + 1None 2RCALL kRelative Subroutine Call PC ← PC + k + 1None 3RET Subroutine Return PC ← STACK None 4RETI Interrupt Return PC ← STACKI 4CPSE Rd, Rr Compare, Skip if Equal if (Rd = Rr) PC ← PC + 2 or 3None 1/2CP Rd, Rr CompareRd - Rr Z,N,V,C,H 1CPC Rd, Rr Compare with CarryRd - Rr - C Z,N,V,C,H 1CPI Rd, K Compare Register with Immediate Rd - KZ N,V,C,H 1SBRC Rr, b Skip if Bit in Register Cleared if (Rr(b) = 0) PC ← PC + 2 or 3None 1/2SBRS Rr, b Skip if Bit in Register is Set if (Rr(b) = 1) PC ← PC + 2 or 3None 1/2SBIC P, b Skip if Bit in I/O Register Cleared if (P(b) = 0) PC ← PC + 2 or 3None 1/2SBIS P, b Skip if Bit in I/O Register is Set if (P(b) = 1) PC ← PC + 2 or 3None 1/2BRBS s, k Branch if Status Flag Set if (SREG(s) = 1) then PC ← PC + k + 1None 1/2BRBC s, k Branch if Status Flag Cleared if (SREG(s) = 0) then PC ← PC + k + 1None 1/2BREQ k Branch if Equal if (Z = 1) then PC ← PC + k + 1None 1/2BRNE k Branch if Not Equal if (Z = 0) then PC ← PC + k + 1None 1/2BRCS k Branch if Carry Set if (C = 1) then PC ← PC + k + 1None 1/2BRCC k Branch if Carry Cleared if (C = 0) then PC ← PC + k + 1None 1/2BRSH k Branch if Same or Higher if (C = 0) then PC ← PC + k + 1None 1/2BRLO k Branch if Lower if (C = 1) then PC ← PC + k + 1None 1/2BRMI k Branch if Minus if (N = 1) then PC ← PC + k + 1None 1/2BRPL k Branch if Plusif (N = 0) then PC ← PC + k + 1None 1/2BRGE k Branch if Greater or Equal, Signed if (N ⊕ V = 0) then PC ← PC + k + 1None 1/2BRLT k Branch if Less than Zero, Signed if (N ⊕ V = 1) then PC ← PC + k + 1None 1/2BRHS k Branch if Half-carry Flag Set if (H = 1) then PC ← PC + k + 1None 1/2BRHC k Branch if Half-carry Flag Cleared if (H = 0) then PC ← PC + k + 1None 1/2BRTS k Branch if T-flag Set if (T = 1) then PC ← PC + k + 1None 1/2BRTC k Branch if T-flag Cleared if (T = 0) then PC ← PC + k + 1None 1/2BRVS k Branch if Overflow Flag is Set if (V = 1) then PC ← PC + k + 1None 1/2BRVC k Branch if Overflow Flag is Cleared if (V = 0) then PC ← PC + k + 1None 1/2BRIE k Branch if Interrupt Enabled if (I = 1) then PC ← PC + k + 1None 1/2BRIDkBranch if Interrupt Disabledif (I = 0) then PC ← PC + k + 1None1/26ATtiny28L/V1062FS–AVR–07/06DATA TRANSFER INSTRUCTIONSLD Rd, Z Load Register Indirect Rd ← (Z)None 2ST Z, Rr Store Register Indirect (Z) ← Rr None 2MOV Rd, Rr Move between Registers Rd ← Rr None 1LDI Rd, K Load Immediate Rd ←K None 1IN Rd, P In Port Rd ← P None 1OUT P, RrOut PortP ← Rr None 1LPMLoad Program MemoryR0 ← (Z)None3BIT AND BIT-TEST INSTRUCTIONS SBI P, b Set Bit in I/O Register I/O(P,b) ← 1None 2CBI P, b Clear Bit in I/O Register I/O(P,b) ←None 2LSL Rd Logical Shift LeftRd(n+1) ← Rd(n), Rd(0) ← 0Z,C,N,V 1LSR Rd Logical Shift Right Rd(n) ← Rd(n+1), Rd(7) ← 0Z,C,N,V 1ROL Rd Rotate Left through Carry Rd(0) ← C, Rd(n+1) ← Rd(n), C ← Rd(7)Z,C,N,V 1ROR Rd Rotate Right through Carry Rd(7) ← C, Rd(n) ← Rd(n+1), C ← Rd(0)Z,C,N,V 1ASR Rd Arithmetic Shift Right Rd(n) ← Rd(n+1), n = 0..6Z,C,N,V 1SWAP Rd Swap Nibbles Rd(3..0) ← Rd(7..4), Rd(7..4) ← Rd(3..0)None 1BSET s Flag Set SREG(s) ← 1SREG(s)1BCLR s Flag Clear SREG(s) ← 0SREG(s)1BST Rr, b Bit Store from Register to T T ← Rr(b)T 1BLD Rd, bBit Load from T to Register Rd(b) ← T None 1SEC Set Carry C ← 1C 1CLC Clear Carry C ←0C 1SEN Set Negative Flag N ← 1N 1CLN Clear Negative Flag N ← 0N 1SEZ Set Zero Flag Z ←1Z 1CLZ Clear Zero Flag Z ← 0Z1SEI Global Interrupt Enable I ← 1I 1CLI Global Interrupt Disable I ←I 1SES Set Signed Test FlagS ← 1S 1CLS Clear Signed Test Flag S ←0S 1SEV Set Two’s Complement OverflowV ←1V 1CLV Clear Two’s Complement Overflow V ← 0V 1SET Set T in SREG T ← 1T 1CLT Clear T in SREG T ← 0T 1SEH Set Half-carry Flag in SREG H ← 1H 1CLH Clear Half-carry Flag in SREG H ←H 1NOP No Operation None 1SLEEP Sleep(see specific descr. for Sleep function)None 1WDRWatchdog Reset(see specific descr. for WDR/timer)None1Instruction Set Summary (Continued)MnemonicOperandsDescriptionOperationFlags# Clocks7ATtiny28L/V1062FS–AVR–07/06Notes:1.This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ordering informationand minimum quantities.2.Pb-free packaging alternative, complies to the European Directive for Restriction of Hazardous Substances (RoHS direc-tive).Also Halide free and fully Green.Ordering InformationSpeed (MHz)Power Supply (Volts)Ordering Code Package (1)Operation Range 42.7 - 5.5A Ttiny28L-4AC A Ttiny28L-4PC A Ttiny28L-4MC32A 28P332M1-A Commercial (0°C to 70°C)A Ttiny28L-4AI A Ttiny28L-4AU (2)A Ttiny28L-4PI A Ttiny28L-4PU (2)A Ttiny28L-4MI A Ttiny28L-4MU (2)32A 32A 28P328P332M1-A 32M1-A Industrial (-40°C to 85°C)1.21.8 - 5.5A Ttiny28V-1AC A Ttiny28V-1PC A Ttiny28V-1MC32A 28P332M1-A Commercial (0°C to 70°C)A Ttiny28V-1AI A Ttiny28V-1AU (2)A Ttiny28V-1PI A Ttiny28V-1PU (2)A Ttiny28V-1MI A Ttiny28V-1MU (2)32A 32A 28P328P332M1-A 32M1-AIndustrial (-40°C to 85°C)Package Type32A 32-lead, Thin (1.0 mm) Plastic Quad Flat Package (TQFP)28P328-lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)32M1-A32-pad, 5x5x1.0 body, Lead Pitch 0.50mm, Quad Flat No-lead/Micro Lead Frame Package (QFN/MLF)8ATtiny28L/V1062FS–AVR–07/06Packaging Information32A9ATtiny28L/V1062FS–AVR–07/0628P310ATtiny28L/V1062FS–AVR–07/0632M1-A11ATtiny28L/V1062FS–AVR–07/06ErrataAll revisionsNo known errata.12ATtiny28L/V1062FS–AVR–07/06Datasheet Revision HistoryPlease note that the referring page numbers in this section are referred to this docu-ment. The referring revision in this section are referring to the document revision.Rev – 01/06G 1.Updated chapter layout.2.Updated “Ordering Information” on page 7.Rev – 01/06G1.Updated description for “Port A” on page 25.2.Added note 6 in “DC Characteristics” on page 54.3.Updated “Ordering Information” on page 7.4.Added “Errata” on page 11.Rev – 03/05F1.Updated “Electrical Characteristics” on page 54.2.MLF-package alternative changed to “Quad Flat No-Lead/Micro Lead Frame PackageQFN/MLF”.3.Updated “Ordering Information” on page 7.1062FS–AVR–07/06© 2006 Atmel Corporation . All rights reserved. ATMEL ®, logo and combinations thereof, Everywhere You Are ®, AVR ®, AVR Studio ®, and oth-ers, are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of oth-ers.Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise,to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL’S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL’S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABIL ITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBIL ITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel’s products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.Atmel CorporationAtmel Operations2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 487-2600Regional HeadquartersEuropeAtmel SarlRoute des Arsenaux 41Case Postale 80CH-1705 Fribourg SwitzerlandTel: (41) 26-426-5555Fax: (41) 26-426-5500AsiaRoom 1219Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong KongTel: (852) 2721-9778Fax: (852) 2722-1369Japan9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTel: (81) 3-3523-3551Fax: (81) 3-3523-7581Memory2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 436-4314Microcontrollers2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 436-4314La Chantrerie BP 7060244306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18Fax: (33) 2-40-18-19-60ASIC/ASSP/Smart CardsZone Industrielle13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00Fax: (33) 4-42-53-60-011150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300Fax: 1(719) 540-1759Scottish Enterprise Technology Park Maxwell BuildingEast Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000Fax: (44) 1355-242-743RF/AutomotiveTheresienstrasse 2Postfach 353574025 Heilbronn, Germany Tel: (49) 71-31-67-0Fax: (49) 71-31-67-23401150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300Fax: 1(719) 540-1759Biometrics/Imaging/Hi-Rel MPU/High Speed Converters/RF DatacomAvenue de Rochepleine BP 12338521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00Fax: (33) 4-76-58-34-80Literature Requests/literature。

CAT28LV256G25;CAT28LV256G-25T;CAT28LV256GI25;CAT28LV256GI-25T;中文规格书,Datasheet资料

s CMOS and TTL Compatible I/O s Automatic Page Write Operation:– 1 to 64 Bytes in 10ms – Page Load Timers End of Write Detection:– Toggle Bit – DATA Pollings Hardware and Software Write Protection s 100,000 Program/Erase Cycles s 100 Year Data RetentionFEATURESs 3.0V to 3.6V Supplys Read Access Times: 200/250/300 ns s Low Power CMOS Dissipation:– Active: 15 mA Max.– Standby: 150 µA Max.s Simple Write Operation:– On-Chip Address and Data Latches – Self-Timed Write Cycle with Auto-Clears Fast Write Cycle Time:– 10ms Max.s Commercial, Industrial and AutomotiveTemperature RangesDESCRIPTIONThe CAT28LV256 is a fast, low power, low voltage CMOS Parallel E 2PROM organized as 32K x 8-bits. It requires a simple interface for in-system programming.On-chip address and data latches, self-timed write cycle with auto-clear and V CC power up/down write protection eliminate additional timing and protection hardware.DATA Polling and Toggle status bits signal the start and end of the self-timed write cycle. Additionally, the CAT28LV256 features hardware and software write protection.The CAT28LV256 is manufactured using Catalyst’s advanced CMOS floating gate technology. It is designed to endure 100,000 program/erase cycles and has a data retention of 100 years. The device is available in JEDEC–approved 28-pin DIP, 28-pin TSOP or 32-pin PLCC packages.BLOCK DIAGRAMA 6A 256K-Bit CMOS PARALLEL EEPROMCAT28LV256CAT28LV256PLCC Package (N, G)DIP Package (P, L)PIN CONFIGURATIONTSOP Top View (8mm X 13.4mm) (H)1234567891011121314282726252423222120191817I/O 6I/O 5I/O 4GND I/O 2A 1A 2V CC WE A 8A 9A 11OE A 7A 6A 5A 4A 3A 10I/O 7A 121615I/O 3I/O 1I/O 0A 0A 13A 14I/O 2V SSI/O 6I/O 5A 1A 0I/O 0I/O 1OE A 10CE I/O 7A 5A 4A 3A 2A 14A 12A 7A 6A 9A 11V CC WE A 13A 8A 6A 5A 4A 35678A 2A 1A 0NC 9101112I/O 013A 8A 9A 11NC 29282726OE A 10CE 25242322I/O 721I /O 1I /O 2V S SN CI /O 3I /O 4I /O 5141516171819204321323130A 7A 12A 14N C V C C W EA 13I/O 4I/O 3I/O 6TOP VIEWPIN FUNCTIONSPin Name Function Pin Name Function A 0–A 14Address Inputs WE Write Enable I/O 0–I/O 7Data Inputs/Outputs V CC 3.0 to 3.6 V Supply CE Chip Enable V SS Ground OEOutput EnableNCNo ConnectCAT28LV256CAPACITANCE T A = 25°C, f = 1.0 MHzSymbol TestMax.Units Conditions C I/O (1)Input/Output Capacitance 10pF V I/O = 0V C IN (1)Input Capacitance6pFV IN = 0VNote:(1)This parameter is tested initially and after a design or process change that affects the parameter.(2)The minimum DC input voltage is –0.5V. During transitions, inputs may undershoot to –2.0V for periods of less than 20 ns. Maximum DCvoltage on output pins is V CC +0.5V, which may overshoot to V CC +2.0V for periods of less than 20 ns.(3)Output shorted for no more than one second. No more than one output shorted at a time.(4)Latch-up protection is provided for stresses up to 100mA on address and data pins from –1V to V CC +1V.*COMMENTStresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device.These are stress ratings only, and functional operation of the device at these or any other conditions outside of those listed in the operational sections of this specifica-tion is not implied. Exposure to any absolute maximum rating for extended periods may affect device perfor-mance and reliability.ABSOLUTE MAXIMUM RATINGS*Temperature Under Bias .................–55°C to +125°C Storage Temperature.......................–65°C to +150°C Voltage on Any Pin withRespect to Ground (2)...........–2.0V to +V CC + 2.0V V CC with Respect to Ground ...............–2.0V to +7.0V Package Power DissipationCapability (Ta = 25°C)...................................1.0W Lead Soldering Temperature (10 secs)............300°C Output Short Circuit Current (3)........................100 mA RELIABILITY CHARACTERISTICS Symbol Parameter Min.Max.Units Test MethodN END (1)Endurance 100,000Cycles/Byte MIL-STD-883, Test Method 1033T DR (1)Data Retention 100Years MIL-STD-883, Test Method 1008V ZAP (1)ESD Susceptibility 2000Volts MIL-STD-883, Test Method 3015I LTH (1)(4)Latch-Up100mAJEDEC Standard 17MODE SELECTIONModeCE WE OE I/O Power ReadL HL D OUT ACTIVE Byte Write (WE Controlled)LH D IN ACTIVE Byte Write (CE Controlled)L H D IN ACTIVE Standby, and Write Inhibit H X X High-Z STANDBY Read and Write InhibitX H HHigh-ZACTIVECAT28LV256D.C. OPERATING CHARACTERISTICSV CC = 3.0V to 3.6V, unless otherwise specifiedNote:(1)This parameter is tested initially and after a design or process change that affects the parameter.(2)V IHC = V CC –0.3V to V CC +0.3V.(3)Output floating (High-Z) is defined as the state when the external data line is no longer driven by the output buffer.CAT28LV256A.C. CHARACTERISTICS, Write Cycle V CC = 3.0V to 3.6V, unless otherwise specified28LV256-2028LV256-2528LV256-30Symbol Parameter Min.Max.Min.Max.Min.Max.Units t WC Write Cycle Time 101010ms t AS Address Setup Time 000ns t AH Address Hold Time 100100100ns t CS CE Setup Time 000ns t CH CE Hold Time 000ns t CW (3)CE Pulse Time 150150150ns t OES OE Setup Time 000ns t OEH OE Hold Time 000ns t WP (3)WE Pulse Width 150150150ns t DS Data Setup Time 505050ns t DH Data Hold Time000ns t INIT (1)Write Inhibit Period After Power-up 510510510ms t BLC (1)(4)Byte Load Cycle Time0.151000.151000.15100µsC L INCLUDES JIG CAPACITANCEINPUT PULSE LEVELSREFERENCE POINTS2.0 V0.6 VV CC - 0.3V0.0 VFigure 1. A.C. Testing Input/Output Waveform (2)28LV256 F04Note:(1)This parameter is tested initially and after a design or process change that affects the parameter.(2)Input rise and fall times (10% and 90%) < 10 ns.(3)A write pulse of less than 20ns duration will not initiate a write cycle.(4)A timer of duration t BLC max. begins with every LOW to HIGH transition of WE . If allowed to time out, a page or byte write will begin;however a transition from HIGH to LOW within t BLC max. stops the timer.Figure 2. A.C. Testing Load Circuit (example)28LV256 F05CAT28LV256ADDRESSCEOEWEDATA OUTDATA INDEVICE OPERATIONReadData stored in the CAT28LV256 is transferred to the data bus when WE is held high, and both OE and CE are held low. The data bus is set to a high impedance state when either CE or OE goes high. This 2-line control architecture can be used to eliminate bus contention in a system environment.Byte WriteA write cycle is executed when both CE and WE are low,and OE is high. Write cycles can be initiated using either WE or CE , with the address input being latched on the falling edge of WE or CE , whichever occurs last. Data,conversely, is latched on the rising edge of WE or CE ,whichever occurs first. Once initiated, a byte write cycle automatically erases the addressed byte and the new data is written within 10 ms.Figure 3. Read Cycle28LV256 F0628LV256 F07CAT28LV256ADDRESSCEOEWEDATA OUTDATA INPage WriteThe page write mode of the CAT28LV256 (essentially an extended BYTE WRITE mode) allows from 1 to 64bytes of data to be programmed within a single E 2PROM write cycle. This effectively reduces the byte-write time by a factor of 64.Following an initial WRITE operation (WE pulsed low, for t WP , and then high) the page write mode can begin by issuing sequential WE pulses, which load the address and data bytes into a 64 byte temporary buffer. The page address where data is to be written, specified by bits A 6to A 14, is latched on the last falling edge of WE . Each byte within the page is defined by address bits A 0 to A 5(which can be loaded in any order) during the first and subsequent write cycles. Each successive byte load cycle must begin within t BLC MAX of the rising edge of the preceding WE pulse. There is no page write window limitation as long as WE is pulsed low within t BLC MAX .Upon completion of the page write sequence, WE must stay high a minimum of t BLC MAX for the internal auto-matic program cycle to commence. This programming cycle consists of an erase cycle, which erases any data that existed in each addressed cell, and a write cycle,which writes new data back into the cell. A page write will only write data to the locations that were addressed and will not rewrite the entire page.28LV256 F09CAT28LV256WECEOEI/O 6DATA PollingDATA polling is provided to indicate the completion of write cycle. Once a byte write or page write cycle is initiated, attempting to read the last byte written will output the complement of that data on I/O 7 (I/O 0–I/O 6are indeterminate) until the programming cycle is com-plete. Upon completion of the self-timed write cycle, all I/O’s will output true data during a read cycle.Toggle BitIn addition to the DATA Polling feature, the device can determine the completion of a write cycle, while a write cycle is in progress, by reading data from the device.This results in I/O 6 toggling between one and zero. Once the write is complete, however, I/O 6 stops toggling and valid data can be read from the device.Figure 7. DATA Polling28LV256 F10Figure 8. Toggle Bit28LV256 F11Note:(1)Beginning and ending state of I/O 6 is indeterminate.CAT28LV256SOFTWARE DATAPROTECTION ACTIVATED(1)(4)Noise pulses of less than 20 ns on the WE or CEinputs will not result in a write cycle.SOFTWARE DATA PROTECTIONThe CAT28LV256 features a software controlled data protection scheme which, once enabled, requires a data algorithm to be issued to the device before a write can be performed. The device is shipped from Catalyst with the software protection NOT ENABLED (the CAT28LV256is in the standard operating mode).Figure 9.Write Sequence for Activating SoftwareData ProtectionFigure 10.Write Sequence for DeactivatingSoftware Data Protection28LV256 F1228LV256 F13Note:(1)Write protection is activated at this point whether or not any more writes are completed. Writing to addresses must occur within t BLCMax., after SDP activation.HARDWARE DATA PROTECTIONThe following hardware data protection features are incorporated into the CAT28LV256.(1)V CC sense provides write protection when V CC fallsbelow 2.0V min.(2) A power on delay mechanism, t INIT (see AC charac-teristics), provides a 5 to 10 ms delay before a write sequence, after V CC has reached 2.4V min.(3)Write inhibit is activated by holding any one of OElow, CE high, or WE high.CAT28LV256To activate the software data protection, the device must be sent three write commands to specific addresses with specific data (Figure 9). This sequence of commands (along with subsequent writes) must adhere to the page write timing specifications (Figure 11). Once this is done,all subsequent byte or page writes to the device must be preceded by this same set of write commands. The data protection mechanism is activated until a deactivate sequence is issued, regardless of power on/off transi-tions. This gives the user added inadvertent write pro-tection on power-up in addition to the hardware protec-tion provided.To allow the user the ability to program the device with an E 2PROM programmer (or for testing purposes) there is a software command sequence for deactivating the data protection. The six step algorithm (Figure 10) will reset the internal protection circuitry, and the device will return to standard operating mode (Figure 12 provides reset timing). After the sixth byte of this reset sequence has been issued, standard byte or page writing can commence.Figure 11. Software Data Protection TimingFigure 12. Resetting Software Data Protection Timing分销商库存信息:ONSEMICAT28LV256G25CAT28LV256G-25T CAT28LV256GI25 CAT28LV256GI-25T。

ATSTK520;中文规格书,Datasheet资料

STK520 .............................................................................................. User GuideSTK520 User Guide 3Table of ContentsSection 1Introduction............................................................................................1-2Section 2Using the STK520 Top Module.............................................................2-42.1Connecting the STK520 to the STK500 Starter Kit..................................2-42.1.1Placing an AT90PWM3 on the STK520.............................................2-42.1.2Placing an AT90PWM2 on the STK520.............................................2-52.2Programming the AVR..............................................................................2-72.2.1In-System Programming....................................................................2-72.2.2High-voltage Programming................................................................2-82.3JTAGICE mkII Connector.........................................................................2-92.4STK520 Jumpers, Leds & Test Points....................................................2-112.5DALI Interface.........................................................................................2-122.6Potentiometer.........................................................................................2-13Section 3Troubleshooting Guide........................................................................3-14Section 4Technical Specifications......................................................................4-16Section 5Technical Support ...............................................................................5-17Section 6Complete Schematics .........................................................................6-20IntroductionSection 1IntroductionThe STK520 board is a top module designed to add AT90PWM family support to theSTK500 development board from Atmel Corporation.The STK520 includes connectors and hardware allowing full utilization of the new fea-tures of the AT90PWM, while the Zero Insertion Force (ZIF) socket allows easy to use ofSO24 & SO32 packages for prototyping.This user guide acts as a general getting started guide as well as a complete technicalreference for advanced users.Notice that in this guide, the word AVR is used to refer to the target component(AT90PWM2, AT90PWM3...)Figure 1-1. STK520 Top Module for STK500Introduction1.1Features STK520 is a New Member of the Successful STK500 Starter Kit Family.Supports the AT90PWM2 & AT90PWM3.DALI Hardware Interface.Supported by AVR Studio® 4.Zero Insertion Force Socket for SO24 & SO32 Packages.High Voltage Parallell Programming.Serial Programming.DALI Peripherals can be Disconnected from the Device.6 Pin Connector for On-chip Debugging using JTAG MKII Emulator.Potentiometer for the Demo Application.Quick Reference to all Switches and Jumpers in the Silk-Screen of the PCB.Using the STK520 Top Module Section 2Using the STK520 Top Module2.1Connecting the STK520 to theSTK500 Starter Kit Connect the STK520 to the STK500 expansion header 0 and 1. It is important that the top module is connected in the correct orientation as shown in Figure 2-1. The EXPAND0 written on the STK520 top module should match the EXPAND0 written beside the expansion header on the STK500 board.Figure 2-1. Connecting STK520 to the STK500 BoardNote:Connecting the STK520 with wrong orientation may damage the board.2.1.1Placing anAT90PWM3 on theSTK520The STK520 contains both a ZIF socket for a SO32 package. Care should be taken so that the device is mounted with the correct orientation. Figure 2-2 shows the location of pin1 for the ZIF socket.Using the STK520 Top ModuleFigure 2-2. Pin1 on ZIF SocketCaution: Do not mount an AT90PWM3 on the STK520 at the same time as an AVR ismounted on the STK500 board or at the same time as an AT90PWM2 is mounted on theSTK520 board. None of the devices might work as intended.2.1.2Placing anAT90PWM2 on theSTK520The STK520 contains both a ZIF socket for a SO24 package. Care should be taken so that the device is mounted with the correct orientation. Figure 2-2 shows the location of pin1 for the ZIF socket.Figure 2-3. Pin1 on ZIF SocketPIN1PIN1Using the STK520 Top Module Caution: Do not mount an AT90PWM2 on the STK520 at the same time as an AVR is mounted on the STK500 board or at the same time as an AT90PWM3 is mounted on the STK520 board. None of the devices might work as intended.Using the STK520 Top Module2.2Programming theAVR The AVR (AT90PWM2, AT90PWM3...) can be programmed using both SPI and High-voltage Parallel Programming. This section will explain how to connect the programming cables to successfully use one of these two modes. The AVR Studio STK500 software is used in the same way as for other AVR partsNote:The AT90PWM3 also support Self Programming, See AVR109 application note for more information on this topic.2.2.1In-SystemProgramming Figure 2-4. In-System ProgrammingTo program the AT90PWM3 using ISP Programming mode, connect the 6-wire cable between the ISP6PIN connector on the STK500 board and the ISP connector on the STK520 board as shown in Figure 2-4. The device can be programmed using the Serial Programming mode in the AVR Studio4 STK500 software.Note:See STK500 User Guide for information on how to use the STK500 front-end software for ISP Programming.Using the STK520 Top Module2.2.2High-voltageProgramming Figure 2-5. High-voltage (Parallel) ProgrammingTo program the AVR using High-voltage (Parallel) Programming, connect the PROGC-TRL to PORTD and PROGDATA to PORTB on the STK500 as shown in Figure 2-5. Make sure that the TOSC-switch is placed in the XTAL position.As described in the STK500 User Guide (jumper settings), mount the BSEL2 jumper in order to High-voltage Program the ATmega devices. This setting also applies to High-voltage Programming of the AVR.The device can now be programmed using the High-voltage Programming mode in AVR Studio STK500 software.Note:See the STK500 User Guide for information on how to use the STK500 front-end software in High-voltage Programming mode.Note:For the High-voltage Programming mode to function correctly, the target voltage must be higher than 4.5V.Using the STK520 Top Module2.3JTAGICE mkIIConnector See the following document :“JTAGICE mkII Quick Start Guide” which purpose is “Connecting to a target board with the AVR JTAGICE mkII”.This note explains which signals are required for ISP and which signals are required for debugWIRE.Figure 2-6 shows how to connect the JTAGICE mkII probe on the STK520 board. Figure 2-6. Connecting JTAG ICE to the STK520The ISP connector is used for the AT90PWM3 built-in debugWire interface. The pin out of the connector is shown in Table 2-1 and is compliant with the pin out of the JTAG ICE available from Atmel. Connecting a JTAG ICE to this connector allows On-chip Debug-ging of the AT90PWM3.More information about the JTAG ICE and On-chip Debugging can be found in the AVR JTAG ICE User Guide, which is available at the Atmel web site, .分销商库存信息: ATMELATSTK520。

AM29F010A中文资料

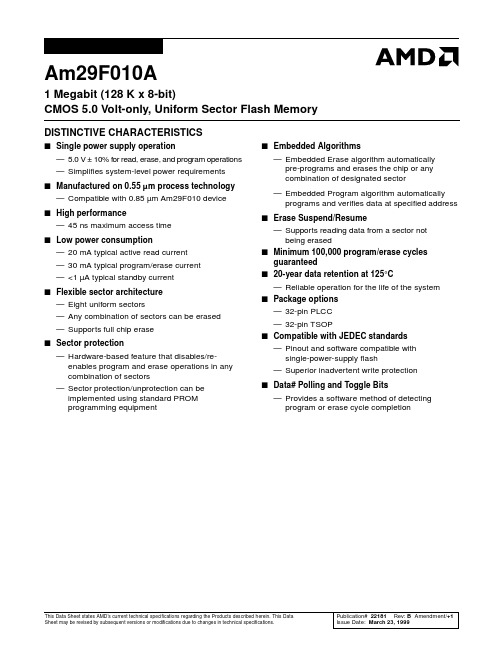

This Data Sheet states AMD’s current technical specifications regarding the Products described herein. This Data Sheet may be revised by subsequent versions or modifications due to changes in technical specifications.Publication# 22181Rev: B Amendment/+1 Issue Date: March 23, 1999Am29F010A1 Megabit (128 K x 8-bit)CMOS 5.0 Volt-only, Uniform Sector Flash Memory DISTINCTIVE CHARACTERISTICSs Single power supply operation—5.0 V ± 10% for read, erase, and program operations —Simplifies system-level power requirementss Manufactured on 0.55 µm process technology —Compatible with 0.85 µm Am29F010 devices High performance—45 ns maximum access times Low power consumption—20 mA typical active read current—30 mA typical program/erase current—<1 µA typical standby currents Flexible sector architecture—Eight uniform sectors—Any combination of sectors can be erased—Supports full chip erases Sector protection—Hardware-based feature that disables/re-enables program and erase operations in anycombination of sectors—Sector protection/unprotection can beimplemented using standard PROMprogramming equipment s Embedded Algorithms—Embedded Erase algorithm automatically pre-programs and erases the chip or anycombination of designated sector—Embedded Program algorithm automatically programs and verifies data at specified address s Erase Suspend/Resume—Supports reading data from a sector notbeing eraseds Minimum 100,000 program/erase cycles guaranteeds20-year data retention at 125°C—Reliable operation for the life of the systems Package options—32-pin PLCC—32-pin TSOPs Compatible with JEDEC standards—Pinout and software compatible withsingle-power-supply flash—Superior inadvertent write protections Data# Polling and Toggle Bits—Provides a software method of detecting program or erase cycle completionGENERAL DESCRIPTIONThe Am29F010A is a 1 Mbit, 5.0 Volt-only Flash memory organized as 131,072 bytes. The Am29F010A is offered in 32-pin PLCC and TSOP packages. The byte-wide data appears on DQ0-DQ7. The device is designed to be programmed in-system with the standard system 5.0 Volt VCC supply. A 12.0 volt VPP is not required for program or erase operations. The device can also be programmed or erased in standard EPROM programmers. This device is manufactured using AMD’s 0.55 µm pro-cess technology, and offers all the features and benefits of the Am29F010, which was manufactured using 0.85µm process technology. In addition, the Am29F010A offers the erase suspend/erase resume feature.The standard device offers access times of 45, 55, 70, 90, and 120 ns, allowing high-speed microprocessors to operate without wait states. To eliminate bus conten-tion the device has separate chip enable (CE#), write enable (WE#) and output enable (OE#) controls.The device requires only a single 5.0 volt power sup-ply for both read and write functions. Internally generated and regulated voltages are provided for the program and erase operations.The device is entirely command set compatible with the JEDEC single-power-supply Flash standard. Com-mands are written to the command register using standard microprocessor write timings. Register con-tents serve as input to an internal state machine that controls the erase and programming circuitry. Write cycles also internally latch addresses and data needed for the programming and erase operations. Reading data out of the device is similar to reading from other Flash or EPROM devices.Device programming occurs by executing the program command sequence. This invokes the Embedded Pro-g ram al g or i thm—an i n ter n al al go ri th m th at automatically times the program pulse widths and verifies proper cell margin.Device erasure occurs by executing the erase com-mand sequence. This invokes the Embedded Erase algorithm—an internal algorithm that automatically preprograms the array (if it is not already programmed) before executing the erase operation. During erase, the device automatically times the erase pulse widths and verifies proper cell margin.The host system can detect whether a program or erase operation is complete by reading the DQ7 (Data# Polling) and DQ6 (toggle) status bits. After a program or erase cycle has been completed, the device is ready to read array data or accept another command.The sector erase architecture allows memory sectors to be erased and reprogrammed without affecting the data contents of other sectors. The device is erased when shipped from the factory.The hardware data protection measures include a low V CC detector automatically inhibits write operations during power transitions. The hardware sector protec-tion feature disables both program and erase operations in any combination of the sectors of memory, and is im-plemented using standard EPROM programmers.The system can place the device into the standby mode. Power consumption is greatly reduced in this mode. AMD’s Flash technology combines years of Flash memory manufacturing experience to produce the highest levels of qual ity, reliabilit y, and cost effectiveness. The device electrically erases all bits within a sector simultaneously via Fowler-Nordheim tunneling. The bytes are programmed one byte at a time using the EPROM programming mechanism of hot electron injection.2Am29F010AAm29F010A 3PRODUCT SELECTOR GUIDENote:See the AC Characteristics section for full specifications.BLOCK DIAGRAMFamily Part Number Am29F010ASpeed OptionV CC = 5.0 V ± 5%-45V CC = 5.0 V ± 10%-55 -70-90-120Max Access Time (ns)45557090120CE# Access (ns)45557090120OE# Access (ns)2530303550Input/Output BuffersX-DecoderY-Decoder Chip Enable Output EnableLogicErase Voltage Generator PGM Voltage GeneratorTimerV CC DetectorState Control Command RegisterV CC V SSWE#CE#OE#STBSTBDQ0–DQ7Data LatchY-GatingCell Matrix22181B-1A d d r e s s L a t c hA0–A164Am29F010ACONNECTION DIAGRAMS22181B-212345678910111213141516Standard TSOP22181B-3A11A9A8A13A14NC WE#V CC NC A16A15A12A7A6A5A432313029282726252423222120191817OE#A10CE#DQ7DQ6DQ5DQ4DQ3V SS DQ2DQ1DQ0A0A1A2A 322181B-412345678910111213141516A11A9A8A13A14NC WE#V CC NC A16A15A12A7A6A5A432313029282726252423222120191817OE#A10CE#DQ7DQ6DQ5DQ4DQ3V SS DQ2DQ1DQ0A0A1A2A 3Reverse TSOPPIN CONFIGURATIONA0–A16=17 AddressesDQ0–DQ7=8 Data Inputs/OutputsCE#=Chip EnableOE#=Output EnableWE#= Write EnableV CC=+5.0 Volt Single Power Supply(See Product Selector Guide for speedoptions and voltage supply tolerances) V SS=Device GroundNC=Pin Not Connected Internally LOGIC SYMBOL178DQ0–DQ7A0–A16CE#OE#WE#22181B-5Am29F010A56Am29F010AORDERING INFORMATION Standard ProductsAMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of the elements below.Valid CombinationsValid Combinations list configurations planned to be sup-ported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.AM29F010A DEVICE NUMBER/DESCRIPTION Am29F010A1 Megabit (128 K x 8-Bit) CMOS Flash Memory 5.0 Volt-only Read, Program, and Erase-70E C OPTIONAL PROCESSING Blank =Standard ProcessingB =Burn-In(Contact an AMD representative for more information.)TEMPERATURE RANGE C = Commercial (0°C to +70°C)I=Industrial (–40°C to +85°C)E =Extended (–55°C to +125°C)PACKAGE TYPEJ =32-Pin Rectangular Plastic LeadedChip Carrier (PL 032)E =32-Pin Thin Small Outline Package(TSOP) Standard Pinout (TS 032)F =32-Pin Thin Small Outline Package(TSOP) Reverse Pinout (TSR032)SPEED OPTIONSee Product Selector Guide and Valid CombinationsBValid CombinationsAM29F010A-45JC, JI, JE,EC, EI, EE, FC, FI, FEAM29F010A-55V CC = 5.0 V ± 10%JC, JI, JE, EC, EI, EE, FC, FI, FEAM29F010A-70AM29F010A-90AM29F010A-120JC, JI, JE,EC, EI, EE, FC, FI, FEDEVICE BUS OPERATIONSThis section describes the requirements and use of the device bus operations, which are initiated through the internal command register. The command register it-self does not occupy any addressable memory location. The register is composed of latches that store the commands, along with the address and data infor-mation needed to execute the command. The contents of the register serve as inputs to the internal state ma-chine. The state machine outputs dictate the function of the device. The appropriate device bus operations table lists the inputs and control levels required, and the resulting output. The following subsections describe each of these operations in further detail.Table 1.Am29F010A Device Bus OperationsLegend:L = Logic Low = VIL, H = Logic High = VIH, VID = 12.0 ± 0.5 V, X = Don’t Care, AIN = Addresses In, DIN = Data In, DOUT = Data OutNotes:1.Addresses are A16:A0.2.The sector protect and sector unprotect functions must be implemented via programming equipment. See the “Sector Pro-tection/Unprotection” section.Requirements for Reading Array DataTo read array data from the outputs, the system must drive the CE# and OE# pins to V IL. CE# is the power control and selects the device. OE# is the output con-trol and gates array data to the output pins. WE# should remain at V IH.The internal state machine is set for reading array data upon device power-up, or after a hardware reset. This ensures that no spurious alteration of the memory con-tent occurs during the power transition. No command is necessary in this mode to obtain array data. Standard microprocessor read cycles that assert valid addresses on the device address inputs produce valid data on the device data outputs. The device remains enabled for read access until the command register contents are altered.See “Reading Array Data” for more information. Refer to the AC Read Operations table for timing specifica-tions and to the Read Operations Timings diagram for the timing waveforms. I CC1 in the DC Characteristics table represents the active current specification for reading array data.Writing Commands/Command Sequences To write a command or command sequence (which in-cludes programming data to the device and erasing sectors of memory), the system must drive WE# and CE# to V IL, and OE# to V IH.An erase operation can erase one sector, multiple sec-tors, or the entire device. The Sector Address Tables indicate the address space that each sector occupies.A “sector address” consists of the address bits required to uniquely select a sector. See the “Command Defini-tions” section for details on erasing a sector or the entire chip.After the system writes the autoselect command se-quence, the device enters the autoselect mode. The system can then read autoselect codes from the inter-nal register (which is separate from the memory array) on DQ7–DQ0. Standard read cycle timings apply in this mode. Refer to the “Autoselect Mode” and “Autoselect Command Sequence” sections for more information.I CC2 in the DC Characteristics table represents the ac-tive current specification for the write mode. The “AC Characteristics” section contains timing specification tables and timing diagrams for write operations.Operation CE#OE#WE#Addresses(Note 1)DQ0–DQ7Read L L H A IN D OUT Write L H L A IN D IN Standby V CC ± 0.5 V X X X High-Z Output Disable L H H X High-Z Hardware Reset X X X X High-ZAm29F010A7Program and Erase Operation Status During an erase or program operation, the system may check the status of the operation by reading the status bits on DQ7–DQ0. Standard read cycle timings and I CC read specifications apply. Refer to “Write Operation Status” for more information, and to each AC Charac-teristics section in the appropriate data sheet for timing diagrams.Standby ModeWhen the system is not reading or writing to the device, it can place the device in the standby mode. In this mode, current consumption is greatly reduced, and the outputs are placed in the high impedance state, inde-pendent of the OE# input. The device enters the CMOS standby mode when the CE# pin is held at V CC ± 0.5 V. (Note that this is a more restricted voltage range than V IH.) The device enters the TTL standby mode when CE# is held at V IH. The device requires the standard access time (t CE) before it is ready to read data.If the device is deselected during erasure or program-ming, the device draws active current until the operation is completed.I CC3 in the DC Characteristics tables represents the standby current specification.Output Disable ModeWhen the OE# input is at V IH, output from the device is disabled. The output pins are placed in the high imped-ance state.Table 2.Am29F010A Sector Addresses Table Autoselect ModeThe autoselect mode provides manufacturer and de-vice identification, and sector protection verification, through identifier codes output on DQ7–DQ0. This mode is primarily intended for programming equipment to automatically match a device to be programmed with its corresponding programming algorithm. However, the autoselect codes can also be accessed in-system through the command register.When using programming equipment, the autoselect mode requires V ID on address pin A9. Address pins A6, A1, and A0 must be as shown in Autoselect Codes (High Voltage Method) table. In addition, when verifying sector protection, the sector address must appear on the appropriate highest order address bits. Refer to the corresponding Sector Address T ables. The Command Definitions table shows the remaining address bits that are don’t care. When all necessary bits have been set as required, the programming equipment may then read the corresponding identifier code on DQ7–DQ0. To access the autoselect codes in-system, the host system can issue the autoselect command via the command register, as shown in the Command Defini-tions table. This method does not require V ID. See “Command Definitions” for details on using the autose-lect mode.Sector A16A15A14Address Range SA000000000h-03FFFh SA100104000h-07FFFh SA201008000h-0BFFFh SA30110C000h-0FFFFh SA410010000h-13FFFh SA510114000h-17FFFh SA611018000h-1BFFFh SA71111C000h-1FFFFh8Am29F010ATable 3.Am29F010A Autoselect Codes (High Voltage Method) L = Logic Low = V IL, H = Logic High = V IH, SA = Sector Address, X = Don’t care.Sector Protection/UnprotectionThe hardware sector protection feature disables both program and erase operations in any sector. The hard-ware sector unprotection feature re-enables both program and erase operations in previously protected sectors.Sector protection/unprotection must be implemented using programming equipment. The procedure re-quires a high voltage (V ID) on address pin A9 and the control pins. Details on this method are provided in a supplement, publication number 20495. Contact an AMD representative to obtain a copy of the appropriate document.The device is shipped with all sectors unprotected. AMD offers the option of programming and protecting sectors at its factory prior to shipping the device through AMD’s ExpressFlash™ Service. Contact an AMD representative for details.It is possible to determine whether a sector is protected or unprotected. See “Autoselect Mode” for details. Hardware Data ProtectionThe command sequence requirement of unlock cycles for programming or erasing provides data protection against inadvertent writes (refer to the Command Defi-nitions table). In addition, the following hardware data protection measures prevent accidental erasure or pro-gramming, which might otherwise be caused by spurious system level signals during V CC power-up and power-down transitions, or from system noise.Low V CC Write InhibitWhen V CC is less than V LKO, the device does not ac-cept any write cycles. This protects data during V CC power-up and power-down. The command register and all internal program/erase circuits are disabled, and the device resets. Subsequent writes are ignored until V CC is greater than V LKO. The system must provide the proper signals to the control pins to prevent uninten-tional writes when V CC is greater than V LKO.Write Pulse “Glitch” ProtectionNoise pulses of less than 5 ns (typical) on OE#, CE# or WE# do not initiate a write cycle.Logical InhibitWrite cycles are inhibited by holding any one of OE# = V IL, CE# = V IH or WE# = V IH. To initiate a write cycle, CE# and WE# must be a logical zero while OE# is a logical one.Power-Up Write InhibitIf WE# = CE# = V IL and OE# = V IH during power up, the device does not accept commands on the rising edge of WE#. The internal state machine is automatically reset to reading array data on power-up.Description CE#Note:OE#WE#A16toA14A13toA10A9A8toA7A6A5toA2A1A0DQ7toDQ0Manufacturer ID: AMD L L H X X V ID X L X L L01h Device ID: Am29F010A L L H X X V ID X L X L H20hSector Protection Verification L L H SA X V ID X L X H L01h (protected)00h (unprotected)Am29F010A9COMMAND DEFINITIONSWriting specific address and data commands or se-quences into the command register initiates device operations. The Command Definitions table defines the valid register command sequences. Writing incorrect address and data values or writing them in the im-proper sequence resets the device to reading array data.All addresses are latched on the falling edge of WE# or CE#, whichever happens later. All data is latched on the rising edge of WE# or CE#, whichever happens first. Refer to the appropriate timing diagrams in the “AC Characteristics” section.Reading Array DataThe device is automatically set to reading array data after device power-up. No commands are required to retrieve data. The device is also ready to read array data after completing an Embedded Program or Em-bedded Erase algorithm.The system must issue the reset command to re-en-able the device for reading array data if DQ5 goes high, or while in the autoselect mode. See the “Reset Com-mand” section, next.See also “Requirements for Reading Array Data” in the “Device Bus Operations” section for more information. The Read Operations table provides the read parame-ters, and Read Operation Timings diagram shows the timing diagram.Reset CommandWriting the reset command to the device resets the de-vice to reading array data. Address bits are don’t care for this command.The reset command may be written between the se-quence cycles in an erase command sequence before erasing begins. This resets the device to reading array data. Once erasure begins, however, the device ig-nores reset commands until the operation is complete. The reset command may be written between the se-quence cycles in a program command sequence before programming begins. This resets the device to reading array data. Once programming begins, how-ever, the device ignores reset commands until the operation is complete.The reset command may be written between the se-quence cycles in an autoselect command sequence. Once in the autoselect mode, the reset command must be written to return to reading array data.If DQ5 goes high during a program or erase operation, writing the reset command returns the device to read-ing array data.Autoselect Command SequenceThe autoselect command sequence allows the host system to access the manufacturer and devices codes, and determine whether or not a sector is protected. The Command Definitions table shows the address and data requirements. This method is an alternative to that shown in the Autoselect Codes (High Voltage Method) table, which is intended for PROM program-mers and requires V ID on address bit A9.The autoselect command sequence is initiated by writ-ing two unlock cycles, followed by the autoselect command. The device then enters the autoselect mode, and the system may read at any address any number of times, without initiating another command sequence.A read cycle at address XX00h or retrieves the manu-facturer code. A read cycle at address XX01h returns the device code. A read cycle containing a sector ad-dress (SA) and the address 02h in returns 01h if that sector is protected, or 00h if it is unprotected. Refer to the Sector Address tables for valid sector addresses. The system must write the reset command to exit the autoselect mode and return to reading array data. Byte Program Command Sequence Programming is a four-bus-cycle operation. The pro-gram command sequence is initiated by writing two unlock write cycles, followed by the program set-up command. The program address and data are written next, which in turn initiate the Embedded Program al-gorithm. The system is not required to provide further controls or timings. The device automatically provides internally generated program pulses and verify the pro-grammed cell margin. The Command Definitions take shows the address and data requirements for the byte program command sequence.When the Embedded Program algorithm is complete, the device then returns to reading array data and ad-dresses are no longer latched. The system can determine the status of the program operation by using DQ7or DQ6. See “Write Operation Status” for informa-tion on these status bits.Any commands written to the device during the Em-bedded Program Algorithm are ignored. Programming is allowed in any sequence and across sector boundaries. A bit cannot be programmed from a “0” back to a “1”. Attempting to do so may halt the operation and set DQ5 to “1”, or cause the Data# Polling algorithm to indicate the operation was suc-cessful. However, a succeeding read will show that the data is still “0”. Only erase operations can convert a “0”to a “1”.10Am29F010ANote:See the appropriate Command Definitions table for program command sequence.Figure 1.Program OperationChip Erase Command SequenceChip erase is a six-bus-cycle operation. The chip erase command sequence is initiated by writing two unlock cycles, followed by a set-up command. Two additional unlock write cycles are then followed by the chip erase command, which in turn invokes the Embedded Erase algorithm. The device does not require the system to preprogram prior to erase. The Embedded Erase algo-rithm automatically preprograms and verifies the entire memory for an all zero data pattern prior to electrical erase. The system is not required to provide any con-trols or timings during these operations. The Command Definitions table shows the address and data require-ments for the chip erase command sequence.Any commands written to the chip during the Embed-ded Erase algorithm are ignored.The system can determine the status of the erase op-eration by using DQ7 or DQ6. See “Write Operation Status” for information on these status bits. When the Embedded Erase algorithm is complete, the device re-turns to reading array data and addresses are no longer latched.Figure 2 illustrates the algorithm for the erase opera-tion. See the Erase/Program Operations tables in “AC Characteristics” for parameters, and to the Chip/Sector Erase Operation Timings for timing waveforms. Sector Erase Command SequenceSector erase is a six bus cycle operation. The sector erase command sequence is initiated by writing two un-lock cycles, followed by a set-up command. Two additional unlock write cycles are then followed by the address of the sector to be erased, and the sector erase command. The Command Definitions table shows the address and data requirements for the sec-tor erase command sequence.The device does not require the system to preprogram the memory prior to erase. The Embedded Erase algo-rithm automatically programs and verifies the sector for an all zero data pattern prior to electrical erase. The system is not required to provide any controls or tim-ings during these operations.After the command sequence is written, a sector erase time-out of 50 µs begins. During the time-out period, additional sector addresses and sector erase com-mands may be written. Loading the sector erase buffer may be done in any sequence, and the number of sec-tors may be from one sector to all sectors. The time between these additional cycles must be less than 50µs, otherwise the last address and command might not be accepted, and erasure may begin. It is recom-mended that processor interrupts be disabled during this time to ensure all commands are accepted. The in-terrupts can be re-enabled after the last Sector Erase command is written. If the time between additional sec-tor erase commands can be assumed to be less than 50 µs, the system need not monitor DQ3. Any com-mand during the time-out period resets the device to reading array data. The system must rewrite the command sequence and any additional sector ad-dresses and commands.The system can monitor DQ3 to determine if the sector erase timer has timed out. (See the “DQ3: Sector Erase Timer” section.) The time-out begins from the rising edge of the final WE# pulse in the command sequence.Once the sector erase operation has begun, all other commands are ignored.When the Embedded Erase algorithm is complete, the device returns to reading array data and addresses are no longer latched. The system can determine the sta-tus of the erase operation by using DQ7 or DQ6. Refer to “Write Operation Status” for information on these status bits.22181B-6Figure 2 illustrates the algorithm for the erase opera-tion. Refer to the Erase/Program Operations tables in the “AC Characteristics” section for parameters, and to the Sector Erase Operations Timing diagram for timing waveforms.Erase Suspend/Erase Resume Commands The Erase Suspend command allows the system to in-terrupt a sector erase operation and then read data from, or program data to, any sector not selected for erasure. This command is valid only during the sector erase operation, including the 50 µs time-out period during the sector erase command sequence. The Erase Suspend command is ignored if written during the chip erase operation or Embedded Program algo-rithm. Writing the Erase Suspend command during the Sector Erase time-out immediately terminates the time-out period and suspends the erase operation. Ad-dresses are “don’t-cares” when writing the Erase Suspend command.When the Erase Suspend command is written during a sector erase operation, the device requires a maximum of 20 µs to suspend the erase operation. However, when the Erase Suspend command is written during the sector erase time-out, the device immediately ter-minates the time-out period and suspends the erase operation.After the erase operation has been suspended, the system can read array data from any sector not se-lected for erasure. (The device “erase suspends” all sectors selected for erasure.) Normal read and write timings and command definitions apply. Reading at any address within erase-suspended sectors produces sta-tus data on DQ7–DQ0. The system can use DQ7 to determine if a sector is actively erasing or is erase-sus-pended. See “Write Operation Status” for information on these status bits.After an erase-suspended program operation is com-plete, the system can once again read array data within non-suspended sectors. The system can determine the status of the program operation using the DQ7 or DQ6 status bits, just as in the standard program oper-ation. See “Write Operation Status” for more information.The system may also write the autoselect command sequence when the device is in the Erase Suspend mode. The device allows reading autoselect codes even at addresses within erasing sectors, since the codes are not stored in the memory array. When the device exits the autoselect mode, the device reverts to the Erase Suspend mode, and is ready for another valid operation. See “Autoselect Command Sequence”for more information.The system must write the Erase Resume command (address bits are “don’t care”) to exit the erase suspend mode and continue the sector erase operation. Further writes of the Resume command are ignored. Another Erase Suspend command can be written after the de-vice has resumed erasing.Notes:1.See the appropriate Command Definitions table for erasecommand sequence.2.See “DQ3: Sector Erase Timer” for more information.Figure 2.Erase Operation。

产品承认书.8doc之英文版规格书

产品承认书SPECIFICATION FOR APPROVAL客户名称(CUSTOMER):客户料号(PART NO.):客户品名(DESCRIPTION):U T 品名(DESCRIPTION): UT-MD070080 V.2 日期(DATE): 2011.7.1CONTENTS contents (2)Change description (3)1. Scope of application (3)2. Product Function Description (3)3. Standard Signal Input (3)4. Work Temp (3)5. Storage Temp (3)6. Operate Power Requirements (3)7. Specification (4)8. Power supply (9)9. Electrical parameters (9)10. LCD Specifications (9)11. Electrical circuit (10)12. Basic operating instructions (10)13. Testing equipment (12)14. Function test (12)15. Reliability test (14)16. Outgoing inspection standards (14)1. Scope of applicationThis standard applies to production for:AT080TN42.AT080TN01.AT080TN03.AT070TN83V.3.AT070TN82 V.1. AT102TN01.AT102TN03.A101VW01..AT080TN52.AT070TN92LCD display module driver board UT-MD070080 V.2 Inspection。

W25Q128BVEIG;中文规格书,Datasheet资料