VHDL语言之调用JK触发器的74Ls290程序

基于计数器74LS290的Multisim仿真出现的问题及处理

基于计数器74LS290的Multisim仿真出现的问题及处理作者:胡洁微周宦银胥飞燕李丽蓉单坤来源:《中国教育技术装备》2016年第24期摘要 Multisim仿真软件是电路分析和设计中常用的一种辅助手段,但若时序逻辑电路设计不当,因时延造成信号畸变,引发电路输出状态偏离原有的“轨道”,将使得电路功能无法实现。

因此,竞争冒险是时序电路设计中必须考虑的重要方面,加入复位电路设计,是解决时序逻辑电路测试生成问题的有效方法。

关键词计数器;Multisim仿真;竞争冒险;复位电路中图分类号:TP391.9 文献标识码:B文章编号:1671-489X(2016)24-0023-03A Problem-solving of Counter 74LS290 Multisim Simulation Cir-cuit//HU Jiewei, ZHOU Huanyin, XU Feiyan, LI Lirong, SHAN KunAbstract Circuit simulation is a common auxiliary analysis and de-sign means by Multisim software, but if the sequential logic circuit design is not correct, the signal distortion may be caused by time delay,and then the output state will deviate from its original orbit, what makesthe circuit functions cannot be achieved. So the race and hazard is quite essential and must be considered when designing logic circuit. Sometimes adding reset circuit design is an important method of sol-ving the sequential logic circuit test generation problem.Key words counter; Multisim simulation; race and hazard; reset circuit1 前言在数字电路中使用最多的时序电路就是计数器电路,计数器不仅可以用于计数,而且可以用于定时、分频、产生脉冲以及进行数字运算等。

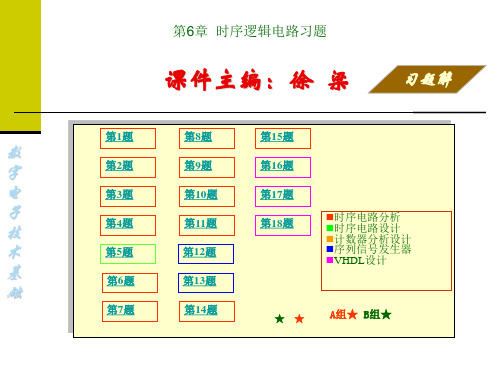

第06章时序逻辑电路习题解

[题6.20]分析图P 6.20给出的电路,说明这是多少进制的计数器,两片之间是多少进制。 74LSl61的功能表见表6.3.4。

解:这是采用整体置数法接成的计数器。 在出现LD'=0信号以前,两片74LSl61均按十六进制计数。即第(1)片到第(2) 片为十六进制。当第(1)片计为2,第(2)片计为5时产生LD'=0信号,待下一个 CLK信号到达后两片74LSl61同时被置零,总的进制为 5 X 16+2+1=83 故为八十三进制计数器。

图A 6.12

[题6.13]试分析图P 6.13的计数器在M=1和M=0时各为几进制。

解:图P6.13电路是采用同步置数法用74160接成的可变进制计数器。在M=1的 状态下,当电路进入Q3Q2Q1Q0=1001(九)以后,LD'=0。下一个CLK到达时将 D3D2D1D0=0100(四)置入电路中,使Q3Q2Q1Q0=0100,再从0100继续作加 法计数。因此,电路在0100到1001这六个状态间循环,构成六进制计数器。同 理,在M=0的情况下,电路计到1001后置入0010(二),故形成八进制计数器。

[题6.6]分析图P 6.6给出的时序电路,画出电路的状态转换图,检查电路能否自启动,说 明电路实现的功能。A为输入变量。

解:由电路图写出驱动方程为 J1=K1=1 J2=K2=A Q1 将上述驱动方程代入JK触发器的特性方程,得到状态方程 Q1*=Q1' Q2*=A Q1 Q2 输出方程为 Y=AQ1Q2+A'Q1'Q2' 根据状态方程和输出方程画出的状态转换图如图A 6.6所示。因为不存在无效 状态,所以电路不存在自启动与否的问题。 当A=0时电路对CLK脉冲作二进制加法计数,A=1时作二进制减法计数。

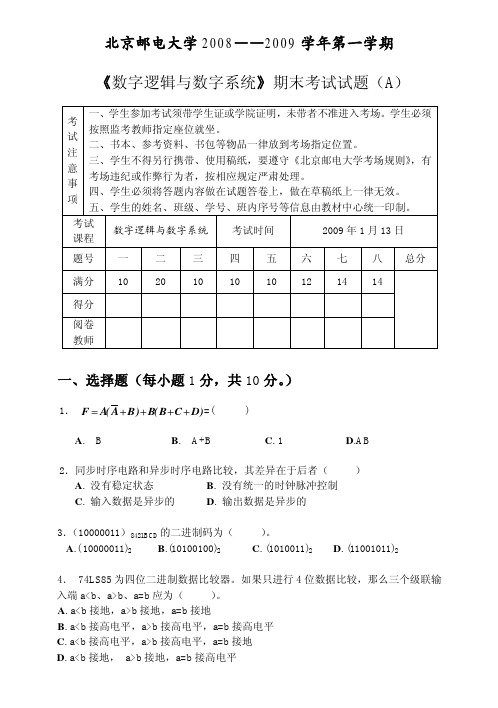

《数字逻辑与数字系统》期末考试试题(A)

北京邮电大学2008——2009学年第一学期《数字逻辑与数字系统》期末考试试题(A )考试注意事项一、学生参加考试须带学生证或学院证明,未带者不准进入考场。

学生必须按照监考教师指定座位就坐。

二、书本、参考资料、书包等物品一律放到考场指定位置。

三、学生不得另行携带、使用稿纸,要遵守《北京邮电大学考场规则》,有考场违纪或作弊行为者,按相应规定严肃处理。

四、学生必须将答题内容做在试题答卷上,做在草稿纸上一律无效。

五、学生的姓名、班级、学号、班内序号等信息由教材中心统一印制。

考试 课程 数字逻辑与数字系统 考试时间 2009年1月13日 题号 一 二 三 四 五 六 七 八 总分满分 10 20 10 10 10 12 14 14 得分 阅卷 教师一、选择题(每小题1分,共10分。

)1. )D C B (B )B A (A F ++++==( )A .B B . A+BC . 1D .AB2.同步时序电路和异步时序电路比较,其差异在于后者( ) A . 没有稳定状态 B . 没有统一的时钟脉冲控制 C . 输入数据是异步的 D . 输出数据是异步的 3.(10000011)8421BCD 的二进制码为( )。

A .( 10000011)2B .(10100100)2C . (1010011)2D . (11001011)24. 74LS85为四位二进制数据比较器。

如果只进行4位数据比较,那么三个级联输入端a<b 、a>b 、a=b 应为( )。

A . a<b 接地,a>b 接地,a=b 接地B . a<b 接高电平,a>b 接高电平,a=b 接高电平C . a<b 接高电平,a>b 接高电平,a=b 接地5. N 个触发器可以构成能寄存( )位二进制数码的寄存器。

A. NB. 2NC. 2ND. N 26.时序电路中对于自启动能力的描述是( )。

A . 无效状态自动进入有效循环,称为具有自启动能力。

用74LS290构成任意进制计数器的方法

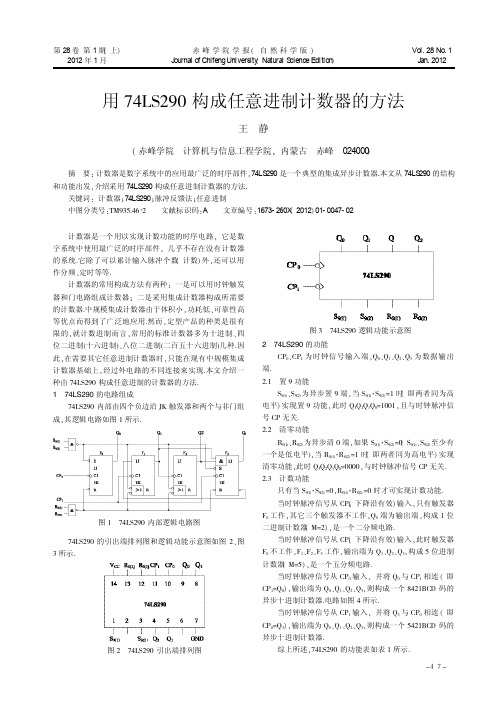

计数器是一个用以实现计数功能的时序电路,它是数字系统中使用最广泛的时序部件,几乎不存在没有计数器的系统.它除了可以累计输入脉冲个数(计数)外,还可以用作分频、定时等等.计数器的常用构成方法有两种:一是可以用时钟触发器和门电路组成计数器;二是采用集成计数器构成所需要的计数器.中规模集成计数器由于体积小,功耗低、可靠性高等优点而得到了广泛地应用.然而,定型产品的种类是很有限的,就计数进制而言,常用的标准计数器多为十进制、四位二进制(十六进制)、八位二进制(二百五十六进制)几种.因此,在需要其它任意进制计数器时,只能在现有中规模集成计数器基础上,经过外电路的不同连接来实现.本文介绍一种由74LS290构成任意进制的计数器的方法.174LS290的电路组成74LS290内部由四个负边沿JK 触发器和两个与非门组成,其逻辑电路如图1所示.74LS290的引出端排列图和逻辑功能示意图如图2、图3所示.274LS290的功能CP 0、CP 1为时钟信号输入端,Q 0、Q 1、Q 2、Q 3为数据输出端.2.1置9功能S 9(1)、S 9(2)为异步置9端,当S 9(1)·S 9(2)=1时(即两者同为高电平)实现置9功能,此时Q 3Q 2Q 1Q 0=1001,且与时钟脉冲信号CP 无关.2.2清零功能R 0(1)、R 0(2)为异步清0端,如果S 9(1)·S 9(2)=0(S 9(1)、S 9(2)至少有一个是低电平),当R 0(1)·R 0(2)=1时(即两者同为高电平)实现清零功能,此时Q 3Q 2Q 1Q 0=0000,与时钟脉冲信号CP 无关.2.3计数功能只有当S 9(1)·S 9(2)=0,R 0(1)·R 0(2)=0时才可实现计数功能.当时钟脉冲信号从CP 0(下降沿有效)输入,只有触发器F 0工作,其它三个触发器不工作,Q 0端为输出端,构成1位二进制计数器(M=2),是一个二分频电路.当时钟脉冲信号从CP 1(下降沿有效)输入,此时触发器F 0不工作,F 1、F 2、F 3工作,输出端为Q 1、Q 2、Q 3,构成5位进制计数器(M=5),是一个五分频电路.当时钟脉冲信号从CP 0输入,并将Q 0与CP 1相连(即CP 1=Q 0),输出端为Q 0、Q 1、Q 2、Q 3,则构成一个8421BCD 码的异步十进制计数器.电路如图4所示.当时钟脉冲信号从CP 1输入,并将Q 3与CP 0相连(即CP 0=Q 3),输出端为Q 0、Q 1、Q 2、Q 3,则构成一个5421BCD 码的异步十进制计数器.综上所述,74LS290的功能表如表1所示.图374LS290逻辑功能示意图图274LS290引出端排列图图174LS290内部逻辑电路图Vo l.28No .1J an.2012赤峰学院学报(自然科学版)J ournal o f ChifengUniversity (Natural S cience Editio n )用74LS290构成任意进制计数器的方法王静(赤峰学院计算机与信息工程学院,内蒙古赤峰024000)摘要:计数器是数字系统中的应用最广泛的时序部件,74LS 290是一个典型的集成异步计数器.本文从74LS 290的结构和功能出发,介绍采用74LS 290构成任意进制计数器的方法.关键词:计数器;74LS 290;脉冲反馈法;任意进制中图分类号:TM935.46+2文献标识码:A文章编号:1673-260X (2012)01-0047-02第28卷第1期(上)2012年1月47--以下是用一片74LS290构成一个七进制计数器的具体方法:首先将74LS290构成8421BCD 码十进制计数器.再用脉冲反馈法.因N=7,对应的BCD 码S N =0111,令R 0(1)=R 0(2)=Q 2Q 1Q 0(Q 2Q 1Q 0通过一个与门与R 0(1)、R 0(2)相连),按图5连线.当Q 3Q 2Q 1Q 0=0111时,迅速复位到0000,然后又开始从0000状态计数.0111状态出现的时间极短,通常只有10ns 左右,并不能看到.因而我们认为该电路是一个实现从0000~0110的七进制计数器.3.2构成大容量计数器第一步:采用级联的方法,将多个集成计数器串联起来,扩大计数器的容量.74LS290没有专门的进位信号输出端,可以用本级的高位输出信号驱动下一级计数器.第二步:采用脉冲反馈法获得所需的计数器.以下是用两片74LS290构成一个84进制计数器的具体方法:首先将每块74LS290按8421BCD 十进制方式连线,分别代表个位和十位.然后设计计数到84返回清零.由于N=84,对应的BCD码SN=10000100,当十位计到8,个位计到4时,在下一计数脉冲下降沿到来后个位、十位计数器均复位到0,从而完成84进制计数的功能.电路如图6所示.4结论74LS290的功能很强,利用脉冲反馈法,适当改变连线、配合门电路就可以灵活地构成任意进制的计数器.如果要构成的计数器容量为1位数,用一片74LS290;如果要构成的计数器容量为两位数,则要用两片74LS290;如要构成更大容量的计数器只需适当地增加74LS290的数量即可.电路结构较为简单,应用广泛.———————————————————参考文献:〔1〕胡晓光.数字电子技术基础[M].北京:高等教育出版社,2010.〔2〕余孟尝.数字电子技术简明教程[M].北京:高等教育出版社,2006.〔3〕张克农,宁改娣.数字电子技术基础[M].北京:高等教育出版社,2010.〔4〕王小海,祁才君,阮秉涛.集成电子技术基础教程[M].北京:高等教育出版社,2008.图684进制计数器图474LS290BCD 码十进制计数器3用74LS290设计任意进制的计数器利用脉冲反馈法获得N 进制计数器,用S 0、S 1、S 2…S N 表示输入0、1、2、…、N 个计数脉冲CP 时计数器的状态.N 进制计数器的计数工作状态应为N 个:S 0、S 1、S 2…S N -1,在输入第N 个脉冲CP 后,通过控制电路利用SN 产生一个有效置0信号,送给异步置0端,使计数器立即置0,即实现了N 进制计数.3.1构成比模十小的任意进制计数器采用脉冲反馈法,如需设计N 进制计数器,就把N 对应的BCD 码中为“1”的输出端进行“与”运算,结果接到74LS290的R 0(1)、R 0(2)端即可.图5七进制计数器输入输出R 0(1)·R 0(2)S 9(1)·S 9(2)CP 0CP 1Q 0Q 1Q 2Q 310××0000(清零)×1××11(置9)00↓00100↓0Q 31↓Q 0↓二进制计数五进制计数8421码十进制计数5421码十进制计数表174LS290的功能表48--。

基于VHDL跑马灯课程设计

目录一.设计任务与要求 (1)(1)方案论证 (1)(2)原理框图 (1)二.总体框图 (1)三.选择器件 (1)四.功能模块 (2)(1) 八分频模块 (2)(2) JK触发器连接的两位加法计数器 (2)(3) ROM32X8 (3)(4) 实现循环闪烁和模式切换的具体说明 (3)(5) 74LS283与7446组成模式显示电路 (5)(6) 仿真波形 (7)五.总体设计电路图 (7)六.设计心得 (14)课程设计一.设计任务与要求1.在八个LED灯上实现从左至右,从右至左,从两边到中间,从中间到两边;四种模式的闪烁。

2.四种模式是事先设置的。

3.实现四种模式的手动切换。

二.总体框图(1)方案论证:本方案采用一片74LS293与两片JK触发器。

74LS293是4位异步二进制加法计数器。

本方案采用它的八分频功能,构成一个八进制循环电路。

并且将两个JK触发器连接成一个两位加法器且由手动开关输入时钟沿。

两部分组合起来实现每种模式的地址线依次循环导通以及四种模式的切换。

用一片ROM32X8来存储四种闪烁模式。

输出连接八个LED灯。

用74LS283与7446连接成显示电路,在实验板上的七段数码管显示模式的编号。

(2)原理框图:图1——原理框图三.选择器件1.主芯片:Altera®的Cyclone EPEC12Q240C82.八个LED灯3.一个自动反弹开关4.EDA实验箱一台5.含有QuartusⅡ软件的计算机一台6.导线若干四.功能模块(1)八分频模块图二——74LS293模块A实现的是一位二进制循环。

B,C,D实现的是三位八进制循环。

本设计使用B,C,D端。

在CLKB加时钟信号后,BCD端实现八进制循环。

内部原理图如下:图三——74LS293内部结构图八分频模块电路图:图四——八分频模块仿真波形:图五——仿真波形分析:CLRA,CLRB为清零信号端,全部接地使失效。

时钟信号输入端CLKA控制QA计数。

VHDL程序设计及应用

ENTITY dff IS PORT(d,clk,Sd,Rd: IN STD_LOGIC; q1,q2: OUT STD_LOGIC);

END dff; ARCHITECTURE xdff OF dff IS BEGIN

PROCESS (时钟信号名[,其它敏感信号]) BEGIN

IF 时钟信号边沿/电平描述 AND 置/复位条件表达式 THEN 置/复位语句;

ELSE 正常执行语句;

ENDIF

格式二:

PROCESS BEGIN

WAIT UNTIL 时钟信号边沿/电平描述 IF 置/复位条件表达式 THEN

置/复位语句; ELSE

ELSE IF Sd=‘1’ THEN q1<=‘1’; q2<=‘0’;

ELSE IF(clk’EVENT AND clk=‘1’) THEN q1<=d; q2<=NOT d;

END IF END PROCESS; END xdff;

例四:JK触发器

[说明]带异步置/复位端的JK触发器采用下降沿触发方式。该触发器有两个数据输入端 j、k;一个时钟输入端clk;一个直接复位端Rd;一个直接置位端Sd;两个数 据输出端q1、q2。假设置/复位信号为低电平有效。

PROCESS(clk) BEGIN

IF(clk’EVENT AND clk=‘1’) THEN IF Rd=‘0’ THEN q1<=‘0’; q2<=‘1’; ELSEIF Sd=‘0’ THEN q1<=‘1’; q2<=‘0’;

ELSE q1<=d; q2<=NOT d;

数字电子技术试卷及答案五套

数字电子技术试卷一、选择题:A组:1.如果采用偶校验方式,下列接收端收到的校验码中,( A )是不正确的A、00100B、10100C、11011D、111102、某一逻辑函数真值表确定后,下面描述该函数功能的方法中,具有唯一性的是(B)A、逻辑函数的最简与或式B、逻辑函数的最小项之和C、逻辑函数的最简或与式D、逻辑函数的最大项之和3、在下列逻辑电路中,不是组合逻辑电路的是(D)A、译码器B、编码器C、全加器D、寄存器4、下列触发器中没有约束条件的是(D)A、基本RS触发器B、主从RS触发器C、同步RS触发器D、边沿D触发器5、555定时器不可以组成D。

A.多谐振荡器B.单稳态触发器C.施密特触发器D.J K触发器6、编码器(A)优先编码功能,因而(C)多个输入端同时为1。

A、有B、无C、允许D、不允许7、(D)触发器可以构成移位寄存器。

A、基本RS触发器B、主从RS触发器C、同步RS触发器D、边沿D触发器8、速度最快的A/D转换器是(A)电路A、并行比较型B、串行比较型C、并-串行比较型D、逐次比较型9、某触发器的状态转换图如图所示,该触发器应是( C )A. J-K触发器B. R-S触发器C. D触发器D. T触发器10.(电子专业作)对于VHDL以下几种说法错误的是(A )A VHDL程序中是区分大小写的。

B 一个完整的VHDL程序总是由库说明部分、实体和结构体等三部分构成C VHDL程序中的实体部分是对元件和外部电路之间的接口进行的描述,可以看成是定义元件的引脚D 结构体是描述元件内部的结构和逻辑功能B组:1、微型计算机和数字电子设备中最常采用的数制是--------------------------------( A )A.二进制B.八进制C. 十进制D.十六进制2、十进制数6在8421BCD码中表示为-------------------------------------------------( B )A.0101B.0110C. 0111D. 10003、在图1所示电路中,使__AY 的电路是---------------------------------------------( A )A. ○1B. ○2C. ○3D. ○44、接通电源电压就能输出矩形脉冲的电路是------------------------------------------( D )A. 单稳态触发器B. 施密特触发器C. D触发器D. 多谐振荡器5、多谐振荡器有-------------------------------------------------------------------------------( C )A. 两个稳态B. 一个稳态C. 没有稳态D. 不能确定6、已知输入A、B和输出Y的波形如下图所示,则对应的逻辑门电路是-------( D )A. 与门B. 与非门C. 或非门D. 异或门7、下列电路中属于时序逻辑电路的是------------------------------------------------------( B )A. 编码器B. 计数器C. 译码器D. 数据选择器8、在某些情况下,使组合逻辑电路产生了竞争与冒险,这是由于信号的---------( A )A. 延迟B. 超前C. 突变D. 放大9、下列哪种触发器可以方便地将所加数据存入触发器,适用于数据存储类型的时序电路--------------------------------------------------------------------------------( C )A. RS触发器B. JK触发器C. D触发器D. T触发器10、电路和波形如下图,正确输出的波形是-----------------------------------------------( A )A. ○1B. ○2C. ○3D. ○4C组:1.十进制数25用8421BCD码表示为 B 。

数电复习题

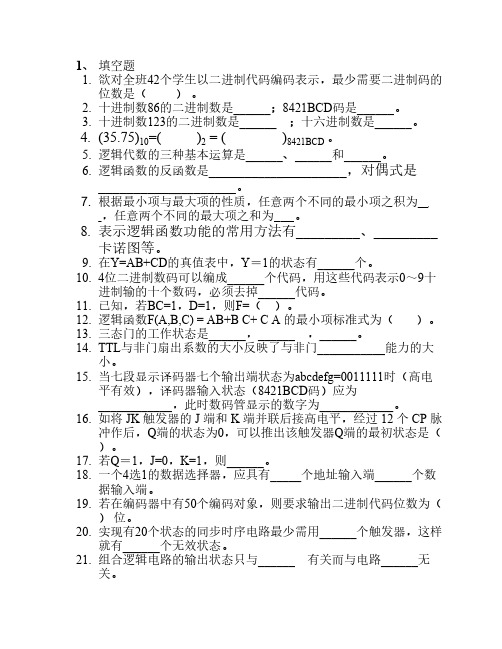

1、填空题1. 欲对全班42个学生以二进制代码编码表示,最少需要二进制码的位数是()。

2. 十进制数86的二进制数是______;8421BCD码是______。

3. 十进制数123的二进制数是______ ;十六进制数是______。

4. (35.75)10=( )2 = ( )8421BCD 。

5. 逻辑代数的三种基本运算是______、______和______。

6. 逻辑函数的反函数是____________________,对偶式是____________________。

7. 根据最小项与最大项的性质,任意两个不同的最小项之积为,任意两个不同的最大项之和为。

8. 表示逻辑函数功能的常用方法有_________、_________卡诺图等。

9. 在Y=AB+CD的真值表中,Y=1的状态有______个。

10. 4位二进制数码可以编成______个代码,用这些代码表示0~9十进制输的十个数码,必须去掉______代码。

11. 已知,若BC=1,D=1,则F=()。

12. 逻辑函数F(A,B,C) = AB+B C+ C A 的最小项标准式为()。

13. 三态门的工作状态是______,______ ,______。

14. TTL与非门扇出系数的大小反映了与非门___________能力的大小。

15. 当七段显示译码器七个输出端状态为abcdefg=0011111时(高电平有效),译码器输入状态(8421BCD码)应为____________,此时数码管显示的数字为____________。

16. 如将 JK 触发器的 J 端和 K 端并联后接高电平,经过 12 个 CP 脉冲作后,Q端的状态为0,可以推出该触发器Q端的最初状态是()。

17. 若Q=1,J=0,K=1,则______。

18. 一个4选1的数据选择器,应具有_____个地址输入端______个数据输入端。

19. 若在编码器中有50个编码对象,则要求输出二进制代码位数为()位。