第6章 Verilog仿真与验证

数字电路仿真与验证

数字电路仿真与验证数字电路是现代电子技术的基础,广泛应用于计算机、通信和其他电子设备中。

数字电路的设计和验证是确保电路能够按照预期工作的关键步骤。

本文将介绍数字电路仿真与验证的重要性以及常用的方法和工具。

一、数字电路仿真的意义数字电路的设计过程复杂且耗时,因此在将其实际制造之前,必须通过仿真来验证其功能和性能。

数字电路仿真的主要目的是通过计算机模拟电路行为,检查其逻辑功能、时序性能和稳定性。

具体来说,仿真可以帮助设计师发现和解决潜在的问题,减少设计错误和重复制造的风险,提高电路设计的可靠性和效率。

二、数字电路仿真的方法1. 行为级仿真:行为级仿真是通过对数字电路的逻辑功能进行建模和测试。

在这种仿真方法中,电路的输入和输出通过逻辑信号表示,并在仿真器中进行模拟计算。

这种仿真方法可以验证电路是否满足设计要求,并帮助发现逻辑错误。

2. 时序级仿真:时序级仿真是针对时序电路设计的一种仿真方法。

时序电路涉及时钟信号和时序逻辑,需要确保电路正确地响应时钟的上升沿和下降沿。

时序级仿真可以验证时序电路的时序特性,包括信号延迟、时钟抖动和稳定性等。

3. 功能级仿真:功能级仿真可以对整个数字系统进行仿真,包括多个数字电路模块的集成。

通过功能级仿真,可以验证数字系统的整体功能和性能,以及各个模块之间的接口和通信。

三、数字电路仿真工具的选择1. SPICE仿真工具:SPICE(Simulation Program with Integrated Circuit Emphasis)是一种常用的模拟电路仿真工具,可以用于数字电路的仿真。

它可以帮助设计师验证电路的逻辑和模拟行为,并检查电路的时序特性。

2. HDL仿真工具:HDL(Hardware Description Language)仿真工具是专门用于数字电路设计的仿真工具。

常用的HDL语言包括VHDL (VHSIC Hardware Description Language)和Verilog HDL。

verilog教程

verilog教程Verilog是一种硬件描述语言(HDL),用于描述数字系统的行为和结构。

它是一种流行的HDL,广泛用于硬件设计和验证领域。

本教程将介绍Verilog的基本概念和语法,以帮助初学者入门。

一、Verilog的基本概念1.1 什么是VerilogVerilog是一种描述数字系统的语言,它可以用来描述硬件电路、验证设计的正确性以及进行电路仿真。

1.2 Verilog的应用领域Verilog广泛应用于硬件设计和验证领域,包括用于开发ASIC(应用特定集成电路)、FPGA(现场可编程门阵列)以及其他数字系统的设计。

1.3 Verilog的版本Verilog有多个版本,包括Verilog-1995、Verilog-2001以及最新的Verilog-2005、这些版本之间有一些语法和功能上的差异。

二、Verilog的语法结构2.1模块和端口在Verilog中,所有的电路描述都是由模块(module)组成的。

模块是电路的基本组成单元,可以看作是一个黑盒子,它接受一些输入,产生一些输出。

2.2信号声明在Verilog中,我们需要声明所有的输入和输出信号。

可以使用`input`和`output`关键字来声明这些信号。

2.3电路实现Verilog允许使用多种语句和结构来描述电路的行为和结构。

这些语句包括顺序语句、条件语句、循环语句以及层次结构。

2.4实例化模块在一个模块中,我们可以实例化其他的模块。

这样可以将一个大的电路拆分成多个小的模块,方便编写和测试。

三、Verilog的仿真和验证3.1静态验证Verilog语言本身提供了很多语法和语义层面的验证功能,对于语法和类型错误会有相应的提示。

3.2激励设计在进行电路验证时,我们需要为输入信号提供激励。

Verilog提供了一种称为`testbench`的特殊模块,用于生成输入信号并将其应用到待验证的电路中。

3.3波形仿真在Verilog中,我们可以使用仿真器来模拟电路的行为,并生成波形图来验证电路是否按预期工作。

FPGA仿真验证

第一编验证的重要性验证,顾名思义就是通过仿真、时序分析、上板调试等手段检验设计正确性的过程,在FPGA/IC开发流程中,验证主要包括功能验证和时序验证两个部分。

为了了解验证的重要性,我们先来回顾一下FPGA开发的整个流程。

FPGA开发流程和IC的开发流程相似,主要分为以下几个部分:1)设计输入,利用HDL输入工具、原理图输入工具或状态机输入工具等把所要设计的电路描述出来;2)功能验证,也就是前仿真,利用Modelsim、VCS等仿真工具对设计进行仿真,检验设计的功能是否正确;常用的仿真工具有Model Tech公司的ModelSim,Synopsys公司的VCS,Cadence公司的NC-Verilog和NC-VHDL,Aldec公司的Active HDL VHDL/Verilog HDL等。

仿真过程能及时发现设计中的错误,加快了设计进度,提高了设计的可靠性。

3)综合,综合优化是把HDL语言翻译成最基本的与或非门的连接关系(网表),并根据要求(约束条件)优化所生成的门级逻辑连接,输出edf和edn等文件,导给CPLD/FPGA厂家的软件进行实现和布局布线。

常用的专业综合优化工具有Synplicity公司的synplify/Synplify Pro、Amplify等综合工具,Synopsys公司的FPGA Compiler II综合工具(Synopsys 公司将停止发展FPGA Express软件,而转到FPGA Compiler II平台),Exemplar Logic公司出品的LeonardoSpectrum等综合工具。

另外FPGA/CPLD厂商的集成开发环境也带有一些综合工具,如Xilinx ISE中的XST等。

4)布局布线,综合的结果只是通用的门级网表,只是一些门与或非的逻辑关系,与芯片实际的配置情况还有差距。

此时应该使用FPGA/CPLD厂商提供的实现与布局布线工具,根据所选芯片的型号,进行芯片内部功能单元的实际连接与映射。

数字系统设计与verilog HDL 第6章

4.关系运算符(Relational operators) < 小于 <= 小于或等于 > 大于 >= 大于或等于

5.等式运算符(Equality Operators) == 等于 != 不等于 === 全等 !== 不全等

例:对于A=2'b1x和 B=2'b1x,则 A==B结果为x, A===B结果为1

关键字(Keywords)

Verilog语言内部已经使用的词称为关键字或

保留字,这些保留字用户不能作为变量或节点

名字使用。

关键字都是小写的。

6.2 常量

程序运行中,值不能被改变的量称为 常量(constants),Verilog中的常量主 要有如下3种类型:

◆ 整数 ◆ 实数

◆ 字符串

整数(integer)

字符串(Strings)

字符串是双引号内的字符序列。 字符串不能分成多行书写。例如:

"INTERNAL ERROR"

字符串的作用主要是用于仿真时,显示一些 相关的信息,或者指定显示的格式。

6.3 数据类型

数据类型(Data Type)是用来表示数字电路中的 物理连线、数据存储和传输单元等物理量的。

空白符和注释

空白符(White space) 空白符包括:空格、tab、换行和换页。空白符使 代码错落有致,阅读起来更方便。在综合时空白符 被忽略。 注释(Comment) ◆ 单行注释:以“//”开始到本行结束,不允许续 行 ◆ 多行注释:多行注释以“/*”开始,到“*/”结 束

标识符(Identifiers)

第6章 Verilog HDL语法与要素

主要内容

verilog仿真验证流程

verilog仿真验证流程Verilog simulation verification flow is a crucial step in the development process of digital designs. It ensures that the design functions as expected before moving on to the implementation stage. The process involves writing testbenches to stimulate the design and check its outputs against the expected results. This iterative process helps uncover bugs and issues early on, saving time and effort in the long run.Verilog仿真验证流程在数字设计开发过程中是一个至关重要的步骤。

它确保设计在进入实现阶段之前能如预期地工作。

该过程涉及编写测试平台来激励设计并检查其输出与预期结果是否一致。

这个迭代过程有助于及早发现错误和问题,从而节省时间和精力。

When it comes to Verilog simulation verification flow, there are several key components to consider. First, the design under test (DUT) should be thoroughly understood to create effective testbenches. Understanding the functionality and expected behavior of the DUT is crucial in writing stimuli that will exercise all aspects of the design. Next, the testbench itself needs to be carefully crafted toensure comprehensive coverage of the design. This includes creating test cases that cover both typical and edge-case scenarios to verify the robustness of the design.说到Verilog仿真验证流程,有几个关键组成部分需要考虑。

veriloga语法 electrical

veriloga语法electrical摘要:1.Verilog 语法基础2.电路描述与建模3.仿真与验证4.设计与实现正文:Verilog 是一种硬件描述语言,广泛应用于数字系统设计和验证。

在电子电路设计中,Verilog 可以描述和模拟电路行为,帮助工程师进行电路设计和优化。

下面我们将详细介绍Verilog 的基本语法以及如何使用Verilog 进行电路建模和仿真验证。

1.Verilog 语法基础Verilog 语法主要包括基本的数据类型、运算符、控制结构和模块等。

数据类型包括布尔型、整数型、实数型等,运算符包括算术运算符、关系运算符和逻辑运算符等。

控制结构包括if-else 语句、for 循环、while 循环等。

模块则是Verilog 设计的基本单元,包括输入端口、输出端口和行为描述等。

2.电路描述与建模使用Verilog 进行电路描述时,需要首先了解电路的基本结构和原理。

然后,通过Verilog 语言中的各种语法元素,描述电路的输入输出关系、逻辑行为等。

例如,可以使用verilog 中的"and"门、"or"门、"not"门等基本逻辑门来构建复杂的逻辑电路。

3.仿真与验证在Verilog 中,可以利用仿真工具对设计的电路进行功能验证。

常用的仿真工具包括ModelSim、VCS 等。

通过编写测试平台,可以对电路进行功能测试,检查电路是否按照预期进行工作。

仿真验证是电子设计过程中非常重要的环节,可以有效提高设计质量和可靠性。

4.设计与实现在完成电路建模和仿真验证后,可以进一步进行电路的实际设计和制作。

这包括硬件制作、软件编程等多个环节。

通过Verilog 语言,可以生成对应的硬件描述文件,供后续硬件制作和测试使用。

同时,Verilog 也可以与其他EDA 工具(如Cadence、Mentor Graphics 等)相结合,实现整个电子设计流程的自动化和智能化。

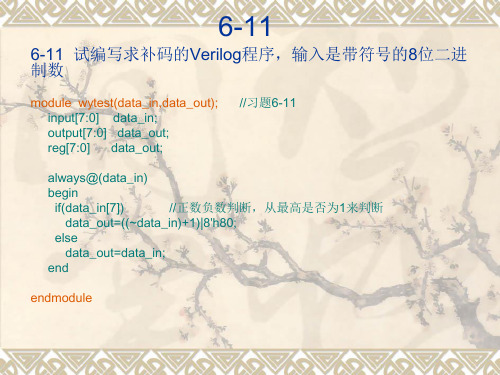

EDA技术与Verilog设计第六章课后习题部分答案

else case(in) 3'd0: out=8'b11111110; 3'd1: out=8'b11111101; 3'd2: out=8'b11111011; 3'd3: out=8'b11110111; 3'd4: out=8'b11101111; 3'd5: out=8'b11011111; 3'd6: out=8'b10111111; 3'd7: out=8'b01111111; endcase end

6-11仿真波形

8A-原码表示的十进制数-10 B6-原码表示的十进制数-54 80-原码表示的十进制数128 0A----十进制数10 36-----十进制数53

6-12

6-12 编写两个四位二进制数相减的verilog程序

module wytest(opr1,opr2,out_data); //完成Opr1-opr2的运算 input[3:0] opr1,opr2; output[4:0] out_data; reg[3:0] out; reg cout; function[3:0] abs; input[3:0] data; case(data[3]) 1'b0:abs=data; 1'b1:abs=(~data)+1; //对负数求绝对值,按位取反再加1 endcase endfunction

6-13

仿真波形

6-13

module wytest(bcd_in,out); //习题6-13 input[3:0] bcd_in; output out; //assign out=(bcd_in>4)?1:0;

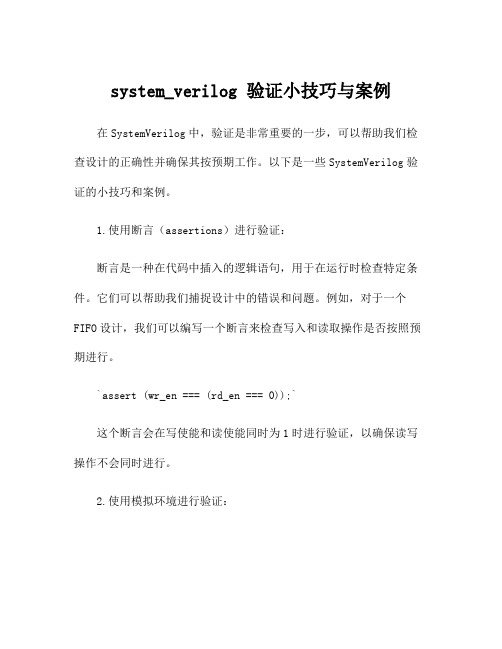

system_verilog 验证小技巧与案例

system_verilog 验证小技巧与案例在SystemVerilog中,验证是非常重要的一步,可以帮助我们检查设计的正确性并确保其按预期工作。

以下是一些SystemVerilog验证的小技巧和案例。

1.使用断言(assertions)进行验证:断言是一种在代码中插入的逻辑语句,用于在运行时检查特定条件。

它们可以帮助我们捕捉设计中的错误和问题。

例如,对于一个FIFO设计,我们可以编写一个断言来检查写入和读取操作是否按照预期进行。

`assert (wr_en === (rd_en === 0));`这个断言会在写使能和读使能同时为1时进行验证,以确保读写操作不会同时进行。

2.使用模拟环境进行验证:在验证过程中,我们通常需要创建一个模拟环境来模拟设计的行为。

这个环境通常包括一个测试程序和设计的驱动程序、监听器和功能模型等。

测试程序主要用于生成输入和验证输出,而驱动程序则负责将测试向设计输入,监听器则用于捕获设计的输出并与期望值进行比较,功能模型则用于模拟设计的行为。

例如,对于一个简单的计数器设计,我们可以编写一个测试程序来递增计数器的值,并验证计数器的值是否按预期递增。

3.使用覆盖率分析:覆盖率分析是一种用于确定设计代码是否已被完全测试的方法。

SystemVerilog提供了覆盖率分析的功能,可以帮助我们确定代码的覆盖率,并找出未被完全测试的部分。

覆盖率分析可以使用covergroup和coverpoints来实现。

covergroup提供了用于组织和管理覆盖率数据的方法,而coverpoints则用于指定要测试的代码的特定部分。

例如,对于一个模块,我们可以使用covergroup来收集每个输入组合的覆盖率,并确定哪些输入组合尚未被测试到。

4.使用随机化测试:SystemVerilog提供了一些功能,例如randomize()和randomize_with(),可用于生成随机输入并对设计进行测试。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

//显示

ModelSim仿真结果

⑶、延时说明块(specify块)

Verilog可对模块中某一指定的路径进行延迟定义,这一 路径连接模块的输入端口(或inout端口)与输出端口 (或inout端口),利用延迟定义块在一个独立的块结构 中定义模块的延时。在延迟定义块中要描述模块中的不 同路径并给这些路径赋值。 延迟定义块的内容应放在关键字specify与endspecify 之间,且必须放在一个模块中,还可以使用specparam 关键字定义参数。

系统任务和系统函数只能用于仿真,在系统综合过程中被忽略。

系统任务与函数分类

⑴显示任务 ⑵文件输入与输出任务 ⑶仿真控制任务 ⑷时间标度任务 ⑸ PLA建模任务 ⑹随机建模任务 ⑺变换函数 ⑻概率分布函数 ⑼字符格式化 ⑽命令行参变量

1.系统任务

⑴、$display与$write $display和$write是两个显示与写系统任务, 两者的功能相同,都用于显示模拟结果,其区别 是$display在输出结束后能自动换行,而 $write不能。 $display和$write的使用格式为: $display(“格式控制符”,输出变量名列表); $write(“格式控制符”,输出变量名列表);

2、系统函数

⑴、$time与$realtime

$time、$realtime是属于显示仿真时间标度的系 统函数。这两个函数被调用时,都返回当前时刻 距离仿真开始时刻的时间量值,所不同的是, $time 函数以64位整数值的形式返回模拟时间, $realtime 函数则以实数型数据返回模拟时间。 如上加法器仿真调试程序。

⑵、$monitor与$strobe

$monitor、$strobe与$display、$write一样 也是属于输出控制类的显示系统任务, $monitor与$strobe都提供在指定时刻监控和 输出参数列表中字符或变量的值的功能;而 $display、$write任务在执行到该语句时执行。 其使用格式为: $monitor(“格式控制符”,输出变量名列表); $strobe(“格式控制符”,输出变量名列表); 这里的格式控制符、输出变量名列表与 $display和$write中定义的完全相同。

还有其它系统任务和函数用于读取文件中数据:

$fread : 从文件中读取二进制数据到存储器中。 $fgetc :从文件中每次读取一个字符。 $fgets :从文件中每次读取一行。 $ungetc :把一个字符插入文件中。 $frewind :重新回到文件的开始处。 $fseek :移动到偏移量指定的位置。 $ftell :返回以文件开始处为基址的偏移量。 $fscanf :从文件,帮助判断 出错误的原因。

⑵、$random

$random是产生随机数的系统函数,每次调用该函数将 返回一个32位的随机数,该随机数是一个带符号的整数。

⑶、$fopen和$fclose $fopen 和$fclose用于打开和关闭一个文件系统函数,

完成后返回一个与文件相关的整数指针。

6.2编译指令的使用

编译指令:

1、宏定义语句define和宏取消语句undef

以返回0个或多个值,而系统函数除只能返回一个值外,与

任务类似。例如:$monitor,$readmemh等。 ◆ 使用不同的Verilog仿真工具(如:VCS、Verilog-XL、 ModelSim等)进行仿真时,这些系统任务和系统函数在 使用方法上可能存在差异,应根据使用手册来使用。 ◆ 一般在intial或always过程块中,调用系统任务和系统 函数。 ◆ 用户可以通过编程语言接口(PLI)将自己定义的系统 任务和系统函数加到语言中,以进行仿真和调试。

⑵、延时的表示与延时说明块

延时的表示方法有下面几种: # delaytime # (d1,d2) # (d1,d2,d3) # delaytime表示延迟时间为delaytime,d1表示上升延 迟,d2表示下降延迟,d3则表示转换到高阻态z的延迟, 这些延迟的具体时间由时间定义语句'timescale确定。

如:语句间延时:sum=(a^b)^cin #4 t1=a&cin 如:语句内延时:sum=#3(a^b)^cin 如果没有定义时延值,缺省时延为0。

激励波形仿真测试程序

【例6.2】 激励波形的描述

0 100 200 300 `timescale 1ns/1ns module test1; a reg a,b,c; initial b begin a=0;b=1;c=0; #100 c=1; c #100 a=1;b=0; #100 a=0; #100 c=0; #100 $stop; end initial $monitor($time,,,"a=%d b=%d c=%d",a,b,c); endmodule 400

module full_adder(cout,si,ai,bi,cin); output si,cout; input ai,bi,cin; assign {cout,si}=ai+bi+cin; endmodule

仿真结果

time ai bi cin cout sum # 0 0 + 0 + 0={0, 0} # 10 0 + 0 + 1={0, 1} # 20 0 + 1+ 0={0, 1} # 30 0 + 1+ 1={1, 0} # 40 1 + 0+ 0={0, 1} # 50 1 + 0+ 1={1, 0} # 60 1 + 1+ 0={1, 0} # 70 1 + 1+ 1={1, 1} # 80 0 + 0+ 0={0, 0} # 90 0 + 0+ 1={0, 1} #100 0 + 1+ 0={0, 1} #110 0 + 1+ 1={1, 0} #120 1 + 0+ 0={0, 1} #130 1 + 0+ 1={1, 0} #140 1 + 1+ 0={1, 0} #150 1 + 1+ 1={1, 1}

采用层次电路设计的全加器仿真显示测试程序

`timescale 1ns/1ps module full_adder_tb; reg[2:0]in; wire sum, cout; integer i,j; full_adder FA(.cout(cout),.si(sum),.ai(in[2]),.bi(in[1]),.cin(in[0])); always #10 in=in+1; initial begin in=0; $display(" time ai bi cin cout sum"); $monitor($time,,,"%b+%b+%b={%b,%b}",in[2],in[1],in[0],cout, sum); #160 $finish; end endmodule

⑶$finish与$stop

系统任务$finish与$stop用于对仿真过程进行控制,分 别表示结束仿真和中断仿真。 $finish与$stop 的使用格式如下: $stop; $stop(n); $finish; $finish(n); n是$finish和$stop的参数,n 可以是0、1、2等值,分 别表示如下含义。 0:不输出任何信息; 1:给出仿真时间和位置; 2:给出仿真时间和位置,还有其他一些运行统计数据。

第6章 Verilog仿真与验证

第6章

Verilog仿真与验证

6.1 系统任务与系统函数

内容

6.2 系统预定义指令

6.3用户自定义元件(UDP) 6.4测试平台 6.5 ModelSim仿真实例 6.6数字电路的仿真

6.1 系统任务与系统函数

◆ 系统任务和系统函数一般以符号“$”开头。系统任务可

用于仿真真实数字电路运行时的电路延时情况和人为设计

的波形输出。

⑴、时间标尺预定义语句`timescale

`timescale语句用于定义模块中指令运行的时间单位和时间 精度,其使用格式如下: `timescale <time_unit>/<time_precision> `timescale <时间单位>/<时间精度> 其中用来表示时间度量的符号有:s、ms、us、ns、ps和fs, 时间单位必须取整数,指令运行时间以时间单位为基准,多 少以时间精度进行取舍。 例如:`timescale 1ns/100ps 上面的语句表示时延单位为1ns,时延精度为100ps(即精确 到0.1ns)。`timescale编译器指令在模块说明外部出现, 并且影响后面所有的时延值,直到遇到另一个`timescale指 令或`resetall指令 。当一个文件含有多个模块,且每个模块 都有各自`timescale指令时,以精度最小的为基准时间精度。

格式控制符

格式控制 符 说明 转义字符 \n \t \\ \“

转义字符

说明 换行 TAB键 符号\ 符号“

%h或%H 以16进制形式显示

%d或%D 以10进制形式显示 %o或%O 以8进制形式显示 %b或%B %c或%C 以2进制形式显示 以ASCII字符形式显示

\ ddd

%%

%v或%V

%m或 %M %s或%S

`include “../../文件名” 其作用是将指定的文件一同与当前文件进行编译,指定文件可以 是相对路径和绝对路径。

3、仿真延时模型的表示

延时包括门延时、assign赋值延时和连线延时等。

门延时是从门输入端发生变化到输出端发生变化的延 迟时间; assign赋值延时指等号右端某个值发生变化到等号左 端发生相应变化的延迟时间; 连线延时则体现了信号在连线上的传输延时。 如果没有定义时延值,缺省时延为0。 延时语句用于仿真测试中,它不能综合生成硬件,主要