高速PCB布线的考量ppt(共28页)

PCB高速信号布线

PCB高速信号布线PCB是印刷电路板(Printed Circuit Board)的英文缩写,它是现代电子产品设计中不可或缺的一部分。

PCB可以在小面积内集成大量的电子元器件,有效地节省了电路板设计的空间。

在PCB 设计中,电路连接的正确性和可靠性是至关重要的。

其中高速信号线的布线设计尤为重要,因为高速信号线往往具有很高的频率和信号速度,容易受到信号衰减、反射、干扰等各种影响。

PCB高速信号布线的目标是尽量减小信号的反射和传导干扰,并且保持信号的完整性。

这个过程需要考虑多个因素,如信号速度、布线长度、布线材料、针脚间距、信号电平等等。

一、布线长度当高速信号线的长度超过了特定的阈值时,会产生反射和信号失真的问题。

此时需要采取一些措施来保持信号完整性。

其中一种方法是添加阻抗匹配电路,使信号源和负载之间的阻抗匹配。

电阻匹配可以降低信号反射,使信号保持不变。

这种方法的缺点是占用空间、增加功耗,但在高速布线设计中是必要的。

二、地平面高速线和地面之间的几何布局也非常重要。

在同层PCB中,地平面应该保持尽可能的连续,适当的地平面将有助于减少反射和传导干扰。

在多层PCB中,每个逻辑层应该都有一个地面平面来提供良好的集总环境。

一个好的地平面应该是连续的、均匀分布,并且根据需要提供足够的连通电绳。

在高速布线设计中,地平面的设计是必须的。

三、材料在高速布线设计中,选择合适的PCB材料对于保持信号完整性非常重要。

常见的PCB材料有FR-4、Rogers等。

在高速布线设计中,一般采用介电常数低、相对介电常数稳定的材料。

介电常数低可以降低信号的传播延迟,不稳定的相对介电常数会导致信号传播速度的变化,从而影响信号完整性。

四、穿孔的位置当需要在PCB板上穿孔时,应该注意使用穿孔位置对高速信号线的影响。

在PCB板上钻孔时,会产生一些毛刺,这些毛刺有可能对信号完整性产生负面的影响,因此,需要对孔壁进行平整处理。

五、差分布线差分信号传输是现在高速布线的普遍应用。

pcb布线规则及技巧 PPT

大家好

(特殊)

大家好

(一般)

大家好

元件封装中的元件中心和 用2D线画出来的

大家好

实际问题反馈

大家好

布线完成后,需检查元件开窗层与助焊层是否按要求处理,元件开窗不可过大, 0.05MM即可,否则易导致短路; 在铺铜是需注意元件周围需设置禁止铺铜区避免短路,禁止铺铜区域比元件大大 可

大家好

大家好

5. 电源线尽可能走0.2MM,如若空间允许,可调整为0.25MM 地线之间有空间可将地线空间补大。 6. 一般情况下,电源线应先经过电容在进入芯片的引脚;模 和I2C数据线尽量不在一起,即AVDD不可从SCL、SDA中间通过 7. 电源AVDD、DVDD、DOVDD应尽量分开,DVDD和DOVDD允许相 最好能隔地;电源线均应尽量少打过孔,尽量走总分结构, 底。 8. AGND的目的是保护AVDD,布线时二者尽量平行。

大家好

模拟电源和数字电源应尽量远离,电源尽量放在

大家好

该图布线存在一个警告, 线与地线在有空间时都应 地线布线中空间不足可采

大家好

该图布线存在一个警告,电源引脚成排时,除了可以采用U型布线外,还可以以两个引脚 如右方图片所示

大家好

EMI是英文Electro Magnetic Interference 的缩写,是 电磁干扰的意思。电源是发生EMI的

覆盖膜

离型纸(生产过程中会被撕掉) 胶 PI(一种塑胶,聚酰亚胺)

(双面)基材

铜箔 AD(胶,没有胶的叫无胶基材) PI AD 铜箔

补强

FR4补强(也是一种胶) 钢片补强 PI补强

EMI屏蔽膜(防止和抑制电磁干扰)

油墨

一个FPC板基材一定有,为保护 材上铺一层覆盖膜和油墨,屏蔽 需要添加屏蔽膜和补强时要在板

《PCB布线与布局》PPT课件

l

心元器件应当优先布局。

l

l

2. 布局中应参考原理框图,根据单板的主信号流向规律安排主要元

l

器件。

l

l

3. 元器件的排列要便于调试和维修,亦即小元件周围不能放置大元件、

l

需调试的元、器件周围要有足够的空间。

l

l

4. 相同结构电路部分,尽可能采用“对称式”标准布局。

h

4

l 5. 按照均匀分布、重心平衡、版面美观的标准优化布局;

h

8

2、四种具体走线方式

、时钟的布线:

时钟线是对EMC 影响最大的因素之一。在时钟线上应少打过孔,尽量避免和其它信号线并 行走线,且应远离一般信号线,避免对信号线的干扰。同时应避开板上的电源部分,以防 止电源和时钟互相干扰。

如果板上有专门的时钟发生芯片,其下方不可走线,应在其下方铺铜,必要时还可以对其 专门割地。

h

23

• ⑩3W规则:

n 为了减少线间串扰,应保证线间距足够大,当线 中心间距不少于3倍线宽时,则可保持70%的电场 不互相干扰,称为3W规则。如要达到98%的电场不 互相干扰,可使用10W的间距。

h

24

• ⑾屏蔽保护

n 对应地线回路规则,实际上也是为了尽量减小信号的回路面积,多见于一些 比较重要的信号,如时钟信号,同步信号;对一些特别重要,频率特别高的 信号,应该考虑采用铜轴电缆屏蔽结构设计,即将所布的线上下左右用地线 隔离,而且还要考虑好如何有效的让屏蔽地与实际地平面有效结合。

l 6. 同类型插装元器件在X或Y方向上应朝一个方向放置。同一种类型的有极性

l

分立元件也要力争在X或Y方向上保持一致,便于生产和检验。

l 7. 发热元件要一般应均匀分布,以利于单板和整机的散热,除温度检测元件

pcb布线规则及技巧幻灯片

开窗与底层网铜相连,符合条件

在上部放置底层开窗的原因是因为上面要加一层钢片,开窗使露铜与钢片相连,引走多余电荷,开窗一般设置2-3个,在评估图底视图中有说明此部

分 在加下钢部片开接窗20地是20为/3/了21贴EMI屏蔽膜,防止和抑制电磁干扰,在评估图侧视图中有说明此部分加双面电磁屏蔽膜

2020/3/21

3

9. 在芯片中若出现成排电源引脚或地引脚(如AVDD和DGND)最好采用如下连接方 式(该方式可避免芯片发生偏移)

2020/3/21

4

10. 摄像头中信号线应尽量放在底层,布线时过孔应尽量打在芯片外部,所有布 线与最外层裁剪框应至少保证0.15MM距离。 11. 在摄像头中,布线结束后需将所有角转变成倒角,避免反射形成干扰;在转 接板中,若只是作为测试用,要求不高是可不必转成倒角,且在布线过程中允许 使用部分直角。 12. 布线时,板子左右两边边缘最好放置一条地线;铺铜时地线最好都能保证连 接以增加导电性。 13. 金手指布线时过孔只能打在补强以下。 14. 布线过程中,过孔的大小为硬板0.4/0.2,其余板0.35/0.15或0.3/0.1 15. MIPI接口是指串行差分接口,DVP接口是指并行传输接口

和抑制干扰,如通讯电缆的终端电阻,电脑的机箱,变压器的屏蔽罩,用顺磁材料或抗磁材料来疏导或阻止电

磁场的穿行等等。EMI是产品投放市场前电工认证的一个必检内容。 我们平时经常见到一些产品由于EMI不过

关的报告或投诉。我们常见的开关电源入口处,有一个两个绕组的电感,这个电感是共模抑制电感,也起到减

少EMI的作用。另外,一些数据线的两头,会鼓出来一个大包包(例如电脑彩显的数据线上,一些数码相机的

(一分为二)

7

当电源线或地线引脚成排时,可采用图示方法布线

高速PCB设计之技术分析之布局布线

高速PCB设计之技术分析之布局布线一般而言,设计电路板最基本的过程可以分为三大步骤。

(1). 电路原理图的设计:(2). 产生网络表(3). 印制电路板的设计电路原理图的设计中,最重要的是布局与布线。

在布局方面,要遵循元件排布的法则(1).在通常条件下,所有的元件均应布置在印制电路的同一面上,只有在顶层元件过密时,才能将一些高度有限并且发热量小的器件,如贴片电阻、贴片电容、贴IC等放在底层。

(2).在保证电气性能的前提下,元件应放置在栅格上且相互平行或垂直排列,以求整齐、美观,一般情况下不允许元件重叠;元件排列要紧凑,输入和输出元件尽量远离。

(3).某元器件或导线之间可能存在较高的电位差,应加大它们的距离,以免因放电、击穿而引起意外短路。

(4).带高电压的元件应尽量布置在调试时手不易触及的地方。

(5).位于板边缘的元件,离板边缘至少有2个板厚的距离。

(6).元件在整个板面上应分布均匀、疏密一致。

(7). 在元器件的布局方面,应该把相互有关的元件尽量放得近一些。

(8). 尽量在关键元件,如ROM、RAM等芯片旁边安装去耦电容。

布线是整个PCB设计中最重要的工序。

这将直接影响着PCB板的性能好坏。

因此布线也应遵循一定的技巧1 电源、地线的处理既使在整个PCB板中的布线完成得都很好,但由于电源、地线的考虑不周到而引起的干扰,会使产品的性能下降,有时甚至影响到产品的成功率。

所以对电、地线的布线要认真对待,把电、地线所产生的噪音干扰降到最低限度,以保证产品的质量。

对每个从事电子产品设计的工程人员来说都明白地线与电源线之间噪音所产生的原因,现只对降低式抑制噪音作以表述:(1)、众所周知的是在电源、地线之间加上去耦电容。

(2)、尽量加宽电源、地线宽度,最好是地线比电源线宽,它们的关系是:地线>电源线>信号线,通常信号线宽为:0.2~0.3mm,最经细宽度可达0.05~0.07mm,电源线为1.2~2.5 mm对数字电路的PCB可用宽的地导线组成一个回路, 即构成一个地网来使用(模拟电路的地不能这样使用)(3)、用大面积铜层作地线用,在印制板上把没被用上的地方都与地相连接作为地线用。

pcb布局布线规则 PPT

5

PCB高频电路布线

(1)、合理选择PCB层数。用中间的电源层(vcc layer)和地层(Gnd layer)可以起到屏蔽作 用,有效降低寄生电感和寄生电容,也可大大缩短布线的长度,减少信号间的交叉干扰。 (2)、走线方式。必须按照45°的拐角方式,不要用90°的拐角。如图:

• 对一些频率较高的设计,需特别考虑 其他地平面信号回路问题,建议采用 多层板

• 在地平面分割时,要考虑到地平面与 重要信号的走线分布,防止由于地平 面开槽带来的问题

PART 1

基础理论与知识

1

PCB板层(Printing Circuit Board)

silk screen (Top overlay): solder Mask (Top/Bottom): Paste Mask (Top/Bottom): Top: Bottom: Drill Guide(Drill Drawing): Keep out layer: Mechanical Layer: Multi Layer: Vcc Layer: Gnd Layer:

材料的镀通孔.

NPTH

盲孔(Buried) :用于多层PCB内层和外层之间的电气连接.

埋孔(Blind) :用于多层PCB内层和内层之间的电器连接.

VCC LAYER VCC LAYER

TOP LAYER

BOTTOM LAYER

盲孔

4

埋孔

PCB的尺寸单位

1.PCB中有两种单位:分别为英制(Imperial)和公制(Metric) 各单位的换算如下: 1米(m)=3.28英尺 1英尺=12英寸(inch)

高速PCB设计的布局布线优化方法

高速PCB设计的布局布线优化方法高速PCB设计|pcb设计|pcb layout|pcb design|SI仿真|EMC设计|PCB生产|承接PCB外包设计|PCB制板焊接加工|-中国电子工程师专业导航网站旗下-夜猫PCB工作室随着半导体工艺的发展,器件的工作频率越来越高,使得高速PCB的设计成为产品设计中的一个重要环节,而高速PCB设计所面临的过冲、下冲、振铃、延迟和单调性等信号完整性问题,将成为传统设计的一个瓶颈,设计人员仅仅凭经验将越来越难设计出完整的解决方案,因此设计人员只有借助一套完整的信号完整性分析工具才能准确预测并消除这些问题。

下面我们结合高速PCB设计分析工具SpecctraQuest来分析以上的PCB级信号完整性问题。

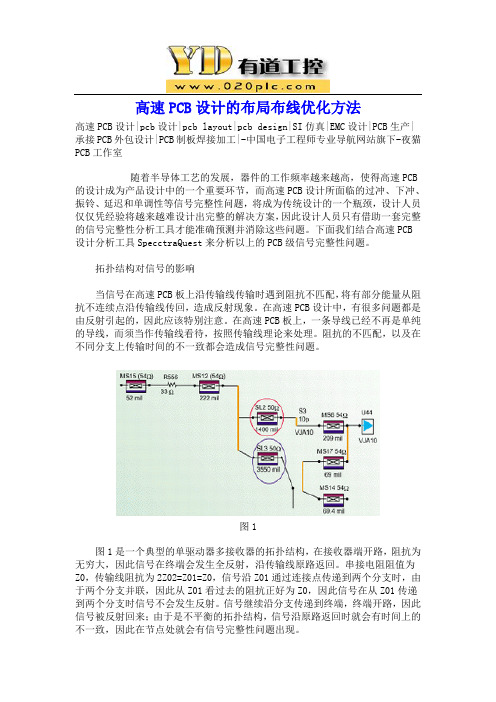

拓扑结构对信号的影响当信号在高速PCB板上沿传输线传输时遇到阻抗不匹配,将有部分能量从阻抗不连续点沿传输线传回,造成反射现象。

在高速PCB设计中,有很多问题都是由反射引起的,因此应该特别注意。

在高速PCB板上,一条导线已经不再是单纯的导线,而须当作传输线看待,按照传输线理论来处理。

阻抗的不匹配,以及在不同分支上传输时间的不一致都会造成信号完整性问题。

图1图1是一个典型的单驱动器多接收器的拓扑结构,在接收器端开路,阻抗为无穷大,因此信号在终端会发生全反射,沿传输线原路返回。

串接电阻阻值为Z0,传输线阻抗为2Z02=Z01=Z0,信号沿Z01通过连接点传递到两个分支时,由于两个分支并联,因此从Z01看过去的阻抗正好为Z0,因此信号在从Z01传递到两个分支时信号不会发生反射。

信号继续沿分支传递到终端,终端开路,因此信号被反射回来;由于是不平衡的拓扑结构,信号沿原路返回时就会有时间上的不一致,因此在节点处就会有信号完整性问题出现。

图2采用对称的拓扑结构可以解决这个问题。

结合如图2所示实际工作中的一个例子来分析,这是在一个路由器中收发器到内存的拓扑结构图,驱动器是BCM5625,接收器是存储器。

《高速PCB设计介绍》课件

布局设计技巧和注意事项

1 分区设计

根据电路功能和信号特性,将PCB划分为不同的区域。

2 信号与电源分离

避免信号和电源之间的相互干扰,以提高信号完整性。

3 走线技巧

采用合适的走线方式,如避免交叉、减小走线长度等。

差分和阻抗匹配设计

1

差分信号

解释差分信号的概念和用途,以及差分线路的布局和走线规则。

2

解释选择适当的线宽线具

介绍常用的PCB设计软件,如Altium Designer和PADS。

PCB的生产流程

原理图设计

使用EDA软件完成电路原理图的设计与验证。

布局设计

将原理图中的元件转换为PCB上的布局,并 考虑布线和散热等因素。

生成Gerber文件

将PCB设计转换为Gerber文件,供PCB制造 厂商生产。

《高速PCB设计介绍》 PPT课件

本课件将深入介绍高速PCB设计的基本概念和流程,让您了解电磁兼容性设 计、高速信号传输特性等关键问题,同时分享布局设计技巧和注意事项。

PCB设计概述

1

基础知识

了解PCB的基本结构和原理,包括通

设计要求

2

过孔、层叠等概念。

明确设计目标,包括信号完整性、干

扰抑制和散热等要求。

阻抗匹配

介绍阻抗匹配的原理和技巧,以确保信号传输的一致性和稳定性。

3

仿真和验证

使用仿真工具验证差分和阻抗匹配设计的性能,如SIwave和HyperLynx。

板厚、层压板和线宽线距选择

板厚选择

讨论选择适当的PCB板厚度对 布局和走线的影响。

层压板设计

介绍多层PCB的设计和层压板 的配置。

线宽线距选择

组装和焊接

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

• 主机板PCB的材料

•

– 环氧树脂玻璃布层压板FR4

– 工作在1GHz以下的PCB可以选用FR4,成本低、多层压制板工 艺成熟

–

• 六层PCB结构

– 板材的性能指标包括有介电常数εr、损耗因子(介质损耗角正 切)tgδ、表面光洁度、表面导体导电率、抗剥强度、热涨系数 、抗弯强度等。其中介电常数εr、损耗因子是主要参数。

铜箔 第二层地层 第三层电源 第四层信号层 第五层地层

铜箔

顶层 基材 基材 双面板

基材 基材 双面板

基材 基材 底层

1OZ /35um/1.38mil 7mil 2.5mil

0.43mm

2.5mil 2.5mil

0.43mm

2.5mil 7mil 1OZ /35um/1.38mil

• 主机板PCB的材料

3 2C P U _ C L K

3 2C P U _ C L K J

CPUC _ 1 0 C F 9L2K 1 C 0 6 0 3 3 .9 n F 5 0 V , X 7R , + /-1 0 %

CPUC _ 1 0 C F 8L2KJ1 C 0 6 0 3 3 .9 n F 5 0 V , X 7R , + /-1 0 %

– 因为会造成互扰

2.传输线及其相关的设计规则

信号线=?传输线

• 反射

–

信号线 等效电路

*

U6F1 ssop28fb

5

6

CLK0 nCLK0

7 8

CLK1

nCLK1

9 CLK_SEL

10 MR

3 SEL0

4 SEL1

1 PLL_SEL

2 11

VCC

18 VCC

19 24 25 28

VCCO VCCO VCCO VCCO

VCCA

ICS8633-01

Q2 nQ2

23 22

Q1 nQ1

21 20

17 Q0 16 nQ0

FB_IN nFB_IN

13 12

VEE

14 15

VEE 26

VEE VEE

27

IO4_CLK IO4_CLKJ

CPU_CLK CPU_CLKJ

R932 R934

49.9 +/-1% R0603 49.9

– 储能和高频滤波电容 :减小电流回路的回路 面积

•

– 模拟与数字电源-地要分开

为什么要分开,谁影响谁多? 怎样分?

2

+12V

U4A1 3 IN

1

C4A1 1uF 10V, X5R, +/-10%

பைடு நூலகம்

L78L05

2 GND

+5VA

OUT 1

1

1

2

C4A3 0.1uF

16V, X7R, +/-10%

2

C4A2 1uF 10V, X5R, +/-10%

•

3.5.1 抗干扰能力强,因为两根差分走线之间的耦合很好,当外界存在

•

杂讯干扰时,几乎是同时被耦合到两条联机,而接收端关心的只

•

是两信号的差值,所以外界的共模杂讯可以被完全抵消.

•

3.5.2 能有效抑制EMI,同样的道理,由于两根信号的极性相反,他们

*

R 5A3

0 +/-5% R 0603

• 电源VIA

•

– 一般一个VIA可以解决0.3-0.5A电流

• 时钟线两侧建议包地线

– 保证包地线各点相位相等

•

–

• 滤波电容的接地和接电源线应尽可能粗

– 等效串联电感会降低电容的谐振频率,削弱其高频滤 波效果.

– –

滤波电容的布局

• 两个层面,不同电源尽量不要重叠

+/-1% R0603 R933 49.9 +/-1% R0603

R935 120 +/-5% R0603

R936 120 +/-5% R937 R0603 120

+/-5% R0603

R938 120 +/-5% R0603

IO4_CLK

22

IO4_CLKJ 22

CPU_CLK 11 CPU_CLKJ 11

• Layout rule

Placement rule Routing rule DFM rule DFA rule DFT rule DFE rule 信号连接及机构检查.doc

• P.C.B Layout tools

1. P-CAD

2. Protel

3. PADS --- Power-PCB 4. Mentor 5. Allegro 6. Others

–

•

三 高速PCB布线的考量

• 何谓高速数字信号

• 高速数字信号由信号的边沿速度决定,一般认为上升时间小于4 倍信号传输

• 延迟时可视为高速信号。平常讲的高频信号是针对信号频率而言 的

• 信号回路的特性

辐射,串扰,EMI

• 法拉第电磁感应原理??

1.电源与地

– 电源线宽与电流的关系

一般40mil宽的铜箔对应1A的电流

主板PCB技术讨论

研发中心 戴庆涛 2007.8.10

一 PCB简介

• PCB=Printed Circuit Board印刷电路板

• 从1903年至今, 可分为三个阶段

– 通孔插装技术(THT)阶段PCB

– 表面安装技术(SMT)阶段PCB – 芯片级封装(CSP)阶段PCB

• PCB的种类

– 单面板(Single-Sided Boards) – 双面板(Double-Sided Boards) – 多层板(Multi-Layer Boards)

•

– 环氧树脂玻璃布层压板FR4

– 工作在1GHz以下的PCB可以选用FR4,成本低、多层压制板工 艺成熟

–

二 Layout & PCB Tool

Ø Layout是连接设计和 制造的纽带。实现 HW设计理念并给予 量产化。

Layout 的主要步骤

1.build library -in 3.Placement 4.Set constraint 5.Routing 6.Check 7.Gerber out

dummy

差分信号(Differential Signal)线应同层,等长,并行走线,保持阻抗一致,

•

差分线间无其它走线.

•

何为差分信号:就是驱动端发送两个等值、反相的信号,接收端通过

•

比较这两个电压的差值来判断逻辑状态“0"还是“1"。而承载差分信号的那

•

一对走线就称为差分走线。

•

差分信号的优点:

**

LPC_CLK0 LPC_CLK1

**

R3J2

R0603

PCI _CLK SI O

22 +/-5%

PCI_CLKSIO

44

R3J3

R0603 22 +/-5%

PCI _CLK LPC

PCI_CLKLPC

49

* * C3J3 10pF

C3J2 10pF

C0603 C0603

50V, NPO, +/-5% dummy 50V, NPO, +/-5%