单片机多字节BCD码加法减法

运用单片机进行加减乘除法的运算

运用单片机进行加减乘除法的运算

单片机介绍 单片机是一种集成在电路芯片,是采用超大规模集成电路技术把具有数据处理能力的中央处理器CPU随机存储器RAM、只读存储器ROM、多种I/O口和中断系统、定时器/计时器等功能(可能还包括显示

驱动电路、脉宽调制电路、模拟多路转换器、A/D转换器等电路)集成到一块硅片上构成的一个小而完善的计算机系统。

单片微型计算机简称单片机,是典型的嵌入式微控制器(Microcontroller Unit),常用英文字母的缩写MCU表示单片机,它最早是被用在工业控制领域。

单片机由芯片内仅有CPU的专用处

理器发展而来。

最早的设计理念是通过将大量外围设备和CPU集成在一个芯

片中,使计算机系统更小,更容易集成进复杂的而对体积要求严格的控制设备当中。

INTEL的Z80是最早按照这种思想设计出的处理器,从此以后,单片机和专用处理器的发展便分道扬镳。

看到这个题目,呵呵,可能好多人要打石头哥的板子;7+5等于几啊?

这还用你教?但是单片机里,数字是用二进制来表示的:这个就有一点拗口啦/ 虽然我们的教材到这里你可能还没有学会一个指令。

但是我的意思是首先作几个试验,提高大家对单片机的兴趣。

具体的指令太多了,不过还好,一般我们只需要记住常用的10-20条就够了。

OK,现在开始动手。

我们写入以下两条指令

MOV P1,#23H

END

这个程序大家想必看得懂,就是把23H这个16进制数送往P1口(即P1.0--P1.7)汇编得到HEX烧写后然后把芯片插入实验卡座;可以看到P1.0-1.7的状态为;。

BCD码加减法

BCD码加减法3、BCD码的加减运算由于编码是将每个十进制数用一组4位二进制数来表示,因此,若将这种BCD码直接交计算机去运算,由于计算机总是把数当作二进制数来运算,所以结果可能会出错。

例:用BCD码求38+49。

解决的办法是对二进制加法运算的结果采用"加6修正,这种修正称为BCD调整。

即将二进制加法运算的结果修正为BCD码加法运算的结果,两个两位BCD数相加时,对二进制加法运算结果采用修正规则进行修正。

修正规则:(1)如果任何两个对应位BCD数相加的结果向高一位无进位,若得到的结果小于或等于9,则该不需修正;若得到的结果大于9且小于16时,该位进行加6修正。

(2)如果任何两个对应位BCD数相加的结果向高一位有进位时(即结果大于或等于16),该位进行加6修正.(3)低位修正结果使高位大于9时,高位进行加6修正。

下面通过例题验证上述规则的正确性。

用BCD码求35+21 BCD码求25+37 用BCD码求38+49 用BCD码求42+95用BCD码求91+83 用BCD码求94+7 用BCD码求76+45两个组合BCD码进行减法运算时,当低位向高位有借位时,由于"借一作十六"与"借一作十"的差别,将比正确的结果多6,所以有借位时,可采用"减6修正法"来修正.两个BCD码进行加减时,先按二进制加减指令进行运算,再对结果用BCD调整指令进行调整,就可得到正确的十进制运算结果。

实际上,计算机中既有组合BCD数的调整指令,也有分离BCD数的调整指令。

另外,BCD码的加减运算,也可以在运算前由程序先变换成二进制数,然后由计算机对二进制数运算处理,运算以后再将二进制数结果由程序转换为BCD码。

4、8421BCD码、余3码、格雷码用四位二进制代码来表示一位十进制数,称为二--十进制编码,简称BCD(Binary Coded Decimal)码。

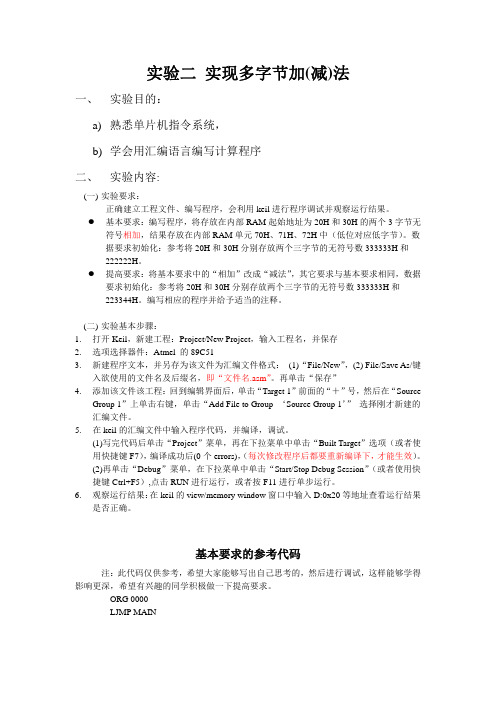

单片机实验多字节加减法

实验二实现多字节加(减)法一、 实验目的:a)熟悉单片机指令系统,b)学会用汇编语言编写计算程序二、 实验内容:(一)实验要求:正确建立工程文件、编写程序,会利用keil进行程序调试并观察运行结果。

z基本要求:编写程序,将存放在内部RAM起始地址为20H和30H的两个3字节无符号相加,结果存放在内部RAM单元70H、71H、72H中(低位对应低字节)。

数据要求初始化:参考将20H和30H分别存放两个三字节的无符号数333333H和222222H。

z提高要求:将基本要求中的“相加”改成“减法”,其它要求与基本要求相同,数据要求初始化:参考将20H和30H分别存放两个三字节的无符号数333333H和223344H。

编写相应的程序并给予适当的注释。

(二)实验基本步骤:1.打开Keil,新建工程:Project/New Project,输入工程名,并保存2.选项选择器件:Atmel 的89C513.新建程序文本,并另存为该文件为汇编文件格式: (1)“File/New”,(2) File/Save As/键入欲使用的文件名及后缀名,即“文件名.asm”。

再单击“保存”4.添加该文件该工程:回到编辑界面后,单击“Target 1”前面的“+”号,然后在“SourceGroup 1”上单击右键,单击“Add File to Group ‘Source Group 1’”选择刚才新建的汇编文件。

5.在keil的汇编文件中输入程序代码,并编译,调试。

(1)写完代码后单击“Project”菜单,再在下拉菜单中单击“Built Target”选项(或者使用快捷键F7),编译成功后(0个errors),(每次修改程序后都要重新编译下,才能生效)。

(2)再单击“Debug”菜单,在下拉菜单中单击“Start/Stop Debug Session”(或者使用快捷键Ctrl+F5),点击RUN进行运行,或者按F11进行单步运行。

单片机实验多字节加减法

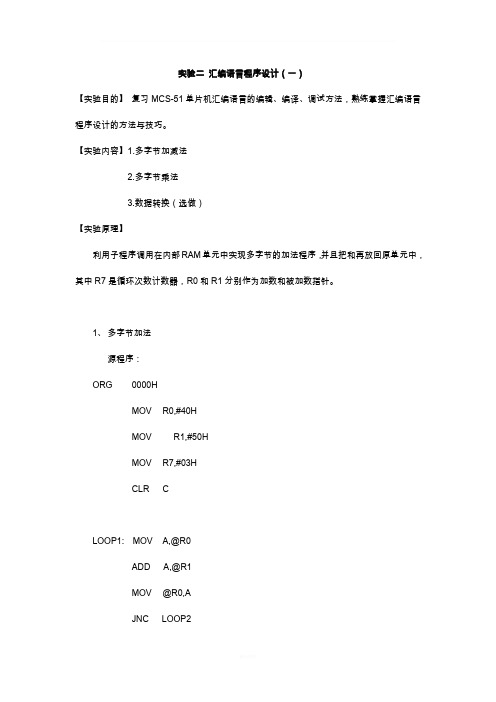

实验二汇编语言程序设计(一)【实验目的】复习MCS-51单片机汇编语言的编辑、编译、调试方法,熟练掌握汇编语言程序设计的方法与技巧。

【实验内容】1.多字节加减法2.多字节乘法3.数据转换(选做)【实验原理】利用子程序调用在内部RAM单元中实现多字节的加法程序,并且把和再放回原单元中,其中R7是循环次数计数器,R0和R1分别作为加数和被加数指针。

1、多字节加法源程序:ORG 0000HMOV R0,#40HMOV R1,#50HMOV R7,#03HCLR CLOOP1: MOV A,@R0ADD A,@R1MOV @R0,AJNC LOOP2LOOP2: INC R0INC R1MOV A,R0DJNZ R7,LOOP1SJMP $END实验结果如下图:2、多字节乘法源程序:ORG 0000HQMUL: MOV A,R3MOV B,R7MUL ABXCH A,R7MOV R5,B MOV B,R2 MUL AB ADD A,R5 MOV R4,A CLR A ADDC A,B MOV R5,A MOV A,R6 MOV B,R3 MUL AB ADD A,R4 XCH A,R6 XCH A,B ADDC A,R5 MOV R5,A MOV F0,C MOV A,R2 MUL AB ADD A,R5 MOV R5,A CLR AMOV ACC.0,CMOV C,F0ADDC A,BMOV R4,AEND实验结果如下图:Welcome To Download !!!欢迎您的下载,资料仅供参考!。

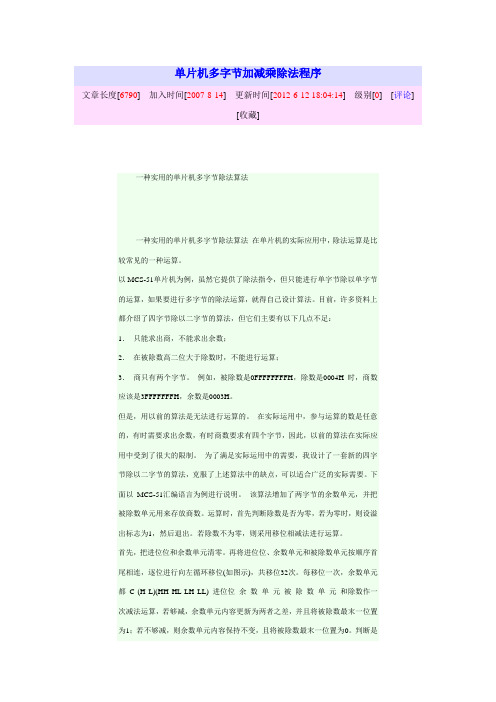

单片机多字节加减乘除法程序

单片机多字节加减乘除法程序文章长度[6790]加入时间[2007-8-14]更新时间[2012-6-12 18:04:14]级别[0][评论][收藏]一种实用的单片机多字节除法算法一种实用的单片机多字节除法算法在单片机的实际应用中,除法运算是比较常见的一种运算。

以MCS-51单片机为例,虽然它提供了除法指令,但只能进行单字节除以单字节的运算,如果要进行多字节的除法运算,就得自己设计算法。

目前,许多资料上都介绍了四字节除以二字节的算法,但它们主要有以下几点不足:1.只能求出商,不能求出余数;2.在被除数高二位大于除数时,不能进行运算;3.商只有两个字节。

例如,被除数是0FFFFFFFFH,除数是0004H时,商数应该是3FFFFFFFH,余数是0003H。

但是,用以前的算法是无法进行运算的。

在实际运用中,参与运算的数是任意的,有时需要求出余数,有时商数要求有四个字节,因此,以前的算法在实际应用中受到了很大的限制。

为了满足实际运用中的需要,我设计了一套新的四字节除以二字节的算法,克服了上述算法中的缺点,可以适合广泛的实际需要。

下面以MCS-51汇编语言为例进行说明。

该算法增加了两字节的余数单元,并把被除数单元用来存放商数。

运算时,首先判断除数是否为零,若为零时,则设溢出标志为1,然后退出。

若除数不为零,则采用移位相减法进行运算。

首先,把进位位和余数单元清零。

再将进位位、余数单元和被除数单元按顺序首尾相连,逐位进行向左循环移位(如图示),共移位32次。

每移位一次,余数单元都 C (H L)(HH HL LH LL) 进位位余数单元被除数单元和除数作一次减法运算,若够减,余数单元内容更新为两者之差,并且将被除数最末一位置为1;若不够减,则余数单元内容保持不变,且将被除数最末一位置为0。

判断是否够减的方法是:在作减法之前,先保存进位位,再看作完减法后的进位位。

仅在作减法之前进位位为0,并且作减法之后进位位为1时判为不够减,其余情况均视为够减。

单片机多字节乘除法

二,用减法做除法: 用减法做除法:

例2 如何用减法做除法计算十六进制89/2=44,余1。 如何用减法做除法计算十六进制89/2=44,余1 用一个空RAM0,RAM0位与除数最多用位数相同, 用一个空RAM0,RAM0位与除数最多用位数相同, 如除数2最多用4位,如除数是88最多用8 如除数2最多用4位,如除数是88最多用8位。 有下式: RAM1=1000 1001,RAM0=0000。和为一体为 1001,RAM0=0000。和为一体为 RAM= RAM=1000 1001 0000, RAM0最后保存的数为余数, RAM0最后保存的数为余数, 8位除以8位,多字节以此类推。 位除以8

直观如下:89( 直观如下:89(1000 1001)/2。结果为44,余1。 1001)/2。结果为44,余 RAM1 RAM0,RAM0为保存余数用。 RAM0,RAM0为保存余数用。 1000 1001 0000 1,0001 0010 0001 2,0010 0100 0010 0010 0101 0000 RAM0>=2,RAM0-2,RAM1+1。 RAM0>=2,RAM0RAM1+1。 3,0100 1010 0000 4,1001 0100 0000 5,0010 1000 0001 6,0101 0000 0010 0101 0001 0000 RAM0>=2,RAM0-2,RAM1+1。 RAM0>=2,RAM0RAM1+1。 7,1010 0010 0000 8,0100 0100 0001

步骤如下:

1,左移一位到C,结果 C=1,RAM= 0110 0000 1,左移一位到C 1,RAM= 2,C=1,则RAM0+2,RAM=0110 0010 2,C=1,则RAM0+2,RAM= 3,左移一位到C,结果 C=0,RAM=1100 0100 3,左移一位到C 0,RAM= 4,C=0,则RAM不加。 4,C=0,则RAM不加。 5,左移一位到C,结果 C=1,RAM= 1000 1000 5,左移一位到C 1,RAM= 6,C=1,则RAM0+2,RAM=1000 1010 6,C=1,则RAM0+2,RAM= 7,左移一位到C,结果 C=1,RAM= 0001 0100 7,左移一位到C 1,RAM= 8,C=1,则RAM0+2,RAM=0001 0110 8,C=1,则RAM0+2,RAM=

单片机bcd码的用法

单片机bcd码的用法

BCD码(Binary Coded Decimal)是一种将十进制数表示为二进制形式的编码方式。

它采用4位二进制数来表示一个十进制数的各个数字,每一位二进制数的取值范围为0-9。

单片机中可以使用BCD码进行数字的存储和显示。

下面是BCD码在单片机中的常见用法:

1. 存储:可以使用BCD码将数字存储到寄存器或内存中。

对于一个十进制数字,可以将其各个位的BCD码存储在相应的内存位置上,每个位置占用4位二进制数。

这样可以方便地访问和操作每个数字位。

2. 显示:将BCD码转换为对应的数字位,可以实现数字的显示。

单片机可以通过将BCD码送到数码管、LCD屏幕或其他显示设备上,来实现数字的显示。

3. 运算:单片机可以对BCD码进行加、减、乘、除等算术运算。

通过BCD码的相加或相减,可以实现两个数字的加法或减法。

通过BCD码的移位和逻辑运算,可以实现乘法或除法。

4. 输入输出:可以通过外部输入设备(如键盘)将BCD码输入到单片机中,也可以通过外部输出设备(如LED灯)将BCD码输出显示出来。

需要注意的是,BCD码虽然便于存储和显示数字,但占用的存储空间相对较大,且运算速度较慢。

在实际应用中,根据需求可以选择其他编码方式来表示数字,例如二进制、十六进制等。

微机原理与接口技术:加法减法运算指令

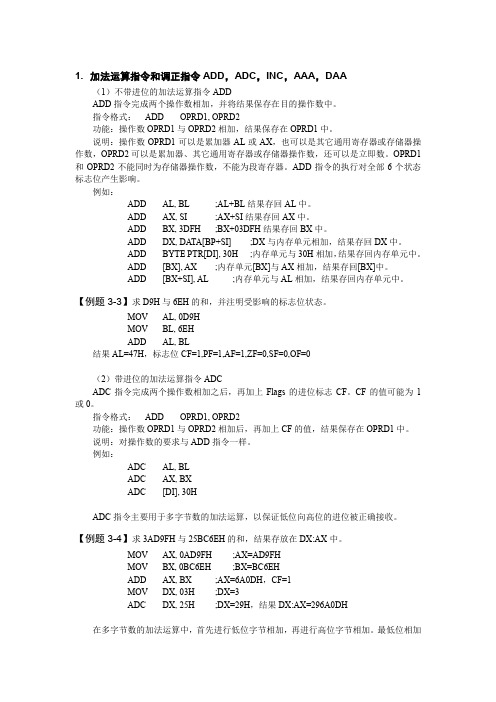

1. 加法运算指令和调正指令ADD,ADC,INC,AAA,DAA(1)不带进位的加法运算指令ADDADD指令完成两个操作数相加,并将结果保存在目的操作数中。

指令格式:ADD OPRD1, OPRD2功能:操作数OPRD1与OPRD2相加,结果保存在OPRD1中。

说明:操作数OPRD1可以是累加器AL或AX,也可以是其它通用寄存器或存储器操作数,OPRD2可以是累加器、其它通用寄存器或存储器操作数,还可以是立即数。

OPRD1和OPRD2不能同时为存储器操作数,不能为段寄存器。

ADD指令的执行对全部6个状态标志位产生影响。

例如:ADD AL, BL ;AL+BL结果存回AL中。

ADD AX, SI ;AX+SI结果存回AX中。

ADD BX, 3DFH ;BX+03DFH结果存回BX中。

ADD DX, DA TA[BP+SI] ;DX与内存单元相加,结果存回DX中。

ADD BYTE PTR[DI], 30H ;内存单元与30H相加,结果存回内存单元中。

ADD [BX], AX ;内存单元[BX]与AX相加,结果存回[BX]中。

ADD [BX+SI], AL ;内存单元与AL相加,结果存回内存单元中。

【例题3-3】求D9H与6EH的和,并注明受影响的标志位状态。

MOV AL, 0D9HMOV BL, 6EHADD AL, BL结果AL=47H,标志位CF=1,PF=1,AF=1,ZF=0,SF=0,OF=0(2)带进位的加法运算指令ADCADC指令完成两个操作数相加之后,再加上Flags的进位标志CF。

CF的值可能为1或0。

指令格式:ADD OPRD1, OPRD2功能:操作数OPRD1与OPRD2相加后,再加上CF的值,结果保存在OPRD1中。

说明:对操作数的要求与ADD指令一样。

例如:ADC AL, BLADC AX, BXADC [DI], 30HADC指令主要用于多字节数的加法运算,以保证低位向高位的进位被正确接收。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

R2,BCD1 ;处理完所有字节RET(2) 标号: BCDB 功能:多字节BCD码减法入口条件:字节数在R7中, 被减数在[R0]中

,减数在[R1]中。出口信息:差在[R0]中,最高位借位在 CY中。影响资源:PSW、A、R2、R3 堆栈需求: 6R1]十进制取补LCALL BCDA ;按多字节 BCD码加法处理CPL C ;将补码加法的进位标志转换

数据指针DJNZ R2,NEG0 ;处理完(R2)字节MOV A,#9AH ; 最低字节单独取补SUBB A,@R0MOV @R0,A

MOV A,R3 ;恢复指针MOV R0,ARET

谢谢观赏!

软件下载 /

取补入口条件:字节数在R7中,操作数在[R0]中。出口信 息:结果仍在[R0]中。影响资源:PSW、A、R2、R3 堆栈 需求: 2字节

NEG: MOV A,R7 ;取(字节数减一)至R2中DEC AMOV R2,AMOV A,R0 ;保护指针MOV R3,ANEG0

: CLR C MOV A,#99HSUBB A,@R0 ;按字节十进制取补MOV @R0,A ;存回[R0]中INC R0 ;调整

成借位标志MOV F0,C ;保护借位标志LCALL NEG1 ;恢复 减数[R1]的原始值MOV C,F0 ;恢复借位标志RETNE

G1: MOV A,R0 ;[R1]十进制取补子程序入口XCH A,R1 ;交 换指针XCH A,R0LCALL NEG ;通过[R0

]实现[R1]取补MOV A,R0XCH A,R1 ;换回指针XCH A,R0RET (3) 标号: NEG 功能:多字节BCD码

单片机多字节BCD码加法减法2006年04月17日 21:050

[导读]

(1) 标号: BC

DA 功能:多字节BCD码加法入口条件:字节数关键

词:加法减法单片机多

(1) 标号: BCDA

功能:多字节BCD码加法入口条件:字节数在R7中, 被加数在[R0]中,加数在[R1]中。出口信息:和在[R0]中, 最高位进位在CY中

。影响资源:PSW、A、R2 堆栈需求: 2字节BCDA: MOV A,R7 ;取字节数至R2中MOV R2,AADD A,R0 ;

初始化数据指针MOV R0,AMOV A,R2ADD A,R1MOV R1,ACLR CBCD1: DEC R0 ;调整数据指针D

EC R1MOV A,@R0ADDC A,@R1 ;按字节相加DA A ;十进 制调整MOV @R0,A ;和存回[R0]中DJNZ