基于FPGA和DSP的图像处理技术研究

基于FPGA+DSP的实时图像处理系统设计与实现

万方数据万方数据·110·微处理机2010年(DPRAM)。

虽然C6416片内集成了高达8M位的片内高速缓存,但考虑到图像处理算法必涉及到对前后几帧图像进行处理,为保证系统运行时存储容量不会成为整个系统的性能瓶颈(chokepoint),在DSP模块中额外扩展存储空间。

由于EMIFA口的数据宽度更大,因此系统在EMIFA的CEl空间内扩展了两片总共128M位的同步存储器。

C6416的引导方式有三种,分别是:不加载,CPU直接开始执行地址0处的存储器中的指令;ROM加载,位于EMIFBCEl空间的ROM中的程序首选通过EDMA被搬人地址O处,ROM加载只支持8位的ROM加载;主机加载,外部主机通过主机接口初始化CPU的存储空间,包括片内配置寄存器。

本系统采用的是ROM加载方式。

C6416片内有三个多通道缓冲串口,经DSP处理的最终结果将通过DSP的多通道缓冲串口传送至FPGA。

3.4图像输出模块该模块的功能是将DSP处理后的图像数据进行数模转换,并与字符信号合成后形成VGA格式的视频信号。

这里选用的数模转换芯片为ADV7125。

这是ADI公司生产的一款三通道(每通道8位)视频数模转换器,其最大数据吞吐率330MSPS,输出信图2原始图像图3FPGA图像增强结果5结论实时图像处理系统以DSP和FPGA为基本结构,并在此结构的基础上进行了优化,增加了视频输入通路。

同时所有的数据交换都通过了FPGA,后期的调试过程证明这样做使得调试非常方便,既可以监视数据的交换又方便修正前期设计的错误。

整个系统结构简单,各个模块功能清晰明了。

经后期大量的系统仿真验证:系统稳定性高,处理速度快,能满足设计要求。

号兼容RS一343A/RS一170。

由FPGA产生的数字视频信号分别进入到ADV7125的三个数据通道,经数模转换后输出模拟视频信号并与原来的同步信号、消隐信号叠加后便可以在显示器上显示处理的结果了。

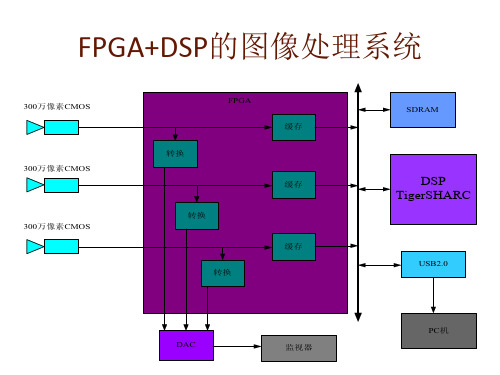

FPGA+DSP的图像处理系统

DSP的发展和趋势

– ADI的DSP具有出色的浮点处理能力,多用于雷

达/声纳等信号处理;独特的多DSP互联能力被

称为“多DSP系统的实现标准”

– TI公司的DSP则更注重单片的处理能力,在民用

高端DSP市场占有很大份额

DAC器件技术发展趋势

①高速、高精度、低功耗;

②多功能集成,如增加滤波器;

③接口电平采用高速协议:LVDS、DDR等技术。

RAM、FIFO技术

• 同步技术、双沿和多沿传输技术应用广泛

• 静态存储器:

– SBSRAM、ZBTSRAM等同步SRAM,时钟频率可 以高达200 MHz以上。 – QDR SRAM,在一个时钟周期内传输4个数据

TigerSHARC DMA Controller

I/O Processor INTERNAL BUS

128-bit DATA 32-bit ADDR

Bus Interface Unit IFIFO OBUF OFIFO DMA Controller

Data Address

Control

DMAR

SOC Bus Interface

USB特点:

• 连接灵活

等;

②缓冲和存储电路,RAM、FIFO等;

③逻辑控制和协处理器,CPLD和FPGA; ④通信接口电路,高速串行通信(光纤/LVDS)

模拟信号数字信号的转换电路

• ADC – Analog Digital Convertor

• DAC – Digital Analog Convertor

ADC器件

ADC器件发展趋势

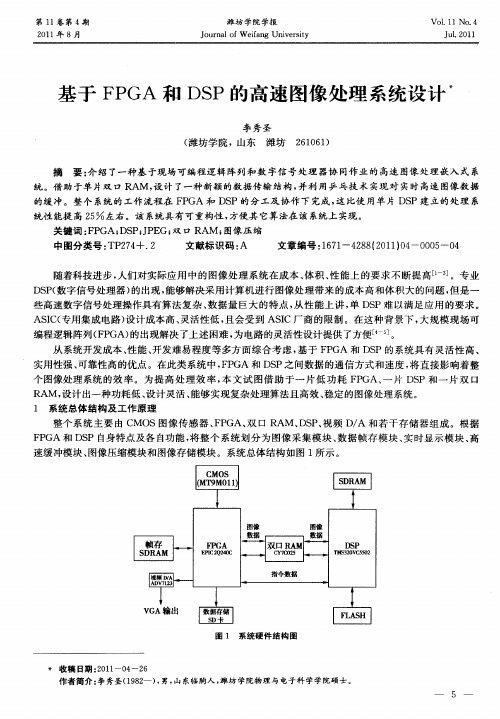

基于FPGA和DSP的高速图像处理系统设计

的缓 冲 。整 个 系统的 工作 流 程 在 F GA 和 D P的分 工 及协 作 下 完成 , 比使 用单 片 DS P S 这 P建 立 的处 理 系

统性 能提 高 2 左右 。该 系统 具 有可重 构性 , 5 方便 其 它算 法在该 系统上 实现 。

关键 词 : P F GA; S J E 双 口 RAM ; D P;P G; 图像 压 缩

第 1 卷 第 4期 1

21 0 1年 8月

潍 坊 学 院 学报

J u n l fW efn ie st o r a ia g Unv r i o y

V0 . 1N0 4 11 .

J 12 1 u. 0 1

基 于 F GA 和 DS P P的 高 速 图 像 处 理 系 统设 计

确 的配置之后 , 就可 以输 出 1 的图像数据 和一些 同步信 号 。在本系统 中采用 I O位 z C实现 传感 器配 置 ,P F— G 管脚通 过模拟 IC时序 , A 。 完成 对 C MOS 感器 的初始 化配置 , 中要 配置 的寄存 器如表 1 传 其 所示 。

表 1 MT M0 9 1寄存 器 设 置

编程逻 辑 阵列 ( P F GA) 出现解 决 了上 述 困难 , 电路 的灵活 性设 计提 供 了方便 [ 。 的 为 4 ]

从 系 统开发 成本 、 能 、 性 开发难 易程 度等 多方 面综 合考 虑 , 基于 F G 和 D P的系 统具 有 灵 活性 高 、 P A S 实用性 强 、 可靠性 高 的优 点 。在此类 系 统 中 ,P F GA和 DS P之 间 数据 的通 信 方式 和速 度 , 直 接影 响着 整 将 个 图像 处理 系统 的效 率 。为 提 高 处 理 效 率 , 文 试 图 借 助 于 一 片 低 功耗 F GA、 片 D P和 一 片 双 口 本 P 一 S

基于DSP和FPGA的实时图像压缩系统设计

f t nl Na i a Ke L b r tr F r l cr n c Me s r me t e h oo y. y a o ao y f n t me tt n ce c & D n mi o y a o ao y o E e t i o a u e n T c n l g Ke L b r tr o I s u na i S in e r o ya c

片 S M 乒乓结构 , 及基 于 T RA 以 I公 司 D P B O S / I S和 支持 X I DA S 帧/ 实 0 s

的 压 缩 速 度 , 统 同时 解 决 了图像 压 缩 中容 量 和 速 度 的 问题 , 验 了采 集 和 压 缩 过 程 的 同 步进 行 . 系 实 大 大 提 高 了 图 像 压 缩 速 度 关 键 词 :D 4 乒 乓 缓 存 ; AI M6 2; XD S

山西 太 原 005 1 30 1

摘 要 : 提 出 了 一 种 基 于 高 频 帧 摄 像 头 的 高 频 帧 实 时 图 像 压 缩 技 术 , 以 此 技 术 为 基 础 . 使 用 T 30 D 4 MS 2 C M6 2和 E 2 3 F G 相 结 合 , 计 了 一 种 高 频 帧 实 时 图 像 处 理 器 硬 件 系统 。该 系统 采 用 2 PC5 P A 设

c mp e so l o i m b u p a o o rs i n a g r h t e s p o fr XDAI S, i r a ie h o r s i n r t o 0 p r s c n .T e s se o ma e o r s in t e l s t e c mp e so a e f 1 0 e e o d z h y t m f i g c mp e so w i a d e sn t e a a i a d h s e d f h e p rme t l r c s o c l c i g n c mp e so smu t n o sy g e t hl e d r s i g h c p c t y n t e p e o t e x e i n a p o e s f o l t a d o r s in i l e u l , r al e n a y i r v s t e s e d o ma e c mp e so . mp o e h p e f i g o r si n

基于DSP+FPGA的图像处理嵌入式开发平台

了集 中处 理造 成 的时 间 延迟 , 降低 了错 误 信 息 汇 报

的风 险 。

方面仪 器在质 量 、 功 耗 及 可 靠 性 方 面 有 诸 多 限

2 硬件架构

由D S P处 理 器 及 其 外 围 器件 组 成 的 高速 运 算 电路共 同实 现硬 件运 行 平 台 , 为软 件 编 程 实 现各 类

清空外部

F

.

一

一

一

一

一

一

一

一

一

一

一

一

一

一

一

一

一

一

F P GA 写 次 级

图 惶 至

密集 图像

一

一 I

2 0 1 3年 4月 1 8日收到 国家 8 6 3计划项 目( 2 0 0 6 A A 7 0 4 2 0 5 ) 资助

硬 件结 构如 图 1右 图所 示 。

其中 , (  ̄ ) P R O M和 F L A S H 负 责 固化 D S P的程 序 , 其 中P R O M 中存 储 是 代 码 量 小 但 可 靠 性 要 求 高 的安

态, 一种 是 目标 数 量 多 ( K级) , 但 个 体 像 素 少 的 工 况 (<1 0 0 p i x以 内) , 另一 种 工 况是 目标 数 目少 , 但

个 体 像 素很 多 ( 3 2 k p i x ) 。 嵌入 式 图像处 理 器 的一 种 方案 是 F P G A 内集 成 或外挂 S R A M( 如 图 1左 图所 示 ) , 将 图像 进 行 全 幅

功能需求 、 器件组成 、 操作 时序和数据流 向, 进行 了深入分析。实践结果表 明, 该 嵌入 式开发平 台具有很强的实用性。 关键 词 图像识别

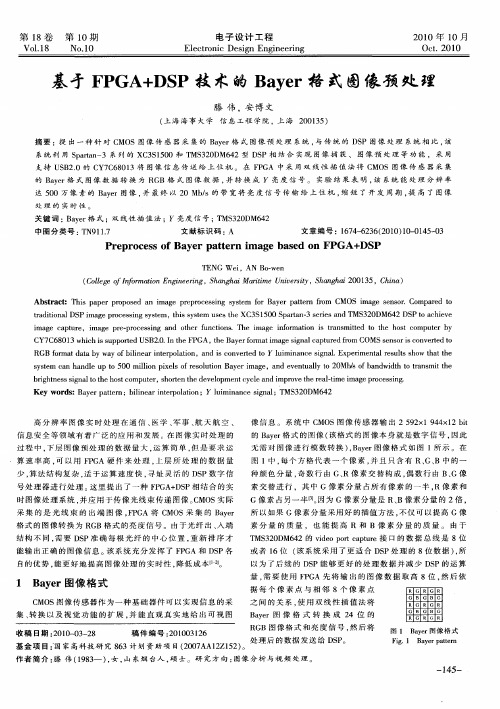

基于FPGA+DSP技术的Bayer格式图像预处理

处理 的 实时性 。

关 键 词 :B y r格 式 :双 线 性 插 值 法 ;l 度 信 号 ; ae ,亮 TM¥ 2 DM6 2 30 4

中图 分 类号 : N 1 . T 91 7

文 献标 识 码 : A

文 章编 号 :1 7 — 2 6 2 1 ) 0 0 4 — 3 6 4 6 3 (0 0 1— 15 0

CY7C6 3wh c ss po td US . I h 801 i hi up re B20. nt eFPGA ,t eBa r o m a a esg a a t r dfo COM Ss n ori o e e o h ye r ti g i n lc p u e r m f m e s sc nv r d t t

RGB f r t aa b a f i n a n e p l t n,a d i c n et d t u mi a c in 1 Ex e me tl e ut h w t a h o ma t y w y o l e r t r o ai d b i i o n s o v r o Y l i n n e sg a. p r n a s l s o h t e e i r s t s se c n h n l p t 0 l o ie so e o u in Ba e g ,a d e e t al o 2 Mbso a d d h t r n mi t e y t m a a d e u o5 0 mi in p x l fr s l t y ri l o ma e n v nu l t 0 / fb n wit o t s t h y a

基于FPGA和DSP架构的红外图像实时处理系统设计

Ke y wor : FPG A; ds DS P; ma e p o e ห้องสมุดไป่ตู้n ;i f a e i g r c s ig n r r d

处理 的各 个领 域 ,相 关 的 图像处 理 算法 复杂 灵

活 、数 据 处 理 量大 。因 此 ,图像 处 理 硬 件 系 统 要

求具 有运 行复 杂灵 活算 法 的能 力 ,以保 证 实现

系统 的 实时性 。半导 体 制造 工 艺 的快速 发 展 以

收 稿 日期 :2 1— 82 02 0 3

0 引 言

图 像 处 理 技 术 已 经 被 广 泛 应 用 于 视 频 图 像

及 计算 机体 系结构 的进一 步 改进 ,使得 数 字信 号 处理器 (i tl i a P oe osD P ) Dg a S n l rcs r, S s 芯片 的 i g s

功能变得越来越 强大;同时, 其数 字器件特有 的 稳定性、可重复性 以及可 大规模集成 的特点 , 也 使得信号 处理 的手 段变得更 加灵 活 [ 。 自从 2 0 世纪 8 0年代 初 D P 投入市 场 以来 ,实时 D P Ss S

数据采 集、数据处理和 数据传输 的并行化 。实验结果表 明,该方 案设计合理 、可行 ,具

有 较高 的工程 实用价值 。

关 键 词 :F GA ; D P; 图像 处 理 ;红 外 P S 中 图分 类 号 : T 1 . 文 献 标 识 码 : A DOI 1. 6/.s.6288 . 1.1. 6 N917 3 : 03 9jsn17—752 2 00 9 i 0 0 0

基于FPGA+DSP的实时图像处理系统设计与实现

No 2 . Ap ., 0 0 r 21

微

处

理

机

MI R0PR C OCES ORS S

第 2期 21 0 0年 4月

基 于 FG P A+D P的实 时 图像 处 理 系统设 计 与实现 S

罗戈亮, 鲁新平 , 李吉成

( 防科 学技术 大学 电子 科学 与工程学院 A R国 防科技 重点实 验室 , 沙 4 0 7 ) 国 T 长 10 3 摘 要 : 对 图像 处理 系统计 算量 大 、 时性高和体 积小 的要 求 , 制 了一种 以 D P为 主处理 针 实 研 S

器 FG P A为辅处理 器 的高性 能实 时图像处理 系 统。利 用这 两种 芯 片 的各 自特 点, 算法分 成 两部 将 分分别 交 由 F G P A和 D P处理 , 大提 高 了算法 的效 率。 系统具 有结构 简 单 易于实 现和运 用方便 S 大

灵活 的特 点 , 载上相 应 的程 序之后 能实现对 所获 取 的图像 跟踪 、 别和 匹配等处理 方法。详 细说 加 识

明了系统 的设计 思路 和硬 件结构 , 并在硬 件 系统上进行 了算法仿真及 实验验 证 。实验 结果表 明: 该

系统实 时性高 , 应性好 , 适 能够 满足设 计要求。 关键词 : 时系统 ; 实 图像处 理 ; H L硬件 语言 ; V D 现场 可编程 门阵列

D I O 编码 :0 3 6 / . s .0 2— 2 9 2 1 .2 0 2 1 .9 9 ji n 10 2 7 .0 0 0 .3 s

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.2 基于 FPGA 和 DSP 的数字图像处理技术的研究现状 ........................................... 4

1.2.1 常用图像处理芯片介绍 ..................................................................................................... 4 1.2.2 FPGA 和 DSP 的发展现状 ................................................................................................ 5 1.2.3 FPGA 和 DSP 在数字图像处理技术的应用现状 ............................................................. 5

1.1.1 数字图像处理技术介绍 ..................................................................................................... 1 1.1.2 图像处理系统介绍 ............................................................................................................. 3

西安电子科技大学 关于论文使用授权的说明

本人完全了解西安电子科技大学有关保留和使用学位论文的规定,即:研究 生在校攻读学位期间论文工作的知识产权单位属西安电子科技大学。 本人保证毕 业离校后,发表论文或使用论文工作成果时署名单位仍然为西安电子科技大学。 学校有权保留送交论文的复印件,允许查阅和借阅论文;学校可以公布论文的全 部或部分内容,可以允许采用影印、缩印或其他复制手段保存论文。 (保密的论 文在解密后遵守此规定) 本人授权西安电子科技大学图书馆保存学位论文, 并同意将论文在互联网上 发布。 本人签名: 日期 导师签名: 日期

目录

V

目录

摘要 .................................................................................................................................... I ABSTRACT ..................................................................................................................... III 目录 ................................................................................................................................... V 第一章 绪论 ..................................................................................................................... 1 1.1 数字图像处理技术和图像处理系统介绍 ................................................................. 1

摘要

I

摘要

图像作为人类信息的主要来源之一,图像处理技术对人们的重要性不言而喻。 目前,图像处理技术已经广泛应用于军事、工业和人们日常生活的各个方面。图 像处理平台主要有高性能的大型图像处理工作统具有小巧、便携、灵活的特点,广泛应用于实时图像处理的场 合,其图像处理核心主要有专用的 ASIC 芯片、FPGA 和 DSP。ASIC 芯片速度高、 稳定,但是灵活性太差,只适合于特殊目的的应用。因此,研究基于 FPGA 和 DSP 的图像处理技术具有重要的意义。 本文以 FPGA 和 DSP 为平台,根据其各自自身特点和优势,结合数字图像处 理现有技术和知识,研究图像处理技术的实现方法, 主要工作有: (1) 介绍了 IUT656 数据格式和 VGA 工业标准时序, 利用 FPGA 的并行流水 线特性,构建了基于 FPGA 的 IUT656 格式视频采集和 VGA 显示系统。 (2)设计了一种用于视频目标检测的 K 近邻分类器和 Avalon 总线接口,可 挂载于 Avalon 总线上,作为整个 SOPC 系统的一部分。 (3)确定了基于 TS201 的并行 SAR 图像去噪系统的框架结构,根据通信协 议, 设计了数据接收与发送方法, 移植优化了基于图像块的统计相似性度量的 SAR 图像降班算法。 本文工作得到了国家自然科学基金(No.60971128) ;华为创新研究计划项目 (No.IRP-2011-03-04)资助。 关键词:图像处理 FPGA DSP

作 者 姓 名 学 科 门 类

提交论文日期

周宇 工学

指导教师姓名、 职务

侯 彪 教授 电路与系统

学科、专业

二○一三年一月

西安电子科技大学 学位论文独创性(或创新性)声明

秉承学校严谨的学风和优良的科学道德, 本人声明所呈交的论文是我个人在 导师指导下进行的研究工作及取得的研究成果。尽我所知,除了文中特别加以标 注和致谢中所罗列的内容以外, 论文中不包含其他人已经发表或撰写过的研究成 果; 也不包含为获得西安电子科技大学或其它教育机构的学位或证书而使用过的 材料。 与我一同工作的同志对本研究所做的任何贡献均已在论文中做了明确的说 明并表示了谢意。 申请学位论文与资料若有不实之处,本人承担一切的法律责任。 本人签名: 日期

1.3 本文研究内容与章节安排 ......................................................................................... 6 第二章 基于 FPGA 的图像采集与 VGA 显示 .............................................................. 9 2.1 视频解码芯片 TVP5150 介绍 ................................................................................... 9

ABSTRACT

III

ABSTRACT

As one of the main source of the information of human, image processing technology played an import role in people's life. Currently, the image processing technology has been widely used in military, industrial, and people's daily life. The main platform of image processing are large-scale image processing workstation, general-purpose computers and embedded system. Embedded image processing system is compact, portable, flexible, and widely used in the occasion of the real-time image processing. The core of embedded image processing system mainly contain ASIC, FPGA and DSP. ASIC was high-speed and stable but poor flexibility, only suitable for the application of the special purpose. So, studying the image processing technology based on FPGA and DSP is very important. The works in this paper are focus on the realization of image processing technology based on FPGA and DSP , according to their own characteristics and existing knowledge. The principal tasks are as follow: (1) A IUT656 format video capture and VGA display system was designed. This system take advantage of the parallel and pipelined characteristic of FPGA. (2) A K-nearest neighbor classifier used for video object detection based on FPGA and its Avalon bus interface were designed .It can be mounted on the Avalon bus and as one part of the entire SOPC system. (3) The structure of parallel SAR image denoising system based on TS201 was determined. Data reception and transmission method according to the communication protocol was designed. SAR image denoising algorithm based on the similarity measure of statistics of the image block was transplanted and optimized on this system. This work was supported by the National Natural Science Foundation of China(No.60971128);Huwei innovation research project(No.IRP-2011-03-04). Keywords: Image processing FPGA DSP