Parallel Image Processing on Configurable Computing Architecture

图像处理中值滤波器中英文对照外文翻译文献

中英文资料对照外文翻译一、英文原文A NEW CONTENT BASED MEDIAN FILTERABSTRACTIn this paper the hardware implementation of a contentbased median filter suitabl e for real-time impulse noise suppression is presented. The function of the proposed ci rcuitry is adaptive; it detects the existence of impulse noise in an image neighborhood and applies the median filter operator only when necessary. In this way, the blurring o f the imagein process is avoided and the integrity of edge and detail information is pre served. The proposed digital hardware structure is capable of processing gray-scale im ages of 8-bit resolution and is fully pipelined, whereas parallel processing is used to m inimize computational time. The architecturepresented was implemented in FPGA an d it can be used in industrial imaging applications, where fast processing is of the utm ost importance. The typical system clock frequency is 55 MHz.1. INTRODUCTIONTwo applications of great importance in the area of image processing are noise filtering and image enhancement [1].These tasks are an essential part of any image pro cessor,whether the final image is utilized for visual interpretation or for automatic an alysis. The aim of noise filtering is to eliminate noise and its effects on the original im age, while corrupting the image as little as possible. To this end, nonlinear techniques (like the median and, in general, order statistics filters) have been found to provide mo re satisfactory results in comparison to linear methods. Impulse noise exists in many p ractical applications and can be generated by various sources, including a number of man made phenomena, such as unprotected switches, industrial machines and car ign ition systems. Images are often corrupted by impulse noise due to a noisy sensor or ch annel transmission errors. The most common method used for impulse noise suppressi on n forgray-scale and color images is the median filter (MF) [2].The basic drawback o f the application of the MF is the blurringof the image in process. In the general case,t he filter is applied uniformly across an image, modifying pixels that arenot contamina ted by noise. In this way, the effective elimination of impulse noise is often at the exp ense of an overalldegradation of the image and blurred or distorted features[3].In this paper an intelligent hardware structure of a content based median filter (CBMF) suita ble for impulse noise suppression is presented. The function of the proposed circuit is to detect the existence of noise in the image window and apply the corresponding MFonly when necessary. The noise detection procedure is based on the content of the im age and computes the differences between the central pixel and thesurrounding pixels of a neighborhood. The main advantage of this adaptive approach is that image blurrin g is avoided and the integrity of edge and detail information are preserved[4,5]. The pro posed digital hardware structure is capable of processing gray-scale images of 8-bitres olution and performs both positive and negative impulse noise removal. The architectt ure chosen is based on a sequence of four basic functional pipelined stages, and parall el processing is used within each stage. A moving window of a 3×3 and 5×5-pixel im age neighborhood can be selected. However, the system can be easily expanded to acc ommodate windows of larger sizes. The proposed structure was implemented using fi eld programmable gate arrays (FPGA). The digital circuit was designed, compiled and successfully simulated using the MAX+PLUS II Programmable Logic Development S ystem by Altera Corporation. The EPF10K200SFC484-1 FPGA device of the FLEX1 0KE device family was utilized for the realization of the system. The typical clock fre quency is 55 MHz and the system can be used for real-time imaging applications whe re fast processing is required [6]. As an example,the time required to perform filtering of a gray-scale image of 260×244 pixels is approximately 10.6 msec.2. ADAPTIVE FILTERING PROCEDUREThe output of a median filter at a point x of an image f depends on the values of t he image points in the neighborhood of x. This neighborhood is determined by a wind ow W that is located at point x of f including n points x1, x2, …, xn of f, with n=2k+1. The proposed adaptive content based median filter can be utilized for impulse noisesu p pression in gray-scale images. A block diagram of the adaptive filtering procedure is depicted in Fig. 1. The noise detection procedure for both positive and negative noise is as follows:(i) We consider a neighborhood window W that is located at point x of the image f. Th e differences between the central pixel at point x and the pixel values of the n-1surr ounding points of the neighborhood (excluding thevalue of the central pixel) are co mputed.(ii) The sum of the absolute values of these differences is computed, denoted as fabs(x ). This value provides ameasure of closeness between the central pixel and its su rrounding pixels.(iii) The value fabs(x) is compared to fthreshold(x), which is anappropriately selected positive integer threshold value and can be modified. The central pixel is conside red to be noise when the value fabs(x) is greater than thethreshold value fthresho d(x).(iv) When the central pixel is considered to be noise it is substituted by the median val ue of the image neighborhood,denoted as fk+1, which is the normal operationof the median filter. In the opposite case, the value of the central pixel is not altered and the procedure is repeated for the next neighborhood window.From the noised etection scheme described, it should be mentioned that the noise detection level procedure can be controlled and a range of pixel values (and not only the fixedvalues of 0 and 255, salt and pepper noise) is considered asimpulse noise.In Fig. 2 the results of the application of the median filter and the CBMF in the gray-sca le image “Peppers” are depicted.More specifically, in Fig. 2(a) the original,uncor rupted image“Peppers” is depicted. In Fig. 2(b) the original imagedegraded by 5% both positive and negative impulse noise isillustrated. In Figs 2(c) and 2(d) the resultant images of the application of median filter and CBMF for a 3×3-pixel win dow are shown, respectively. Finally, the resultant images of the application of m edian filter and CBMF for a 5×5-pixelwindow are presented in Figs 2(e) and 2(f). It can be noticed that the application of the CBMF preserves much better edges a nddetails of the images, in comparison to the median filter.A number of different objective measures can be utilized forthe evaluation of these results. The most wi dely used measures are the Mean Square Error (MSE) and the Normalized Mean Square Error (NMSE) [1]. The results of the estimation of these measures for the two filters are depicted in Table I.For the estimation of these measures, the result ant images of the filters are compared to the original, uncorrupted image.From T able I it can be noticed that the MSE and NMSE estimatedfor the application of t he CBMF are considerably smaller than those estimated for the median filter, in all the cases.Table I. Similarity measures.3. HARDWARE ARCHITECTUREThe structure of the adaptive filter comprises four basic functional units, the mo ving window unit , the median computation unit , the arithmetic operations unit , and th e output selection unit . The input data of the system are the gray-scale values of the pi xels of the image neighborhood and the noise threshold value. For the computation of the filter output a3×3 or 5×5-pixel image neighborhood can be selected. Image input d ata is serially imported into the first stage. In this way,the total number of the inputpin s are 24 (21 inputs for the input data and 3 inputs for the clock and the control signalsr equired). The output data of the system are the resultant gray-scale values computed f or the operation selected (8pins).The moving window unit is the internal memory of the system,used for storing th e input values of the pixels and for realizing the moving window operation. The pixel values of the input image, denoted as “IMAGE_INPUT[7..0]”, areimported into this u nit in serial. For the representation of thethreshold value used for the detection of a no Filter Impulse noise 5% mse Nmse(×10-2) 3×3 5×5 3×3 5×5Median CBMF 57.554 35.287 130.496 84.788 0.317 0.194 0.718 0.467ise pixel 13 bits are required. For the moving window operation a 3×3 (5×5)-pixel sep entine type memory is used, consisting of 9 (25)registers. In this way,when the windoP1 P2 P3w is moved into the next image neighborhood only 3 or 5 pixel values stored in the memory are altered. The “en5×5” control signal is used for the selection of the size of th e image window, when“en5×5” is equal to “0” (“1”) a 3×3 (5×5)-pixel neighborhood is selected. It should be mentioned that the modules of the circuit used for the 3×3-pix el window are utilized for the 5×5-pixel window as well. For these modules, 2-to-1mu ltiplexers are utilized to select the appropriate pixel values,where necessary. The mod ules that are utilized only in the case of the 5×5-pixel neighborhood are enabled by th e“en5×5” control signal. The outputs of this unit are rows ofpixel values (3 or 5, respe ctively), which are the inputs to the median computation unit.The task of the median c omputation unit is to compute themedian value of the image neighborhood in order to substitutethe central pixel value, if necessary. For this purpose a25-input sorter is utili zeed. The structure of the sorter has been proposed by Batcher and is based on the use of CS blocks. ACS block is a max/min module; its first output is the maximumof the i nputs and its second output the minimum. The implementation of a CS block includes a comparator and two 2-to-1 multiplexers. The outputs values of the sorter, denoted a s “OUT_0[7..0]”…. “OUT_24[7..0]”, produce a “sorted list” of the 25 initial pixel val ues. A 2-to-1 multiplexer isused for the selection of the median value for a 3×3 or 5×5-pixel neighborhood.The function of the arithmetic operations unit is to computethe value fabs(x), whi ch is compared to the noise threshold value in the final stage of the adaptive filter.The in puts of this unit are the surrounding pixel values and the central pixelof the neighb orhood. For the implementation of the mathematical expression of fabs(x), the circuit of this unit contains a number of adder modules. Note that registers have been used to achieve a pipelined operation. An additional 2-to-1 multiplexer is utilized for the selec tion of the appropriate output value, depending on the “en5×5” control signal. From th e implementation point of view, the use of arithmetic blocks makes this stage hardwar e demanding.The output selection unit is used for the selection of the appropriateoutput value of the performed noise suppression operation. For this selection, the corresponding no ise threshold value calculated for the image neighborhood,“NOISE_THRES HOLD[1 2..0]”,is employed. This value is compared to fabs(x) and the result of the comparison Classifies the central pixel either as impulse noise or not. If thevalue fabs(x) is greater than the threshold value fthreshold(x) the central pixel is positive or negative impulse noise and has to be eliminated. For this reason, the output of the comparison is used as the selection signal of a 2-to-1 multiplexer whose inputs are the central pixel and the c orresponding median value for the image neighborhood. The output of the multiplexer is the output of this stage and the final output of the circuit of the adaptive filter.The st ructure of the CBMF, the computation procedure and the design of the four aforeme n tioned units are illustrated in Fig. 3.ImagewindoeFigure 1: Block diagram of the filtering methodFigure 2: Results of the application of the CBMF: (a) Original image, (b) noise corrupted image (c) Restored image by a 3x3 MF, (d) Restored image by a 3x3 CBMF, (e) Restored image by a 5x5 MF and (f) Restored image by a 5x5 CBMF.4. IMPLEMENTATION ISSUESThe proposed structure was implemented in FPGA,which offer an attractive com bination of low cost, high performance and apparent flexibility, using the software pa ckage+PLUS II of Altera Corporation. The FPGA used is the EPF10K200SFC484-1 d evice of the FLEX10KE device family,a device family suitable for designs that requir e high densities and high I/O count. The 99% of the logic cells(9965/9984 logic cells) of the device was utilized to implement the circuit . The typical operating clock frequ ency of the system is 55 MHz. As a comparison, the time required to perform filtering of a gray-scale image of 260×244 pixelsusing Matlab® software on a Pentium 4/2.4 G Hz computer system is approximately 7.2 sec, whereas the corresponding time using h ardware is approximately 10.6 msec.The modification of the system to accommodate windows oflarger sizes can be done in a straightforward way, requiring onlya small nu mber of changes. More specifically, in the first unit the size of the serpentine memory P4P5P6P7P8P9SubtractorarryMedianfilteradder comparatormuitiplexerf abc(x)valueand the corresponding number of multiplexers increase following a square law. In the second unit, the sorter module should be modified,and in the third unit the number of the adder devicesincreases following a square law. In the last unit no changes are requ ired.5. CONCLUSIONSThis paper presents a new hardware structure of a content based median filter, ca pable of performing adaptive impulse noise removal for gray-scale images. The noise detection procedure takes into account the differences between the central pixel and th e surrounding pixels of a neighborhood.The proposed digital circuit is capable ofproce ssing grayscale images of 8-bit resolution, with 3×3 or 5×5-pixel neighborhoods as op tions for the computation of the filter output. However, the design of the circuit is dire ctly expandableto accommodate larger size image windows. The adaptive filter was d eigned and implemented in FPGA. The typical clock frequency is 55 MHz and the sys tem is suitable forreal-time imaging applications.REFERENCES[1] W. K. Pratt, Digital Image Processing. New York: Wiley,1991.[2] G. R. Arce, N. C. Gallagher and T. Nodes, “Median filters:Theory and applicat ions,” in Advances in ComputerVision and Image Processing, Greenwich, CT: JAI, 1986.[3] T. A. Nodes and N. C. Gallagher, Jr., “The output distributionof median type filte rs,” IEEE Transactions onCommunications, vol. COM-32, pp. 532-541, May1984.[4] T. Sun and Y. Neuvo, “Detail-preserving median basedfilters in imageprocessing,” Pattern Recognition Letters,vol. 15, pp. 341-347, Apr. 1994.[5] E. Abreau, M. Lightstone, S. K. Mitra, and K. Arakawa,“A new efficient approachfor the removal of impulsenoise from highly corrupted images,” IEEE Transa ctionson Image Processing, vol. 5, pp. 1012-1025, June 1996.[6] E. R. Dougherty and P. Laplante, Introduction to Real-Time Imaging, Bellingham:SPIE/IEEE Press, 1995.二、英文翻译基于中值滤波的新的内容摘要在本设计中的提出了基于中值滤波的硬件实现用来抑制脉冲噪声的干扰。

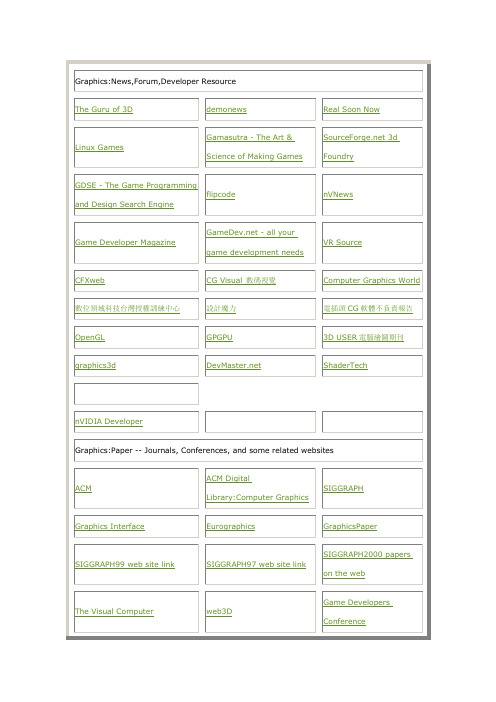

常用的图形库

ESRI

PCI Geomatics

Digital Grove

JDMCox Global Mapper Software(USAPhotoMaps) 3DEM

MARPLOT

Map Maker

OCAD

SurGe

3D Contour Maps

geoTIFF Examiner

shapechk

GeoMerge

Relief Texture Mapping

Graphics:Non-Photo-Realistic Rendering(NPR)

NPR

Shadows for Cel Animation

David Salesin

Virtual Clay: A Deformation NPRQuake Model by 3D Cellular Automata

GRAIL: Graphics and Imaging Laboratory

Microsoft Research: UCSC SciVis Graphics

Visualization Lab SUNY at Stony VRVis Brook, New York

Institut of Computer Graphics and Algorithms

tiff library

Independent JPEG Group

FFTW

paintlib

png library

libungif

Gnuplot

Interactive Data ImageMagick Language(IDL) Matlab

IPL98

CVIPtools

Cppima

Open Source Computer VXL Vision Library JBIG-KIT

System-level

This research was partly sponsored by the JESSI AC75 project of the EC

1

Abstract

Application studies in the areas of image and video processing systems indicate that between 50 and 80% of the area cost in (application-speci c) architectures for realtime multi-dimensional signal processing (RMSP) is due to memory units , i.e. single or multi-port RAMs, pointer-addressed memories, and register les. This is true for both single-processor and weakly parallel processor realizations. This paper has two main contributions. First, to reduce this dominant cost, we propose to address the systemlevel storage organization for the multi-dimensional (M-D) signals as a rst step in the overall methodology to map these applications, even before the parallelization and load balancing. Secondly, we will demonstrate the usefulness of this novel approach based on two realistic test-vehicles, namely a cavity detector for medical image processing and a quad-tree based image coding application. The novel design results for these relevant applications are useful as such.

CCF推荐的国际学术会议和期刊目录修订版发布

CCF推荐的国际学术会议和期刊目录修订版发布CCF(China Computer Federation中国计算机学会)于2010年8月发布了第一版推荐的国际学术会议和期刊目录,一年来,经过业内专家的反馈和修订,于日前推出了修订版,现将修订版予以发布。

本次修订对上一版内容进行了充实,一些会议和期刊的分类排行进行了调整,目录包括:计算机科学理论、计算机体系结构与高性能计算、计算机图形学与多媒体、计算机网络、交叉学科、人工智能与模式识别、软件工程/系统软件/程序设计语言、数据库/数据挖掘/内容检索、网络与信息安全、综合刊物等方向的国际学术会议及期刊目录,供国内高校和科研单位作为学术评价的参考依据。

目录中,刊物和会议分为A、B、C三档。

A类表示国际上极少数的顶级刊物和会议,鼓励我国学者去突破;B类是指国际上著名和非常重要的会议、刊物,代表该领域的较高水平,鼓励国内同行投稿;C类指国际上重要、为国际学术界所认可的会议和刊物。

这些分类目录每年将学术界的反馈和意见,进行修订,并逐步增加研究方向。

中国计算机学会推荐国际学术刊物(网络/信息安全)一、 A类序号刊物简称刊物全称出版社网址1. TIFS IEEE Transactions on Information Forensics andSecurity IEEE /organizations/society/sp/tifs.html2. TDSC IEEE Transactions on Dependable and Secure ComputingIEEE /tdsc/3. TISSEC ACM Transactions on Information and SystemSecurity ACM /二、 B类序号刊物简称刊物全称出版社网址1. Journal of Cryptology Springer /jofc/jofc.html2. Journal of Computer SecurityIOS Press /jcs/3. IEEE Security & Privacy IEEE/security/4. Computers &Security Elsevier http://www.elsevier.nl/inca/publications/store/4/0/5/8/7/7/5. JISecJournal of Internet Security NahumGoldmann. /JiSec/index.asp6. Designs, Codes andCryptography Springer /east/home/math/numbers?SGWID=5 -10048-70-35730330-07. IET Information Security IET /IET-IFS8. EURASIP Journal on InformationSecurity Hindawi /journals/is三、C类序号刊物简称刊物全称出版社网址1. CISDA Computational Intelligence for Security and DefenseApplications IEEE /2. CLSR Computer Law and SecurityReports Elsevier /science/journal/026736493. Information Management & Computer Security MCB UniversityPress /info/journals/imcs/imcs.jsp4. Information Security TechnicalReport Elsevier /locate/istr中国计算机学会推荐国际学术会议(网络/信息安全方向)一、A类序号会议简称会议全称出版社网址1. S&PIEEE Symposium on Security and Privacy IEEE /TC/SP-Index.html2. CCSACM Conference on Computer and Communications Security ACM /sigs/sigsac/ccs/3. CRYPTO International Cryptology Conference Springer-Verlag /conferences/二、B类序号会议简称会议全称出版社网址1. SecurityUSENIX Security Symposium USENIX /events/2. NDSSISOC Network and Distributed System Security Symposium Internet Society /isoc/conferences/ndss/3. EurocryptAnnual International Conference on the Theory and Applications of Cryptographic Techniques Springer /conferences/eurocrypt2009/4. IH Workshop on Information Hiding Springer-Verlag /~rja14/ihws.html5. ESORICSEuropean Symposium on Research in Computer Security Springer-Verlag as.fr/%7Eesorics/6. RAIDInternational Symposium on Recent Advances in Intrusion Detection Springer-Verlag /7. ACSACAnnual Computer Security Applications ConferenceIEEE /8. DSNThe International Conference on Dependable Systems and Networks IEEE/IFIP /9. CSFWIEEE Computer Security Foundations Workshop /CSFWweb/10. TCC Theory of Cryptography Conference Springer-Verlag /~tcc08/11. ASIACRYPT Annual International Conference on the Theory and Application of Cryptology and Information Security Springer-Verlag /conferences/ 12. PKC International Workshop on Practice and Theory in Public Key Cryptography Springer-Verlag /workshops/pkc2008/三、 C类序号会议简称会议全称出版社网址1. SecureCommInternational Conference on Security and Privacy in Communication Networks ACM /2. ASIACCSACM Symposium on Information, Computer and Communications Security ACM .tw/asiaccs/3. ACNSApplied Cryptography and Network Security Springer-Verlag /acns_home/4. NSPWNew Security Paradigms Workshop ACM /current/5. FC Financial Cryptography Springer-Verlag http://fc08.ifca.ai/6. SACACM Symposium on Applied Computing ACM /conferences/sac/ 7. ICICS International Conference on Information and Communications Security Springer /ICICS06/8. ISC Information Security Conference Springer /9. ICISCInternational Conference on Information Security and Cryptology Springer /10. FSE Fast Software Encryption Springer http://fse2008.epfl.ch/11. WiSe ACM Workshop on Wireless Security ACM /~adrian/wise2004/12. SASN ACM Workshop on Security of Ad-Hoc and Sensor Networks ACM /~szhu/SASN2006/13. WORM ACM Workshop on Rapid Malcode ACM /~farnam/worm2006.html14. DRM ACM Workshop on Digital Rights Management ACM /~drm2007/15. SEC IFIP International Information Security Conference Springer http://sec2008.dti.unimi.it/16. IWIAIEEE International Information Assurance Workshop IEEE /17. IAWIEEE SMC Information Assurance Workshop IEEE /workshop18. SACMATACM Symposium on Access Control Models and Technologies ACM /19. CHESWorkshop on Cryptographic Hardware and Embedded Systems Springer /20. CT-RSA RSA Conference, Cryptographers' Track Springer /21. DIMVA SIG SIDAR Conference on Detection of Intrusions and Malware and Vulnerability Assessment IEEE /dimva200622. SRUTI Steps to Reducing Unwanted Traffic on the Internet USENIX /events/23. HotSecUSENIX Workshop on Hot Topics in Security USENIX /events/ 24. HotBots USENIX Workshop on Hot Topics in Understanding Botnets USENIX /event/hotbots07/tech/25. ACM MM&SEC ACM Multimedia and Security Workshop ACM。

红楼梦论文外文参考文献大全

红楼梦论文外文参考文献大全《红楼梦》复杂的版本问题历来为学界所关注。

20世纪20年代以来,陆续发现的抄本刻本就达13种之多,且彼此间存在相当数量的异文。

在何本为最好的版本这一问题上,学界的评价标准呈现多元化特征。

其中,从校勘学的研究视角,以是否贴近曹雪芹原笔原意,是否“真本”作为“优本”评判标准的观点占主流,以文字的艺术效果作为评判标准的观点占少数。

我们在这里了一些红楼梦论文外文参考文献,希望对你有用。

1、陆超逸。

AContrastiveStudyoftheTranslationofCultural-SpecificContent inHongloumeng[J].海外英语。

xx(05)2、王丽鸽。

OnEnglishTranslationofCharacters'NamesofTwoEnglishVersionso fADreamofRedMansions[J].海外英语。

xx(16)3、李淑曼。

浅析《红楼梦》第三回中异化归化译法现象[J].北方文学。

xx(18)4、余丽娟。

TheTranslationoftheFuzzyNumeralsinADreamofRedMansions[J].教师。

xx(09)5、俞心瑶。

TranslationsofUnreliableNarrativeinHongloumeng:AComparativeStudyonADreamofRedMansionsandTheStoryoftheStone[J].疯狂英语(理论版)。

xx(02)6、高林芝。

OntheEnglishTranslationofPortraitDescriptionintheTwoVersion sofADreamofRedMansionsfromthePerspectiveofDiction[J].校园英语。

xx(13)7、张曦。

OntheTranslationofIdiomsinADreamofRedMansions[J].台声。

计算机专用术语英文及中文翻译

计算机术语大全1、CPU3DNow!(3D no waiting,无须等待的3D处理)AAM(AMD Analyst Meeting,AMD分析家会议)ABP(Advanced Branch Prediction,高级分支预测)ACG(Aggressive Clock Gating,主动时钟选择)AIS(Alternate Instruction Set,交替指令集)ALA T(advanced load table,高级载入表)ALU(Arithmetic Logic Unit,算术逻辑单元)Aluminum(铝)AGU(Address Generation Units,地址产成单元)APC(Advanced Power Control,高级能源控制)APIC(Advanced rogrammable Interrupt Controller,高级可编程中断控制器)APS(Alternate Phase Shifting,交替相位跳转)ASB(Advanced System Buffering,高级系统缓冲)A TC(Advanced Transfer Cache,高级转移缓存)A TD(Assembly Technology Development,装配技术发展)BBUL(Bumpless Build-Up Layer,内建非凹凸层)BGA(Ball Grid Array,球状网阵排列)BHT(branch prediction table,分支预测表)Bops(Billion Operations Per Second,10亿操作秒)BPU(Branch Processing Unit,分支处理单元)BP(Brach Pediction,分支预测)BSP(Boot Strap Processor,启动捆绑处理器)BTAC(Branch Target Address Calculator,分支目标寻址计算器)CBGA (Ceramic Ball Grid Array,陶瓷球状网阵排列)CDIP (Ceramic Dual-In-Line,陶瓷双重直线)Center Processing Unit Utilization,中央处理器占用率CFM(cubic feet per minute,立方英尺秒)CMT(course-grained multithreading,过程消除多线程)CMOS(Complementary Metal Oxide Semiconductor,互补金属氧化物半导体)CMOV(conditional move instruction,条件移动指令)CISC(Complex Instruction Set Computing,复杂指令集计算机)CLK(Clock Cycle,时钟周期)CMP(on-chip multiprocessor,片内多重处理)CMS(Code Morphing Software,代码变形软件)co-CPU(cooperative CPU,协处理器)COB(Cache on board,板上集成缓存,做在CPU卡上的二级缓存,通常是内核的一半速度))COD(Cache on Die,芯片内核集成缓存)Copper(铜)CPGA(Ceramic Pin Grid Array,陶瓷针型栅格阵列)CPI(cycles per instruction,周期指令)CPLD(Complex Programmable Logic Device,複雜可程式化邏輯元件)CPU(Center Processing Unit,中央处理器)CRT(Cooperative Redundant Threads,协同多余线程)CSP(Chip Scale Package,芯片比例封装)CXT(Chooper eXTend,增强形K6-2内核,即K6-3)Data Forwarding(数据前送)dB(decibel,分贝)DCLK(Dot Clock,点时钟)DCT(DRAM Controller,DRAM控制器)DDT(Dynamic Deferred Transaction,动态延期处理)Decode(指令解码)DIB(Dual Independent Bus,双重独立总线)DMT(Dynamic Multithreading Architecture,动态多线程结构)DP(Dual Processor,双处理器)DSM(Dedicated Stack Manager,专门堆栈管理)DSMT(Dynamic Simultaneous Multithreading,动态同步多线程)DST(Depleted Substrate Transistor,衰竭型底层晶体管)DTV(Dual Threshold V oltage,双重极限电压)DUV(Deep Ultra-Violet,纵深紫外光)EBGA(Enhanced Ball Grid Array,增强形球状网阵排列)EBL(electron beam lithography,电子束平版印刷)EC(Embedded Controller,嵌入式控制器)EDB(Execute Disable Bit,执行禁止位)EDEC(Early Decode,早期解码)Embedded Chips(嵌入式)EM64T(Extended Memory 64 Technology,扩展内存64技术)EPA(edge pin array,边缘针脚阵列)EPF(Embedded Processor Forum,嵌入式处理器论坛)EPL(electron projection lithography,电子发射平版印刷)EPM(Enhanced Power Management,增强形能源管理)EPIC(explicitly parallel instruction code,并行指令代码)EUV(Extreme Ultra Violet,紫外光)EUV(extreme ultraviolet lithography,极端紫外平版印刷)FADD(Floationg Point Addition,浮点加)FBGA(Fine-Pitch Ball Grid Array,精细倾斜球状网阵包装)FBGA(flipchip BGA,轻型芯片BGA)FC-BGA(Flip-Chip Ball Grid Array,翻转芯片球形网阵包装)FC-LGA(Flip-Chip Land Grid Array,翻转接点网阵包装)FC-PGA(Flip-Chip Pin Grid Array,翻转芯片球状网阵包装)FDIV(Floationg Point Divide,浮点除)FEMMS:Fast EntryExit Multimedia State,快速进入退出多媒体状态FFT(fast Fourier transform,快速热欧姆转换)FGM(Fine-Grained Multithreading,高级多线程)FID(FID:Frequency identify,频率鉴别号码)FIFO(First Input First Output,先入先出队列)FISC(Fast Instruction Set Computer,快速指令集计算机)flip-chip(芯片反转)FLOPs(Floating Point Operations Per Second,浮点操作秒)FMT(fine-grained multithreading,纯消除多线程)FMUL(Floationg Point Multiplication,浮点乘)FPRs(floating-point registers,浮点寄存器)FPU(Float Point Unit,浮点运算单元)FSUB(Floationg Point Subtraction,浮点减)GFD(Gold finger Device,金手指超频设备)GHC(Global History Counter,通用历史计数器)GTL(Gunning Transceiver Logic,射电收发逻辑电路)GVPP(Generic Visual Perception Processor,常规视觉处理器)HL-PBGA表面黏著,高耐热、轻薄型塑胶球状网阵封装HTT(Hyper-Threading Technology,超级线程技术)Hz(hertz,赫兹,频率单位)IA(Intel Architecture,英特尔架构)IAA(Intel Application Accelerator,英特尔应用程序加速器)IA TM(Intel Advanced Thermal Manager,英特尔高级热量管理指令集)ICU(Instruction Control Unit,指令控制单元)ID(identify,鉴别号码)IDF(Intel Developer Forum,英特尔开发者论坛)IDMB(Intel Digital Media Boost,英特尔数字媒体推进指令集)IDPC(Intel Dynamic Power Coordination,英特尔动态能源调和指令集)IEU(Integer Execution Units,整数执行单元)IHS(Integrated Heat Spreader,完整热量扩展)ILP(Instruction Level Parallelism,指令级平行运算)IMM Intel Mobile Module, 英特尔移动模块Instructions Cache,指令缓存Instruction Coloring(指令分类)IOPs(Integer Operations Per Second,整数操作秒)IPC(Instructions Per Clock Cycle,指令时钟周期)ISA(instruction set architecture,指令集架构)ISD(inbuilt speed-throttling device,内藏速度控制设备)ITC(Instruction Trace Cache,指令追踪缓存)ITRS(International Technology Roadmap for Semiconductors,国际半导体技术发展蓝图)KNI(Katmai New Instructions,Katmai新指令集,即SSE)Latency(潜伏期)LDT(Lightning Data Transport,闪电数据传输总线)LFU(Legacy Function Unit,传统功能单元)LGA(land grid array,接点栅格阵列)LN2(Liquid Nitrogen,液氮)Local Interconnect(局域互连)MAC(multiply-accumulate,累积乘法)mBGA (Micro Ball Grid Array,微型球状网阵排列)nm(namometer,十亿分之一米毫微米)MCA(Machine Check Architecture,机器检查架构)MCU(Micro-Controller Unit,微控制器单元)MCT(Memory Controller,内存控制器)MESI(Modified, Exclusive, Shared, Invalid:修改、排除、共享、废弃)MF(MicroOps Fusion,微指令合并)mm(micron metric,微米)MMX(MultiMedia Extensions,多媒体扩展指令集)MMU(Multimedia Unit,多媒体单元)MMU(Memory Management Unit,内存管理单元)MN(model numbers,型号数字)MFLOPS(Million Floationg PointSecond,每秒百万个浮点操作)MHz(megahertz,兆赫)mil(PCB 或晶片佈局的長度單位,1 mil = 千分之一英寸)MIMD(Multi Instruction Multiple Data,多指令多数据流)MIPS(Million Instruction Per Second,百万条指令秒)MOESI(Modified, Owned, Exclusive, Shared or Invalid,修改、自有、排除、共享或无效)MOF(Micro Ops Fusion,微操作熔合)Mops(Million Operations Per Second,百万次操作秒)MP(Multi-Processing,多重处理器架构)MPF(Micro processor Forum,微处理器论坛)MPU(Microprocessor Unit,微处理器)MPS(MultiProcessor Specification,多重处理器规范)MSRs(Model-Specific Registers,特别模块寄存器)MSV(Multiprocessor Specification V ersion,多处理器规范版本)MVP(Mobile V oltage Positioning,移动电压定位)IVNAOC(no-account OverClock,无效超频)NI(Non-Intel,非英特尔)NOP(no operation,非操作指令)NRE(Non-Recurring Engineering charge,非重複性工程費用)OBGA(Organic Ball Grid Arral,有机球状网阵排列)OCPL(Off Center Parting Line,远离中心部分线队列)OLGA(Organic Land Grid Array,有机平面网阵包装)OoO(Out of Order,乱序执行)OPC(Optical Proximity Correction,光学临近修正)OPGA(Organic Pin Grid Array,有机塑料针型栅格阵列)OPN(Ordering Part Number,分类零件号码)PA T(Performance Acceleration Technology,性能加速技术)PBGA(Plastic Pin Ball Grid Array,塑胶球状网阵排列)PDIP (Plastic Dual-In-Line,塑料双重直线)PDP(Parallel Data Processing,并行数据处理)PGA(Pin-Grid Array,引脚网格阵列),耗电大PLCC (Plastic Leaded Chip Carriers,塑料行间芯片运载)Post-RISC(加速RISC,或后RISC)PPE(Power Processor Element,Power处理器元件)PPU(Physics Processing Unit,物理处理单元)PR(Performance Rate,性能比率)PIB(Processor In a Box,盒装处理器)PM(Pseudo-Multithreading,假多线程)PPGA(Plastic Pin Grid Array,塑胶针状网阵封装)PQFP(Plastic Quad Flat Package,塑料方块平面封装)PSN(Processor Serial numbers,处理器序列号)QFP(Quad Flat Package,方块平面封装)QSPS(Quick Start Power State,快速启动能源状态)RAS(Return Address Stack,返回地址堆栈)RAW(Read after Write,写后读)REE(Rapid Execution Engine,快速执行引擎)Register Contention(抢占寄存器)Register Pressure(寄存器不足)Register Renaming(寄存器重命名)Remark(芯片频率重标识)Resource contention(资源冲突)Retirement(指令引退)RISC(Reduced Instruction Set Computing,精简指令集计算机)ROB(Re-Order Buffer,重排序缓冲区)RSE(register stack engine,寄存器堆栈引擎)RTL(Register Transfer Level,暫存器轉換層。

国际计算机会议与期刊分级列表

Computer Science Department Conference RankingsSome conferences accept multiple categories of papers. The rankingsbelow are for the most prestigious category of paper at a givenconference. All other categories should be treated as "unranked".AREA: Artificial Intelligence and Related SubjectsRank 1:IJCAI: Intl Joint Conf on AIAAAI: American Association for AI National ConferenceICAA: International Conference on Autonomous Agents(现改名为AAMAS) CVPR: IEEE Conf on Comp Vision and Pattern RecognitionICCV: Intl Conf on Computer VisionICML: Intl Conf on Machine LearningKDD: Knowledge Discovery and Data MiningKR: Intl Conf on Principles of KR & ReasoningNIPS: Neural Information Processing SystemsUAI: Conference on Uncertainty in AIACL: Annual Meeting of the ACL (Association of Computational Linguistics) Rank 2:AID: Intl Conf on AI in DesignAI-ED: World Conference on AI in EducationCAIP: Inttl Conf on Comp. Analysis of Images and PatternsCSSAC: Cognitive Science Society Annual ConferenceECCV: European Conference on Computer VisionEAI: European Conf on AIEML: European Conf on Machine LearningGP: Genetic Programming ConferenceIAAI: Innovative Applications in AIICIP: Intl Conf on Image ProcessingICNN/IJCNN: Intl (Joint) Conference on Neural NetworksICPR: Intl Conf on Pattern RecognitionICDAR: International Conference on Document Analysis and RecognitionICTAI: IEEE conference on Tools with AIAMAI: Artificial Intelligence and MathsDAS: International Workshop on Document Analysis SystemsWACV: IEEE Workshop on Apps of Computer VisionCOLING: International Conference on Computational LiguisticsEMNLP: Empirical Methods in Natural Language ProcessingRank 3:PRICAI: Pacific Rim Intl Conf on AIAAI: Australian National Conf on AIACCV: Asian Conference on Computer VisionAI*IA: Congress of the Italian Assoc for AIANNIE: Artificial Neural Networks in EngineeringANZIIS: Australian/NZ Conf on Intelligent Inf. SystemsCAIA: Conf on AI for ApplicationsCAAI: Canadian Artificial Intelligence ConferenceASADM: Chicago ASA Data Mining Conf: A Hard Look at DMEPIA: Portuguese Conference on Artificial IntelligenceFCKAML: French Conf on Know. Acquisition & Machine LearningICANN: International Conf on Artificial Neural NetworksICCB: International Conference on Case-Based ReasoningICGA: International Conference on Genetic AlgorithmsICONIP: Intl Conf on Neural Information ProcessingIEA/AIE: Intl Conf on Ind. & Eng. Apps of AI & Expert SysICMS: International Conference on Multiagent SystemsICPS: International conference on Planning SystemsIWANN: Intl Work-Conf on Art & Natural Neural NetworksPACES: Pacific Asian Conference on Expert SystemsSCAI: Scandinavian Conference on Artifical IntelligenceSPICIS: Singapore Intl Conf on Intelligent SystemPAKDD: Pacific-Asia Conf on Know. Discovery & Data MiningSMC: IEEE Intl Conf on Systems, Man and CyberneticsPAKDDM: Practical App of Knowledge Discovery & Data MiningWCNN: The World Congress on Neural NetworksWCES: World Congress on Expert SystemsINBS: IEEE Intl Symp on Intell. in Neural \& Bio SystemsASC: Intl Conf on AI and Soft ComputingPACLIC: Pacific Asia Conference on Language, Information and Computation ICCC: International Conference on Chinese ComputingOthers:ICRA: IEEE Intl Conf on Robotics and AutomationNNSP: Neural Networks for Signal ProcessingICASSP: IEEE Intl Conf on Acoustics, Speech and SPGCCCE: Global Chinese Conference on Computers in EducationICAI: Intl Conf on Artificial IntelligenceAEN: IASTED Intl Conf on AI, Exp Sys & Neural NetworksWMSCI: World Multiconfs on Sys, Cybernetics & InformaticsAREA: Hardware and ArchitectureRank 1:ASPLOS: Architectural Support for Prog Lang and OSISCA: ACM/IEEE Symp on Computer ArchitectureICCAD: Intl Conf on Computer-Aided DesignDAC: Design Automation ConfMICRO: Intl Symp on MicroarchitectureHPCA: IEEE Symp on High-Perf Comp ArchitectureRank 2:FCCM: IEEE Symposium on Field Programmable Custom Computing Machines SUPER: ACM/IEEE Supercomputing ConferenceICS: Intl Conf on SupercomputingISSCC: IEEE Intl Solid-State Circuits ConfHCS: Hot Chips SympVLSI: IEEE Symp VLSI CircuitsISSS: International Symposium on System SynthesisDATE: IEEE/ACM Design, Automation & Test in Europe ConferenceRank 3:ICA3PP: Algs and Archs for Parall ProcEuroMICRO: New Frontiers of Information TechnologyACS: Australian Supercomputing ConfUnranked:Advanced Research in VLSIInternational Symposium on System SynthesisInternational Symposium on Computer DesignInternational Symposium on Circuits and SystemsAsia Pacific Design Automation ConferenceInternational Symposium on Physical DesignInternational Conference on VLSI DesignAREA: ApplicationsRank 1:I3DG: ACM-SIGRAPH Interactive 3D GraphicsSIGGRAPH: ACM SIGGRAPH ConferenceACM-MM: ACM Multimedia ConferenceDCC: Data Compression ConfSIGMETRICS: ACM Conf on Meas. & Modelling of Comp SysSIGIR: ACM SIGIR Conf on Information RetrievalPECCS: IFIP Intl Conf on Perf Eval of Comp \& Comm SysWWW: World-Wide Web ConferenceRank 2:EUROGRAPH: European Graphics ConferenceCGI: Computer Graphics InternationalCANIM: Computer AnimationPG: Pacific GraphicsIEEE-MM: IEEE Intl Conf on Multimedia Computing and SysNOSSDAV: Network and OS Support for Digital A/VPADS: ACM/IEEE/SCS Workshop on Parallel \& Dist Simulation WSC: Winter Simulation ConferenceASS: IEEE Annual Simulation SymposiumMASCOTS: Symp Model Analysis \& Sim of Comp \& Telecom Sys PT: Perf Tools - Intl Conf on Model Tech \& Tools for CPENetStore - Network Storage SymposiumRank 3:ACM-HPC: ACM Hypertext ConfMMM: Multimedia ModellingDSS: Distributed Simulation SymposiumSCSC: Summer Computer Simulation ConferenceWCSS: World Congress on Systems SimulationESS: European Simulation SymposiumESM: European Simulation MulticonferenceHPCN: High-Performance Computing and NetworkingGeometry Modeling and ProcessingWISEDS-RT: Distributed Simulation and Real-time ApplicationsIEEE Intl Wshop on Dist Int Simul and Real-Time ApplicationsUn-ranked:DVAT: IS\&T/SPIE Conf on Dig Video Compression Alg \& Tech MME: IEEE Intl Conf. on Multimedia in EducationICMSO: Intl Conf on Modelling, Simulation and OptimisationICMS: IASTED Intl Conf on Modelling and SimulationAREA: System TechnologyRank 1:SIGCOMM: ACM Conf on Comm Architectures, Protocols & Apps INFOCOM: Annual Joint Conf IEEE Comp & Comm SocSPAA: Symp on Parallel Algms and ArchitecturePODC: ACM Symp on Principles of Distributed ComputingPPoPP: Principles and Practice of Parallel ProgrammingMassPar: Symp on Frontiers of Massively Parallel ProcRTSS: Real Time Systems SympSOSP: ACM SIGOPS Symp on OS PrinciplesSOSDI: Usenix Symp on OS Design and ImplementationCCS: ACM Conf on Comp and Communications SecurityIEEE Symposium on Security and PrivacyMOBICOM: ACM Intl Conf on Mobile Computing and Networking USENIX Conf on Internet Tech and SysICNP: Intl Conf on Network ProtocolsOPENARCH: IEEE Conf on Open Arch and Network ProgPACT: Intl Conf on Parallel Arch and Compil TechRank 2:CC: Compiler ConstructionIPDPS: Intl Parallel and Dist Processing SympIC3N: Intl Conf on Comp Comm and NetworksICPP: Intl Conf on Parallel ProcessingICDCS: IEEE Intl Conf on Distributed Comp SystemsSRDS: Symp on Reliable Distributed SystemsMPPOI: Massively Par Proc Using Opt InterconnsASAP: Intl Conf on Apps for Specific Array ProcessorsEuro-Par: European Conf. on Parallel ComputingFast Software EncryptionUsenix Security SymposiumEuropean Symposium on Research in Computer SecurityWCW: Web Caching WorkshopLCN: IEEE Annual Conference on Local Computer NetworksIPCCC: IEEE Intl Phoenix Conf on Comp & CommunicationsCCC: Cluster Computing ConferenceICC: Intl Conf on CommRank 3:MPCS: Intl. Conf. on Massively Parallel Computing SystemsGLOBECOM: Global CommICCC: Intl Conf on Comp CommunicationNOMS: IEEE Network Operations and Management SympCONPAR: Intl Conf on Vector and Parallel ProcessingVAPP: Vector and Parallel ProcessingICPADS: Intl Conf. on Parallel and Distributed SystemsPublic Key CryptosystemsIEEE Computer Security Foundations WorkshopAnnual Workshop on Selected Areas in CryptographyAustralasia Conference on Information Security and PrivacyInt. Conf on Inofrm and Comm. SecurityFinancial CryptographyWorkshop on Information HidingSmart Card Research and Advanced Application ConferenceICON: Intl Conf on NetworksIMSA: Intl Conf on Internet and MMedia SysNCC: Nat Conf CommIN: IEEE Intell Network WorkshopICME: Intl Conf on MMedia & ExpoSoftcomm: Conf on Software in Tcomms and Comp NetworksINET: Internet Society ConfWorkshop on Security and Privacy in E-commerceUn-ranked:PARCO: Parallel ComputingSE: Intl Conf on Systems EngineeringAREA: Programming Languages and Software EngineeringRank 1:POPL: ACM-SIGACT Symp on Principles of Prog LangsPLDI: ACM-SIGPLAN Symp on Prog Lang Design & ImplOOPSLA: OO Prog Systems, Langs and ApplicationsICFP: Intl Conf on Function ProgrammingJICSLP/ICLP/ILPS: (Joint) Intl Conf/Symp on Logic ProgICSE: Intl Conf on Software EngineeringFSE: ACM Conference on the Foundations of Software Engineering (inc: ESEC-FSE when held jointly)FM/FME: Formal Methods, World Congress/EuropeCAV: Computer Aided VerificationRank 2:CP: Intl Conf on Principles & Practice of Constraint ProgTACAS: Tools and Algos for the Const and An of SystemsESOP: European Conf on ProgrammingICCL: IEEE Intl Conf on Computer LanguagesPEPM: Symp on Partial Evalutation and Prog ManipulationSAS: Static Analysis SymposiumRTA: Rewriting Techniques and ApplicationsESEC: European Software Engineering ConfIWSSD: Intl Workshop on S/W Spec & DesignCAiSE: Intl Conf on Advanced Info System EngineeringITC: IEEE Intl Test ConfIWCASE: Intl Workshop on Cumpter-Aided Software EngSSR: ACM SIGSOFT Working Conf on Software ReusabilitySEKE: Intl Conf on S/E and Knowledge EngineeringICSR: IEEE Intl Conf on Software ReuseASE: Automated Software Engineering ConferencePADL: Practical Aspects of Declarative LanguagesISRE: Requirements EngineeringICECCS: IEEE Intl Conf on Eng. of Complex Computer SystemsIEEE Intl Conf on Formal Engineering MethodsIntl Conf on Integrated Formal MethodsFOSSACS: Foundations of Software Science and Comp StructRank 3:FASE: Fund Appr to Soft EngAPSEC: Asia-Pacific S/E ConfPAP/PACT: Practical Aspects of PROLOG/Constraint TechALP: Intl Conf on Algebraic and Logic ProgrammingPLILP: Prog, Lang Implentation & Logic ProgrammingLOPSTR: Intl Workshop on Logic Prog Synthesis & TransfICCC: Intl Conf on Compiler ConstructionCOMPSAC: Intl. Computer S/W and Applications ConfCSM: Conf on Software MaintenanceTAPSOFT: Intl Joint Conf on Theory & Pract of S/W DevWCRE: SIGSOFT Working Conf on Reverse EngineeringAQSDT: Symp on Assessment of Quality S/W Dev ToolsIFIP Intl Conf on Open Distributed ProcessingIntl Conf of Z UsersIFIP Joint Int'l Conference on Formal Description Techniques and Protocol Specification, Testing, And VerificationPSI (Ershov conference)UML: International Conference on the Unified Modeling LanguageUn-ranked:Australian Software Engineering ConferenceIEEE Int. W'shop on Object-oriented Real-time Dependable Sys. (WORDS)IEEE International Symposium on High Assurance Systems EngineeringThe Northern Formal Methods WorkshopsFormal Methods PacificInt. Workshop on Formal Methods for Industrial Critical SystemsJFPLC - International French Speaking Conference on Logic and Constraint ProgrammingL&L - Workshop on Logic and LearningSFP - Scottish Functional Programming WorkshopHASKELL - Haskell WorkshopLCCS - International Workshop on Logic and Complexity in Computer ScienceVLFM - Visual Languages and Formal MethodsNASA LaRC Formal Methods Workshop(1) FATES - A Satellite workshop on Formal Approaches to Testing of Software(1) Workshop On Java For High-Performance Computing(1) DSLSE - Domain-Specific Languages for Software Engineering(1) FTJP - Workshop on Formal Techniques for Java Programs(*) WFLP - International Workshop on Functional and (Constraint) Logic Programming(*) FOOL - International Workshop on Foundations of Object-Oriented Languages(*) SREIS - Symposium on Requirements Engineering for Information Security(*) HLPP - International workshop on High-level parallel programming and applications(*) INAP - International Conference on Applications of Prolog(*) MPOOL - Workshop on Multiparadigm Programming with OO Languages(*) PADO - Symposium on Programs as Data Objects(*) TOOLS: Int'l Conf Technology of Object-Oriented Languages and Systems(*) Australasian Conference on Parallel And Real-Time SystemsAREA: Algorithms and TheoryRank 1:STOC: ACM Symp on Theory of ComputingFOCS: IEEE Symp on Foundations of Computer ScienceCOLT: Computational Learning TheoryLICS: IEEE Symp on Logic in Computer ScienceSCG: ACM Symp on Computational GeometrySODA: ACM/SIAM Symp on Discrete AlgorithmsSPAA: ACM Symp on Parallel Algorithms and ArchitecturesPODC: ACM Symp on Principles of Distributed ComputingISSAC: Intl. Symp on Symbolic and Algebraic ComputationCRYPTO: Advances in CryptologyEUROCRYPT: European Conf on CryptographyRank 2:CONCUR: International Conference on Concurrency TheoryICALP: Intl Colloquium on Automata, Languages and ProgSTACS: Symp on Theoretical Aspects of Computer ScienceCC: IEEE Symp on Computational ComplexityWADS: Workshop on Algorithms and Data StructuresMFCS: Mathematical Foundations of Computer ScienceSWAT: Scandinavian Workshop on Algorithm TheoryESA: European Symp on AlgorithmsIPCO: MPS Conf on integer programming & comb optimization LFCS: Logical Foundations of Computer ScienceALT: Algorithmic Learning TheoryEUROCOLT: European Conf on Learning TheoryWDAG: Workshop on Distributed AlgorithmsISTCS: Israel Symp on Theory of Computing and SystemsISAAC: Intl Symp on Algorithms and ComputationFST&TCS: Foundations of S/W Tech & Theoretical CSLATIN: Intl Symp on Latin American Theoretical InformaticsRECOMB: Annual Intl Conf on Comp Molecular BiologyCADE: Conf on Automated DeductionIEEEIT: IEEE Symposium on Information TheoryAsiacryptRank 3:MEGA: Methods Effectives en Geometrie AlgebriqueASIAN: Asian Computing Science ConfCCCG: Canadian Conf on Computational GeometryFCT: Fundamentals of Computation TheoryWG: Workshop on Graph TheoryCIAC: Italian Conf on Algorithms and ComplexityICCI: Advances in Computing and InformationAWTI: Argentine Workshop on Theoretical InformaticsCATS: The Australian Theory SympCOCOON: Annual Intl Computing and Combinatorics ConfUMC: Unconventional Models of ComputationMCU: Universal Machines and ComputationsGD: Graph DrawingSIROCCO: Structural Info & Communication ComplexityALEX: Algorithms and ExperimentsALG: ENGG Workshop on Algorithm EngineeringLPMA: Intl Workshop on Logic Programming and Multi-Agents EWLR: European Workshop on Learning RobotsCITB: Complexity & info-theoretic approaches to biologyFTP: Intl Workshop on First-Order Theorem Proving (FTP)CSL: Annual Conf on Computer Science Logic (CSL)AAAAECC: Conf On Applied Algebra, Algebraic Algms & ECC DMTCS: Intl Conf on Disc Math and TCSUn-ranked:Information Theory WorkshopAREA: Data BasesRank 1:SIGMOD: ACM SIGMOD Conf on Management of DataPODS: ACM SIGMOD Conf on Principles of DB SystemsVLDB: Very Large Data BasesICDE: Intl Conf on Data EngineeringICDT: Intl Conf on Database TheoryRank 2:SSD: Intl Symp on Large Spatial DatabasesDEXA: Database and Expert System ApplicationsFODO: Intl Conf on Foundation on Data OrganizationEDBT: Extending DB TechnologyDOOD: Deductive and Object-Oriented DatabasesDASFAA: Database Systems for Advanced ApplicationsCIKM: Intl. Conf on Information and Knowledge ManagementSSDBM: Intl Conf on Scientific and Statistical DB MgmtCoopIS - Conference on Cooperative Information SystemsER - Intl Conf on Conceptual Modeling (ER)Rank 3:COMAD: Intl Conf on Management of DataBNCOD: British National Conference on DatabasesADC: Australasian Database ConferenceADBIS: Symposium on Advances in DB and Information SystemsDaWaK - Data Warehousing and Knowledge DiscoveryRIDE WorkshopIFIP-DS: IFIP-DS ConferenceIFIP-DBSEC - IFIP Workshop on Database SecurityNGDB: Intl Symp on Next Generation DB Systems and AppsADTI: Intl Symp on Advanced DB Technologies and IntegrationFEWFDB: Far East Workshop on Future DB SystemsMDM - Int. Conf. on Mobile Data Access/Management (MDA/MDM)ICDM - IEEE International Conference on Data MiningVDB - Visual Database SystemsIDEAS - International Database Engineering and Application SymposiumOthers:ARTDB - Active and Real-Time Database SystemsCODAS: Intl Symp on Cooperative DB Systems for Adv AppsDBPL - Workshop on Database Programming LanguagesEFIS/EFDBS - Engineering Federated Information (Database) SystemsKRDB - Knowledge Representation Meets DatabasesNDB - National Database Conference (China)NLDB - Applications of Natural Language to Data BasesKDDMBD - Knowledge Discovery and Data Mining in Biological Databases Meeting FQAS - Flexible Query-Answering SystemsIDC(W) - International Database Conference (HK CS)RTDB - Workshop on Real-Time DatabasesSBBD: Brazilian Symposium on DatabasesWebDB - International Workshop on the Web and DatabasesWAIM: Interational Conference on Web Age Information Management(1) DASWIS - Data Semantics in Web Information Systems(1) DMDW - Design and Management of Data Warehouses(1) DOLAP - International Workshop on Data Warehousing and OLAP(1) DMKD - Workshop on Research Issues in Data Mining and Knowledge Discovery (1) KDEX - Knowledge and Data Engineering Exchange Workshop(1) NRDM - Workshop on Network-Related Data Management(1) MobiDE - Workshop on Data Engineering for Wireless and Mobile Access(1) MDDS - Mobility in Databases and Distributed Systems(1) MEWS - Mining for Enhanced Web Search(1) TAKMA - Theory and Applications of Knowledge MAnagement(1) WIDM: International Workshop on Web Information and Data Management(1) W2GIS - International Workshop on Web and Wireless Geographical Information Systems * CDB - Constraint Databases and Applications* DTVE - Workshop on Database Technology for Virtual Enterprises* IWDOM - International Workshop on Distributed Object Management* IW-MMDBMS - Int. Workshop on Multi-Media Data Base Management Systems* OODBS - Workshop on Object-Oriented Database Systems* PDIS: Parallel and Distributed Information SystemsAREA: MiscellaneousRank 1:Rank 2:AMIA: American Medical Informatics Annual Fall SymposiumDNA: Meeting on DNA Based ComputersRank 3:MEDINFO: World Congress on Medical InformaticsInternational Conference on Sequences and their ApplicationsECAIM: European Conf on AI in MedicineAPAMI: Asia Pacific Assoc for Medical Informatics ConfSAC: ACM/SIGAPP Symposium on Applied ComputingICSC: Internal Computer Science ConferenceISCIS: Intl Symp on Computer and Information SciencesICSC2: International Computer Symposium ConferenceICCE: Intl Conf on Comps in EduEd-MediaWCC: World Computing CongressPATAT: Practice and Theory of Automated TimetablingNot Encouraged (due to dubious referee process):International Multiconferences in Computer Science -- 14 joint int'l confs.SCI: World Multi confs on systemics, sybernetics and informaticsSSGRR: International conf on Advances in Infrastructure for e-B, e-Edu and e-Science and e-MedicineIASTED conferences以下是期刊:IEEE/ACM TRANSACTIONS期刊系列一般都被公认为领域顶级期刊,所以以下列表在关于IEEE/ACM TRANSACTIONS的分类不一定太准确。

18_Parallel Processing

• Now have multiple processors as well as multiple I/O modules

Symmetric Multiprocessor Organization

Time Share Bus - Advantages

• Simplicity • Flexibility • Reliability

• Performance

—If some work can be done in parallel

• Availability

—Since all processors can perform the same functions, failure of a single processor does not halt the system

• L2 cache 32 MB

— Clusters of five — Each cluster supports eight processors and access to entire main memory space

• System control element (SCE)

— Arbitrates system communication — Maintains cache coherence

Taxonomy of Parallel Processor Architectures

MIMD - Overview

• General purpose processors • Each can process all instructions necessary • Further classified by method of processor communication

Signal and Image Processing

Signal and Image Processing Signal and image processing are two of the most important fields in modern technology. They play a crucial role in a variety of applications, ranging from communication systems and medical imaging to security and surveillance. Signal processing involves the analysis, manipulation, and transformation of signals, which can be in the form of sound, images, or other types of data. Image processing, on the other hand, is focused on the analysis and manipulation ofdigital images, which are composed of pixels or small picture elements. One ofthe key challenges in signal and image processing is dealing with noise and other forms of interference. Noise can be introduced into a signal or image through a variety of sources, such as electromagnetic interference, thermal noise, or quantization errors. To address this challenge, signal and image processing techniques have been developed that can reduce or eliminate noise from a signal or image. For example, filtering techniques can be used to remove noise from a signal, while image enhancement techniques can be used to improve the quality of an image by reducing noise and increasing contrast. Another important aspect of signal and image processing is feature extraction. Feature extraction involves identifyingand isolating specific features or characteristics of a signal or image that are relevant to a particular application. For example, in medical imaging, feature extraction techniques can be used to identify tumors or other abnormalities in an image. In security and surveillance applications, feature extraction techniquescan be used to identify specific individuals or objects in a video stream. Machine learning is also becoming increasingly important in signal and image processing. Machine learning algorithms can be used to automatically learn and adapt to patterns in signals and images, allowing for more efficient and accurate processing. For example, machine learning algorithms can be used to classify different types of signals or images, or to detect anomalies or other unusual patterns. One of the challenges of signal and image processing is the sheer amount of data that is generated. Modern sensors and cameras can produce vast amounts of data, which can be difficult to process and analyze in real-time. To address this challenge, techniques such as compression and data reduction can be used to reduce the amount of data that needs to be processed. Additionally,parallel processing and distributed computing techniques can be used to speed up the processing of large amounts of data. In conclusion, signal and image processing are essential fields in modern technology. They play a critical role in a wide range of applications, from communication systems and medical imaging to security and surveillance. Signal and image processing techniques are constantly evolving, driven by advances in technology and the increasing demand for more efficient and accurate processing. As the amount of data generated by sensors and cameras continues to grow, new techniques will be needed to address the challenges of processing and analyzing this data in real-time.。

香港理工大学高分辨率的指纹(HRF)数据库_图像处理_科研数据集

⾹港理⼯⼤学⾼分辨率的指纹(HRF)数据库_图像处理_科研数据集⾹港理⼯⼤学⾼分辨率的指纹(HRF) 数据库(The Hong Kong Polytechnic University(PolyU)High-Resolution-Fingerprint (HRF)Database)数据介绍:Fingerprint is the most widely used biometric characteristic for personal identification because of its uniqueness and stability over time. Most of the existing automatic fingerprint recognition systems (AFRS) use the minutia features on fingerprints, i.e. the terminations and bifurcations of fingerprint ridges, for recognition. Although they can achieve good recognition accuracy and have been used in many civil applications, their performance still needs much improvement when a large population is involved or a high security level is required. One solution to enhancing the accuracy of AFRS is to employ more features on fingerprints other than only minutiae. Fingerprint additional features, such as pores, dots and incipient ridges (see Fig. 1 for examples), are routinely used by experts in manual latent fingerprint matching. Some of these additional features, e.g. pores, require high resolution fingerprint images to reliably capture them. Thanks to the distinctiveness of these fingerpr关键词:⾼分辨率的指纹,⾹港理⼯⼤学,UGC/CRC,High-Resolution-Fingerprint,PolyU,UGC/CRC,数据格式:IMAGE数据详细介绍:The Hong Kong Polytechnic University (PolyU)High-Resolution-Fingerprint (HRF) DatabaseOverview:Fingerprint is the most widely used biometric characteristic for personal identification because of its uniqueness and stability over time. Most of the existing automatic fingerprint recognition systems (AFRS) use the minutia features on fingerprints, i.e. the terminations and bifurcations of fingerprint ridges, for recognition. Although they can achieve good recognition accuracy and have been used in many civil applications, their performance still needs much improvement when a large population is involved or a high security level is required. One solution to enhancing the accuracy of AFRS is to employ more features on fingerprints other than only minutiae. Fingerprint additional features, such as pores, dots and incipient ridges (see Fig. 1 for examples), are routinely used by experts in manual latent fingerprint matching. Some of these additional features, e.g. pores, require high resolution fingerprint images to reliably capture them. Thanks to the distinctiveness of these fingerprint additional features and to the advent of high quality fingerprint imaging sensors, they have recently attracted increasing attention from researchers and practitioners working on AFRS.Our team in the Biometrics Research Centre (UGC/CRC) of the HongKong Polytechnic University has developed a high resolution fingerprintimaging device and has used it to constructed large-scale high resolutionfingerprint databases (HRF). We intend to publish our database to facilitate researchers designing effective and efficient algorithms for extracting andmatching fingerprint additional features.Fig. 1: Example additional features on fingerprints, pores, dots, and incipientridges.Description of the PolyU HRF Database:An optical fingerprint imaging device (see Fig. 2) has been built by our team.Its resolution is around 1,200dpi, and it can capture fingerprint images ofvarious sizes, e.g. 320*240 pixels and 640*480 pixels.(a) (b)Fig. 2: (a) The high resolution fingerprint imaging device we developed and (b) its inner structure.Two high resolution fingerprint image databases (denoted as DBI and DBII)have been set up by using the developed fingerprint imaging device. DBIconsists of a small training dataset and a large test dataset. The images of thesame finger in both databases were collected in two sessions which wereseparated by about two weeks. Each image is namedas “ID_S_X”.“ID” represents the identity of the person. “S” represents the session of the captured image. “X”represents the image number of each session. The following table gives the detailed information of the databases.We labeled the ground truth of sweat pores in 30 images selected from DBI. The central coordinates (row, col) of each pore were wrote into a text file (.txt). The ground truth of dots and incipients of 48 selected images were also offered. The central coordinates (row, col) of dots and two ends of each incipient were wrote into a text file (.txt). Here, the 48 selected images consists of 2 set of images ("SetIGroundTruthSampleimage" and "SetIIGroundTruthSampleimage") captured in two sessions. All of the original sample images and text files are contained in "Ground Truth.zip".Related Publication:1. Qijun Zhao, David Zhang, Lei Zhang, and Nan Luo, "AdaptiveFingerprint Pore Modeling and Extraction," Pattern Recognition, vol.43(8), pp. 2833-2844, 20102. Qijun Zhao, David Zhang, Lei Zhang, and Nan Luo, "High ResolutionFragmentary Fingerprint Alignment Using Pore-Valley Descriptors,"Pattern Recognition, vol. 43, pp. 1050-1061, 20103. Qijun Zhao, Lei Zhang, David Zhang, Nan Luo, and Jing Bao,“Adaptive Pore Model for Fingerprint Pore Extraction,” IAPR 19thInternational Conference on Pattern Recognition (ICPR2008), 20084. Qijun Zhao, Lei Zhang, David Zhang, and Nan Luo, “Direct PoreMatching for Fingerprint Recognition,” IAPR/IEEE 3rd InternationalConference on Biometrics (ICB2009), pp. 597-606, 20095. David Zhang, Feng Liu, Qijun Zhao, Guangming Lu, and Nan Luo,"Selecting a Reference High Resolution for Fingerprint RecognitionUsing Minutiae and Pores," IEEE Transactions on Instrumentation and Measurement, to appear6. Qijun Zhao, Feng Liu, Lei Zhang, and David Zhang, "A ComparativeStudy on Quality Assessment of High Resolution Fingerprint Images,"Proceedings of the IEEE International Conference on Image Processing (ICIP2010), Hong Kong, September 20107. Qijun Zhao, Feng Liu, Lei Zhang, and David Zhang, "Parallel versusHierarchical Fusion of Extended Fingerprint Features," Proceedings ofthe IAPR 20th International Conference on Pattern Recognition(ICPR'10), Istanbul, Turkey, August 20108. Feng Liu, Qijun Zhao, Lei Zhang, and David Zhang, "Fingerprint PoreMatching based on Sparse Representation," Proceedings of the IAPR20th International Conference on Pattern Recognition(ICPR'10), Istanbul, Turkey, August 20109. Q. Zhao, Lei Zhang, David Zhang, Wenyi Huang, and Jian Bai,“Curvature and Singularity Driven Diffusion for Oriented PatternEnhancement with Singular Points,” CVPR09. Proceedings of IEEEConference on Computer Vision and Pattern Recognition, pp. 1-7,Miami, Florida, USA, June 22-24 2009.The Announcement of the CopyrightAll rights of the PolyU HRF Database are reserved. The database is only available for research and noncommercial purposes. Commercial distribution or any act related to commercial use of this database is strictly prohibited. A clear acknowledgement should be made for any public work based on the PolyU HRF Database. A citation to "PolyU HRF Database, /doc/399f7c6fa45177232f60a2bf.html .hk/~biometrics/HRF/HRF.htm” and our related works must be added in the references. A soft copy of any released or public documents that use the PolyU HRF Database must be forwardedto: cslzhang@/doc/399f7c6fa45177232f60a2bf.html .hkDownloading Steps:Download “HRF DBI.zip”, “HRF DBII.zip”, or "Ground Truth.zip"to your local disk. Then, fill in the application forms. Send the application formto cslzhang@/doc/399f7c6fa45177232f60a2bf.html .hk. The successful applicants will receive the passwords for unzipping the files downloaded.HRF Databases:HRF DBI.zipHRF DBII.zipGround Truth.zipContact Information:Lei ZHANG, Associate ProfessorBiometric Research Centre (UGC/CRC)The Hong Kong Polytechnic UniversityHung Hom, Kowloon, Hong KongE-mail: cslzhang@/doc/399f7c6fa45177232f60a2bf.html .hk数据预览:点此下载完整数据集。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。