嵌入式系统的低功耗设计

应用于低功耗嵌入式处理器的功耗动态管理策略设计

Ab s t r a c t :I n o r d e r t o r e d u c e t h e p o we r c o n s u mp i t o n a n d c o s t o f a n e mb e d d e d a p p  ̄ c a i f o n s y s t e m ,a

Vo 1 . 4 3 No. 4

J u l y 2 0 1 3

d o i : 1 0 . 3 9 6 9 / j . i s s n . 1 0 0 1— 0 5 0 5 . 2 0 1 3 . 0 4 . 0 0 5

应 用 于低 功 耗嵌入 式 处理器 的功 耗动态 管理 策略设计

S u n Da y i n g Xu S h e n Xu Yu mi n Su n We i f e n g Lu S he n g l i

( N a t i o n l a AS I C S y s t e m E n g i n e e r i n g R e s e a r c h C e n t e r ,S o u t h e a s t Un i v e r s i t y ,N a n j i n g 2 1 0 0 9 6, C h i n a )

f u n c i t o n nd a p e r f o r ma nc e r e q u i r e me n t ,t h e o p e r a in t g mo d e s wi t c h nd a he t r e g u l a i t o n of o p e r a in t g f r e — q ue n c y nd a v o l t Байду номын сангаас g e a r e r e a l i z e d t o r e d u c e he t p o we r c o ns umpt i o n a c c o r d i n g t o he t r e q u i r e me n t v a r i a — io t n o f as t k.Th e r a p i d v a r i a b l e vo l ag t e s u p pl y u it n i s a l s o i n t e g r a t e d i nt o he t i c m r o p r o c e s s o r ,whi c h s u p p o ̄s he t i n t e l l i g e nt r e a l — ime t s u p p l y v o l ag t e r e g u l a t i o n nd a r e d u c e s c os t .Th e ma na g e me n t s t r a t e — g y i s t e s t e d by n a e mb e d d e d a pp l i c a i t o n s y s t e m p r o t o t y pe,a nd he t e x er p ime n t a l r e s u l t s s h o w ha t t t h e p o we r c o ns u mpt i o n C n a b e e f f e c iv t e l y r e d u c e d wh e n e x e c ut i ng d i f f e r e n t as t ks .T h e r e f o r e,wh e n he t p o we r dy n a mi c ma na g e me n t s t r a t e g y i s a p pl i e d t o e mb e d d e d a p pl i c a io t n s ys t e ms ,t he p o we r c o n-

嵌入式系统中的低功耗设计策略

嵌入式系统中的低功耗设计策略在嵌入式系统中,低功耗设计一直是一个重要的课题。

随着移动互联网的迅速发展和智能设备的普及,对于嵌入式系统的功耗要求也越来越高。

低功耗设计不仅可以延长嵌入式系统的使用时间,还可以降低系统的发热量,提高系统的稳定性和可靠性。

因此,如何在设计阶段合理降低系统的功耗,成为了设计工程师们必须面对的一个挑战。

首先,在嵌入式系统中实施低功耗设计策略时,可以从硬件设计和软件设计两个方面进行考虑。

在硬件设计方面,采用低功耗的微处理器和低功耗芯片是提高整体系统功耗效率的关键。

选择适合的电源管理芯片并在设计中合理布局供电线路,可以有效减少功耗的消耗。

此外,通过合理设计系统的时钟频率和使用低功耗组件也是低功耗设计的重要手段。

其次,对于软件设计而言,优化软件算法和程序结构是减少系统功耗的有效途径。

在编写程序时,尽量避免频繁的访问外设和传输数据,可以有效减少系统的功耗。

同时,合理控制系统的进程调度和休眠策略,避免程序长时间运行或者在系统空闲时进入休眠模式,也是保证系统低功耗的必备措施。

另外,在嵌入式系统中,尽量利用硬件加速器来减少系统功耗也是一个有效策略。

通过合理设计硬件加速器的功能和使用场景,可以将部分高功耗任务交给硬件加速器来完成,减轻处理器的计算压力,从而降低系统功耗。

此外,采用合适的传输协议和数据压缩技术,也可以有效减少系统在数据传输时的功耗消耗。

最后,为了实时监测系统功耗情况,可以在系统中集成功耗监测模块,随时监控系统各组件的功耗情况。

通过实时监测系统的功耗消耗情况,可以及时发现系统中存在的功耗瓶颈和问题,从而采取相应措施进行优化,保证系统的最佳功耗状态。

综上所述,嵌入式系统中的低功耗设计策略涉及多个方面,包括硬件设计、软件设计、利用硬件加速器、传输协议选择以及功耗监测等各个环节。

只有在全面考虑各个方面的因素并采取相应措施的情况下,才能够确保嵌入式系统在功耗上取得最佳性能,满足用户对于低功耗和高性能的需求。

《嵌入式系统的低功耗与可靠性技术研究》

《嵌入式系统的低功耗与可靠性技术研究》一、引言随着物联网、智能设备以及移动计算技术的快速发展,嵌入式系统作为各种智能设备的核心部分,其低功耗与可靠性问题逐渐成为了重要的研究课题。

在面对能源短缺、环境污染以及设备稳定性要求日益严格的今天,嵌入式系统的低功耗与可靠性技术显得尤为重要。

本文将详细探讨嵌入式系统的低功耗和可靠性技术的研究现状及未来发展趋势。

二、嵌入式系统低功耗技术研究1. 硬件低功耗设计硬件低功耗设计是嵌入式系统低功耗技术的关键。

设计者在硬件设计阶段应考虑采用低功耗芯片、合理的电源管理策略等手段降低系统的整体功耗。

此外,选择合理的元器件及封装方式也能有效降低功耗。

在设计中还可以使用动态电源管理技术,根据系统运行状态调整电源供应,以达到节能目的。

2. 软件优化软件优化是降低嵌入式系统功耗的另一重要手段。

通过优化算法、减少不必要的计算和通信等措施,可以有效降低系统的运行功耗。

此外,合理设计系统任务调度策略,根据任务优先级进行任务分配和调度,也可以实现功耗的降低。

3. 休眠与唤醒机制休眠与唤醒机制是降低嵌入式系统功耗的有效手段。

通过在系统空闲时进入休眠状态,可以有效降低系统的功耗。

当系统需要再次工作时,再从休眠状态唤醒,以恢复工作状态。

这种机制在嵌入式系统中得到了广泛应用。

三、嵌入式系统可靠性技术研究1. 硬件冗余与容错设计硬件冗余与容错设计是提高嵌入式系统可靠性的重要手段。

通过采用冗余硬件和容错技术,可以在系统出现故障时保证系统的正常运行。

例如,采用双机热备、三模冗余等技术,可以提高系统的可靠性和稳定性。

2. 软件容错与恢复技术软件容错与恢复技术是提高嵌入式系统可靠性的另一重要手段。

通过设计容错算法、实现软件故障的自恢复等功能,可以在软件出现故障时及时恢复系统的正常运行。

此外,通过定期更新和修复软件漏洞,也可以提高系统的安全性与稳定性。

3. 系统级可靠性设计系统级可靠性设计是提高嵌入式系统可靠性的综合手段。

嵌入式系统中的低功耗芯片设计与实现

嵌入式系统中的低功耗芯片设计与实现嵌入式系统是一种专门设计用于特定应用领域的计算机系统。

随着技术的不断进步,嵌入式系统正逐渐融入到我们的生活中,如智能手机、汽车电子和智能家居等。

然而,由于嵌入式系统通常需要长时间运行,因此低功耗芯片的设计和实现成为了一个关键的挑战。

本文将介绍嵌入式系统中低功耗芯片的设计原理和实现方法。

一、低功耗芯片设计原理在嵌入式系统中,低功耗芯片设计的原理主要包括以下几个方面:1. 电源管理:合理的电源管理是实现低功耗设计的关键。

通过采用高效的降压转换器来降低芯片电源供电电压,从而降低功耗。

此外,充分利用电源管理技术激活和关闭子系统,灵活控制功耗,也是一种重要的设计方法。

2. 算法优化:对于某些特定的应用场景,通过优化算法可以大大降低芯片的功耗。

例如,对数据进行压缩和加密,通过减少存储和传输数据量来降低功耗。

此外,在软件开发过程中,合理利用休眠模式和节能算法也是降低功耗的重要手段。

3. 架构设计:合理的芯片架构设计有助于降低功耗。

通过采用多核处理器架构,可以将任务分配到不同的核心,实现功耗均衡。

同时,采用适当的Cache技术,减少内存访问次数,也能有效降低功耗。

二、低功耗芯片的实现方法低功耗芯片的实现方法有多种途径,下面分别介绍其中几种常用的方法:1. 优化电路设计:在芯片设计中,通过优化电路设计来降低功耗是一种常见的手段。

通过采用低功耗电路技术,例如提高传输电平的速度、降低开关电流和减小器件尺寸等,可以降低芯片的功耗。

2. 功耗管理单元:在芯片设计中引入功耗管理单元也是一种常用的方法。

功耗管理单元可监控芯片功耗的变化,并根据实际需求动态调整系统的工作状态。

通过灵活地调整系统的电源供应和工作频率,以及启用和关闭子系统,可以实现低功耗设计。

3. 时钟和时钟管理:在嵌入式系统中,时钟是一个重要的组成部分。

通过优化时钟的设计和管理,可以有效降低功耗。

例如,采用动态电压频率缩放(DVFS)技术,根据不同任务的需求调整时钟频率,以及利用时钟门控电路来管理时钟信号的开关等。

嵌入式系统设计中的功耗优化方法

嵌入式系统设计中的功耗优化方法嵌入式系统是一种专用的计算机系统,通常用于特定应用领域。

这类系统通常具有功耗限制,因为它们需要长时间运行,并且通常使用电池供电。

在嵌入式系统设计中,功耗优化是一个关键的考虑因素。

本文将介绍几种常见的功耗优化方法,包括硬件和软件级别的优化。

一、硬件级别的功耗优化方法1. 低功耗处理器选择:选择低功耗处理器是功耗优化的关键步骤之一。

现在市场上有许多专门设计用于嵌入式系统的低功耗处理器。

与传统的桌面处理器相比,这些处理器通常在功耗方面具有更好的表现。

2. 电源管理:合理的电源管理可以显著降低系统的功耗。

一种常见的方法是使用智能电源管理芯片,它可以根据系统的负载情况自动调整电源的供应和电压。

此外,利用睡眠模式等技术也能有效地降低系统的功耗。

3. 优化电路设计:通过优化电路设计,可以降低功耗。

例如,使用低功耗组件、优化时钟频率和电压、减少干扰等。

另外,采用节能设计的存储器和外设也是功耗优化的重要方面。

二、软件级别的功耗优化方法1. 任务调度:合理的任务调度可以降低系统的功耗。

通过动态地调整任务的优先级、任务的执行顺序以及任务的频率等,可以最大程度地减少系统的功耗。

2. 休眠模式:使用休眠模式是一种常见的软件功耗优化方法。

在系统空闲时,将不需要工作的模块或部件设置为休眠状态,以减少功耗。

3. 优化算法:选择合适的算法可以降低系统的计算负载和功耗。

例如,在数据压缩领域,选择更高效的压缩算法可以减少数据传输的功耗。

4. 循环优化:循环在嵌入式系统中通常是性能瓶颈和功耗集中的地方。

通过对循环进行优化,可以减少不必要的计算和数据传输,从而降低功耗。

5. I/O优化:合理地管理输入输出操作可以降低系统的功耗。

例如,通过合并多个I/O操作、使用中断和DMA等技术来降低功耗。

综上所述,嵌入式系统设计中的功耗优化是一个非常重要的问题。

通过在硬件级别和软件级别上进行综合优化,我们可以有效地降低系统的功耗。

嵌入式系统低功耗设计考试

嵌入式系统低功耗设计考试(答案见尾页)一、选择题1. 嵌入式系统低功耗设计的主要目标是:A. 提高处理器速度B. 减少芯片面积C. 降低系统能耗D. 增加程序运行时间2. 在低功耗设计中,通常会考虑哪些硬件组件?A. 内存B. 显示屏C. 传感器D. 打印机3. 以下哪个不是低功耗设计的策略?A. 使用高效能处理器B. 降低工作电压C. 减少不必要的中断D. 使用大容量电池4. 在低功耗设计中,哪种类型的电路最耗电?A. 线性电路B. 逻辑电路C. 微处理器D. 以上都是5. 为了降低功耗,通常会对电路进行哪种处理?A. 混频B. 振荡C. 降压D. 限流6. 在低功耗设计中,哪种技术可以减少电流泄漏?A. 超级结B. FETC. 反相器D. 以上都是7. 低功耗设计中,哪种方法可以提高电源效率?A. 使用开关稳压器B. 使用线性稳压器C. 使用电池D. 使用燃料电池8. 在设计低功耗系统时,以下哪个不是需要考虑的因素?A. 功耗B. 散热C. 信号完整性D. 以上都是9. 低功耗设计中,哪种工具可以帮助评估系统的功耗?A. 示波器B. 逻辑分析仪C. 电源分析仪D. 万用表10. 在实际应用中,如何判断一个嵌入式系统的功耗是否达标?A. 对比同类产品B. 监测实时功耗C. 查看说明书中的功耗数据D. 以上都是11. 嵌入式系统低功耗设计的主要目标是什么?A. 提高处理器的速度B. 减少系统的能耗C. 增加内存容量D. 提高系统的并行处理能力12. 在低功耗设计中,哪种类型的电路通常被认为是低功耗的?A. 晶体管数量较少的电路B. 采用高电压供电的电路C. 使用动态电压和频率调整的电路D. 采用大容量电容的电路13. 在低功耗设计中,通常会考虑哪些因素?A. 功耗、性能和成本B. 功耗、存储器和时间C. 功耗、温度和可靠性D. 功耗、体积和重量14. 低功耗设计中,哪种技术通常用于提高设备的待机或休眠模式下的能源效率?A. 睡眠模式B. 休眠模式C. 深度睡眠模式D. 低功耗模式15. 在嵌入式系统中,哪种设备通常用于降低功耗?A. 显示器B. 键盘C. 网络接口卡D. 扬声器16. 低功耗设计中,哪种类型的电源最适合用于嵌入式系统?A. 开关电源B. 线性电源C. 电池17. 在低功耗设计中,减少系统中的冗余操作可以:A. 提高能效B. 增加成本C. 影响性能D. 减少功耗18. 以下哪个不是低功耗设计中使用的技术?A. 动态电压和频率调整(DVFS)B. 待机或休眠模式的实现C. 硬件循环替换D. 增加处理器的时钟频率19. 在进行低功耗设计时,工程师通常会考虑哪些约束条件?A. 成本、时间和复杂性B. 成本、空间和质量C. 时间、空间和质量D. 成本、时间和质量20. 在低功耗设计中,通常会考虑哪种器件?A. 计算器B. 显示器C. 传感器D. 扬声器21. 以下哪个不是低功耗设计的技术手段?A. 优化代码质量B. 使用高效能处理器C. 降低工作电压D. 增加电池容量22. 在低功耗设计中,通常会采用哪种电路拓扑结构?B. 星型C. 网状型D. 树状型23. 低功耗设计中,哪种类型的存储器具有最低的功耗?A. RAMB. ROMC. FlashD. SRAM24. 在低功耗设计中,通常会如何处理时钟信号?A. 高频时钟信号B. 低频时钟信号C. 可变频率时钟信号D. 锁相环(PLL)时钟信号25. 低功耗设计中,哪种电源管理策略可以有效地降低系统功耗?A. 低压差线性稳压器(LDO)B. 降压变换器C. 电荷泵D. 电压频率转换器(VFC)26. 在低功耗设计中,哪种类型的省电模式通常用于待机或休眠状态?A. 空闲模式B. 省电模式C. 深度睡眠模式D. 休眠模式27. 低功耗设计中,如何通过软件手段进一步降低系统功耗?A. 优化操作系统设置B. 使用低功耗硬件C. 减少中断次数D. 降低采样率28. 在低功耗设计中,哪种技术通常用于提高通信设备的续航能力?A. 加密技术B. 软件无线电技术C. 并行处理技术D. 低功耗算法29. 在嵌入式系统低功耗设计中,通常会考虑以下哪个因素?A. 硬件设备的性能B. 软件算法的效率C. 使用环境的气候条件D. 系统的扩展性30. 以下哪个不是低功耗设计中常用的技术?A. 时钟门控B. 深度睡眠模式C. 动态电压与频率调整(DVFS)D. 硬件加速器31. 在低功耗设计中,通常会优化哪种类型的电路?A. 信号处理电路B. 计算电路C. 电源电路D. 接口电路32. 低功耗设计中,哪种类型的存储器更适用于低功耗场景?A. 随机存取存储器(RAM)B. 只读存储器(ROM)C. 闪存(Flash Memory)D. 电可擦除可编程只读存储器(EEPROM)33. 在低功耗设计中,为了减少能量损耗,通常会对电路进行哪两种优化?A. 动态调度和静态划分B. 动态调整和静态约束C. 动态编译和静态优化D. 动态分配和静态平衡34. 在低功耗设计中,以下哪个不是电源管理模块的功能?A. 电池充电管理B. 电源电压监控C. 功率因数校正D. 电磁兼容性(EMC)控制35. 在低功耗设计中,通常会使用哪种工具进行功耗分析?A. 性能分析仪B. 逻辑分析仪C. 电源分析仪D. 热分析仪36. 在低功耗设计中,为了提高能源利用效率,通常会采用哪种策略?A. 动态电源管理(DPM)B. 静态电源管理C. 动态频率调整D. 静态频率调整37. 在低功耗设计中,为了确保系统在待机状态下也能保持低功耗,通常会采取哪种措施?A. 使用低功耗的处理器B. 关闭未使用的硬件组件C. 降低系统的时钟频率D. 切换到更高的工作电压38. 在低功耗设计中,哪种类型的电路结构通常具有更低的功耗?A. 线性电路B. 非线性电路C. 混合电路D. 以上都不是39. 以下哪个因素不是影响低功耗设计的关键因素?A. 电路设计B. 软件优化C. 硬件选择D. 使用环境40. 在低功耗设计中,通常会采用哪种技术来降低功耗?A. 大规模集成电路B. 微型化C. 低功耗工艺D. 集成电路41. 以下哪种设备在低功耗设计中是不必要的?A. 电池B. 开关电源C. 节能芯片D. 复位电路42. 在低功耗设计中,通常会考虑哪些方面来优化功耗?A. 电源电压和电流B. 功耗和散热C. 信号处理和存储容量D. 以上都是43. 以下哪种方法不是低功耗设计的常用策略?A. 动态电源管理B. 工作频率调整C. 电路级优化D. 手动控制电源44. 在低功耗设计中,哪种类型的器件通常具有更低的功耗?A. 门电路B. 晶体管C. 二极管D. 以上都是45. 以下哪种方法可以帮助在低功耗设计中提高能效比?A. 增加电路复杂性B. 减少电路组件C. 优化电路布局D. 增大电源容量46. 在低功耗设计中,通常会采用哪种技术来减少动态功耗?A. 降低工作电压B. 增加工作频率C. 使用低功耗工艺D. 以上都不是二、问答题1. 什么是低功耗设计?它在嵌入式系统中的作用是什么?2. 在低功耗设计中,常用的电源管理技术有哪些?3. 什么是时钟门控和电源门控?它们如何降低功耗?4. 请简述动态电源管理的实现方式。

嵌入式系统中的功耗分析和优化

嵌入式系统中的功耗分析和优化随着科技的不断发展,嵌入式系统在现代生活中起着越来越重要的作用。

我们在日常生活中用到的许多电子设备,如智能手机、智能家居、智能手表、智能电视等,都是嵌入式系统的典型代表。

然而,随着这些设备的功能越来越强大,功耗问题也愈加引人关注。

本文将探讨嵌入式系统中的功耗分析和优化。

一、嵌入式系统中的功耗问题功耗问题是嵌入式系统设计面临的主要挑战之一。

随着嵌入式系统中集成电路技术的迅速发展,系统的计算能力和性能越来越强大,但功耗问题却越来越严重。

嵌入式系统的功耗问题主要来源于以下几个方面:1.电池容量的限制许多嵌入式设备都是由电池驱动的,因此电池容量的限制成为了制约嵌入式设备功耗的关键因素。

随着设备功能的不断拓展和人们对长时间使用的需求,为了保证设备的续航时间,需限制设备的功耗。

2.高性能的处理器和应用程序现在许多嵌入式设备都含有高性能的处理器,并支持各种繁琐的应用程序。

例如,智能手机中具有多媒体和视频功能的应用程序和游戏等都需要更高的处理能力,这不仅会增加设备的功耗,而且还会导致设备在短时间内电池耗尽。

3.温度、电压和环境噪声等因素在嵌入式系统设计中,电子元件工作的温度也会对设备的功耗产生显著影响。

此外,不同电压下,电子元器件的功耗也有所不同。

在噪声环境中,许多嵌入式系统设计都需要考虑该环境对元器件的影响。

噪声干扰的严重程度可能导致电子元件无法正常工作,这将影响设备的功耗。

二、功耗分析嵌入式设备的功耗分析是发现系统耗电量的过程,也是构建可降低功耗的系统的关键。

对于功耗分析,通常分为以下两类:1.软件功耗分析软件功耗分析是对软件程序的功耗分析过程。

软件系统通常包括控制逻辑和计算逻辑。

在软件系统中,程序中的每个模块都会消耗功耗。

因此在嵌入式系统中,所使用的软件及其算法决定了系统的功耗消耗。

软件功耗分析的目的是减少功耗。

它需要对软件程序进行全面的分析,考虑从算法、模块、数据结构和电源管理策略方面入手,以实现功耗最小化目标。

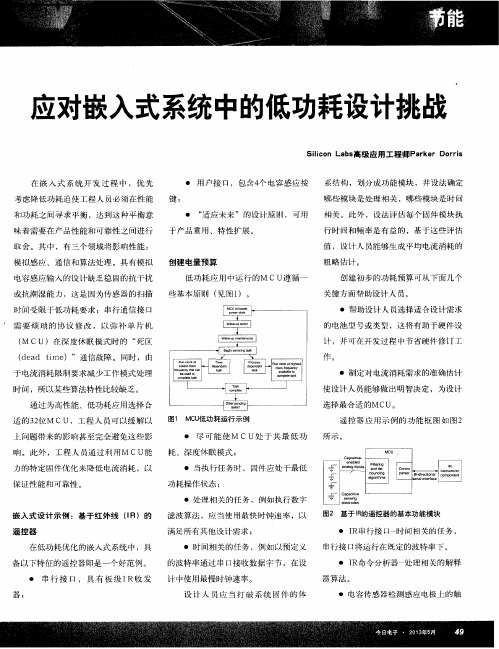

应对嵌入式系统中的低功耗设计挑战

块 可以 在不到 5 0 m s 内执 行 l 6 位 转换 。

感应 固件 模块 不 需 要 为 判 别 用 户是 否 按 键 而 持 续 执 行 转 换 。相 反 ,固件 能够 利 用 M C U片 上 实 时 时 钟 特 性 周 期 从 深 度

作。

时 间受 限 于 低 功 耗 要 求 ; 串行 通 信 接 口 ‘ 需 要 烦 琐 的 协 议 修 改 ,以 弥 补 单 片 机 ( M CU )在 深 度休 眠 模 式 时 的 “ 死 区

( d e a d t i me )”通信 故障 。同时 ,由

于 电流 消 耗 限 制要 求 减 少 工 作 模 式 处 理

・ 制 定 对 电流 消 耗 需 求 的准 确估 计

时间 ,所以某些算法特性比较缺乏 。

通 过 为 高性 能 、低 功 耗 应 用 选 择 合 适的3 2 位 M C U,工 程 人 员可 以 缓 解 以 上 问 题 带 来 的 影 响 甚 至 完 全 避 免 这 些 影 响 。 此 外 ,工 程 人 员通 过 利 用 M C U能 力 的 特 定 固件 优 化 来 降低 电 流 消 耗 ,以 保 证性 能 和 可 靠 性 。

键 ;

系结 构 ,划 分 成 功 能 模 块 ,并 设 法 确 定 哪 些 模 块 是 处 理 相 关 ,哪 些 模 块 是 时 间 相 关 。此 外 ,设 法 评 估 每 个 固 件 模 块 执 行 时 间和 频 率 是 有 益 的 ,基 于 这 些 评 估 值 ,设 计 人 员能 够 生 成 平 均 电 流 消 耗 的

应对嵌入式系统中的低功耗设计挑战

S i l i c o n L a b s 高 级应 用 工 程 I J i  ̄ P a r k e r Do r r i s 在 嵌 入 式 系 统 开 发 过 程 中 ,优 先 考 虑 降 低 功 耗 迫 使 工 程 人 员必 须 在 性 能 ・ 用 户接 V I ,包 含 4 个 电容感应按

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第27卷第6期增刊 2006年6月仪 器 仪 表 学 报Chinese Journal of Scientific InstrumentVol.27No.6J une.2006 嵌入式系统的低功耗设计3杨天池 金 梁 王天鹏(解放军信息工程大学 郑州 450002)摘 要 嵌入式系统的电源管理是系统设计中关键部分,合理的电源管理方案可以减少系统的功耗并提高整体性能。

本文提出了一种层次化的电源管理结构,分别为硬件层、驱动层、操作系统层、电源管理层和应用层。

本文同时引入了动态的电源管理方法来解决电源功耗的动态管理问题。

通过在实际的系统中的测试表明,该电源管理机制的有效性。

关键词 嵌入式系统 低功耗设计 动态电源管理 PXA255Low pow er design in embedded systemYang Tianchi Jin Liang Wang Tianpeng(Universit y of I nf ormation Engineering ,Zhengz hou 450002,China )Abstract Proper power management mechanism is important when designing embedded system.It is helpful to reduce power consumption and improve performance.This low power model adopt s five 2layer architecture ,which are hardware platform ,driver layer ,operating system ,power manage mechanism and application program.Dynamic power management (DPM )technology is also introduced to solve the problem of power consumption.The experiment on embedded system demonstrates t hat this power management mechanism is feasible.K ey w ords embedded system low power design dynamic power management PXA255 3基金项目:河南人才创新基金(0421000100)1 引 言随着嵌入式系统的发展以及应用面的不断扩展,功耗控制是系统设计中必不可少的组成部分。

如何最大限度的降低系统功耗、减少不必要的能源损失、延长电池使用时间已经成为嵌入式系统特别是便携式系统设计中研究的热点问题。

系统的低功耗设计,并非是某一方面、某一角度的解决方案,而应当从系统级的设计考虑功耗的节省,是一个硬件设计与软件控制相互结合的协调过程。

2 低功耗电路模型低功耗设计对于无线设备、PDA 等便携式设备的实际应用具有重要的意义。

低功耗元件的发展和系统设计的进步使得通用计算技术可以用到表、无线电话、PDA 和桌面计算机中。

在这些系统中的电源管理技术传统上集中在休眠模式和设备能源管理这2个方面上[1]。

但是,这样的电源管理缺乏直观性和灵活性,而且功耗的降低,并非单独软件、硬件单方面可以解决的[2],因此设计并建立如图1所示的系统低功耗设计模型。

整个模型由硬件平台,驱动层,操作系统层,电源管理机制层和应用程序五个部分组成。

2.1 硬件平台几乎所有系统功耗都集中于硬件平台,因此降低硬件平台的功耗是实现低功耗的基本所在。

公式(1)为系统功耗的表达式:P ∞CV 2f(1)式中:C 是负载电容,V 是器件电压,f 是工作频率[3]。

系统功耗同负载电容、器件电压平方以及工作频率成正比。

因此,硬件平台设计多选用低电压,电压、频率可调器件,以及采用SOC 设计来进一步降低功耗[4,5]。

另外,模式可控器件在空闲状态消耗的能量为运行状 第6期增刊嵌入式系统的低功耗设计947态的千分之一甚至更小,能动态改变外围电路工作状态也是低功耗系统设计的要求之一。

2.2 驱动层驱动层提供硬件平台和操作系统之间的衔接和通信。

传统的驱动层一般并未包含有电源的动态管理(DPM)功能。

对功耗敏感的应用设计之中具有DPM功能的驱动则是必不可少的了。

DPM对外围设备可允许的工作状态进行定义,对电压、频率可调设备的压/频级别进行明确的划分,接受操作系统的模式转换命令,对外设进行操作,实现硬件状态的切换。

例如MAX3232即在DPM中记录了运行和休眠两种模式,并由其完成此两种模式间的转换[6]。

2.3 操作系统层与传统的层次结构相比,本文涉及的操作系统层的概念没有本质性的改变,仍然负责实现获取外设状态信息,并将信息转换为对驱动层的命令并传达的功能。

2.4 电源管理机制层电源管理机制层(PMM)是动态电源管理的核心所在,也是本文所要讨论的重点。

电源管理机制层是位于操作系统内核以外的软件抽象层,全权负责整个系统的电源状态切换。

为了实现对整个系统功耗的管理,每个功耗可控设备在启用之前,必须注册到PMM,统一由PMM层管理。

所有注册的设备在PMM层维持一个链表,用于记录设备的工作模式、状态等信息,如图2所示。

出于对应用软件兼容性以及电源管理的有效性和灵活性的考虑,可将PMM的管理模式配置为SMAR T模式以及APPL ICA TION模式。

在SMART模式,PMM对功耗的管理完全不需要应用程序的介入和参与,PMM根据task的状态来智能切换外设工作模式,动态改变电压、频率等,因此采用此钟模式可以不必对应用程序做任何修改,保持了应用程序向前的兼容性。

如图3所示,SMART模式下,任务的状态不断在sleeping,running,ready和suspend之间转换,通过获取当前任务的各种状态,来动态调整外设的电压、频率以及工作状态。

但是SMART模式的功耗控制比较简单,属于面向任务级的功耗控制,灵活性较差,而且对功耗的控制能力有限。

在APPL ICA TION模式下,PMM对功耗的管理则必须由应用程序来控制。

PMM层提供对应用程序的API函数接口,直接调用DMP层相应的模式或压/频级别的转换函数实现功率控制,因此应用程序可以灵活、自由的控制外围设备的运行状态,动态改变外围设备的电压、工作频率。

APPL ICA TION属于面向设备的功耗控制,其灵活性和有效性极高。

功耗统计功能。

对于手持、移动等这类功耗敏感应用设备,研发阶段必须对系统的功耗进行测试,因此功耗统计功能则变得十分重要。

如图2所示,在PMM 层实现power consumption statistic(PCS)功能,用于统计设备以及整个系统的功耗。

每次外设工作状态或者压/频级别改变时,PCS获取当前的系统时间以及该设备的工作状态并以文件方式记录下来。

事后将该文件上传到PC机,统计出指定外设或者整个系统的功948 仪 器 仪 表 学 报第27卷 率消耗情况。

由于PCS需占用较多的存储资源,且只在初期调试阶段有意义,因此PCS功能的支持为可选,发布的产品中一般不包含PCS功能。

对Cache的支持。

Cache属于较为特殊的外设。

Cache一般固化在CPU内部,可以用作程序和数据存储器。

但是与普通外部存储设备不同之处是,其工作电压低于外部存储设备一半或者更低,而其负载电容一般是外部存储设备负载电容的1/1000,由公式(1),相同的程序分别在cache中和外围设备中运行,其功率的消耗比为1∶4000。

由此可见,cache的使用对降低系统功耗将具有极大的作用。

但是cache的使用存在命中的问题,因此实际使用中功耗的改善程度要低于上述的计算值。

在PMM层将系统中被频繁调用的函数常驻于cache中(如taskSchedule(),sys Timer()等),cache内容的替换则采用Random replacement或Round robin replacement算法,来提高cache的命中率。

2.5 应用程序应用程序设计可以调用PMM层提供的API函数接口,灵活的控制外设的状态以及压/频级别来降低功率的消耗。

3 结 论本论文提出的低功耗设计模型,在PXA255处理器上进行了验证,采用A TI公司的nucleus嵌入式操作系统,测试结果如表1所示。

表1 系统功耗列表Device Normal mode Low power modeCPU288mW77mWLCD342mW almost0FLASH33mW401μWCF card248mW almost0SERIAL POR T6mW3μW USB host165mW502μW图4为采用PCS后,对串行口工作状态变化的统计图。

所有功能模块同时工作在运行模式,功耗大约为1093mW,而采用PMM层管理策略之后,系统平均功耗为150mw,而idle模式系统功耗仅为69mw由此可见,采用低功耗模型的设计方式极大的降低了系统的总功耗,使得电源的使用得到了控制,从而能源利用更加有效。

参考文献[1] L.Benini,A.Bogliolo,G. D.Micheli.A Survey ofDesign Techniques for System2Level Dynamic PowerManagement[J].IEEE Transactions on Very LargeScale Integration Systems,2000,10(2):2992316. [2] CO.IBM.Dynamic Power Managementfor EmbeddedSystems[G].2002.[3] K.Nowka.A322bit Power PC Syetem2on2a2Chip withSupport for Dynamic Voltage Scaling and DynamicFrequency Scaling[J].IEEE Journal of Solid2StateCircuits,2002,37(11):144121447.[4] T.Lindkvist,J.Lofvenberg,O.Gustaf son.DeepSub2Micron Bus Invert Coding[G].Dept.of EE,Linkopings Universitet,Sweden.[5] J.Pouwelse,ngendoen,H.Sips.Application2directed voltage scaling[J].IEEE Transactions onVery Large Scale Integration Systems,2003.[6] CO.MAXIM.1μA Supply2Current,True+3V to+515V RS2232Transceivers with Auto Shutdown[G].2003.。