第三章 Verilog HDL语言要素

Verilog HDL介绍

关于时延(续)

时间单位通过编译指令与物理时间相关联 ‘timescale 1ns/100ps ; 即:时延时间单位为1ns,时间精度为 100ps 时间精度 #5.21 // 对应5.2ns

#6.17

// 对应6.2ns

Verilog主要描述方式

数据流描述方式 行为描述方式

结构化描述方式

数据流描述方式

• VHDL “Tell me how your circuit should behave and I will give you the hardware that does the job.” • Verilog HDL Similar to VHDL • ABEL-HDL、AHDL(Altera HDL) “Tell me what hardware you want and I will give it to you” •硬件C语言:SystemC、Handle-C

Verilog 与VHDL的比较(续)

• Verilog HDL的编程风格比VHDL更加简 洁明了、高效便捷。如果单纯从描述结构上 考察,两者的代码之比约为1:3。

• Verilog HDL也于1995年实现了标准化 (IEEE-1364)。目前市场上所有的 EDA 工具都支持这两种语言。而在ASIC 设计领 域,Verilog HDL占有明显优势。

Verilog的基本描述单位

module module_name (port_list);

port declarations data type declarations circuit functionality endmodule

注意:所有的关键字都小写。

【例1】半加器的module

module HalfAdder ( A, B, sum, carry); inputA, B ; outputsum, carry ; assign #2 sum = A ^ B ; assign #5 carry = A & B ;

数字设计中的Verilog HDL语言基础

数字设计中的Verilog HDL语言基础Verilog HDL语言是数字设计中非常重要的一门编程语言,它被广泛应用于集成电路设计和硬件描述语言。

在数字设计中,Verilog HDL语言被用来描述硬件的行为和结构,使得工程师能够通过编写代码来设计和实现各种数字电路。

Verilog HDL语言具有如下几个基础要素:1. 模块(Module):Verilog HDL语言中的最基本构建单元就是模块,一个模块可以包含端口、输入、输出、内部信号和行为描述等部分。

模块用来描述数字电路中的一个功能模块或组件,它是实现数字电路的基础。

2. 信号(Signal):信号是Verilog HDL语言中用来传递信息的基本元素,它可以是输入信号、输出信号或者中间信号。

信号可以是数字类型、整数类型、浮点数类型等,通过信号的传输和逻辑操作来描述整个数字电路的行为。

3. 端口(Port):端口是模块与外部环境进行通信的接口,它可以是输入端口、输出端口或者双向端口。

端口定义了模块和其他模块或顶层模块之间的信号传输规则,是数字电路的输入输出通道。

4. 运算符(Operator):Verilog HDL语言中包含了各种运算符,用来对信号进行逻辑运算、算术运算和比较运算等操作。

常见的运算符包括与(&)、或(|)、非(!)、加(+)、减(-)、乘(*)、除(/)、取余(%)等,通过运算符的使用能够实现数字电路中的各种功能。

5. 时钟(Clock):时钟信号在数字设计中起到非常重要的作用,它用来同步数字电路中的各个组件,确保它们按照时序进行正确的操作。

时钟信号通常是周期性的信号,在数字电路中广泛用于触发、同步和控制各个模块的工作。

通过学习Verilog HDL语言的基础知识,可以帮助我们更好地理解数字设计中的原理和技术,进而能够设计和实现各种复杂的数字电路。

掌握Verilog HDL语言的基础概念和语法规则,是每一位数字设计工程师必备的技能之一。

第三章 Verilog HDL的基本语法汇总

512个单元,每个单元为32位

3.3 Verilog HDL的运算符

算术运算符 逻辑运算符 关系运算符 等值运算符 位运算符 缩减运算符 移位运算符 条件运算符 拼接运算符

1.算术运算符

算术运算符包括: + (加法运算符或正值运算符,如x+y,+8) - (减法运算符或负值运算符,如x-y,-90) * (乘法运算符,如x*y) / (除法运算符,如x/y) % (取模运算符,如x % y)

1.间隔符: Verilog 的间隔符主要起分隔文本的作用,可以使 文本错落有致,便于阅读与修改。

间隔符包括空格符(\b)、TAB 键(\t)、换行符(\n)及 换页符。

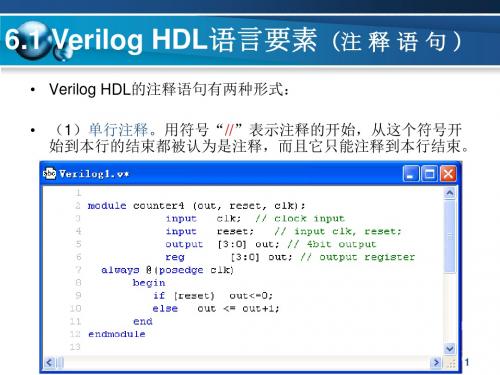

2.注释符:注释只是为了改善程序的可读性,在编译时不起作用。 多行注释符(用于写多行注释): /* --- */; 单行注释符 :以//开始到行尾结束为注释文字。

3.标识符和关键词

标识符:给对象(如模块名、电路的输入与输出端口、变

量等)取名所用的字符串。以英文字母或下划线开始

如,clk、counter8、_net、bus_A 。

关键词:是Verilog语言本身规定的特殊字符串,用来定义 语言的结构。例如,module、endmodule、input、 output、wire、reg、and等都是关键词。关键词都是小 写,关键词不能作为标识符使用 。出始终根据输入的变化而 更新其值的变量,它一般指的是硬件电路中的各种物理 连接.

例:网络型变量L的值由与门的驱动信号 a和b所决定,即L=a&b。a、b的值发 生变化,线网L的值会立即跟着变化。

a

&L

chVerilogHDL语法与要素

3

数据类型与表达式

• Verilog HDL提供了丰富的数据类型,本章把Verilog HDL的数据分为常量和变量两类,并分别介绍其特点和使 用方法。 • 表达式是操作符、操作数和标点符号序列,其目的是用来 说明一个计算过程。程序中的大部分语句是由表达式构成 的,因此表达式是Verilog HDL的重要部分。

12

(3) 字符串型常量

• 字符串常量是由一对双引号括起来的字符序列。出现在双 引号内的任何字符(包括空格和下划线)都将被作为字符 串的一部分。如下例: • "INTERNAL ERROR“ • " R E A C H E D- > H E R E " 所以是字符串的组成部分 • "12345_6789_0" 以是字符串的组成部分 //空格出现在双引号内,

6.1 Verilog HDL语言要素(注 释 语 句 )

• Verilog HDL的注释语句有两种形式: • (1)单行注释。用符号“//”表示注释的开始,从这个符号开 始到本行的结束都被认为是注释,而且它只能注释到本行结束。

1

注释语句

• (2)多行注释。以起始符“/*”开始,到终止符“*/”结束, 可以跨越多行,在一对起始符与终止符之间的所有内容都被认 为是注释。

10

(2) 实数型常量

• 在Verilog HDL中,实数就是浮点数,实数的定义方式有 两种:

• (1)十进制格式,由数字和小数点组成(必须有小数 点),例如: • 2.0 • 5.678 • 11572.12 • 0.1 • 2. // 非法:小数点右侧必须有数字

11

• 2)指数格式,由数字和字符e(E)组成,e(E)的前面 必须要有数字而且后面必须为整数, • • • • 例如: 23_5.1e2 //其值为23510.0,忽略下划线 3.6E2 //其值为360.0 ( e与E相同) 5E-4 //其值为0.0005

VerilogHDL入门教程

VerilogHDL入门教程第一部分:Verilog HDL概述(约200字)Verilog HDL是一种硬件描述语言,用于描述和建模数字电路和系统。

它是一种被广泛使用的硬件设计语言,特别适合用于逻辑设计和验证。

Verilog HDL提供了一种形式化的方式来表示数字电路和系统的行为和结构,使得工程师可以更轻松地进行硬件设计和验证。

第二部分:Verilog HDL基础(约400字)在Verilog HDL中,最基本的组成单元是模块。

模块是Verilog HDL中的一个独立的、可重用的单元,可以由其他模块实例化和连接。

每个模块由端口(输入和输出)和内部功能(如逻辑代码和信号声明)组成。

module and_gate(input a, input b, output y);assign y = a & b;endmodule这个模块表示一个与门,它有两个输入a和b,一个输出y。

使用assign语句,我们将输出y连接到输入a和b的逻辑与操作。

第三部分:Verilog HDL高级特性(约400字)除了基本的模块和连接之外,Verilog HDL还提供了一些高级特性,用于更复杂的电路建模和验证。

一种特殊的构造是always块。

always块用于描述模块内的行为,基于一个条件或时钟信号的变化。

例如,下面是一个使用always块的模块示例:module counter(input clk, input enable, output reg count);if (enable)count = count + 1;endendmodule这个模块表示一个简单的计数器,在时钟上升沿时根据enable信号增加计数器的值。

Verilog HDL还支持层次化的建模,允许将模块层次化地组织起来,以便更好地管理和复用代码。

层次化建模通过使用模块的层次命名和连接来实现。

例如,我们可以将上面的计数器模块实例化为另一个模块,如下所示:module top_module(input clk, input enable, output reg count);countercounter_inst(.clk(clk), .enable(enable), .count(count));endmodule这个模块实例化了上面定义的计数器模块,并将其内部信号和端口连接到外部接口。

Verilog HDL基础知识

tri tri0 tri1 triand trior trireg unsigned vectored wait wand weak0 weak1 while wire wor xnor xor

第3章 Verilog HDL基础知识

3.2 数 据 类 型

Verilog HDL支持两种形式的注释符:/*……*/与//。其中, /*……*/为多行注释符,用于对多行语句注释;//为单行注释符, 只对注释符所在的行有效。下面是一个使用注释符对1位加法器 进行说明的例子。

第3章 Verilog HDL基础知识

【例3-2】注释符的例子。

/* 该例利用一位加法器来说明单行注释符与多行注释符的

第3章 Verilog HDL基础知识

1. 字符串变量的声明 Verilog HDL中采用寄存器变量来存储字符串,寄存器变量的 位数要大于字符串的最大长度。需要注意的是,Verilog HDL中并 不需要特殊位来存储终止符。 【例3-6】字符串变量的声明。

reg [8*12:1] stringvar; initial

'<base_format><number> 符号“'”为基数格式表示的固有字符,该字符不能省略,否 则为非法表示形式;参数<base_format>用于说明数值采用的进制 格式;参数<number>为相应进制格式下的一串数字。这种格式未 指定位宽,其缺省值至少为32位。

第3章 Verilog HDL基础知识

第3章 Verilog HDL基础知识

module addbit (a,b,ci,sum,co);

input

Verilog的基本语言要素

–

科学表示法表示方式:

<尾数><e或E><指数>, 表示: 尾数×10指数

6.3 32e- 4 4.1E3

decimal notation scientific notation for 0.0032 scientific notation for 4100

.12 9. .2e-7

系统任务及函数

$<标识符> • $符号指示这是系统任务和函数 • 系统函数有很多:

编译指令(Compiler Directives)

• 宏编译指令 • 条件编译指令 • 文件包含编译指令 • 时间标度编译指令

宏编译指令- `define、 `undef

宏编译指令`define提供了一种简单的文本替换(substitution)的功能 `define <macro_name> <macro_text>

数值前面加‘+’和‘-’表示数的正负

•

指定位宽的基数格式

<size><’base><value> 其中 size :指定数的二进制位宽的大小。由十进制数表示。缺省为32位。 ’ base:数基,可为2(b)、8(o)、10(d)、16(h)进制。缺省为10进制 ’b ’o ’d ’h ’sb ’so ’sd ’sh

编译指令(Compiler Directives)

• ( `)符号标识一个编译指令 • 编译指令句末不加; • 这些编译指导使仿真编译器进行一些特殊的操作 • 编译指令对所有被编译的文件都有效,一直保持有效 直到被覆盖或解除,或整个编译结束。 • `resetall 复位所有的编译指令为缺省值,应该在其它 编译指令之前使用

第三讲verilogHDL语法入门

Verilog语法说明

有符号整数表示方法 负数取补码 如:-7’d30 8’sb1000_0001=-8’b0111_1111

位数’基数表示的数默认为无符号数, 符号说明s,表示认为有符号数,最高位为符号位; 10进描述,默认有符号数,;

• 实数和字符串

实数综合时被短截,常用于仿真,可用十进制 表示或用科学浮点数表示, 如:32e-4 (表示0.0032) 4.1E3( 表示 4100) • 字符串用引号“….”每个字符采用8bitASCII

Verilog 基本语法-条件、循环语句

1 if---else---2 if ---else if----…… else---3 case(signals)

cond1:--cond2:--…… default:--endcase

1

casex,casez 可综合

forever begin -----end 2 repeat (n) -----3 while (condition) -----4 for(---,---,---) begin -----end

1.组合逻辑块 module au(a, b, s,d); input [7:0]a,b; output [8:0] s,d; wire[7:0] a,b;//可省略 wire[8:0] sum; ;//可省略 assign s=a+b; assign d=a-b endmodule

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

芜湖职业技术学院

2. 寄存器型

寄存器型变量对应的是具有状态保持作用的电路元件, 如触发器、寄存器等。register型变量与net型变量的根本 区 别 在 于 : register 型 变 量 需 要 被 明 确 地 赋 值 , 并 且 register型变量在被重新赋值前一直保持原值。在设计中必 须将寄存器型变量放在过程语句(initial、always)中,通过 过程赋值语句赋值。注:在initial、always等过程块内,被 赋值的每一个信号都必须定义成寄存器型。 Verilog HDL 有4种寄存器型变量,见表:

1.空白符和注释 空白符和注释

空白符 代码中, 在Verilog HDL代码中,空白符包括空格、tab、换行 代码中 空白符包括空格、 、 和换页。空白符使代码错落有致,阅读起来方便。 和换页。空白符使代码错落有致,阅读起来方便。在综合 空白符被忽略。 时,空白符被忽略。 Verilog程序可以不分行,也可以加入空白符采用多行 程序可以不分行, 程序可以不分行 编写。例如: 编写。例如: initial begin ina =3’b001; inb= 3’b011; end 这段程序等同于下面的书写格式: 这段程序等同于下面的书写格式:

类型 wire、tri 、 wor、trior 、 wand、triand 、 tri1、tri0 、 supply1、supply0 、 功能说明 连线类型 具有线或特性的连线 具有线与特性的连线 分别为上拉电阻和下 拉电阻 分别为电源(逻辑 和 分别为电源 逻辑1)和 逻辑 逻辑0) 地(逻辑 ) √ 可综合说明 √

宽度为多位的reg类型变量的定义格式如下: reg[n-1:0] 数据名1,数据名2,……,数据名n; reg[7:0] qout // qout的宽度为8位

芜湖职业技术学院

3. parameter

在Verilog HDL中,用paramter来定义符号常量,即用 parameter来定义一个标志符代表一个常量。其定义 格式为: parameter sel=8, code=8’ha3; 分别定义参数sel代表常量8(10进制),参数code 代表常量a3(16进制); 还可以定义为: parameter datawidth=8, addrwidth=datawidth*2; 定义参数datawidth代表常数8,参数addrwidth代 表16(8*2);

芜湖职业技术学院

整数

基数表示形式整数的例子: 基数表示形式整数的例子: 5'O37 5位八进制数(二进制 位八进制数( 位八进制数 二进制11111) ) 4'D2 4位十进制数(二进制 位十进制数( 位十进制数 二进制0011) ) 4'B1x_01 4位二进制数 位二进制数 7'Hx 7位x(扩展的 ,即xxxxxxx 扩展的x), 位 扩展的 4'hZ 4位z(扩展的 ,即zzzz 扩展的z), 位 扩展的 4'd-4 非法: 非法:数值不能为负 8‘h 2A 在位长和字符之间,以及基数和数值 在位长和字符之间, 之间允许出现空格 3' b001 非法: 和基数 和基数b之间不允许出现空格 非法:`和基数 之间不允许出现空格 (2+3)'b10 非法:位长不能够为表达式 非法:

芜湖职业技术学院

3.2 数据类型

在硬件描述语言当中,数据类型是用来表示 数字电路中的物理连线,数据存储和传送等物理 量。 Verilog语言中的数据类型很多,最基本的的主 要有两类:一类称为连线型,另一类称为寄存器 型。在这两类中,最常用的是:wire型、reg型、 integer型和parameter型4种数据类型。本节着重 介绍wire型、reg型和parameter型数据类型的使用。

例

Count COUNT R56_68 FIVE$ 30不同

//非法 标识符不允许以数字开头 非法:标识符不允许以数字开头 非法 //非法,标识符中不允许包含字符 非法, 非法 标识符中不允许包含字符*

芜湖职业技术学院

4.关键字 关键字 Verilog语言内部已经使用的词称为关键字或 语言内部已经使用的词称为关键字或 保留字,这些关键字用户不能随便使用。 保留字,这些关键字用户不能随便使用。

Verilog HDL定义的 定义的 一些常用的 关键词

需要注意的是, 所有关键字都是小写的, 例如, 需要注意的是 , 所有关键字都是小写的 , 例如 , ALWAYS(标识符 不是关键字 , 它与 标识符)不是关键字 关键字)是 标识符 不是关键字,它与always(关键字 是 关键字 不同的。 不同的。

always edge endspecify if module and else endtable initial negedge assign end endtas k inout nor begin endcas e event input not case endmodul e for integer or default endfuncti on forever fork join output disable endprimiti ve function large

芜湖职业技术学院 Verilog HDL中有 种类型的常量 中有3种类型的常量 中有 种类型的常量: 整数; 实数; 字符串。

下划线符号( 可以随意用在整数或实数中, 下划线符号( _ )可以随意用在整数或实数中,它 们就数量本身没有意义,可用来提高易读性, 们就数量本身没有意义,可用来提高易读性,唯一的限 制是下划线符号不能用做首字符。 制是下划线符号不能用做首字符。

芜湖职业技术学院

2. 数字与字符串

Verilog HDL有下面 种基本逻辑状态 有下面4种基本逻辑状态 有下面 种基本逻辑状态: 0:低电平、逻辑0或逻辑非; 1:高电平、逻辑1或“真”; x或X:不确定或未知的逻辑状态; z或Z:高阻态。 注意,这四种值的解释都内置于语言中。如一个为 的值 注意,这四种值的解释都内置于语言中。如一个为z的值 总是意味着高阻抗,一个为0 的值通常是指逻辑0; 总是意味着高阻抗,一个为 的值通常是指逻辑 ;在门 的输入或一个表达式中为“ 的值通常解释成 的值通常解释成“ 。 的输入或一个表达式中为“z”的值通常解释成“x ”。此 值和z值都是不分大小写的 外,x值和 值都是不分大小写的,也就是说,值0x1z与值 值和 值都是不分大小写的,也就是说, 与值 0X1Z相同。 相同。 相同

芜湖职业技术学院

3.标识符 标识符

Verilog HDL中的标识符可以是任意一组字母、数字、 中的标识符可以是任意一组字母、 中的标识符可以是任意一组字母 数字、 $符号和 下划线 符号的组合,但标识符的第一个字符必 符号和_(下划线 符号的组合, 符号和 下划线)符号的组合 须是字母或者下划线。另外,标识符是区分大小写的。 须是字母或者下划线。另外,标识符是区分大小写的。

芜湖职业技术学院

3.1 词 法

词法概念: 程序是由各种符号流构成的, 词法概念: Verilog HDL程序是由各种符号流构成的,这 程序是由各种符号流构成的 些符号包括空白符、操作符、数字、字符串、注释、 些符号包括空白符、操作符、数字、字符串、注释、标识 符和关键字等,我们将其称为词法。 符和关键字等,我们将其称为词法。

类型 reg integer real time 功能说明 常用的寄存器型变量 32位带符号整型变量 位带符号整型变量 64位带符号实型变量 位带符号实型变量 无符号时间变量 √ √ 可综合性说明

芜湖职业技术学院 integer、real和time三种寄存器型变量都是纯数学的抽 象描述,不对应任何具体的硬件电路。reg型变量是最常用 的一种寄存器型变量。 reg型 型 宽度为1位的reg类型变量的定义格式如下: reg 数据名1,数据名2,……,数据名n; 例如:reg a,b; //定义了两个reg型变量a和b

芜湖职业技术学院

第3章 Verilog HDL语言要素 章 语言要素

词法 数据类型 寄存器和存储器 运算符

芜湖职业技术学院

本章概述

本章介绍Verilog语言的基本要素,包括数字、字符 串、标识符、运算符、数据类型和保留字等,这些语言 要素既有与软件编程语言(如C语言)相同和相似之处,也 有Verilog HDL作为一种硬件描述语言所特有的地方。比 如:Verilog语言的运算符与C语言的很相像,而数据类 型(wire、reg等)则是Verilog HDL所特有的。必须深入理 解硬件描述语言与软件编程语言的本质区别。

芜湖职业技术学院

字符串

字符串是双引号内的字符序列, 字符串是双引号内的字符序列,字符串不能分成 多行书写。 多行书写。 字符串中的特殊字符必须用字符“ 来说明 比如: 来说明, 字符串中的特殊字符必须用字符“\”来说明,比如: \n 换行符 \t Tab键 键 \\ 字符“ 本身 字符“\”本身 \” 双引号” 双引号” \206 八进制数206对应的 对应的ASC||值 八进制数 对应的 值

芜湖职业技术学院 1.线网类型 线网类型 线网类型数据相当于硬件电路中的各种物理连接,如器 件的管脚、内部器件如与门的输出等。其特点是输出的 值紧跟输入值的变化而变化。 对连线型有两种驱动方式, 一种方式是在结构描述中将其连接到一个逻辑门或模块 的输出端;另一种方式是用持续赋值语句assign对其进 行赋值。 Verilog HDL提供了多种连线型变量。见表:

宽度为多位的wire类型变量的定义格式如下: wire[n-1:0] 数据名1,数据名2,……,数据名n; wire[7:0] databus // databus的宽度为8位

芜湖职业技术学院 wire型数据的使用 型数据的使用 wire[7:0] in,out; //定义了两个8位宽度向量in和out assign out,in; //不能用always操作