基于FPGA的直流电机PWM调速系统设计与实现

基于FPGA直流压缩机的PWM控制器设计

值, 可 以改 变 电机 两端 电压 的平 均值 , 从而达 到调 速 的 目的_ 4 ] . 脉宽 调制原 理框 图如 图 1所 示 , 波形 图如 图

2所 示 .

控制 车 内温度 的 目的.

1 P W M 的 调 制 原 理

度进 行 处 理 , 产 生 占空 比为 1 O %~ 1 0 0 的 可 调 的 P W M 控制 信号 , 控 制膨胀 阀及压 缩 机 工作 , 从 而达 到

比例 , 占空 比越 大 , 电机 转 速 越 快 . a是 一 个很 重要 的 参数 , 在 电源 电压 不 变 的情 况 下 , 电机 两端 的电压

的规模 、 内部 互 连线 的 结构 和采 用 的可 编 程元 件 上存

在 较 大 的差 异 , 较 常 用 的 有 Al t e r a 、 X i n l i n x和 Ac t e l

即可 使 电压与频 率协 调变 化. 若在 一 个 周期 丁 内 的导

通 时间为 t , 则 电机两 端 的平 均 电压 U 为 : u—U ×丁 t一口 式中, a为 占空 比 , a —t / T( O ≤n ≤1 ) ; U 是 电源 电压 . 由于 电机 电压与 电机 的转 速成 比例 , 而 电机 电压 与控

制 器 的 实 现 原 理 及 VHD L的 实 现 方 法 . 该 控 制 器 能 产 生 占空 比为 l O ~l D O %的可调的 P WM 控制信号 , 控 制压 缩 机 电

机的频率变化 , 从 而 达 到对 制 冷 量 调 节 的 目的 . 运 行结 果表 明, 该 系统控制 精度高 、 可靠 性好 , 具有设 计灵 活 、 处 理 速 度

基于FPGA的直流电机PWM控制实现

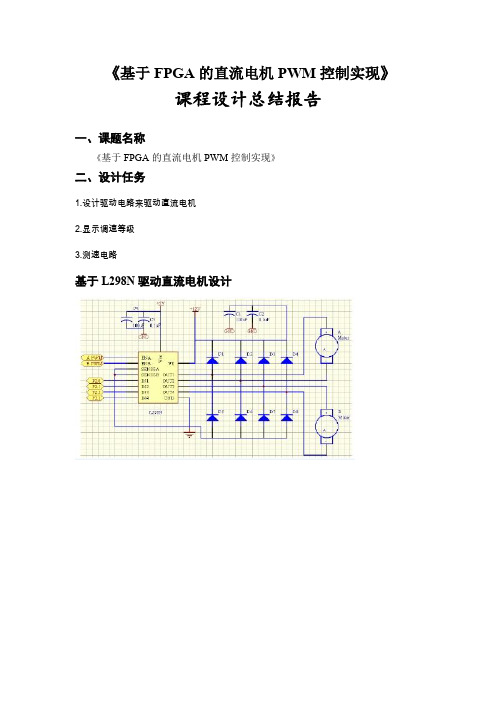

《基于FPGA的直流电机PWM控制实现》课程设计总结报告一、课题名称《基于FPGA的直流电机PWM控制实现》二、设计任务1.设计驱动电路来驱动直流电机2.显示调速等级3.测速电路基于L298N驱动直流电机设计三、系统总体设计方案(画出系统原理框图、方案的论证与比较等内容);1.系统原理框图2.PWM的实现与比较一般的脉宽调制PWM信号是通过模拟比较器产生的,比较器的一端接给定的参考电压,另一端周期线性增加的锯齿波电压。

当锯齿波电压小于参考电压时输出低电平,当锯齿波电压大于参考电压时输出高电平。

改变参考电压就可以改变PWM波形中高电平的宽度。

若用单片机产生的PWM信号波形,需要通过D/A转换器产生锯齿波电压和设置参考电压,通过外接模拟比较器输出PWM波形,因此外围电路比较复杂。

FPGA中的数字PWM控制欲一般的模拟PWM控制不同。

用FPGA产生PWM波形,只需FPGA内部资源就可以实现。

用数字比较器代替模拟比较器,其一端接设定值计数器输出,另一端接线性递增计数器输出。

当线性计数器的计数值小于设定值时输出低电平,当计数值大于设定值时输出高电平。

与模拟控制比较,省去了外接的D/A转换器和模拟比较器,FPGA外部连线很少,电路更加简单,便于控制。

脉宽调制式细分驱动电路的关键是脉宽调制,转速的波动随着PWM脉宽系法术的增大而减小。

四、具体实现方案(各模块或单元电路的设计、工作原理阐述等内容);1. PWM脉宽调制信号发生模块PWM-SQU1此模块是FPGA中的PWM脉宽调制信号产生电路。

它的输出接一电机转向控制电路模块,此模块输出的两个端口接直流电机。

通过控制SL端(键1),可以改变电机转向。

PWM-SQU1的输入端之一来自模块COUNTER8B。

这是一个8为计数器,输出的数据相当于锯齿波信号,此信号的频率就是PWM波的频率,它有来自锁相环的C0的频率决定。

PWM-SQU1另一端来自键控的8位数据,其中低4为CIN[3..0]设定为恒定1111,高4位有计数器CNT4B产生,计数器的时钟来自键K8.于是可以通过手动按键控制电机的转速。

基于单片机的PWM直流电机调速系统设计

基于单片机的PWM直流电机调速系统设计摘要本文主要介绍基于单片机的PWM直流电机调速系统的设计和实现方法。

该系统通过利用单片机控制器控制电机的启动、停止、正转和反转等操作,同时实现对电机速度的调节。

在电机工作时,单片机通过PWM技术控制电机的电压和电流,从而达到调节电机转速的效果。

系统设计思路为了实现电机的调速功能,本系统采用基于单片机控制器和PWM技术的电机驱动控制方案。

系统整体分为硬件和软件两个部分,硬件部分主要包括电机、电路组成和控制器,而软件部分则是单片机程序设计。

电路组成系统电路主要由电源、单片机控制器、电机驱动模块和电机组成。

其中,电源主要用于系统供电,单片机控制器主要用于控制电机驱动模块的输出,电机驱动模块负责将单片机控制器输出的PWM信号转换为直流电机可控的电流。

单片机程序设计系统中需要对单片机进行程序设计,以实现对电机的启动、停止、正转和反转等操作,同时实现电机的调节功能。

程序设计主要包括以下几个部分:1.系统初始化:包括系统时钟初始化、输入输出口初始化以及中断配置等。

2.电机控制:控制电机的启动、停止、正转和反转等操作。

3.电机调速:利用PWM技术实现对电机的调节功能。

4.数据处理:对输入的调节参数进行处理,然后转换成PWM占空比输出到电机。

PWM技术原理PWM技术是通过控制模拟信号的占空比,来达到模拟信号的数字化的目的。

具体而言,通过控制PWM信号的占空比,从而实现对电机输出电压和电流的控制,从而达到对电机转速的调节。

系统实现步骤本系统的实现步骤主要包括以下几个部分:电机接线首先,需要根据电机的参数和工作电压要求,正确接线电机。

接线时需要注意电机正反转的问题,以及电路的安全性问题。

程序编写根据我们的设计思路,需要编写相应的单片机程序。

程序编写包括系统初始化、电机控制、电机调速和数据处理等部分。

编写程序时需要考虑到各参数变化的初始值和变化范围,以及程序的鲁棒性和可调节性。

系统调试在程序编写完成后,需要对整个系统进行调试。

基于FPGA直流电机的PWM控制——毕业设计

基于FPGA直流电机的PWM控制Based on FPGA direct current machine's PWMcontrol rotational摘要EDA技术是用于电子产品设计中比较先进的技术,可以代替设计者完成电子系统设计中的大部分工作,而且可以直接从程序中修改错误及系统功能而不需要硬件电路的支持,既缩短了研发周期,又大大节约了成本,受到了电子工程师的青睐。

实现直流电机转速的控制方法很多,可以用可编程序控制器PLC、单片机等方案来实现。

但是这些控制方法的功能修改及调试都需要硬件电路的支持,在一定程度上增加了功能修改及系统调试的困难。

因此,在设计中采用EDA技术,应用目前广泛应用的VHDL硬件电路描述语言,实现直流电机转向的控制设计,利用QuartusⅡ集成开发环境进行综合、仿真。

关键词:电子系统、硬件电路、直流电机、转向ABSTRACTEDA the technology is uses in the electronic products design the quite advanced technology, may replace the desi gner to complete in the electronic system design the majority of work, moreover may revise wrong and the system function directly from the procedure, but does not need hardware circuit's support, both reduced the research and development cycle, and saved t he cost greatly, has received the electronic engineer's favor.Realizes the direct current machine rotational speed control method to be many, may use programmable plans and so on controller PLC, monolithic integrated circuit to realize. But these control method's function revision and the debugging needed hardware circuit's support, to increase the function revision and the system debugging difficulty to a certain extent. Therefore, uses the EDA technology in the design, the application present widespread application VHDL hardware circuit description language, realizes control design which the direct current machine changes, uses QuartusⅡThe integrated development environment carries on the synthesis, the simulation.Key word:EDA、VHDL、QuartusⅡ、the direct current machine、realizes control目录前言 (3)第一章PWM技术 (4)第二章EDA简要介绍 (6)§2.1 EDA技术的发展历程 (6)§2.2 EDA技术的主要内容 (8)§2.3 EDA技术的发展趋势 (9)第三章硬件描述语言VHDL (11)§3.1 VHDL语言概况 (11)§3.2 VHDL硬件程序结构 (13)§3.3 VHDL语言的特点 (16)第四章QuartusII开发系统 (17)§4.1 QuartusII设计流程: (17)§4.2 QuartusII的设计特点 (20)第五章本设计中所用到的各基本原件的程序及仿真波形 (22)§5.1 八位计数器 (22)§5.2 A_D转换器 (23)§5.3 比较器 (25)§5.5 元件组合完成电机方向转换的仿真 (28)结论 (31)参考文献 ............................................... 错误!未定义书签。

基于FPGA的直流电机PWM控制实现

《基于FPGA的直流电机PWM控制实现》课程设计总结报告一、课题名称《基于FPGA的直流电机PWM控制实现》二、设计任务1.设计驱动电路来驱动直流电机2.显示调速等级3.测速电路基于L298N驱动直流电机设计三、系统总体设计方案(画出系统原理框图、方案的论证与比较等内容);1.系统原理框图2.PWM的实现与比较一般的脉宽调制PWM信号是通过模拟比较器产生的,比较器的一端接给定的参考电压,另一端周期线性增加的锯齿波电压。

当锯齿波电压小于参考电压时输出低电平,当锯齿波电压大于参考电压时输出高电平。

改变参考电压就可以改变PWM波形中高电平的宽度。

若用单片机产生的PWM信号波形,需要通过D/A转换器产生锯齿波电压和设置参考电压,通过外接模拟比较器输出PWM波形,因此外围电路比较复杂。

FPGA中的数字PWM控制欲一般的模拟PWM控制不同。

用FPGA产生PWM波形,只需FPGA内部资源就可以实现。

用数字比较器代替模拟比较器,其一端接设定值计数器输出,另一端接线性递增计数器输出。

当线性计数器的计数值小于设定值时输出低电平,当计数值大于设定值时输出高电平。

与模拟控制比较,省去了外接的D/A转换器和模拟比较器,FPGA外部连线很少,电路更加简单,便于控制。

脉宽调制式细分驱动电路的关键是脉宽调制,转速的波动随着PWM脉宽系法术的增大而减小。

四、具体实现方案(各模块或单元电路的设计、工作原理阐述等内容);1. PWM脉宽调制信号发生模块PWM-SQU1此模块是FPGA中的PWM脉宽调制信号产生电路。

它的输出接一电机转向控制电路模块,此模块输出的两个端口接直流电机。

通过控制SL端(键1),可以改变电机转向。

PWM-SQU1的输入端之一来自模块COUNTER8B。

这是一个8为计数器,输出的数据相当于锯齿波信号,此信号的频率就是PWM波的频率,它有来自锁相环的C0的频率决定。

PWM-SQU1另一端来自键控的8位数据,其中低4为CIN[3..0]设定为恒定1111,高4位有计数器CNT4B产生,计数器的时钟来自键K8.于是可以通过手动按键控制电机的转速。

fpga直流电机pwm控制实验原理

fpga直流电机pwm控制实验原理FPGA是一种可编程门阵列器件,可以用于实现数字电路设计,在工业自动化控制中有很广泛的应用。

而直流电机是一种常见的机电设备,其控制方式多种多样。

其中较常用的一种是PWM控制方式,即采用脉宽调制技术来实现电机控制。

在PWM控制方式中,通过将直流电源接入一个可变的开关,将其与电机串联,开关控制周期性地将电源接入电机绕组中,从而实现电机转动的控制。

在实际控制过程中,通过调整开关的开闭时间,可以实现不同的控制效果。

FPGA直流电机PWM控制实验,就是通过使用FPGA器件来实现对电机的PWM控制。

实验的流程如下:1.定义时钟信号:FPGA是一种异步工作的器件,需要一个时钟信号来同步各种逻辑操作。

因此,实验开始时需要定义一个时钟信号。

2.配置PWM模块:PWM模块是FPGA内部的一个模块,用于生成脉宽调制信号。

在此步骤中,需要对PWM模块进行配置,包括设置PWM输出频率、占空比、极性等参数。

3.编写控制代码:编写控制代码来实现PWM控制。

控制代码需要读取PWM模块输出,根据实际需要设置占空比、频率等参数,从而实现对电机的控制。

4.连接硬件:将FPGA器件与直流电机连接起来,使得FPGA能够对电机进行控制。

5.测试验证:通过实验来验证控制代码及电路的正确性。

在测试过程中,需要对PWM 信号进行观测,以确保其频率、占空比等参数符合预期,同时需要对电机转速进行观测,以确保电机的实际控制效果与预期一致。

总之,FPGA直流电机PWM控制实验,可以帮助我们更好地理解数字电路和控制原理,并通过实验验证对控制技术的应用。

在之后的研究和实际应用中,可以根据需要选择不同的PWM控制方式,并结合实际应用场景进行优化和调整,以实现最佳的控制效果。

基于FPGA的直流电机PWM调速系统设计实现分析

基于FPGA的直流电机PWM调速系统设计实现分析1.引言直流电机广泛应用于各个领域,如工业控制、机器人等。

调速系统是直流电机应用中非常重要的一部分,直流电机的调速在一定范围内能够满足不同负载需求。

本文将介绍基于FPGA的直流电机PWM调速系统的设计实现分析。

2.系统设计2.1系统架构设计基于FPGA的直流电机PWM调速系统主要包括FPGA、PWM控制器、驱动电路和直流电机。

其中,FPGA负责进行调速算法的运算和时序控制,PWM控制器用于生成PWM信号,驱动电路控制直流电机的转速和方向。

2.2算法设计调速算法一般采用PID控制算法,通过测量直流电机的转速和负载情况,计算出PWM占空比,并调整PWM信号的频率和占空比以实现电机的调速。

在FPGA中,可以使用硬件描述语言(HDL)进行算法实现。

使用VHDL或Verilog等HDL语言,编写PID控制器、计数器和状态机等模块,实现调速算法的运算和时序控制。

3.系统实现3.1FPGA的选择FPGA是可编程逻辑芯片,具有灵活性和高性能的特点。

在选择FPGA 时,需要考虑系统的性能需求、资源使用和开发成本等因素。

常用的FPGA型号包括Xilinx系列和Altera(Intel)系列等。

3.2PWM控制器设计PWM控制器的设计主要包括频率和占空比的控制。

可以使用计数器和状态机实现PWM信号的生成。

计数器用于计数并产生PWM控制信号的频率,状态机用于控制计数器并调整PWM占空比。

3.3驱动电路设计驱动电路主要负责将FPGA生成的PWM信号转化为适合驱动直流电机的电压和电流信号。

驱动电路一般包括功率放大器、H桥驱动模块和电流反馈模块等。

通过控制H桥驱动模块的开关,可以实现直流电机的正反转和调速功能。

4.总结本文介绍了基于FPGA的直流电机PWM调速系统的设计实现分析。

通过使用FPGA进行调速算法的运算和时序控制,实现了对直流电机的精确调速。

系统设计包括FPGA选择、PWM控制器设计和驱动电路设计等。

基于FPGA的直流电机PWM控制器设计

基于FPGA的直流电机PWM控制器设计基于FPGA的直流电机PWM控制器设计摘要:利用FPGA可编程芯片及Verilog HDL语言实现了对直流电机PWM控制器的设计,对直流电机速度进行控制。

介绍了用Verilog HDL语言编程实现直流电机PWM控制器的PWM产生模块、转向调节模块等功能,该系统无须外接D/A转换器及模拟比较器,结构简单,控制精度高,可方便对电机进行远程控制,有广泛的应用前景。

关键词:FPGA;PWM;直流电机;实验0 引言传统的方法产生PWM信号电路比较复杂。

数字PWM控制只需FPGA中的内部资源就可以实现。

本文介绍了一种用单片大规模FPGA 实现的PWM发生的直流电机控制器,其中产生的PWM波具有脉冲中心对称、PWM 周期和死区时间可编程等特点,且性能优异,灵活性和可靠性高。

用数字比较器代替模拟比较器,数字比较器的一端接设定值计数器的输出,另一端接线性递增计数器输出。

当线性计数器计数值小于设定值时输出低电平,大于设定值时输出高电平。

与模拟控制相比,省去了外接的D/A转换器和模拟比较器,FPGA外部连线很少,电路更加简单。

而且通过总线数据或按键控制在系统调整脉宽数及数字比较器的设定值,从而实现对电机转速、波动性等参数的灵活控制。

1 系统整体设计系统的整体框图如图1所示。

该系统以FPGA芯片为控制核心,通过按键或上位机设定电机速度和PWM占空比,由FPGA的I/O口控制直流电机驱动芯片驱动直流电机的转动。

转速的测量由码盘完成,速度显示数码管来实现。

本系统是基于实现电机的恒速调节而进行设计的。

系统分以下几个模块:转速调节模块,脉宽调制(PWM)模块,速度检测模块,在图2中所示的FPGA是根据设计要求设计好的一个芯片,其内部逻辑电路如图3。

START是电机的开启端,U_D控制电机加速与减速,EN1用于设定电机转速的初值,Z_F是电机的方向端口,选择电机运行的方向。

CLK2和CLK0是外部时钟端,其主要作用是向FPGA 控制系统提供时钟脉冲,控制电机进行运转。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FPGA课程设计题目:基于FPGA的直流电机PWM调速系统设计与实现班级:微电子学1202班姓名:杜英学号:01日期:2016年3月24日基于FPGA的直流电机PWM调速系统设计与实现1设计任务与要求设计任务完成基于FPGA的直流电机PWM调速系统设计与实现,实现对直流电机的闭环调速,速度值采用LCD或数码管显示。

设计要求了解PWM控制方法及应用;掌握PWM直流电机调速控制原理;掌握直流电机调速及驱动控制原理;完成基于FPGA的直流电机PWM调速系统设计。

采用PWM(脉冲宽度调制)技术,速度值采用LCD或数码管显示。

通过课程设计的实践,进一步了解和掌握硬件描述语言(VHDL或Verilog)和TOP-DOWN的设计流程,提高对实际项目的分析和设计能力,体会FPGA项目开发的过程,熟悉实验报告的编写规范。

2设计原理分析2.1直流电机结构如下图所示图直流电机的构造将直流电源通过电刷接通线组线圈,使线组线圈导体(电枢导体)有电流通过,在电磁的作用下,线组线圈将会产生磁场,同时产生的磁场与主磁极的磁场产生电磁力,这个电磁力作用于转子,使转子以一定的速度开始旋转,电机就开始工作。

在电机的外部电路加入开关型的霍尔元件,同时在电子转子的转盘上加入一个使霍尔元件产生输出的带有磁场的磁钢片。

当直流电机旋转时转盘与磁钢片一起旋转,当磁钢片转到霍尔元件上方时,可以使霍尔元件的输出端高电平变为低电平。

当磁钢片离开霍尔元件上方后,霍尔元件输出端又恢复高电平。

如此,点击每旋转一周,会使霍尔元件的输出端产生一个低脉冲,可以通过检测单位时间内霍尔元件输出端低脉冲的个数推算出直流电机的转速。

本次设计中,调节PWM占空比进而控制直流电机转速,在本次设计中,为了保护霍尔元件,故设定程序每6秒刷新一次数据,所以在数码管显示的数据乘以10就是在该占空比时的直流电机每分钟转速。

在这次的实验中数码管采用的8位共阴极数码管,通过锁存器输入数据使得数码管的8个段码数字显示,再通过选择输出数据对所需数码管进行选择。

2.2电路原理图图电路原理图3 设计方案上述原理图中包含PWM模块、测速模块、计数模块、电机模块、滤波模块。

电机的外部电路加入开关型的霍尔元件,同时在电子转子的转盘上加入一个使霍尔元件产生输出的带有磁场的磁钢片。

当直流电机旋转时转盘与磁钢片一起旋转,当磁钢片转到霍尔元件上方时,可以使霍尔元件的输出端高电平变为低电平。

当磁钢片离开霍尔元件上方后,霍尔元件输出端又恢复高电平。

如此,点击每旋转一周,会使霍尔元件的输出端产生一个低脉冲,可以通过检测单位时间内霍尔元件输出端低脉冲的个数推算出直流电机的转速。

本次设计为六秒记一次数,乘十就是每分钟转速值。

再通过驱动模块显示数码管数据。

4设计步骤(1)首先确定整体设计方案,确定设计需要使用的软件;(2)设计电路模块,编写各模块程序代码并进行仿真编译;(3)完成整体电路图设计后,使用QuartusⅡ软件对整体电路进行仿真调试;(4)连接硬件,使用示波器观察产生的波形,对不足之处进行改进调试。

5调试结果说明连接好试验箱,把硬件与实验箱接通,将程序下载到实验箱中。

进行实验,示波器观察PWM脉冲波形(占空比),看实验结果与预期效果是否相同,若相同,则实验无误。

其波形如下:占空比为50%时占空比为90%时将程序下载到实验箱中后,其实际操作过程如下:K12为使能键,使K12=‘1’;输入时钟信号为1MHZ;(1) K4=1时,示波器和LED的显示如下:示波器显示的是霍尔元件单位时间内计数的个数为显示器是每六秒电机转的圈数为186转结论:*6=于186近似,所以结论符合要求。

(2) K4=1,k3=1时,示波器和LED的显示如下:结论:*6=于412近似,所以结论符合要求。

(3) K4=1,k3=1,K2=1时,示波器和LED的显示如下:结论:*6=于513近似,所以结论符合要求。

(4) K4=1,k3=1,K2=1,K1=1时,示波器和LED的显示如下:结论:*6=于541近似,所以结论符合要求。

通过以上的比较,发现示波器中的结果与数码管上数据大概一致,即实验结果基本达到要求。

6心得体会? 本次课程设计,用FPGA控制直流电机,完成直流电机PWM调速系统设计,实现对直流电机的闭环调速,速度值采用LCD或数码管显示。

是一次很好的学习和实践的机会。

通过课程设计,我明白了电机工作的原理,以及用FPGA控制电机的原理。

最重要的是,对如何设计一个系统有了更进一步的了解,积累了很多经验。

?从下载测试的结果来看,设计的要求基本上都实现了。

但是仍存在不少问题。

每个模块生成基本电路后,把各个模块的进行连接,仿真结果是正确的。

但是当连接到试验箱后,电机正常转动,LED却无法显示。

检查电路和程序还有电路图,并发现什么问题。

无意中发现LED偶尔会出现数字,但也只是闪一下。

最后才发现是因为电机转动太快了,LED无法及时显示或者是一直在闪,人眼无法识别。

在程序中加入了滤波模块,才解决了问题。

在设计的过程中,开始照着EDA课本上的原理设计,后来才发现所设计的电路有很多地方都满足不了设计要求,使设计一度遭遇了很大困难。

通过与同学讨论请教,逐步改进了设计,终于使设计的电路和设计要求相吻合。

在这中间,通过不断提出问题,解决问题,我对这次设计的原理有了更深的了解,也给我分析问题,解决问题提供了很多好的方法,好的思路。

同时,我也发现了自己存在的很多不足。

发现自己在设计一个系统的时候不能够统筹兼顾,不能够从总体上把握设计的思路,也不能看清问题的核心与关键所在。

这些都需要在下面不断学习实践,理论毕竟只是理论,要多参加实践,这样才能提高自己的能力,积累经验。

附录一PWM模块程序Library ieee;use PWM isport(clock:in std_logic;duty_cycle:in std_logic_vector(3 downto 0);pwm_en:in std_logic;pwm_out:out std_logic);end entity;architecture art of PWM issignal pwm_out_io:std_logic;signal count:std_logic_vector(3 downto 0); beginpwm_out<=pwm_out_io;process(clock)beginif rising_edge(clock) thenif pwm_en='1' thencount<=count+1;end if;end if;end process;process(clock)beginif rising_edge(clock) thenif pwm_en='1' and count<duty_cycle thenpwm_out_io<='1';elsepwm_out_io<='0';end if;end if;end process;end;测速模块程序library ieee ;use ;use ;use ;entity cesu isport( clk : in std_logic; --时钟输入1Mhzena : out std_logic; --允许计数clr : out std_logic; --计数器清零信号产生load : out std_logic); --锁存、显示输出允许高有效end cesu;architecture behav of cesu issignal clkk :std_logic; --1HZ时钟信号signal count :integer range 0 to 7;--6秒计数signal clr1 :std_logic; --清零信号signal ena1 :std_logic; --允许计数信号signal load1 :std_logic; --允许计数信号--signal cq1,cq2,cq3,cq4 : INTEGER RANGE 0 TO 15;--计数数据beginprocess(clk)variable c:std_logic;variable cnt:integer range 0 to 500000;beginif clk'event and clk='1' thencnt:=cnt+1;if cnt=500000 thencnt:=0; c:=not c;end if;end if;clkk<=c;end process;process(clkk) --6秒计数beginif clkk'event and clkk='1' thencount<=count+1;if count<6 thenena1<='1';load1<='0';clr1<='0';elsif count=6 thenena1<='0';load1<='1';clr1<='0';elsif count=7 thenena1<='0';load1<='1';clr1<='1';end if;end if;ena<=ena1;load<=load1;clr<=clr1;end process;end behav;计数模块程序library ieee;useentity cnt10 isport (clk:in std_logic; --计数时钟信号clr:in std_logic; --清零信号ena:in std_logic; --计数使能信号cq :out integer range 0 to 15;--4位计数结果输出carry_out:out std_logic); --计数进位end cnt10;architecture behav of cnt10 issignal cq1:integer range 0 to 15;beginprocess(clk,ena)beginif clr= '1' then cq1<= 0; ----计数器异步清零elsif clk'event and clk= '1' thenif ena= '1' thenif cq1=10 then cq1<=1;else cq1<=cq1+1;end if; ----等于9,则计数器清零end if;end if;end process;process (cq1)beginif cq1=10 then carry_out<= '1'; ----进位输出else carry_out<= '0';end if;end process;cq<=cq1;end behav;驱动模块程序library ieee;use qudong_8 isport(clk:in std_logic;--动态显示刷新速度时钟QQ1,QQ2,QQ3:in std_logic_vector(3 downto 0);--32位BCD码输入,最0~3低位,28~31最高位qudong1:out std_logic_vector(7 downto 0);--驱动信号输出,0~7分别为abcdefgpcontrl:buffer std_logic_vector(2 downto 0));--数码管位选输出,000最低位数码管有效,111最高位数码管有效end qudong_8;architecture behavior of qudong_8 issignal disp:std_logic_vector(3 downto 0);signal temp:std_logic_vector(2 downto 0);beginprocess(clk)beginif clk'event and clk='1' thentemp<=temp+1;end if;contrl<=temp;end process;process(contrl)--位选信号产生进程begincase contrl is--when"000"=>disp<=QQ7;--when"001"=>disp<=QQ6;--when"010"=>disp<=QQ5;--when"011"=>disp<=QQ4;when"100"=>disp<=QQ3;when"101"=>disp<=QQ2;when"110"=>disp<=QQ1;--when"111"=>disp<="0000";when others=>disp<="0000";end case;end process;process(disp)--译码进程begincase disp iswhen"0000"=>qudong1<="00111111";when"0001"=>qudong1<="00000110";when"0010"=>qudong1<="01011011";when"0011"=>qudong1<="01001111";when"0100"=>qudong1<="01100110";when"0101"=>qudong1<="01101101";when"0110"=>qudong1<="01111101";when"0111"=>qudong1<="00000111";when"1000"=>qudong1<="01111111";when"1001"=>qudong1<="01101111";when others=>qudong1<="00000110";end case;end process;end behavior;消抖模块程序library ieee;useentity xiaodou isport(clk,input: in std_logic;output: out std_logic);end xiaodou;architecture behav of xiaodou issignal cp:std_logic;signal count:integer range 0 to 3;beginprocess(clk)beginif(clk'event and clk='1') then --检测上升沿if(input='1')then --如果有输入信号if(count=3)then count<=count; --当计数达到3时,保持计数值不变else count<=count+1; --当其小于3时,进行加1处理end if;if(count=2)then cp<='1'; --如果计数达到2,cp置1else cp<='0'; -- 其余情况全部为0end if;else count<=0; --如果计数出现非法状况,进行清零复位end if;end if;output<=cp; --信号输出end process;end behav;。