PL-PLCC44-S-02中文资料

TDIH资料

Features•In-system programmable 3.3V PROMs for configuration of Xilinx FPGAs-Endurance of 10,000 program/erase cycles-Program/erase over full commercial voltage and temperature range•IEEE Std 1149.1 boundary-scan (JTAG) support •Simple interface to the FPGA; could be configured to use only one user I/O pin•Cascadable for storing longer or multiple bitstreams •Dual configuration modes-Serial Slow/Fast configuration (up to 15 mHz).-Parallel•Low-power advanced CMOS FLASH process• 5 V tolerant I/O pins accept 5 V, 3.3 V and 2.5 V signals.• 3.3 V or 2.5 V output capability•Available in PC20, SO20, PC44 and VQ44 packages.•Design support using the Xilinx Alliance and Foundation series software packages.•JTAG command initiation of standard FPGA configuration.DescriptionXilinx introduces the XC1800 series of in-system program-mable configuration PROMs. Initial devices in this 3.3V family are a 4 megabit, a 2 megabit, a 1 megabit, a 512 Kbit, a 256 Kbit, and a 128 Kbit PROM that provide an easy-to-use, cost-effective method for re-programming and storing large Xilinx FPGA or CPLD configuration bit-streams.When the FPGA is in Master Serial mode, it generates a configuration clock that drives the PROM. A short access time after the rising CCLK, data is available on the PROM DATA (D0) pin that is connected to the FPGA DIN pin. The FPGA generates the appropriate number of clock pulses to complete the configuration. When the FPGA is in Slave Serial mode, the PROM and the FPGA are clocked by an external clock.When the FPGA is in Express or SelectMAP Mode, an external oscillator will generate the configuration clock that drives the PROM and the FPGA. After the rising CCLK edge, data are available on the PROM’s DATA (D0-D7) pins. The data will be clocked into the FPGA on the follow-ing rising edge of the CCLK. Neither Express nor Select-MAP utilize a Length Count, so a free-running oscillator may be used. See Figure5Multiple devices can be concatenated by using the CEO output to drive the CE input of the following device. The clock inputs and the DATA outputs of all PROMs in this chain are interconnected. All devices are compatible and can be cascaded with other members of the family or with the XC1700L one-time programmable Serial PROM family.September 17, 1999 (Version 1.3)Preliminary Product Specification Figure 1: XC1800 Series Block DiagramPinout and Pin Description Table 1: Pin Names and DescriptionsPin Name BoundaryScanOrderFunction Pin Description44-pinVQFP44-pinPLCC20-pinSOIC & PLCCD04DATA OUT D0 is the DATA output pin to provide datafor configuring an FPGA in serial mode.40213OUTPUTENABLED16DATA OUT D0- D7 are the output pins to provide par-allel data for configuring a Xilinx FPGA inexpress mode.2935165OUTPUTENABLED22DATA OUT4242 1OUTPUTENABLED38DATA OUT273315 7OUTPUTENABLED424DATA OUT9157* 23OUTPUTENABLED510DATA OUT253114 9OUTPUTENABLED617DATA OUT14209 16OUTPUTENABLED714DATA OUT192512 13OUTPUTENABLECLK0DATA IN Each rising edge on the CLK input incre-ments the internal address counter if bothCE is low and OE/RESET is high.4353OE/ RESET 20DATA IN When Low, this input holds the addresscounter reset and the DATA output athigh impedance. 13198 19DATA OUT18OUTPUTENABLECE15DATA IN When CE is High, this pin puts the deviceinto standby mode. The DATA output pinis at High impedance, and the device is inlow power standby mode.152110CF22DATA OUT Allows JTAG CONFIG instruction to ini-tiate FPGA configuration without power-ing down FPGA.10167*21DATA IN*Programmable for Serial Mode only on 18512 and 1801.CEO13DATA OUT Chip Enable (CEO) output is connectedto the CE input of the next PROM in thechain. This output is Low when the CEand OE/RESET inputs are active AND the internal address counter has been in-cremented beyond its Terminal Count (TC) value. When the PROM has been read, CEO will follow CE as long as OE/RESET is High. When OE/RESET goes Low, CEO stays High until the PROM is brought out of reset by bringing OE/RE-SET High. CEO can be programmed to be either active High or active Low.21271314OUTPUTENABLEGND GND is the ground connection.6, 18, 28 & 413, 12, 24 &3411TMSMODE SELECTThe state of TMS on the rising edge of TCK determines the state transitions at the Test Access Port (TAP) controller. TMS has an internal 50K ohm resistive pull-up on it to provide a logic 1 to the de-vice if the pin is not driven.5115TCK CLOCK This pin is the JTAG test clock. It se-quences the TAP controller and all the JTAG test and programming electronics.7136TDI DATA IN This pin is the serial input to all JTAG in-struction and data registers. TDI has an internal 50K ohm resistive pull-up on it to provide a logic 1 to the system if the pin is not driven.394TDODATA OUT This pin is the serial output for all JTAGinstruction and data registers. TDO has an internal 50k ohm resistive pull-up on it to provide a logic 1 to the system if the pin is not driven.313717V CC Positive voltage supply of 3.3V for inter-nal logic and input buffers.17, 35 & 3823, 41 & 4418 & 20V CCOPositive voltage supply connected to the output voltage drivers.8, 16, 26 & 3614, 22, 32 & 4219Pin Name Boundary Scan OrderFunctionPin Description44-pin VQFP 44-pin PLCC 20-pin SOIC & PLCCXilinx FPGAs and CompatiblePROMsCapacityDevice Configuration Bits PROM XC4003E53,984XC18128 XC4005E95,008XC18128 XC4006E119,840XC18128 XC4008E147,552XC18256 XC4010E178,144XC18256 XC4013E247,968XC18256 XC4020E329,312XC18512 XC4025E422,176XC18512 XC4002XL61,100XC18128 XC4005XL151,960XC18256 XC4010XL283,424XC18512 XC4013XL/XLA393,632XC18512 XC4020XL/XLA521,880XC18512 XC4028XL/XLA668,184XC1801 XC4036XL/XLA832,528XC1801 XC4044XL/XLA1,014,928XC1801 XC4052XL/XLA1,215,368XC1802 XC4062XL/XLA1,433,864XC1802 XC4085XL/XLA1,924,992XC1802 XC40110XV2,686,136XC1804 XC40150XV3,373,448XC1804 XC40200XV4,551,056XC1804 +XC18512 XC40250XV5,433,888XC1804 +XC1802 XCV50559,232XC1801 XCV100781,248XC1801 XCV1501,041,128XC1801 XCV2001,335,872XC1802 XCV3001,751,840XC1802 XCV4002,546,080XC1804 XCV6003,608,000XC1804 XCV8004,715,648XC1804 +XC18512 XCV10006,127,776XC1804 +XC1802Devices Configuration Bits 18044,194,304 18022,097,152 18011,048,576 18512524,288 18256262,144 18128131,072In-System ProgrammingOne or more in-system programmable PROMs can be daisy chained together and programmed in-system via the standard 4-pin JTAG protocol as shown in Figure2. In-sys-tem programming offers quick and efficient design itera-tions and eliminates unnecessary package handling or socketing of devices. The Xilinx development system pro-vides the programming data sequence using Xilinx JTAG Programmer software and a download cable, a third-party JTAG development system, a JTAG-compatible board tester, or a simple microprocessor interface that emulates the JTAG instruction sequence.All outputs are 3-stated or held at clamp levels during in-system programming.External ProgrammingXilinx reprogrammable PROMs can also be programmed by the Xilinx HW-130 device programmer. This provides the added flexibility of using pre-programmed devices in design, boundary-scan manufacturing tools, with an in-sys-tem programmable option for future enhancements and design changes.Reliability and EnduranceXilinx in-system programmable products provide a mini-mum endurance level of 10,000 in-system program/erase cycles and a minimum data retention of 10 years. Each device meets all functional, performance, and data reten-tion specifications within this endurance limit.Design SecurityThe Xilinx in-system programmable PROM devices incor-porate advanced data security features to fully protect the programming data against unauthorized reading. Table2 shows the security setting available.The read security bit can be set by the user to prevent the internal programming pattern from being read or copied via JTAG. When set it allows device erase. Erasing the entire device is the only way to reset the read security bit.Table 2: Data Security OptionsDefault SetRead AllowedProgram/Erase AllowedRead Inhibited via JTAGErase AllowedX5902(a)(b)Figure 2: In-System Programming Operation (a) solder device to PCB and (b) Program using Download CableIEEE 1149.1 Boundary-Scan (JTAG) The XC1800 family is fully compliant with the IEEE Std. 1149.1 Boundary-Scan, also known as JTAG. A Test Access Port (TAP) and registers are provided to support all required boundary scan instructions, as well as many of the optional instructions specified by IEEE Std. 1149.1. In addi-tion, the JTAG interface is used to implement in-system programming (ISP) to facilitate configuration, erasure, and verification operations on the XC1800 device.Table3 lists the required and optional boundary-scan instructions supported in the XC1800. Refer to the IEEE Std. 1149.1 specification for a complete description of boundary-scan architecture and the required and optional instructions.Table 3: Boundary Scan InstructionsInstruction RegisterThe Instruction Register (IR) for the XC1800 is 8-bits wide and is connected between TDI and TDO during an instruc-tion scan sequence. In preparation for an instruction scan sequence, the instruction register is parallel loaded with a fixed instruction capture pattern. This pattern is shifted out onto TDO (LSB first), while an instruction is shifted into the instruction register from TDI. The detailed composition of the instruction capture pattern is illustrated in Figure 3. The ISP Status field, IR(4), contains logic 1 if the device is currently in ISP mode; otherwise, it will contain 0. The Security field, IR(3), will contain logic 1 if the device has been programmed with the security option turned on; other-wise, it will contain 0.Figure 3: Instruction Register values loaded into IR as part of an instruction scan sequenceBoundary Scan RegisterThe boundary-scan register is used to control and observe the state of the device pins during the EXTEST, SAMPLE/ PRELOAD, and CLAMP instructions. Each output pin on the XC1800 has two register stages that contribute to the boundary-scan register, while each input pin only has one register stage.For each output pin, the register stage nearest to TDI con-trols and observes the output state, and the second stage closest to TDO controls and observes the 3-state enable state of the pin.For each input pin, the register stage controls and observes the input state of the pin.Identification RegistersThe IDCODE is a fixed, vendor-assigned value that is used to electrically identify the manufacturer and type of the device being addressed. The IDCODE register is 32-bits wide. The IDCODE register can be shifted out for examina-tion by using the IDCODE instruction.The IDCODE register has the following binary format: vvvv:ffff:ffff:aaaa:aaaa:cccc:cccc:ccc1 wherev= the die version numberf=the family code (50h for XC1800 family)a=the ISP PROM product ID (06h for the XC1804)c=the company code (49h for Xilinx)Note: The LSB of the IDCODE register is always read as logic 1 as defined by IEEE Std. 1149.1Table 4: IDCODES Assigned to XC1800 devicesTable4 lists the IDCODE register values for the XC1800 devices.Boundary-Scan Command Binary Code(7:0)DescriptionRequired InstructionsBYPASS11111111Enables BYPASSSAMPLE/ PRELOAD 00000001Enables boundary-scanSAMPLE/PRELOADoperationEXTEST00000000Enables boundary-scanEXTEXT operation Optional InstructionsCLAMP11111010Enables boundary-scanCLAMP operation HIGHZ111111003-states all outputssimultaneously IDCODE11111110Enables shifting out 32-bit IDCODE USERCODE11111101Enables shifting out 32-bit USERCODEXC1800 Specific InstructionsCONFIG11101110Initiates FPGAconfiguration by pulsingCF pin lowIR(7:5)IR(4)IR(3)IR(2)IR(1:0)TDI->0 0 0ISPStatus Security00 1->TDO Note: IR(1:0) = 01 is specified by IEEE Std. 1149.1ISP-PROM IDCODEXC180105004093hXC180405006093hThe USERCODE instruction gives access to a 32-bit user programmable scratch pad typically used to supply infor-4-wire Test Access Port (TAP). This simplifies system designs and allows standard Automatic Test Equipment to Symbol ParameterMin MaxTCKMIN TCK Minimum Clock Period 100TMSS TMS Setup Time 10TMSH TMS Hold Time 10TDIS TDI Setup Time 15TDIH TDI Hold Time25TDOZX TDO Float to Valid Delay 35TDOXZ TDI Valid to Float Delay 35TDOVTDO Valid Delay35Controlling Configuration PROMs Connecting the FPGA device with the configuration PROM. •The DATA output(s) of the of the PROM(s) drives the DIN input of the lead FPGA device.•The Master FPGA CCLK output drives the CLK input(s) of the PROM(s).•The CEO output of a PROM drives the CE input of the next PROM in a daisy chain (if any).•The OE/RESET input of all PROMs is best driven by the INIT output of the lead FPGA device. Thisconnection assures that the PROM address counter is reset before the start of any (re)configuration, evenwhen a reconfiguration is initiated by a V CC glitch.•The PROM CE input can be driven from either the LDC or DONE pins. Using LDC avoids potential contention on the DIN pin. If the CE input of the first (or only)PROM can be driven by the DONE output of the first FPGA device, provided that DONE is not permanently grounded. Otherwise, LDC can be used to drive CE, but must then be unconditionally High during useroperation. CE can also be permanently tied Low, but this keeps the DATA output active and causes anunnecessary supply current of 10 mA maximum.•Express mode is similar to slave serial mode. The DATA is clocked out of the SPROM one byte per CCLK instead of one bit per CCLK cycle. To synchronize with the FPGA the first byte of data is valid 20ns before the second rising edge of CCLK and then on everyconsecutive CCLK thereafter. Note: Whenprogramming in Express mode, to accommodate the 4us set-up time on the INIT pin of the Spartan FPGA, the first line of the configuration stream must not beplaced higher than the 3C byte address of the PROM. Initiating FPGA ConfigurationThe XC1800 devices incorporate a pin named CF that is controllable through the JTAG CONFIG instruction. Execut-ing the CONFIG instruction through JTAG will pulse the CF low for 300-500ns, which will reset the FPGA and initiate configuration.The CF pin must be connected to the PROGRAM pin on the FPGA to use this feature.Selecting Configuration ModesThe XC1800 accommodates serial and parallel methods of configuration. The configuration modes are selectable through a user control register in the XC1800 device. This control register is accessible through JTAG, using the Xilinx JTAG Programmer software.FPGA Master Serial Mode Summary The I/O and logic functions of the Configurable Logic Block (CLB) and their associated interconnections are estab-lished by a configuration program. The program is loaded either automatically upon power up, or on command, depending on the state of the three FPGA mode pins. In Master Serial mode, the FPGA automatically loads the con-figuration program from an external memory. Xilinx PROMs are designed for compatibility with the Master Serial mode. Upon power-up or reconfiguration, an FPGA enters the Master Serial mode whenever all three of the FPGA mode-select pins are Low (M0=0, M1=0, M2=0). Data is read from the PROM sequentially on a single data line. Synchroniza-tion is provided by the rising edge of the temporary signal CCLK, which is generated during configuration.Master Serial Mode provides a simple configuration inter-face. Only a serial data line and two control lines are required to configure an FPGA. Data from the PROM is read sequentially, accessed via the internal address and bit counters which are incremented on every valid rising edge of CCLK. If the user-programmable, dual-function DIN pin on the FPGA is used only for configuration, it must still be held at a defined level during normal operation. The Xilinx FPGA families take care of this automatically with an on-chip default pull-up resistor.Programming the FPGA With Counters Unchanged Upon CompletionWhen multiple FPGA-configurations for a single FPGA are stored in a PROM, the OE/RESETpin should be tied Low. Upon power-up, the internal address counters are reset and configuration begins with the first program stored in memory. Since the OE/RESETpin is held Low, the address counters are left unchanged after configuration is com-plete. Therefore, to reprogram the FPGA with another pro-gram, the DONE line is pulled Low and configuration begins at the last value of the address counters.This method fails if a user applies OE/RESET during the FPGA configuration process. The FPGA aborts the config-uration and then restarts a new configuration, as intended, but the PROM does not reset its address counter, since it never saw a High level on its OE input. The new configura-tion, therefore, reads the remaining data in the PROM and interprets it as preamble, length count etc. Since the FPGA is the master, it issues the necessary number of CCLK pulses, up to 16 million (224) and DONE goes High. How-ever, the FPGA configuration will be completely wrong, with potential contentions inside the FPGA and on its output pins. This method must, therefore, never be used when there is any chance of external reset during configuration. Cascading Configuration PROMsFor multiple FPGAs configured as a daisy-chain, or for FPGAs requiring larger configuration memories, cascaded PROMs provide additional memory. Multiple XC1800 devices can be concatenated by using the CEO output to drive the CE input of the following device. The clock inputs and the data outputs of all XC1800 devices in the chain areinterconnected. After the last bit from the first PROM is read, the next clock signal to the PROM asserts its CEO output Low and disables its DATA line. The second PROM recognizes the Low level on its CE input and enables its DATA output. See Figure5.After configuration is complete, the address counters of all cascaded PROMs are reset if the PROM OE/RESET pin goes Low.To reprogram the FPGA with another program, the DONE line goes Low and configuration begins where the address counters had stopped. In this case, avoid contention between DATA and the configured I/O use of DIN.Figure 5: (a) Master Serial Mode (b) Virtex Select MAP Mode (c) Spartan XL Express Mode5V Tolerant I/OsThe I/Os on each re-programmable PROM are fully 5V tol-erant even through the core power supply is 3.3 volts. This allows 5V CMOS signals to connect directly to the PROM inputs without damage. In addition, the 3.3V V CC power supply can be applied before or after 5V signals are applied to the I/Os. In mixed 5V/3.3V/2.5V systems, the user pins,the core power supply (V CC ), and the output power supply (V CCO ) may have power applied in any order. This makes the PROM devices immune to power supply sequencing issues.Reset ActivationOn power up, OE/RESET is held low until the XC1800 is active (1ms) and able to supply data after receiving a CCLK pulse from the FPGA. OE/RESET is connected to an exter-nal resistor to pull OE/RESET HIGH releasing the FPGA INIT and allowing configuration to begin. OE/RESET is held low until the XC1800 voltage reaches the operating voltage range. If the power drops below 2.0 Volts, the PROM will reset.Standby ModeThe PROM enters a low-power standby mode whenever CE is asserted High. The output remains in a high imped-ance state regardless of the state of the OE input. JTAG pins TMS, TDI and TDO can be 3-state or high.Note:TC = Terminal Count = highest address value. TC+1 = address 0.Table 6: Truth Table for PROM Control InputsControl Inputs Internal AddressOutputsOE/RESET CE DATA CEO I cc Low Low if address < TC: increment if address > TC: don’t change active 3-state High Low active reduced High Low Held reset 3-state High active Low High Held reset 3-state High standby HighHighHeld reset3-stateHighstandbyAbsolute Maximum RatingsSymbol Description Value Units V CC Supply voltage relative to GND-0.5 to +4.0VV IN Input voltage with respect to GND-0.5 to +5.5VV TS Voltage applied to 3-state output-0.5 to +5.5VT STG Storage temperature (ambient)-65 to +150°CT SOL Maximum soldering temperature (10 s @ 1/16 in.)+260°CT J Junction Temperature+150°C Notes1: Maximum DC undershoot below GND must be limited to either 0.5V or 10mA, whichever is easier to achieve. During transitions, the device pins may undershoot to -2.0V or overshoot to +7.0V, provided this over- or undershoot lasts less then10 ns and with the forcing current being limited to 200mA.2:Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those listed under OperatingConditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect devicereliability.Recommended Operating ConditionsSymbol Parameter Min Max Units V CCINT Commercial Internal Voltage supply (T A = 0°C to +70°C) 3.0 3.6V Industrial Internal Voltage supply (T A = -40°C to +85°C) 3.0 3.6V V CCO Supply voltage for output drivers for 3.3V operation 3.0 3.6V Supply voltage for output drivers for 2.5V operation 2.3 2.7V V IL Low-level input voltage00.8V V IH High-level input voltage 2.0 5.5V V O Output voltage0V CCO V Quality and Reliability CharacteristicsSymbol Description Min Max Units t DR Data Retention10-Years N PE Program/Erase Cycles (Endurance)10,000-Cycles V ESD Electrostatic Discharge (ESD)2,000-Volts* 1801/18512/18256/18128 only, cascadable**1801/18512/18256/18128 only, non-cascadableSymbol ParameterTest Conditions Min MaxUnits V OHHigh-level output voltage for 3.3 V outputs I OH = -4 mA 2.4V High-level output voltage for 2.5 V outputsI OH = -500 µA 90% V CCOV V OLLow-level output voltage for 3.3V outputs I OL = 8 mA 0.4V Low-level output voltage for 2.5V outputsI OL = 500 µA 0.4V I CCA Supply current, active mode at maximum frequency30.0mA I CCS1Supply current, standby mode 1 2.0mA I CCS2*Supply current, standby mode 2300µA I CCS3**Supply current, standby mode 3100µA I ILJ JTAG pins TMS, TDI, and TDO V CC = MAX V IN = GND -100µA I IL Input leakage currentV CC = MaxV IN = GND or V CC -10.010.0µA I IHInput & Output high-Z leakage current V CC = MaxV IN = GND or V CC -10.010.0µA C IN & C OUTInput and Output CapacitanceV IN = GND f = 1.0 MHz10.0pFSymbol Description Min Max Units 1T OE OE to Data Delay30ns 2T CE CE to Data Delay45ns 3T CAC CLK to Data Delay45ns 4T OH Data Hold From CE, OE, or CLK0ns 5T DF CE or OE to Data Float Delay250ns 6T CYC Clock Periods67ns 7T LC CLK Low Time325ns 8T HC CLK High Time325ns 9T SCE CE Setup Time to CLK (to guarantee proper counting)25ns 10T HCE CE Hold Time to CLK (to guarantee proper counting)0ns 11T HOE OE Hold Time (guarantees counters are reset)25nsNotes:1.AC test load = 50 pF2.Float delays are measured with 5 pF AC loads. Transition is measured at +/- 200mV from steady state active levels.3.Guaranteed by design, not tested.4.All AC parameters are measured with V IL = 0.0 V and V IH = 3.0 V.AC Characteristics Over Operating Condition When CascadingNotes:1.AC test load = 50 pF2.Float delays are measured with 5 pF AC loads. Transition is measured at +/- 200mV from steady state active levels.3.Characterized but not 100% tested.4.All AC parameters are measured with V IL = 0.0 V and V IH = 3.0 V.Symbol DescriptionMin Max Units 12T CDF CLK to Data Float Delay 2, 350ns 13T OCK CLK to CEO Delay 330ns 14T OCE CE to CEO Delay 335ns 15T OOERESET/OE to CEO Delay 330nsCLKDATACECEORESET/OEOrdering InformationValid Ordering CombinationsMarking InformationRevision ControlXC1804VQ44C XC1802VQ44C XC1801SO20C XC18512SO20C XC18256SO20C XC18128SO20C XC1804PC44C XC1802PC44C XC1801PC20C XC18512PC20C XC18256PC20C XC18128PC20C XC1804VQ44I XC1802VQ44I XC1801SO20I XC18512SO20I XC18256SO20I XC18128SO20I XC1804PC44IXC1802PC44IXC1801PC20IXC18512PC20IXC18256PC20IXC18128PC20IDate Version Revision2/9/99 1.0First publication of this early access specification 8/23/99 1.1Edited text, changed marking, added CF and parallel load 9/1/99 1.2Corrected JTAG order, Security and Endurance data.9/16/991.3Corrected SelectMAP diagram, control inputs, reset polarity. Added JTAG and CF description, 256 Kbit and 128 Kbit devices.XC1804 VQ44 COperating Range/Processing C =Commercial(T A= 0° to +70°C)I=Industrial (T A = –40° to +85°C)Package TypeVQ44=44-Pin Plastic Quad Flat Package PC44=44-Pin Plastic Chip Carrier SO20=20-Pin Small-Outline PackagePC20=20-Pin Plastic Leaded Chip CarrierDevice NumberXC1804XC1802XC1801XC18512XC18256XC18128XC1804 VQ44 COperating Range/ProcessingC =Commercial (T A = 0° to +70°C)I =Industrial (T A = –40° to +85°C)Package TypeVQ44=44-Pin Plastic Quad Flat Package PC44=44-Pin Plastic, Leaded Chip CarrierDevice NumberXC1804XC18021801 S COperating Range/ProcessingC =Commercial (T A = 0° to +70°C)I =Industrial (T A = –40° to +85°C)Package TypeS=20-Pin Small-Outline Package J=20-Pin Plastic Leaded Chip CarrierDevice NumberXC1801XC18512XC18256XC1812820-Pin Package44-Pin Package。

集成电路中英文对照

表面贴装集成电路SURFACE MOUNT INTEGRATED CIRCUITTYPE NO. FUNCTIONPIN TYPE NO. FUNCTIONPIN LM358 单电源通用型双运放8 UC3843 脉宽调制8/14 UPC1251 单电源通用型双运放(工业级) 8 UC3844 脉宽调制(开关电源) 14 LM741 单运放(通用型)8 LM317 三端可调(1.25~37V ) 8 UPC258 双运放(通用型)(工业级) 8 LM337 三端可调(1.25~37V ) 8 LM1458 双运放(通用型) 8 LM385 基准二极管(1.25V,2.5V) 8 LM4558 双运放(通用型) 8 78L05 三端稳压5V/100MA 3/8 LM324 单电源四运放14 78DS05 三端稳压5V/30MA(低压差) 3 UPC451 单电源四运放(工业级) 14 78L06 三端稳压6V/100MA 3 LM3403 单电源四运放 14 78L09 三端稳压9V/100MA 3 LM4741 单电源四运放 14 78L12 三端稳压12V/100MA 3 LF353 BI-GET 输入型双运放 8 79L05 三端稳压-5V/100MA 3 TL061 低功耗JFET 输入单远放 8 79L06 三端稳压-6V/100MA 3 TL062 低功耗JFET 输入双远放 8 79L09 三端稳压-9V/100MA 3 TL064 低功耗JFET 输入四远放 14 79L12 三端稳压-12V/100MA 3 TL072 低功耗JFET 输入双远放 8 78M05 三端稳压5V/500MA 3 TL074 低功耗JFET 输入四远放 14 78D05 三端稳压5V/500MA(低压差) 3 MC34074 高性能、单电源四远放 14 78M12 三端稳压12V/500MA 5 TL081 BEJFET 输入单远放 8 79M05 三端稳压-5V/500MA 3 TL082 BJ-JFET 输入双远放 8 79M12 三端稳压-12V500MA 3 TL084 BJ-JFET 输入四远放 14 A1600 单调MOSFET 陈列*8 16 UPC4572 高性能双远放 8 MC1403 精密基准二极管2.5V 8 UPC4574 高性能四远放 14 MC34063 开关电源 8 LM339 四电压比较器 14 MC34064 欠压传感电路 8 LM393 双电压比较器8 CD4001 二输入端四或非门 14 UPC277 双电压比较器(工业级) 8 CD4007 双互补对加倒相器 14 LM311 通用比较器(单) 8 CD4011 二输入端四与非门 14 LM319 高速双比较器8 CD4013 双D 触发器 14 LM2901 四电压比较器(-20℃~) 14 CD4016 四与向模拟开关 14 LM2902 单电源四运放(-20℃~) 14 CD4017 十进制计数/分配器 16 LM2903 双电压比较器(-20℃~) 8 CD4019 四与或选择器 16 LM2904 双电压比较器(-20℃~) 8 CD4021 八位静态移位寄存器 16 7660 电源变换器 8 CD4027 双J-K 触发器 16 LM386 功率放大 8 CD4028 BCD 十进制译码器 16 LM555 时基电路 8 CD4030 四异或门14 LMC555 COMS 时基电路 8 CD4040(HC) 四R/S 锁存器(与非三态) 14 LM556 双时基电路 14 CD4043 四R/S 锁存器(与非三态) 14 TLC556 CMOS 双时基电路 14 CD4046 锁相环16 TL431 可调三端 3/8 CD4049 六反相缓冲器/转换器 16 TL1451 双脉宽调制控制 16 CD4050(HC) 六同相缓冲器/转换器 16 D4990 串行I/O 实时时钟 16 CD4051 八选一模拟开关 16 OP07 低失调电压型运放 8 CD4052 双四选一模拟开关 16 OP27 低噪声低失调电压型运放 8 CD4053 三组二路双向模拟开关 16 OP37 低噪声低失调电压型运放(高速) 8 CD4060 14位串行二进制计数/分频/振荡 14 OP177 低失调电流型运放 8 CD4066 四双向模拟开关 14 7106 3 1/2DVM 用A/D 液晶 44 CD4069 六反相器 14 7107 3 1/2DVM 用A/D 数码管44 CD4070 四异或门 14 7117 3 1/2DVM 用A/D 数码管(HCLD ) 44 CD4071 二输入端四或门 14 D7554 4-Bit 单片机 20 CD4081 二输入端四或门14 MN1035 运放 8 CD4093 二输入端四与非史密特触发器 14 NJM318 高速单运放 8 CD4094 八位移位存储总线寄存器 16 TA76494 开关式稳压源 16 CD4512 八通道数据选择器 16 TL494 开关式稳压源 16 CD4516 二进制四位可逆计数器 16 MB3759 开关式稳压源 16 CD4518 双BCD 加法计数器 16 UC3842脉宽调制14CD4520双二进制加法计数器16表面贴装集成电路SURFACE MOUNT INTEGRATED CIRCUIT。

at89s52封装

AT89S52封装简介AT89S52是一款高性能、低功耗的8位单片机,由Atmel 公司生产。

它基于MCS-51体系结构,并且被广泛应用于嵌入式系统、工业控制和电子设备中。

该单片机的封装种类多样,根据不同的应用需求和布局要求,用户可以选择合适的封装类型。

主要封装类型1.DIP40封装–DIP40(双列直插式40引脚)封装是较为常见的一种封装类型。

它采用了直插式引脚布局,方便用户在开发过程中插拔。

这种封装类型适合需要频繁更换芯片的应用场景。

2.PLCC44封装–PLCC44(可编程逻辑器件载波式44引脚)封装是一种表面安装封装类型。

它采用了载波式布局,适用于自动化生产线进行批量焊接。

这种封装类型针对大规模生产的需求,减少了人工操作环节。

3.QFP44封装–QFP44(矩形薄膜引脚44引脚)封装是另一种表面安装封装类型。

它采用了薄膜引脚布局,与PLCC44封装类似,适用于自动化生产线。

QFP44封装在同样的尺寸下,引脚数目更多,能提供更多的I/O接口。

4.LQFP44封装–LQFP44(低型薄膜引脚44引脚)封装是LQFP封装系列的一种。

与QFP封装相比,它具有更低的外延和较小的封装尺寸。

LQFP44封装也适用于密集布线的高引脚密度应用。

封装选择建议•如果您的应用需要频繁更换芯片,建议选择DIP40封装,这样可以方便插拔。

•如果您的应用需要批量生产和焊接,建议选择PLCC44封装,它适合自动化生产线。

•如果您需要更多的I/O接口和较小的封装尺寸,可以选择QFP44或LQFP44封装。

封装尺寸图示下图展示了AT89S52不同封装类型的尺寸和引脚布局示意图:封装示意图封装示意图结论根据不同的应用需求和布局要求,我们可以选择合适的AT89S52封装类型。

对于需要方便插拔的应用,可以选择DIP40封装;对于大规模生产的需求,可以选择PLCC44封装;而对于高引脚密度和较小封装尺寸的应用,可以选择QFP44或LQFP44封装。

第一篇2

第一篇贴装元器件封装命名清单1总则本文件作为“封装命名规范--贴装元器件部分”的第一篇,列出了贴装元器件的封装名称。

其他说明:z SF、SX、SPL、SRN、STC、QFP、SFLT的封装命名中涉及尺寸的特征参数采用了公制单位(mm)。

z封装命名中的“补充描述”项用于描述前面的关键特征参数所不足以描述的内容,如引脚外展式IC的管脚长度差异。

2贴装电容 SC(不含贴装钽电容)封装命名规则:SC 0402| || 贴装电容 | 器件大小SMD-Capacitor 0402=40mil x 20mil贴装电容的封装名称:SC0402SC0603SC0805SC1206SC1210SC1808 SC1812SC1825SC2220SC22253贴装二极管(含发光二极管) SD封装命名规则:SD 0805| || 贴装二极管 | 器件大小SMD-Diode 0805=80mil x 50mil1714=170mil x 140mil贴装二极管、发光二极管的封装名称:SD0805SD1206SD1714SD27234贴装保险管(含管座) SF封装命名规则:SF 6127 H| | || 贴装保险管 | 器件大小 | 属性描述SMD-Fuse 6127=6.1mm x 2.7mm H=Holder(座、支架)贴装保险管、座的封装名称:SF6127SF9750H5贴装电感 SL(不含贴装功率电感)封装命名规则:SL 0603| || 贴装电感 | 器件大小SMD-L 0603= 60mil x 30mil贴装电感的封装名称:SL0603SL0805SL0906SL1008SL1206SL1210SL1810SL1812 SL22206贴装电阻 SR封装命名规则:SR 0402| || 贴装电阻 | 器件大小SMD-Resistor 0402= 40mil x 20mil贴装电阻的封装名称:SR0402SR0603SR0805SR1206SR1210SR2010SR2512SR3218SR47327贴装晶体(含晶体振荡器) SX封装命名规则:SX 4 - 1210 A| | | || 贴装晶体 | PIN数 | 器件大小 | 补充描述SMD-X 1210=12mm x 10mm贴装晶体的封装名称:SX4-0805SX4-1210SX6-12108贴装二极管阵列(含发光二极管阵列) SDA(暂缺数据)9小外形晶体管 SOT封装命名规则:SOT 23 - 1 A| | | || 小外形晶体管 | 封装代号 | 管脚排列分类 | 补充描述Small-Outline-Transistor小外形晶体管的封装名称:SOT23-1SOT23-1A SOT23-1B SOT23-2SOT23-2ASOT23-2B SOT89SOT89A SOT143 SOT223SOT25210贴装功率电感 SPL封装命名规则:SPL 0505| || 贴装功率电感 | 器件大小SMD-Power-L 0505=5mm x 5mm贴装功率电感的封装名称:SPL0404SPL0505SPL0707SPL0604SPL1209SPL1815 11贴装阻排 SRN封装命名规则:SRN 8 - 1608| | || 贴装阻排 | PIN数 | 特征参数SMD-Resistor-Net 16:体宽=1.6mm08:PIN间距=0.8mm贴装阻排的封装名称:SRN8-1608SRN8-2012SRN8-3212SRN10-1606SRN10-321212贴装钽电容 STC封装命名规则:STC 3216| || 贴装钽电容 | 器件大小SMD-Tantalum-Capacitor 3216=3.2mm x 1.6mm贴装钽电容的封装名称:STC3216STC3528STC6032STC734313球栅阵列 BGA封装命名规则:BGA 117 - 40 - 1111 A| | | | || 球栅阵列 | PIN数 | PIN间距 | 阵列大小 | 补充描述Ball-Grid-Array 缺省=50mil 1111=11行x11列40=40mil球栅阵列的封装名称:BGA121-1111BGA256-1616BGA256-2020BGA268-2020BGA292-2020BGA304-2323BGA340-2626BGA352-2626BGA356-2626BGA357-1919BGA360-1919BGA388-2626BGA432-3131BGA452-262614四方扁平封装IC QFP封装命名规则:QFP 44 A - 080 - 1010 L| | | | | || 四方扁平封装IC | PIN数 | 分类 | PIN间距 | 实体面积 | 管脚排列Quad-Flat-Package-IC 080=0.80mm 1010= 10mmx10mm L=left063=0.63mm M=mid 四方扁平封装IC的封装名称:QFP32-080-0707L QFP44-080-1010L QFP44A-080-1010 QFP44-080-1010MQFP44A-080-1010M QFP48-050-0707L QFP48-080-1010L QFP48-080-1212LQFP52-065-1010L QFP52A-065-1010L QFP52-065-1010M QFP52A-065-1010MQFP64-050-1010L QFP64-080-1414L QFP64A-080-1414L QFP80-065-1414LQFP80-080-1420L QFP100-050-1414L QFP100-050-1414M QFP100-063-1919LQFP100-063-1919M QFP100-065-2020L QFP100-065-2020M QFP100-065-1420LQFP120-040-1414L QFP128-050-1420L QFP128-080-2828L QFP132-063-2222LQFP132-063-2222M QFP144-050-2020L QFP160-065-2828L QFP208-050-2828LQFP208-050-3232L QFP240-050-3232L15J引线小外形封装IC SOJ(不含引脚外展式IC)封装命名规则:SOJ 26 - 50 - 300 A| | | | || J引线小外形封装IC | PIN数 | PIN间距 | 实体体宽 | 补充描述Small-Outline-package 50=50mil 300=300milIC of J-leadJ引线小外形封装IC的封装名称:SOJ20-50-300SOJ26-50-300SOJ28-50-300SOJ28-50-400 SOJ32-50-300SOJ32-50-400SOJ36-50-400SOJ40-50-400 SOJ42-50-400SOJ44-50-40016小外形封装IC SOP封装命名规则:SOP 20 - 25 - 150 A| | | | || 小外形封装IC | PIN数 | PIN间距 | 实体体宽 | 补充描述Small-Outline-Package-IC 25=25mil 150=150mil小外形封装IC的封装名称:SOP8-26-150SOP8-26-173SOP8-26-208SOP8-50-150SOP8-50-173SOP8-50-208SOP14-16-173SOP14-26-173SOP14-26-208SOP14-50-150SOP14-50-173SOP14-50-208SOP16-16-173SOP16-25-150SOP16-26-173SOP16-26-208SOP16-50-150SOP16-50-208SOP16-50-300 SOP18-50-300SOP20-16-173SOP20-25-150SOP20-26-173SOP20-26-208SOP20-50-208SOP20-50-300SOP20-50-433 SOP24-16-173SOP24-25-150SOP24-26-173SOP24-26-208SOP24-50-208SOP24-50-300SOP28-25-150SOP28-26-173SOP28-26-208SOP28-50-300SOP28-50-350SOP28-50-400SOP30-26-300SOP30-40-300SOP32-20-720SOP32-50-400SOP36-32-208SOP40-20-720SOP44-50-520SOP48-16-173SOP48-20-250SOP48-20-720SOP48-25-300SOP48-26-300SOP50-32-400SOP56-16-173SOP56-20-250SOP56-25-300SOP56-32-520 SOP64-20-250SOP86-20-40017塑封有引线载体(含插座) PLCC封装命名规则:PLCC 20 - X S| | | || 塑封有引线芯片载体 | PIN数 | PIN间距 | 器件特征Plastic-Leaded-Chip-Carrier 缺省=50mil S-方形 R-长方形贴装塑封有引线载体的封装名称:PLCC20S PLCC28S PLCC28R PLCC32RPLCC44S PLCC52S PLCC68S PLCC84S 18贴装滤波器 SFLT封装命名规则:SFLT 10 - 0905 - A| | | || 贴装滤波器 | PIN数 | 实体面积 | 补充描述SMD-Filter 0905=9mm x 5mm贴装滤波器的封装名称:SFLT2-0504SFLT2-0606SFLT2-0704SFLT3-0706SFLT4-0504SFLT6-0404SFLT8-0302SFLT8-0303SFLT10-0905SFLT10-090719贴装锁相环 SPLL封装命名规则:SPLL 28 - 50 - 300 A| | | | || 贴装锁相环 | PIN数 | PIN间距 | 实体体宽 | 补充描述SMD-Phase-Locked-Loop 50=50mil 300=300mil贴装锁相环的封装名称:SPLL28-50-30020贴装电位器 SPOT封装命名规则:SPOT 3 - 45 - 190| | | || 贴装电位器 | PIN数 | PIN间距 | 实体体宽SMD-Potentiometer 45=45mil 190=190mil贴装电位器的封装名称:SPOT3-45-190SPOT3-52-18021贴装继电器 SRLY封装命名规则:SRLY 10 - 100 - 350 A| | | | || 贴装继电器 | PIN数 | PIN间距 | 实体体宽 | 补充描述SMD-Relay 100=100mil 350=350mil贴装继电器的封装名称:SRLY6-100-173SRLY8-100-173SRLY10-100-35022贴装变压器 STFM封装命名规则:STFM 16 - 100 - 400| | | || 贴装变压器 | PIN数 | PIN间距 | 实体体宽SMD-TRansformer 100=100mil 400=400mil贴装变压器的封装名称:STFM6-100-275STFM10-100-600STFM12-100-450STFM16-50-280 STFM16-100-400STFM16-100-600STFM32-50-300STFM40-50-480。

倍福PLC卡件介绍

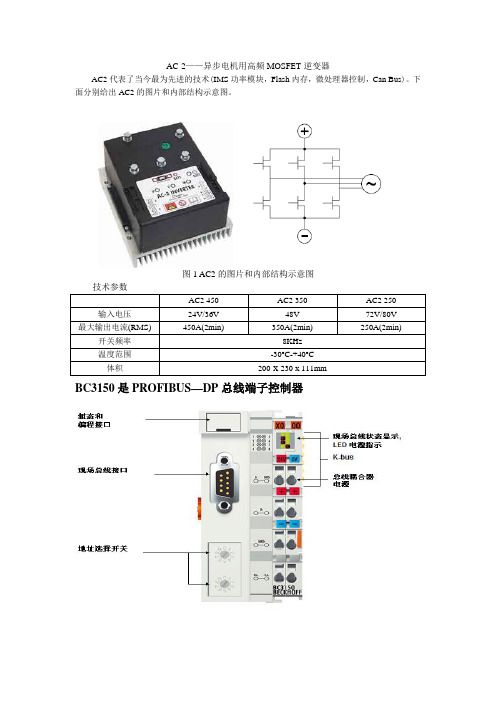

AC-2——异步电机用高频MOSFET逆变器AC2代表了当今最为先进的技术(IMS功率模块,Flash内存,微处理器控制,Can Bus)。

下面分别给出AC2的图片和内部结构示意图。

图1 AC2的图片和内部结构示意图BC3150是PROFIBUS—DP总线端子控制器总线端子控制器是带 PLC 控制功能的总线耦合器。

控制器有一个 PROFIBUS-DP 现场总线接口,可在 PROFIBUS-DP 系统中作为智能从站使用。

“紧凑型”总线端子控制器 BC3150 比较小巧而且经济。

BC3150 通过 K-BUS 总线扩展技术,可连接多达 255 个总线端子。

PROFIBUS 控制器自动检测波特率,最大可至 12 M波特率,使用两个地址选择开关分配地址。

总线端子控制器使用符合 IEC 61131-3 标准的 TwinCAT 进行编程。

组态和编程接口用于装载 PLC 程序,如果使用软件 PLC TwinCAT,则其 PLC 程序也可通过现场总线装载。

所连接的总线端子的输入/输出在 PLC 的缺省设置中被赋值。

可对每个总线端子进行配置,使其直接通过现场总线实现与上层控制单元的数据交换。

同样,预处理的数据也可通过现场总线实现总线端子控制器和上层控制器之间的数据交换。

BK3150是PRORIBUS—DP总线端子耦合器PROFIBUS-DP “紧凑型”总线耦合器 BK3150 扩展了 Beckhoff 总线端子系统,比较小巧而经济。

可以连接多达 64 个总线端子;若采用端子总线扩展技术,则可连接多达 255 个总线端子。

PROFIBUS 总线耦合器具有自动波特率检测功能,速率最大可以达到 12 Mbaud ,2 个地址选择开关用作地址分配。

对于现场总线连接,有提供 1 个 D-sub9 针接口,用于订货号为 ZS1031-3000 或 ZB3100 的 PROFIBUS 接头。

CX1020-0xxx 基本 CPU 模块CX1020 基本 CPU 模块通过一个功能更为强大的 1GHz Intel® M CPU 对现有CX1000 系列产品进行了扩展。

CM44中文技术资料

通信和数据处理 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14 可靠性 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

通信规范参数 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

HART . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . PROFIBUS DP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Modbus RS485 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Modbus TCP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Web 服务器 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23 23 23 24 24

有源电流输出 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

富士PLC培训教材

指示灯含义

No. Color Display POW Green Power

ALM Red Error

RUN RDY CN1 CN2 CN3 CN4 CN5 CN6 CN7 CN8

Green Green Yellow Yellow Yellow Yellow Yellow Yellow Yellow Yellow

型号 NC1B02 ~ NC1B10 NC1S-1 NC1S-2 NC1S-4 NC1P-S / NC1P-E SERISES NC1ET 单对屏蔽双绞线(通常用9463) I/O模块、各种功能模块 NH5F-COOTL17<10013-C10>

F70S 地址设置( 1 )

1600 points

Channel (link) No. 0

In operation Ready for communication Connection status of connection no.1 Connection status of connection no.2 Connection status of connection no.3 Connection status of connection no.4 Connection status of connection no.5 Connection status of connection no.6 Connection status of connection no.7 Connection status of connection no.8

Powers

0

Supply Unit

CPU

Optional

Card

F

10

20

30

IC知识

IC产品认识大部分IC产品型号的开头字母,也就是通常所说的前缀都是为生产厂家的前两个或前三个字母,比如:MAXIM公司的以MAX为前缀,AD公司的以AD为前缀,ATMEL公司的以AT为前缀,CY公司的以CY为前缀,像AMD,IDT,LT,DS,HY这些公司的IC产品型号都是以生产厂家的前两个或前三个为前缀。

但也有很多生产厂家不是这样的,如TI的,一般以SN,TMS,TPS,TL,TLC,TLV等字母为前缀;ALTERA(阿尔特拉)、XILINX(赛灵斯或称赛灵克斯)、Lattice(莱迪斯),称为可编程逻辑器件CPLD、FPGA。

ALTERA的以EP,EPM,EPF为前缀,它在亚洲国家卖得比较好,XILINX的以XC为前缀,它在欧洲国家卖得比较好,功能相当好。

Lattice一般以M4A,LSP,LSIG为前缀,NS的以LM为前缀居多等等,这里就不一一做介绍了。

紧跟前缀后面的几位字母或数字一般表示其系列及功能,每个厂家规则都不一样,这里不做介绍,之后跟的几位字母(一般指的是尾缀)表示温度系数和管脚及封装,一般情况下,C 表示民用级,I表示工业级,E表示扩展工业级,A表示航空级,M表示军品级下面几个介比较具有代表性的生产厂家,简单介绍一下:AMD公司FLASH常识:AM29LV 640 D(1) U(2) 90R WH(3) I(4)1:表示工艺:B=0.32uM C=0.32uM thin-film D=0.23uM thin-film G=0.16uM thin-film M=MirrorBit 2:表示扇区方式:T=TOP B=BOTTOM H=Unifom highest address L=Unifom lowest address U、BLANK=Unifom 3:表示封装:P=PDIP J=PLCC S=SOP Z=SSOP E/F=TSSOP M/P/W=FPGA4:温度范围C=0℃TO+60℃ I=-40℃TO+85℃ E=-55TO℃+85℃MAXIMMAXIM产品命名信息(专有命名体系)MAXIM推出的专有产品数量在以下相当可观的速度增长.这些器件都按以功能划分的产品类别进行归类。