bq2058MSN中文资料

ADC0808S125资料

CLOCK DRIVER

ADC0808S

LATCH

17 26

CCS CCSSEL

IN INN

33 32

TRACK AND HOLD

8

RESISTOR LADDERS

ADC CORE

LATCH

8

D0 to D7 21 OTC

FSIN/ REFSEL

30 U/I LATCH

20

IR

INTERNAL REFERENCE

元器件交易网

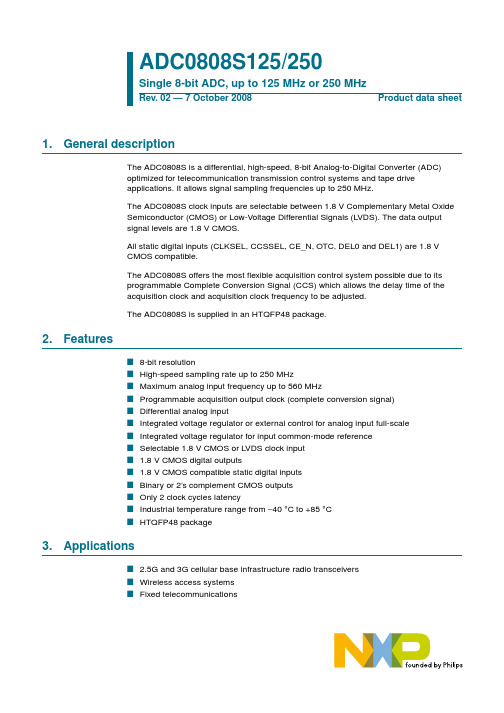

ADC0808S125/250

Single 8-bit ADC, up to 125 MHz or 250 MHz

Rev. 02 — 7 October 2008 Product data sheet

1. General description

The ADC0808S is a differential, high-speed, 8-bit Analog-to-Digital Converter (ADC) optimized for telecommunication transmission control systems and tape drive applications. It allows signal sampling frequencies up to 250 MHz. The ADC0808S clock inputs are selectable between 1.8 V Complementary Metal Oxide Semiconductor (CMOS) or Low-Voltage Differential Signals (LVDS). The data output signal levels are 1.8 V CMOS. All static digital inputs (CLKSEL, CCSSEL, CE_N, OTC, DEL0 and DEL1) are 1.8 V CMOS compatible. The ADC0808S offers the most flexible acquisition control system possible due to its programmable Complete Conversion Signal (CCS) which allows the delay time of the acquisition clock and acquisition clock frequency to be adjusted. The ADC0808S is supplied in an HTQFP48 package.

RJ-051.8SH资料

0515

3.315

15.000 10.000 5.000 0.000 -5.000 -10.000

3.305

0505

15.000 10.000 5.000 0.000 -5.000 -10.000

3.309

0509

1215

1205

1209

0% 20% 40% 60% Total Output current (%)

100 80 60 100

RJ-xx12S

Efficiency / Load

80 60

3.305

1205

0509

0512

1212

0505 Efficiency %

40 20 0

1209 Efficiency % 3.309

Efficiency %

40 20 0

3.312

20 0

0% 20% 40% 60% Total Output current (%)

Input Voltage Range Output Voltage Accuracy Line Voltage Regulation Load Voltage Regulation (10% to 100% full load) Output Ripple and Noise (20MHz limited) Operating Frequency Efficiency at Full Load No Load Power Consumption Isolation Voltage Rated Working Voltage Isolation Voltage Rated Working Voltage Isolation Capacitance Isolation Resistance Short Circuit Protection P-Suffix Operating Temperature Range (free air convection) Storage Temperature Range Relative Humidity Package Weight H-Suffix H-Suffix (tested for 1 second) (long term isolation) (tested for 1 second) (long term isolation) 1.8V, 3.3V output types 5V output type 9V, 12V, 15V, 24V output types ±10% ±5% 1.2%/1% of Vin typ. 20% max. 15% max. 10% max. 100mVp-p max. 57kHz min. / 90kHz typ. / 105kHz max. 70% min. / 80% typ. 102mW min./180mW typ./260mW max. 3000VDC min. see Application Notes. 4000VDC min. see Application Notes

LM78M12中文资料

LM78M12中⽂资料LM341/LM78MXX Series3-Terminal Positive Voltage RegulatorsGeneral DescriptionThe LM341and LM78MXX series of three-terminal positive voltage regulators employ built-in current limiting,thermal shutdown,and safe-operating area protection which makes them virtually immune to damage from output overloads.With adequate heatsinking,they can deliver in excess of 0.5A output current.Typical applications would include local (on-card)regulators which can eliminate the noise and de-graded performance associated with single-point regulation.Featuresn Output current in excess of 0.5A n No external componentsn Internal thermal overload protection n Internal short circuit current-limitingn Output transistor safe-area compensationnAvailable in TO-220,TO-39,and TO-252D-PAK packagesn Output voltages of 5V,12V,and 15VConnection DiagramsTO-39Metal Can Package (H)DS010484-5Bottom ViewOrder Number LM78M05CH,LM78M12CH or LM78M15CHSee NS Package Number H03ATO-220Power Package (T)DS010484-6Top ViewOrder Number LM341T-5.0,LM341T-12,LM341T-15,LM78M05CT,LM78M12CT or LM78M15CTSee NS Package Number T03BTO-252DS010484-19Top ViewOrder Number LM78M05CDT See NS Package Number TD03BJuly 1999LM341/LM78MXX Series 3-Terminal Positive Voltage Regulators1999National Semiconductor Corporation /doc/96ef4d46852458fb770b5641.htmlAbsolute Maximum Ratings(Note1)If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.Lead Temperature(Soldering,10seconds)TO-39Package(H)300?C TO-220Package(T)260?C Storage Temperature Range?65?C to+150?C Operating Junction TemperatureRange?40?C to+125?C Power Dissipation(Note2)Internally Limited Input Voltage5V≤V O≤15V35V ESD Susceptibility TBDElectrical CharacteristicsLimits in standard typeface are for T J=25?C,and limits in boldface type apply over the?40?C to+125?C operating temperature range.Limits are guaranteed by production testing or correlation techniques using standard Statistical Quality Control(SQC) methods.LM341-5.0,LM78M05CUnless otherwise specified:V IN=10V,C IN=0.33µF,C O=0.1µFSymbol Parameter Conditions Min Typ Max Units V O Output Voltage I L=500mA 4.8 5.0 5.2V5mA≤I L≤500mA 4.75 5.0 5.25P D≤7.5W,7.5V≤V IN≤20VV R LINE Line Regulation7.2V≤V IN≤25V I L=100mA50mVI L=500mA100V R LOAD Load Regulation5mA≤I L≤500mA100I Q Quiescent Current I L=500mA410.0mA ?I Q Quiescent Current Change5mA≤I L≤500mA0.57.5V≤V IN≤25V,I L=500mA 1.0V n Output Noise Voltage f=10Hz to100kHz40µVElectrical CharacteristicsLimits in standard typeface are for T J=25?C,and limits in boldface type apply over the?40?C to+125?C operating temperature range.Limits are guaranteed by production testing or correlation techniques using standard Statistical Quality Control(SQC) methods.(Continued)LM341-12,LM78M12CUnless otherwise specified:V IN=19V,C IN=0.33µF,C O=0.1µFSymbol Parameter Conditions Min Typ Max UnitsV O Output Voltage I L=500mA11.51212.5V5mA≤I L≤500mA11.41212.6P D≤7.5W,14.8V≤V IN≤27VV R LINE Line Regulation14.5V≤V IN≤30V I L=100mA120mVI L=500mA240V R LOAD Load Regulation5mA≤I L≤500mA240I Q Quiescent Current I L=500mA410.0mAI Q Quiescent Current Change5mA≤I L≤500mA0.514.8V≤V IN≤30V,I L=500mA 1.0V n Output Noise Voltage f=10Hz to100kHz75µVRipple Rejection f=120Hz,I L=500mA69dBV IN Input Voltage Required I L=500mA17.6V to Maintain Line RegulationV O Long Term Stability I L=500mA60mV/khrs Note1:Absolute maximum ratings indicate limits beyond which damage to the component may occur.Electrical specifications do not apply when operating the de-vice outside of its rated operating conditions.Note2:The typical thermal resistance of the three package types is:T(TO-220)package:θ(JA)=60?C/W,θ(JC)=5?C/WH(TO-39)package:θ(JA)=120?C/W,θ(JC)=18?C/WDT(TO-252)package:θ(JA)=92?C/W,θ(JC)=10?C/W3/doc/96ef4d46852458fb770b5641.htmlSchematic DiagramDS010484-1 /doc/96ef4d46852458fb770b5641.html 4 Typical Performance CharacteristicsPeak Output CurrentDS010484-10Ripple RejectionDS010484-11Ripple RejectionDS010484-12Dropout VoltageDS010484-13Output Voltage(Normalizedto1V at T J=25?C)DS010484-14Quiescent CurrentDS010484-15/doc/96ef4d46852458fb770b5641.html 5Typical Performance Characteristics(Continued)Design ConsiderationsThe LM78MXX/LM341XX fixed voltage regulator series has built-in thermal overload protection which prevents the de-vice from being damaged due to excessive junction tem-perature.The regulators also contain internal short-circuit protection which limits the maximum output current,and safe-area pro-tection for the pass transistor which reduces the short-circuit current as the voltage across the pass transistor is in-creased.Although the internal power dissipation is automatically lim-ited,the maximum junction temperature of the device must be kept below +125?C in order to meet data sheet specifica-tions.An adequate heatsink should be provided to assure this limit is not exceeded under worst-case operating condi-tions (maximum input voltage and load current)if reliable performance is to be obtained).1.0Heatsink ConsiderationsWhen an integrated circuit operates with appreciable cur-rent,its junction temperature is elevated.It is important to quantify its thermal limits in order to achieve acceptable per-formance and reliability.This limit is determined by summing the individual parts consisting of a series of temperature rises from the semiconductor junction to the operating envi-ronment.A one-dimension steady-state model of conduction heat transfer is demonstrated in The heat generated at thedevice junction flows through the die to the die attach pad,through the lead frame to the surrounding case material,to the printed circuit board,and eventually to the ambient envi-ronment.Below is a list of variables that may affect the ther-mal resistance and in turn the need for a heatsink.R θJC (Component Variables)R θCA (Application Variables)Leadframe Size &Material Mounting Pad Size,Material,&LocationNo.of Conduction Pins Placement of Mounting Pad Die SizePCB Size &Material Die Attach MaterialTraces Length &WidthMolding Compound Size and MaterialAdjacent Heat Sources Volume of Air Air FlowAmbient Temperature Shape of Mounting PadQuiescent CurrentDS010484-16Output ImpedanceDS010484-17Line Transient Response DS010484-7Load Transient ResponseDS010484-8/doc/96ef4d46852458fb770b5641.html6Design Considerations(Continued)The LM78MXX/LM341XX regulators have internal thermal shutdown to protect the device from over-heating.Under all possible operating conditions,the junction temperature of the LM78MXX/LM341XX must be within the range of 0?C to 125?C.A heatsink may be required depending on the maxi-mum power dissipation and maximum ambient temperature of the application.To determine if a heatsink is needed,the power dissipated by the regulator,P D ,must be calculated:I IN =I L +I GP D =(V IN ?V OUT )I L +V IN I Gshows the voltages and currents which are present in the circuit.The next parameter which must be calculated is the maxi-mum allowable temperature rise,T R (max):θJA =TR (max)/P D If the maximum allowable value for θJA ?C/w is found to be ≥60?C/W for TO-220package or ≥92?C/W for TO-252pack-age,no heatsink is needed since the package alone will dis-sipate enough heat to satisfy these requirements.If the cal-culated value for θJA fall below these limits,a heatsink is required.As a design aid,Table 1shows the value of the θJA of TO-252for different heatsink area.The copper patterns that we used to measure these θJA are shown at the end of the Application Note Section.reflects the same test results as what are in the Table 1shows the maximum allowable power dissipation vs.ambi-ent temperature for theTO-252device.shows the maximum allowable power dissipation vs.copper area (in 2)for the TO-252device.Please see AN1028for power enhancement techniques to be used with TO-252package.TABLE 1.θJA Different Heatsink AreaLayoutCopper AreaThermal Resistance Top Sice (in 2)*Bottom Side (in 2)(θJA ,?C/W)TO-25210.0123010320.06608730.306040.5305450.7605261047700.284800.470900.6631000.857110157120.0660.06689130.1750.17572140.2840.28461150.3920.39255160.50.553*Tab of device attached to topside copperDS010484-23FIGURE 1.Cross-sectional view of Integrated Circuit Mounted on a printed circuit board.Note that the case temperature is measured at the point where the leadscontact with the mounting pad surface DS010484-24FIGURE 2.Power Dissipation Diagram/doc/96ef4d46852458fb770b5641.html 7Design Considerations(Continued)Typical ApplicationDS010484-20FIGURE 3.θJA vs.2oz Copper Area for TO-252DS010484-22FIGURE 4.Maximum Allowable Power Dissipation vs.Ambient Temperature for TO-252DS010484-21FIGURE 5.Maximum Allowable Power Dissipation vs.2oz.Copper Area for TO-252DS010484-9*Required if regulator input is more than 4inches from input filter capacitor (or if no input filter capacitor is used).**Optional for improved transient response./doc/96ef4d46852458fb770b5641.html 8 Physical Dimensions inches(millimeters)unless otherwise notedTO-39Metal Can Package(H)Order Number LM78M05CH,LM78M12CH or LM78M15CHNS Package Number H03A9/doc/96ef4d46852458fb770b5641.htmlPhysical Dimensions inches(millimeters)unless otherwise noted(Continued)TO-220Power Package(T)Order Number LM341T-5.0,LM341T-12,LM341T-15,LM78M05CT,LM78M12CT or LM78M15CT NS Package Number T03B/doc/96ef4d46852458fb770b5641.html 10Physical Dimensionsinches (millimeters)unless otherwise noted (Continued)LIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or systems which,(a)are intended for surgical implant into the body,or (b)support or sustain life,and whose failure to perform when properly used in accordance with instructions for use provided in the labeling,can be reasonably expected to result in a significant injury to the user.2.A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.National Semiconductor Corporation AmericasTel:1-800-272-9959Fax:1-800-737-7018Email:support@/doc/96ef4d46852458fb770b5641.htmlNational Semiconductor EuropeFax:+49(0)180-5308586Email:europe.support@/doc/96ef4d46852458fb770b5641.htmlDeutsch Tel:+49(0)180-5308585English Tel:+49(0)180-5327832Fran?ais Tel:+49(0)180-5329358Italiano Tel:+49(0)180-5341680National Semiconductor Asia Pacific Customer Response Group Tel:65-2544466Fax:65-2504466Email:sea.support@/doc/96ef4d46852458fb770b5641.htmlNational Semiconductor Japan Ltd.Tel:81-3-5639-7560Fax:81-3-5639-7507/doc/96ef4d46852458fb770b5641.htmlTO-252Order Number LM78M05CDT NS Package Number TD03BLM341/LM78MXX Series 3-Terminal Positive Voltage RegulatorsNational does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry andspecifications.。

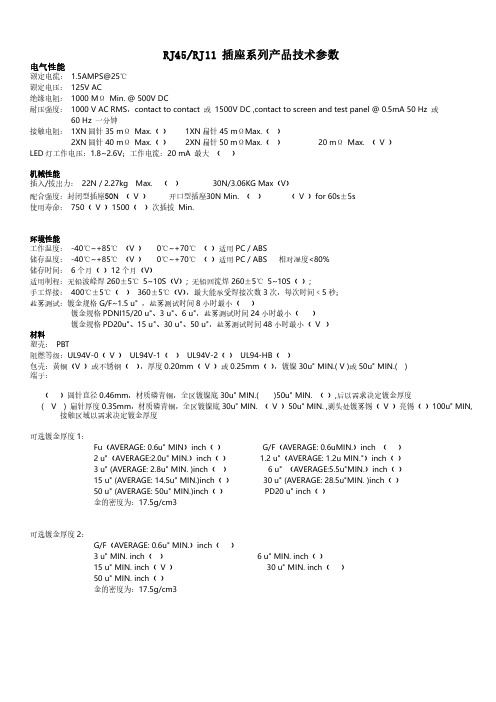

RJ45、RJ11 插座系列产品技术参数(中英文)

可选镀金厚度 1: Fu(AVERAGE: 0.6u" MIN)inch( ) 2 u"(AVERAGE:2.0u" MIN.)inch( ) 3 u" (AVERAGE: 2.8u" MIN. )inch( ) 15 u" (AVERAGE: 14.5u" MIN.)inch( ) 50 u" (AVERAGE: 50u" MIN.)inch( ) 金的密度为:17.5g/cm3

( )圆针直径 0.46mm,材质磷青铜,全区镀镍底 30u" MIN.( )50u" MIN. ( ),后以需求决定镀金厚度

( V ) 扁针厚度 0.35mm,材质磷青铜,全区镀镍底 30u" MIN. ( V )50u" MIN. ,剥头处镀雾锡( V )亮锡( )100u" MIN, 接触区域以需求决定镀金厚度

60 Hz 一分钟

接触电阻: 1XN 圆针 35 mΩ Max.( ) 1XN 扁针 45 mΩMax.( )

2XN 圆针 40 mΩ Max.( ) 2XN 扁针 50 mΩMax.( )

20 mΩ Max. ( V )

LED 灯工作电压:1.8~2.6V;工作电流:20 mA 最大 ( )

机械性能 插入/拔出力: 22N / 2.27kg Max. ( )

0.25MM, ( )

NICKEL 30u" MIN.( )OR 50u" MIN.( ) OVER ALL ( V )THICKNESS 0.35MM PHOSPHOR BRONZE ,GOLD PLATING AT CONTACT AREA, MATTE TIN AT TAIL 100 u" MIN.,

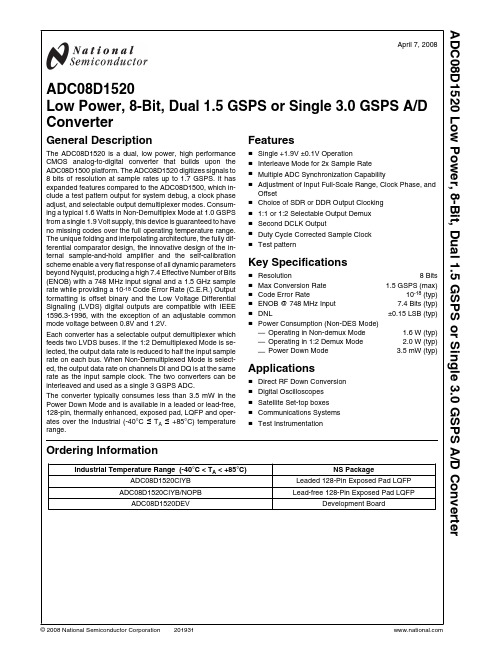

ADC08D1520资料

April 7, 2008 ADC08D1520Low Power, 8-Bit, Dual 1.5 GSPS or Single 3.0 GSPS A/D ConverterGeneral DescriptionThe ADC08D1520 is a dual, low power, high performance CMOS analog-to-digital converter that builds upon the ADC08D1500 platform. The ADC08D1520 digitizes signals to 8 bits of resolution at sample rates up to 1.7 GSPS. It has expanded features compared to the ADC08D1500, which in-clude a test pattern output for system debug, a clock phase adjust, and selectable output demultiplexer modes. Consum-ing a typical 1.6 Watts in Non-Demultiplex Mode at 1.0 GSPS from a single 1.9 Volt supply, this device is guaranteed to have no missing codes over the full operating temperature range. The unique folding and interpolating architecture, the fully dif-ferential comparator design, the innovative design of the in-ternal sample-and-hold amplifier and the self-calibration scheme enable a very flat response of all dynamic parameters beyond Nyquist, producing a high 7.4 Effective Number of Bits (ENOB) with a 748 MHz input signal and a 1.5 GHz sample rate while providing a 10-18 Code Error Rate (C.E.R.) Output formatting is offset binary and the Low Voltage Differential Signaling (LVDS) digital outputs are compatible with IE E E 1596.3-1996, with the exception of an adjustable common mode voltage between 0.8V and 1.2V.Each converter has a selectable output demultiplexer which feeds two LVDS buses. If the 1:2 Demultiplexed Mode is se-lected, the output data rate is reduced to half the input sample rate on each bus. When Non-Demultiplexed Mode is select-ed, the output data rate on channels DI and DQ is at the same rate as the input sample clock. The two converters can be interleaved and used as a single 3 GSPS ADC.The converter typically consumes less than 3.5 mW in the Power Down Mode and is available in a leaded or lead-free, 128-pin, thermally enhanced, exposed pad, LQFP and oper-ates over the Industrial (-40°C ≤ T A≤ +85°C) temperature range.Features■Single +1.9V ±0.1V Operation■Interleave Mode for 2x Sample Rate■Multiple ADC Synchronization Capability■Adjustment of Input Full-Scale Range, Clock Phase, and Offset■Choice of SDR or DDR Output Clocking■1:1 or 1:2 Selectable Output Demux■Second DCLK Output■Duty Cycle Corrected Sample Clock■Test patternKey Specifications■Resolution8 Bits ■Max Conversion Rate 1.5 GSPS (max)■Code Error Rate10-18 (typ)■ENOB @ 748 MHz Input7.4 Bits (typ)■DNL±0.15 LSB (typ)■Power Consumption (Non-DES Mode)—Operating in Non-demux Mode 1.6 W (typ)—Operating in 1:2 Demux Mode 2.0 W (typ)—Power Down Mode 3.5 mW (typ) Applications■Direct RF Down Conversion■Digital Oscilloscopes■Satellite Set-top boxes■Communications Systems■Test InstrumentationOrdering InformationIndustrial Temperature Range (-40°C < TA< +85°C)NS PackageADC08D1520CIYB Leaded 128-Pin Exposed Pad LQFPADC08D1520CIYB/NOPB Lead-free 128-Pin Exposed Pad LQFPADC08D1520DEV Development Board© 2008 National Semiconductor ADC08D1520 Low Power, 8-Bit, Dual 1.5 GSPS or Single 3.0 GSPS A/D ConverterBlock Diagram20193153 2A D C 08D 1520Pin Configuration20193101 Note: The exposed pad on the bottom of the package must be soldered to a ground plane to ensure rated performance. ADC08D1520Pin Descriptions and Equivalent CircuitsPin Functions Pin No.SymbolEquivalent CircuitDescription3OutV / SCLKOutput Voltage Amplitude and Serial Interface Clock. Tie this pin logic high for normal differential DCLK and dataamplitude. Ground this pin for a reduced differential output amplitude and reduced power consumption. See 1.1.6 The LVDS Outputs . When the Extended Control Mode isenabled, this pin functions as the SCLK input which clocks in the serial data. See 1.2 NON-EXTENDED ANDEXTENDED CONTROL MODE for details on the Extended Control Mode. See 1.3 THE SERIAL INTERFACE for description of the serial interface.29PDQPower Down Q-channel. A logic high on the PDQ pin puts only the Q-channel into the Power Down Mode.4OutEdge / DDR /SDATADCLK Edge Select, Double Data Rate Enable and Serial Data Input. This input sets the output edge of DCLK+ at which the output data transitions. See 1.1.5.2 OutEdge and Demultiplex Control Setting . When this pin is floating or connected to 1/2 the supply voltage, DDR clocking isenabled. When the Extended Control Mode is enabled, this pin functions as the SDATA input. See 1.2 NON-EXTENDED AND EXTENDED CONTROL MODE for details on the Extended Control Mode. See 1.3 THE SERIAL INTERFACE for description of the serial interface.15DCLK_RST /DCLK_RST+DCLK Reset. When single-ended DCLK_RST is selected by floating or setting pin 52 logic high, a positive pulse on this pin is used to reset and synchronize the DCLK outputs of multiple converters. See 1.5 MULTIPLE ADCSYNCHRONIZATION for detailed description. Whendifferential DCLK_RST is selected by setting pin 52 logic low,this pin receives the positive polarity of a differential pulse signal used to reset and synchronize the DCLK outputs of multiple converters.26PDPower Down Pins. A logic high on the PD pin puts the entire device into the Power Down Mode.30CALCalibration Cycle Initiate. A minimum t CAL_L input clockcycles logic low followed by a minimum of t CAL_H input clock cycles high on this pin initiates the self calibration sequence.See 2.4.2 Calibration for an overview of calibration and 2.4.2.2 On-Command Calibration for a description of on-command calibration. The calibration cycle may similarly be initiated via the CAL bit in the Calibration register (0h). 4A D C 08D 1520Pin Functions Pin No.SymbolEquivalent CircuitDescription14FSR/ALT_ECE/DCLK_RST-Full Scale Range Select, Alternate Extended Control Enable and DCLK_RST-. This pin has three functions. It canconditionally control the ADC full-scale voltage, enable the Extended Control Mode, or become the negative polarity signal of a differential pair in differential DCLK_RST mode.If pin 52 is floating or at logic high and pin 41 is floating, this pin can be used to set the full-scale-range or can be used as an alternate Extended Control Mode enable pin. When used as the FSR pin, a logic low on this pin sets the full-scale differential input range to a reduced V IN input level . A logic high on this pin sets the full-scale differential input range to a higher V IN input level. See Converter ElectricalCharacteristics. To enable the Extended Control Mode,whereby the serial interface and control registers are employed, allow this pin to float or connect it to a voltage equal to V A /2. See 1.2 NON-EXTENDED AND EXTENDED CONTROL MODE for information on the Extended Control Mode. Note that pin 41 overrides the Extended Control Mode enable of this pin. When pin 52 is held at logic low, this pin acts as the DCLK_RST- pin. When in differential DCLK_RST mode, there is no pin-controlled FSR and the full-scale-range is defaulted to the higher V IN input level.127CalDly / DES / SCSCalibration Delay, Dual Edge Sampling and Serial Interface Chip Select. In non-extended control mode, this pin functions as the Calibration Delay select. A logic high or low the number of input clock cycles after power up beforecalibration begins (See 1.1.1 Calibration ). When this pin is floating or connected to a voltage equal to V A /2, DES (Dual Edge Sampling) Mode is selected where the I-channel is sampled at twice the input clock rate and the Q-channel is ignored. See 1.1.5.1 Dual-Edge Sampling . In extended control mode, this pin acts as the enable pin for the serial interface input and the CalDly value becomes "0" (short delay with no provision for a long power-up calibration delay).1819CLK+CLK-Differential clock input pins for the ADC. The differential clock signal must be a.c. coupled to these pins. The input signal is sampled on the falling edge of CLK+. See 1.1.2 Acquiring the Input for a description of acquiring the input and 2.3 THE CLOCK INPUTS for an overview of the clock inputs.10112223V IN I-V IN I+V IN Q+V IN Q−Analog signal inputs to the ADC. The differential full-scale input range of this input is programmable using the FSR pin 14 in Non-Extended Control Mode and the Input Full-Scale Voltage Adjust register in the Extended Control Mode. Refer to the V IN specification in the Converter ElectricalCharacteristics for the full-scale input range in the Non-Extended Control Mode. Refer to 1.4 REGISTERDESCRIPTION for the full-scale input range in the Extended Control Mode.ADC08D1520Pin Functions Pin No.SymbolEquivalent CircuitDescription7V CMOCommon Mode Voltage. This pin is the common mode output in d.c. coupling mode and also serves as the a.c.coupling mode select pin. When d.c. coupling is used at the analog inputs, the voltage output at this pin is required to be the common mode input voltage at V IN + and V IN −. When a.c.coupling is used, this pin should be grounded. This pin is capable of sourcing or sinking 100 μA. See 2.2 THE ANALOG INPUT .31V BGBandgap output voltage. This pin is capable of sourcing or sinking 100 μA and can drive a load up to 80 pF.126CalRunCalibration Running indication. This pin is at a logic high when calibration is running.32R EXTExternal bias resistor connection. Nominal value is 3.3 k Ω(±0.1%) to ground. See 1.1.1 Calibration .3435Tdiode_P Tdiode_NTemperature Diode Positive (Anode) and Negative (Cathode). This pin is used for die temperature measurements. See 2.6.2 Thermal Management .41ECEExtended Control Enable. This pin always enables ordisables Extended Control Mode. When this pin is set logic high, the Extended Control Mode is inactive and all control of the device must be through control pins only . When it is set logic low, the Extended Control Mode is active. This pin overrides the Extended Control Enable signal set using pin 14.52DRST_SELDCLK_RST select. This pin selects whether the DCLK is reset using a single-ended or differential signal. When this pin is floating or logic high, the DCLK_RST operation is single-ended and pin 14 functions as FSR/ALT_ECE. When this pin is logic low, the DCLK_RST operation becomes differential with functionality on pin 15 (DCLK_RST+) and pin 14 (DCLK_RST-). When in differential DCLK_RST mode,there is no pin-controlled FSR and the full-scale-range is defaulted to the higher V IN input level. When pin 41 is set logic low, the Extended Control Mode is active and the Full-Scale Voltage Adjust registers can be programmed. 6A D C 08D 1520Pin FunctionsPin No.Symbol Equivalent Circuit Description83 / 7884 / 7785 / 7686 / 7589 / 7290 / 7191 / 7092 / 6993 / 6894 / 6795 / 6696 / 65 100 / 61 101 / 60 102 / 59 103 / 58DI7− / DQ7−DI7+ / DQ7+DI6− / DQ6−DI6+ / DQ6+DI5− / DQ5−DI5+ / DQ5+DI4− / DQ4−DI4+ / DQ4+DI3− / DQ3−DI3+ / DQ3+DI2− / DQ2−DI2+ / DQ2+DI1− / DQ1−DI1+ / DQ1+DI0− / DQ0−DI0+ / DQ0+I- and Q-channel LVDS Data Outputs that are not delayed inthe output demultiplexer. Compared with the DId and DQdoutputs, these outputs represent the later time samples.These outputs should always be terminated with a 100Ωdifferential resistor.In Non-demultiplexed Mode, only these outputs are active.104 / 57 105 / 56 106 / 55 107 / 54 111 / 50 112 / 49 113 / 48 114 / 47 115 / 46 116 / 45 117 / 44 118 / 43 122 / 39 123 / 38 124 / 37 125 / 36DId7− / DQd7−DId7+ / DQd7+DId6− / DQd6−DId6+ / DQd6+DId5− / DQd5−DId5+ / DQd5+DId4− / DQd4−DId4+ / DQd4+DId3− / DQd3−DId3+ / DQd3+DId2− / DQd2−DId2+ / DQd2+DId1− / DQd1−DId1+ / DQd1+DId0− / DQd0−DId0+ / DQd0+I- and Q-channel LVDS Data Outputs that are delayed byone CLK cycle in the output demultiplexer. Compared withthe DI and DQ outputs, these outputs represent the earliertime sample. These outputs should always be terminatedwith a 100Ω differential resistor.In Non-demultiplexed Mode, these outputs are disabled andare high impedance. When disabled, these outputs must beleft floating.79 80OR+/DCLK2+OR-/DCLK2-Out Of Range, second Data Clock output. When functioningas OR+/-, a differential high at these pins indicates that thedifferential input is out of range (outside the range ±VIN/2 asprogrammed by the FSR pin in Non-extended Control Modeor the Input Full-Scale Voltage Adjust register setting in theExtended Control Mode). This single out of range indicationis for both the I- and Q-channels, unless PDQ is asserted, inwhich case it only applies to the I-channel input. Whenfunctioning as DCLK2+/-, DCLK2 is the exact replica ofDCLK and outputs the same signal at the same rate. Thefunctionality of these pins is selectable in Extended ControlMode only; default is OR+/-.ADC08D1520Pin Functions Pin No.SymbolEquivalent CircuitDescription8182DCLK-DCLK+Data Clock. Differential Clock outputs used to latch the output data. Delayed and non-delayed data outputs are supplied synchronously to this signal. In 1:2 Demux Mode,this signal is at 1/2 the input clock rate in SDR mode and at 1/4 the input clock rate in the DDR mode. In the Non-demux Mode, DCLK can only be in DDR mode and is at 1/2 the input clock rate. By default, the DCLK outputs are not active during the termination resistor trim section of the calibration cycle.If a system requires DCLK to run continuously during a calibration cycle, the termination resistor trim portion of the cycle can be disabled by setting the Resistor Trim Disable (RTD) bit to logic high in the Extended ConfigurationRegister. This disables all subsequent termination resistor trims after the initial trim which occurs during power-on calibration. This output is not recommended as a system clock unless the resistor trim is disabled.2, 5, 8, 13,16, 17, 20,25, 28, 33,128V AAnalog power supply pins. Bypass these pins to ground.40, 51, 62,73, 88, 99,110, 121V DROutput Driver power supply pins. Bypass these pins to DR GND.1, 6, 9, 12,21, 24, 27GNDGround return for V A .42, 53, 64,74, 87, 97,108, 119DR GNDGround return for V DR .63, 98, 109,120NCNo Connection. Make no connection to these pins. 8A D C 08D 1520Absolute Maximum Ratings(Notes 1, 2)If Military/Aerospace specified devices are required,please contact the National Semiconductor Sales Office/Distributors for availability and specifications.Supply Voltage (V A , V DR ) 2.2VSupply Difference V DR - V A0V to 100 mVVoltage on Any Input Pin −0.15V to (V A +0.15V)Ground Difference |GND - DR GND|0V to 100 mVInput Current at Any Pin (Note 3)±25 mA Package Input Current (Note 3)±50 mAPower Dissipation at T A ≤ 85°C 2.35 WESD Susceptibility (Note 4) Human Body Model Machine ModelCharged Device Model 2500V 250V 1000VStorage Temperature−65°C to +150°COperating Ratings(Notes 1, 2)Ambient Temperature Range−40°C ≤ T A ≤ +85°CSupply Voltage (V A )+1.8V to +2.0V Driver Supply Voltage (V DR )+1.8V to V A Analog Input Common Mode Voltage V CMO ±50 mV V IN +, V IN - Voltage Range (Maintaining Common Mode)200mV to V AGround Difference (|GND - DR GND|)0V CLK Pins Voltage Range 0V to V ADifferential CLK Amplitude0.4V P-P to 2.0V P-PPackage Thermal ResistancePackage θJA θJC Top of Package θJC Thermal Pad 128-Lead,Exposed Pad LQFP26°C / W10°C / W2.8°C / WSoldering process must comply with National Semiconductor’s Reflow Temperature Profile specifications.Refer to /packaging. (Note 5)Converter Electrical CharacteristicsThe following specifications apply after calibration for V A = V DR = +1.9V; OutV = 1.9V; V IN FSR (a.c. coupled) = differential 870mV P-P ; C L = 10 pF; Differential, a.c. coupled Sine Wave Input Clock, f CLK = 1.5 GHz at 0.5 V P-P with 50% duty cycle; V BG = Floating;Non-extended Control Mode; SDR Mode; R EXT = 3300 Ω ±0.1%; Analog Signal Source Impedance = 100 Ω Differential; 1:2Demultiplex Mode; Duty Cycle Stabilizer on. Boldface limits apply for T A = T MIN to T MAX . All other limits T A = 25°C, unless otherwise noted. (Notes 6, 7, 16)SymbolParameterConditionsTypical (Note 8)Limits (Note 8)Units (Limits)STATIC CONVERTER CHARACTERISTICS INL Integral Non-Linearity (Best fit)DC Coupled, 1 MHz Sine Wave Over-ranged±0.3±0.9LSB (max)DNL Differential Non-Linearity DC Coupled, 1 MHz Sine Wave Over-ranged ±0.15±0.6LSB (max)Resolution with No Missing Codes 8Bits V OFF Offset Error−0.75 LSB V OFF _ADJ Input Offset Adjustment Range Extended Control Mode±45 mV PFSE Positive Full-Scale Error (Note 9) ±25mV (max)NFSE Negative Full-Scale Error (Note 9)±25mV (max)FS_ADJ Full-Scale Adjustment Range Extended Control Mode ±20±15%FS 1:2 DEMUX NON-DES MODE, DYNAMIC CONVERTER CHARACTERISTICS; F CLK = 1.5 GHZFPBW Full Power Bandwidth Non-DES Mode 2.0 GHz C.E.R.Code Error Rate10−18 Error/SampleGain Flatnessd.c. to 748 MHz ±0.5 dBFS d.c. to 1.5 GHz±1.0 dBFS ENOB Effective Number of Bitsf IN = 373 MHz, V IN = FSR − 0.5 dB 7.4 6.8Bits (min)f IN = 748 MHz, V IN = FSR − 0.5 dB7.4 Bits SINAD Signal-to-Noise Plus Distortion Ratio f IN = 373 MHz, V IN = FSR − 0.5 dB 46.542.5dB (min)f IN = 748 MHz, V IN = FSR − 0.5 dB 46.4 dB SNRSignal-to-Noise Ratiof IN = 373 MHz, V IN = FSR − 0.5 dB 46.844.0dB (min)f IN = 748 MHz, V IN = FSR − 0.5 dB47dBADC08D1520Symbol ParameterConditionsTypical (Note 8)Limits (Note 8)Units (Limits)THD Total Harmonic Distortion f IN = 373 MHz, V IN = FSR − 0.5 dB −58-47.5dB (max)f IN = 748 MHz, V IN = FSR − 0.5 dB −55dB 2nd Harm Second Harmonic Distortion f IN = 373 MHz, V IN = FSR − 0.5 dB −65dB f IN = 748 MHz, V IN = FSR − 0.5 dB −59dB 3rd Harm Third Harmonic Distortion f IN = 373 MHz, V IN = FSR − 0.5 dB −58dB f IN = 748 MHz, V IN = FSR − 0.5 dB −58dB SFDR Spurious-Free Dynamic Range f IN = 373 MHz, V IN = FSR − 0.5 dB 5847.5dB (min)f IN = 748 MHz, V IN = FSR − 0.5 dB 55 dB IMD Intermodulation Distortion f IN1 = 365 MHz, V IN = FSR − 7 dB −50 dB f IN2 = 375 MHz, V IN = FSR − 7 dBOut of Range Output Code(V IN +) − (V IN −) > + Full Scale 255 (V IN +) − (V IN −) < − Full Scale 0 NON-DEMUX NON-DES MODE, DYNAMIC CONVERTER CHARACTERISTICS; F CLK = 1 GHZ ENOB Effective Number of Bitsf IN = 248 MHz, V IN = FSR − 0.5 dB 7.3 Bits f IN = 498 MHz, V IN = FSR − 0.5 dB7.3Bits SINAD Signal to Noise Plus Distortion Ratio f IN = 248 MHz, V IN = FSR − 0.5 dB 45.7 dB f IN = 498 MHz, V IN = FSR − 0.5 dB 45.7dB SNR Signal to Noise Ratio f IN = 248 MHz, V IN = FSR − 0.5 dB 46 dB f IN = 498 MHz, V IN = FSR − 0.5 dB 46dB THD Total Harmonic Distortion f IN = 248 MHz, V IN = FSR − 0.5 dB -57dB f IN = 498 MHz, V IN = FSR − 0.5 dB -57dB 2nd Harm Second Harmonic Distortion f IN = 248 MHz, V IN = FSR − 0.5 dB -63dB f IN = 498 MHz, V IN = FSR − 0.5 dB -63dB 3rd Harm Third Harmonic Distortion f IN = 248 MHz, V IN = FSR − 0.5 dB -64dB f IN = 498 MHz, V IN = FSR − 0.5 dB -64dB SFDRSpurious Free Dynamic Rangef IN = 248 MHz, V IN = FSR − 0.5 dB 57 dB f IN = 498 MHz, V IN = FSR − 0.5 dB 57dB 1:4 DEMUX DES MODE, DYNAMIC CONVERTER CHARACTERISTICS; F CLK = 1.5 GHZ FPBW Full Power Bandwidth DES Mode1.3 GHz ENOB Effective Number of Bitsf IN = 748 MHz, V IN = FSR − 0.5 dB7.0 Bits SINAD Signal to Noise Plus DistortionRatiof IN = 748 MHz, V IN = FSR − 0.5 dB44 dB SNR Signal to Noise Ratio f IN = 748 MHz, V IN = FSR − 0.5 dB 46.3 dB THD Total Harmonic Distortion f IN = 748 MHz, V IN = FSR − 0.5 dB −47dB 2nd Harm Second Harmonic Distortion f IN = 748 MHz, V IN = FSR − 0.5 dB −55dB 3rd Harm Third Harmonic Distortionf IN = 748 MHz, V IN = FSR − 0.5 dB−64dB SFDRSpurious Free Dynamic Range f IN = 748 MHz, V IN = FSR − 0.5 dB47dB ANALOG INPUT AND REFERENCE CHARACTERISTICSV INFull Scale Analog Differential Input RangeFSR pin 14 Low 650590mV P-P (min)730mV P-P (max)FSR pin 14 High 870800mV P-P (min)940mV P-P (max)V CMICommon Mode Input VoltageV CMOV CMO − 0.05V (min)V CMO + 0.05V (max) 10A D C 08D 1520Symbol Parameter Conditions Typical(Note 8)Limits(Note 8)Units(Limits)C IN Analog Input Capacitance,Normal operation(Notes 10, 11)Differential0.02pFEach input pin to ground 1.6pF Analog Input Capacitance,DES Mode (Notes 10, 11)Differential0.08pFEach input pin to ground 2.2pFR IN Differential Input Resistance10094Ω (min)106Ω (max)ANALOG OUTPUT CHARACTERISTICSV CMO Common Mode Output Voltage I CMO = ±100 µA 1.260.95V (min)1.45V (max)TC VCMO Common Mode Output VoltageTemperature CoefficientTA= −40°C to +85°C118ppm/°CVCMO_LVL VCMOinput threshold to set D.C.Coupling modeVA= 1.8V0.60VVA= 2.0V0.66VC LOAD VCMOMaximum VCMOLoadCapacitance80pFV BG Bandgap Reference OutputVoltageIBG= ±100 µA 1.261.20V (min)1.33V (max)TC VBG Bandgap Reference VoltageTemperature CoefficientTA= −40°C to +85°C,IBG= ±100 µA28ppm/°CC LOAD VBGMaximum Bandgap Referenceload Capacitance80pFCHANNEL-TO-CHANNEL CHARACTERISTICSOffset Match1LSBPositive Full-Scale Match Zero offset selected in Control Register1LSBNegative Full-Scale Match Zero offset selected in Control Register1LSBPhase Matching (I, Q)f IN = 1.5 GHz< 1DegreeX-TALK Crosstalk from I-channel(Aggressor) to Q-channel(Victim)Aggressor = 867 MHz F.S.Victim = 100 MHz F.S.−65dBX-TALK Crosstalk from Q-channel(Aggressor) to I-channel(Victim)Aggressor = 867 MHz F.S.Victim = 100 MHz F.S.−65dBLVDS CLK INPUT CHARACTERISTICS (Typical specs also apply to DCLK_RST)V ID Differential Clock Input LevelSine Wave Clock0.60.4V P-P (min)2.0V P-P (max)Square Wave Clock0.60.4V P-P (min)2.0V P-P (max)VOSIInput Offset Voltage 1.2VC IN Input Capacitance(Notes 10, 11)Differential0.02pFEach input to ground 1.5pFDIGITAL CONTROL PIN CHARACTERISTICSV IH Logic High Input VoltageOutV, DCLK_RST, PD, PDQ, CAL, ECE,DRST_SEL0.69 x VAV (min)OutEdge, FSR, CalDly0.79 x V A V (min)V IL Logic Low Input VoltageOutV, DCLK_RST, PD, PDQ, CAL0.28 x V A V (max)OutEdge, FSR, CalDly, ECE, DRST_SEL0.21 x V A V (max)C IN Input Capacitance(Notes 11, 13)Each input to ground 1.2pFADC08D1520SymbolParameterConditionsTypical (Note 8)Limits (Note 8)Units (Limits)DIGITAL OUTPUT CHARACTERISTICSV ODLVDS Differential Output VoltageMeasured differentially, OutV = V A ,V BG = Floating (Note 15)740480mV P-P (min)950mV P-P (max)Measured differentially, OutV = GND, V BG = Floating (Note 15)560320mV P-P (min)720mV P-P (max)ΔV O DIFF Change in LVDS Output SwingBetween Logic Levels±1 mV V OS Output Offset Voltage See Figure 1V BG = Floating 800 mV V BG = V A (Note 15)1175 mV ΔV OS Output Offset Voltage ChangeBetween Logic Levels±1 mV I OS Output Short Circuit Current Output+ and Output−connected to 0.8V ±4 mA Z O Differential Output Impedance100 Ohms V OH CalRun H level output I OH = −400 µA (Note 12) 1.65 1.5V V OLCalRun L level outputI OH = 400 µA (Note 12)0.150.3V POWER SUPPLY CHARACTERISTICS (NON-DES MODE)I AAnalog Supply Current1:2 Demux Mode; f CLK = 1.5 GHz PD = PDQ = LowPD = Low, PDQ = High PD = PDQ = High 8185611.9 930640 mA (max)mA (max)mA Non-demux Mode; f CLK = 1.0 GHz PD = PDQ = LowPD = Low, PDQ = High PD = PDQ = High 7124641.5 803530 mA (max)mA (max)mA I DROutput Driver Supply Current1:2 Demux Mode; f CLK = 1.5 GHz PD = PDQ = LowPD = Low, PDQ = High PD = PDQ = High 2251230.074 305166 mA (max)mA (max)mA Non-demux Mode; f CLK = 1.0 GHz PD = PDQ = LowPD = Low, PDQ = High PD = PDQ = High 13683.50.047 212120 mA (max)mA (max)mA P DPower Consumption1:2 Demux Mode; f CLK = 1.5 GHz PD = PDQ = LowPD = Low, PDQ = High PD = PDQ = High 2.01.33.8 2.351.53 W (max)W (max)mW Non-demux Mode; f CLK = 1.0 GHz PD = PDQ = LowPD = Low, PDQ = High PD = PDQ = High 1.61.042.76 1.921.235W (max)W (max)mW PSRR1D.C. Power Supply Rejection RatioChange in Full Scale Error with change in V A from 1.8V to 2.0V-30dBA D C 08D 1520Symbol Parameter Conditions Typical(Note 8)Limits(Note 8)Units(Limits)A.C. ELECTRICAL CHARACTERISTICSfCLK (max)Maximum Input ClockFrequencyDemux Mode (DES or Non-DES Mode) 1.7 1.5GHz (max)Non-Demux Mode (DES or Non-DESMode)1.0GHz (max)fCLK (min)Minimum Input ClockFrequency1:2 Demux Non-DES Mode200MHz1:4 Demux DES Mode500MHz Input Clock Duty CyclefCLK(min)≤ fCLK≤ 1.5 GHz(Note 12)5020% (min)80% (max)tCLInput Clock Low Time(Note 11)333133ps (min)tCHInput Clock High Time(Note 11)333133ps (min)DCLK Duty Cycle(Note 11)5045% (min) 55% (max)tSRSetup Time DCLK_RST±(Note 12)90pstHRHold Time DCLK_RST±(Note 12)30pst PWR Pulse Width DCLK_RST±(Note 11)4Input ClockCycles (min)t LHT Differential Low-to-HighTransition Time10% to 90%, CL= 2.5 pF150pst HLT Differential High-to-LowTransition Time10% to 90%, CL= 2.5 pF150pst OSK DCLK-to-Data Output Skew50% of DCLK transition to 50% of Datatransition, SDR Modeand DDR Mode, 0° DCLK (Note 11)±50ps (max)tSUData-to-DCLK Set-Up Time DDR Mode, 90° DCLK (Note 11)400pstHDCLK-to-Data Hold Time DDR Mode, 90° DCLK (Note 11)560pstADSampling (Aperture) Delay Input CLK+ Fall to Acquisition of Data 1.6nstAJAperture Jitter0.4ps (rms)t OD Input Clock-to Data OutputDelay (in addition to PipelineDelay)50% of Input Clock transition to 50% of Datatransition4.0nsPipeline Delay (Latency) in 1:2Demux Mode(Notes 11, 14)DI Outputs13Input ClockCyclesDId Outputs14DQ OutputsNon-DES Mode13DES Mode13.5DQd OutputsNon-DES Mode14DES Mode14.5Pipeline Delay (Latency) inNon-Demux Mode(Notes 11, 14)DI Outputs13Input ClockCyclesDQ OutputsNon-DES Mode13DES Mode13.5Over Range Recovery TimeDifferential VINstep from ±1.2V to 0V to getaccurate conversion1Input ClockCyclet WU PD low to Rated AccuracyConversion (Wake-Up Time)Non-DES Mode (Note 11)500nsDES Mode (Note 11)1µsfSCLKSerial Clock Frequency(Note 11)15MHzt SSU Serial Data to Serial ClockRising Setup Time(Note 11) 2.5ns (min)t SH Serial Data to Serial ClockRising Hold Time(Note 11)1ns (min)t SCS CS to Serial Clock Rising SetupTime2.5nsADC08D1520Symbol ParameterConditionsTypical (Note 8)Limits (Note 8)Units (Limits)t HCS CS to Serial Clock Falling HoldTime1.5 ns Serial Clock Low Time 30ns (min) Serial Clock High Time 30ns (min)t CAL Calibration Cycle Time1.4 x 106Clock Cycles t CAL_L CAL Pin Low Time See Figure 10 (Note 11) 1280Clock Cycles(min)t CAL_HCAL Pin High TimeSee Figure 10 (Note 11)1280Clock Cycles(min)t CalDlyCalibration delay determined by CalDly (pin 127)CalDly = LowSee 1.1.1 Calibration , Figure 10,(Note 11)226Clock Cycles(max)CalDly = HighSee 1.1.1 Calibration , Figure 10,(Note 11)232Clock Cycles(max)Note 1:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. There is no guarantee of operation at the Absolute Maximum Ratings. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.Note 2:All voltages are measured with respect to GND = DR GND = 0V, unless otherwise specified.Note 3:When the input voltage at any pin exceeds the power supply limits (that is, less than GND or greater than V A ), the current at that pin should be limited to 25 mA. The 50 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 25 mA to two. This limit is not placed upon the power, ground and digital output pins.Note 4:Human body model is 100 pF capacitor discharged through a 1.5 k Ω resistor. Machine model is 220 pF discharged through ZERO Ohms. Charged device model simulates a pin slowly acquiring charge (such as from a device sliding down the feeder in an automated assembler) then rapidly being discharged.Note 5:Reflow temperature profiles are different for lead-free and non-lead-free packages.Note 6:The analog inputs are protected as shown below. Input voltage magnitudes beyond the Absolute Maximum Ratings may damage this device.20193104Note 7:To guarantee accuracy, it is required that V A and V DR be well bypassed. Each supply pin must be decoupled with separate bypass capacitors. Additionally,achieving rated performance requires that the backside exposed pad be well grounded.Note 8:Typical figures are at T A = 25°C, and represent most likely parametric norms. Test limits are guaranteed to National's AOQL (Average Outgoing Quality Level).Note 9:Calculation of Full-Scale Error for this device assumes that the actual reference voltage is exactly its nominal value. Full-Scale Error for this device,therefore, is a combination of Full-Scale Error and Reference Voltage Error. See Figure 2. For relationship between Gain Error and Full-Scale Error, see Specification Definitions for Gain Error.Note 10:The analog and clock input capacitances are die capacitances only. Additional package capacitances of 0.65 pF differential and 0.95 pF each pin to ground are isolated from the die capacitances by lead and bond wire inductances.Note 11:This parameter is guaranteed by design and is not tested in production.Note 12:This parameter is guaranteed by design and/or characterization and is not tested in production.Note 13:The digital control pin capacitances are die capacitances only. Additional package capacitance of 1.6 pF each pin to ground are isolated from the die capacitances by lead and bond wire inductances.Note 14:The ADC08D1520 has two LVDS output buses, each of which clocks data out at one half the sample rate. The second bus (D0 through D7) has a pipeline latency that is one clock cycle less than the latency of the first bus (Dd0 through Dd7).Note 15:Tying V BG to the supply rail will increase the output offset voltage (V OS ) by 400mv (typical), as shown in the V OS specification above. Tying V BG to the supply rail will also affect the differential LVDS output voltage (V OD ), causing it to increase by 40mV (typical).Note 16:The maximum clock frequency for Non-Demux Mode is 1 GHz.A D C 08D 1520。

CXD2500BQ中文资料

CXD2500BQ

80 pin QFP (Plastic)

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

CLV processor

TEST 10

Noise shaper

NC 5

18-times over samplling

filter

70

6

Register

32K RAM

Address generator

8

Priority encoder

D/A data processor

Serial/Parallel processor

56 53 54 53

Clock generator

17 19

Digital PLL vari-pitch double speed

EFM demodulator

∗

MUX

Sync Protector

Timing Generator

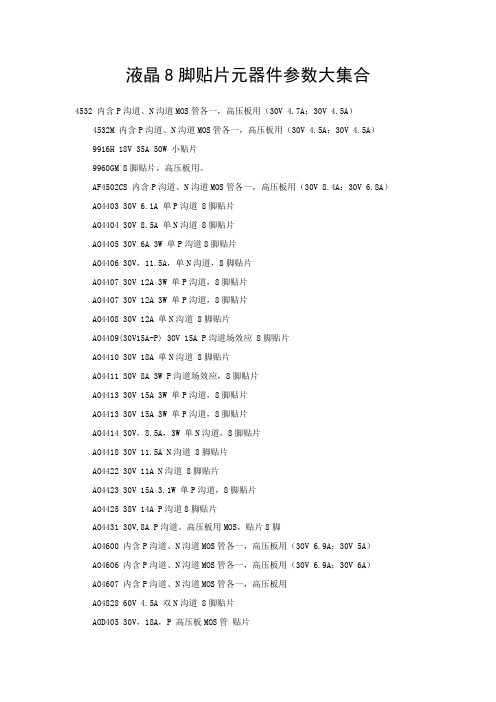

液晶8脚贴片元器件参数大集合

液晶8脚贴片元器件参数大集合4532 内含P沟道、N沟道MOS管各一,高压板用(30V 4.7A;30V 4.5A)4532M 内含P沟道、N沟道MOS管各一,高压板用(30V 4.5A;30V 4.5A)9916H 18V 35A 50W 小贴片9960GM 8脚贴片,高压板用。

AF4502CS 内含P沟道、N沟道MOS管各一,高压板用(30V 8.4A;30V 6.8A) AO4403 30V 6.1A 单P沟道 8脚贴片AO4404 30V 8.5A 单N沟道 8脚贴片AO4405 30V 6A 3W 单P沟道8脚贴片AO4406 30V,11.5A,单N沟道,8脚贴片AO4407 30V 12A 3W 单P沟道,8脚贴片AO4407 30V 12A 3W 单P沟道,8脚贴片AO4408 30V 12A 单N沟道 8脚贴片AO4409(30V15A-P) 30V 15A P沟道场效应 8脚贴片AO4410 30V 18A 单N沟道 8脚贴片AO4411 30V 8A 3W P沟道场效应,8脚贴片AO4413 30V 15A 3W 单P沟道,8脚贴片AO4413 30V 15A 3W 单P沟道,8脚贴片AO4414 30V,8.5A,3W 单N沟道,8脚贴片AO4418 30V 11.5A N沟道 8脚贴片AO4422 30V 11A N沟道 8脚贴片AO4423 30V 15A 3.1W 单P沟道,8脚贴片AO4425 38V 14A P沟道8脚贴片AO4431 30V,8A P沟道。

高压板用MOS,贴片8脚AO4600 内含P沟道、N沟道MOS管各一,高压板用(30V 6.9A;30V 5A)AO4606 内含P沟道、N沟道MOS管各一,高压板用(30V 6.9A;30V 6A)AO4607 内含P沟道、N沟道MOS管各一,高压板用AO4828 60V 4.5A 双N沟道 8脚贴片AOD405 30V,18A,P 高压板MOS管贴片AOD408 30V,18A,N 高压板MOS管贴片AOD409 60V 26/18A P 高压板MOS管贴片AOD409 60V 26/18A P 高压板MOS管贴片AOD420 30V,10A,N 高压板MOS管贴片AOD442 60V,38/27A,N 高压板MOS管贴片AOD442 60V,38/27A,N 高压板MOS管贴片AOD444 60V,12A,N 高压板MOS管贴片AOP600 内含P、N沟道各1,30V 7.5A、30V 4.5A。

SO8-200

Publication Release Date: October 01, 2012 Revision D3V 128M-BITSERIAL FLASH MEMORY WITH DUAL/QUAD SPI & QPI- 1 -Table of Contents1. GENERAL DESCRIPTIONS ............................................................................................................. 52. FEATURES ....................................................................................................................................... 53.PACKAGE TYPES AND PIN CONFIGURATIONS ........................................................................... 6 3.1 Pin Configuration SOIC / VSOP 208-mil .............................................................................. 6 3.2 Pad Configuration WSON 6x5-mm / 8x6-mm ...................................................................... 6 3.3 Pin Description SOIC / VSOP 208-mil, WSON 6x5-mm / 8x6-mm ...................................... 6 3.4 Pin Configuration SOIC 300-mil ........................................................................................... 7 3.5 Pin Description SOIC 300-mil ............................................................................................... 7 3.6 Ball Configuration TFBGA 8x6-mm (5x5 or 6x4 Ball Array) ................................................. 8 3.7 Ball Description TFBGA 8x6-mm ......................................................................................... 8 3.8 Pin Configuration PDIP 300-mil ............................................................................................ 9 3.9Pin Description PDIP 300-mil ............................................................................................... 9 4. PIN DESCRIPTIONS ...................................................................................................................... 10 4.1 Chip Select (/CS) ................................................................................................................ 10 4.2 Serial Data Input, Output and IOs (DI, DO and IO0, IO1, IO2, IO3) ................................... 10 4.3 Write Protect (/WP) ............................................................................................................ 10 4.4 HOLD (/HOLD) ................................................................................................................... 10 4.5 Serial Clock (CLK) .............................................................................................................. 10 4.6Reset (/RESET) (10)5. BLOCK DIAGRAM .......................................................................................................................... 116.FUNCTIONAL DESCRIPTIONS ..................................................................................................... 12 6.1SPI / QPI Operations (12)6.1.1 Standard SPI Instructions ..................................................................................................... 12 6.1.2 Dual SPI Instructions ............................................................................................................ 12 6.1.3 Quad SPI Instructions ........................................................................................................... 13 6.1.4 QPI Instructions .................................................................................................................... 13 6.1.5 Hold Function ....................................................................................................................... 13 6.1.6 Software Reset & Hardware /RESET pin (14)6.2Write Protection (15)6.2.1 Write Protect Features (15)7.STATUS AND CONFIGURATION REGISTERS ............................................................................ 16 7.1Status Registers (16)7.1.1 Erase/Write In Progress (BUSY) – Status Only .................................................................... 16 7.1.2 Write Enable Latch (WEL) – Status Only ............................................................................. 16 7.1.3 Block Protect Bits (BP2, BP1, BP0) – Volatile/Non-Volatile Writable .. (16)7.1.4 Top/Bottom Block Protect (TB) – Volatile/Non-Volatile Writable .......................................... 17 Publication Release Date: October 01, 2012- 2 - Revision D7.1.5 Sector/Block Protect Bit (SEC) – Volatile/Non-Volatile Writable .......................................... 17 7.1.6 Complement Protect (CMP) – Volatile/Non-Volatile Writable ............................................... 17 7.1.7 Status Register Protect (SRP1, SRP0) – Volatile/Non-Volatile Writable .............................. 17 7.1.8 Erase/Program Suspend Status (SUS) – Status Only .......................................................... 18 7.1.9 Security Register Lock Bits (LB3, LB2, LB1) – Volatile/Non-Volatile OTP Writable ............. 18 7.1.10 Quad Enable (QE) – Volatile/Non-Volatile Writable ........................................................... 18 7.1.11 Write Protect Selection (WPS) – Volatile/Non-Volatile Writable ........................................ 19 7.1.12 Output Driver Strength (DRV1, DRV0) – Volatile/Non-Volatile Writable ............................. 19 7.1.13 HOLD or /RESET Pin Function (HOLD/RST) – Volatile/Non-Volatile Writable ................... 19 7.1.14 Reserved Bits – Non Functional ......................................................................................... 19 7.1.15 W25Q128FV Status Register Memory Protection (WPS = 0, CMP = 0) ............................ 20 7.1.16 W25Q128FV Status Register Memory Protection (WPS = 0, CMP = 1) ............................ 21 7.1.17 W25Q128FV Individual Block Memory Protection (WPS=1) . (22)8. INSTRUCTIONS ............................................................................................................................. 23 8.1Device ID and Instruction Set Tables (23)8.1.1 Manufacturer and Device Identification ................................................................................ 23 8.1.2 Instruction Set Table 1 (Standard/Dual/Quad SPI Instructions) ........................................... 24 8.1.3 Instruction Set Table 2 (Standard/Dual/Quad SPI Instructions) ........................................... 25 8.1.4 Instruction Set Table 3 (QPI Instructions) .. (26)8.2 Instruction Descriptions (28)8.2.1 Write Enable (06h) ............................................................................................................... 28 8.2.2 Write Enable for Volatile Status Register (50h) .................................................................... 28 8.2.3 Write Disable (04h) ............................................................................................................... 29 8.2.4 Read Status Register-1 (05h), Status Register-2 (35h) & Status Register-3 (15h) .............. 29 8.2.5 Write Status Register-1 (01h), Status Register-2 (31h) & Status Register-3 (11h) .............. 30 8.2.6 Read Data (03h) ................................................................................................................... 33 8.2.7 Fast Read (0Bh) ................................................................................................................... 34 8.2.8 Fast Read Dual Output (3Bh) ............................................................................................... 36 8.2.9 Fast Read Quad Output (6Bh) .............................................................................................. 37 8.2.10 Fast Read Dual I/O (BBh) ................................................................................................... 38 8.2.11 Fast Read Quad I/O (EBh) ................................................................................................. 40 8.2.12 Word Read Quad I/O (E7h) ................................................................................................ 43 8.2.13 Octal Word Read Quad I/O (E3h) ....................................................................................... 45 8.2.14 Set Burst with Wrap (77h) .................................................................................................. 47 8.2.15 Page Program (02h) ........................................................................................................... 48 8.2.16 Quad Input Page Program (32h) ........................................................................................ 50 8.2.17 Sector Erase (20h) ............................................................................................................. 51 8.2.18 32KB Block Erase (52h) ..................................................................................................... 52 8.2.19 64KB Block Erase (D8h) ..................................................................................................... 53 8.2.20 Chip Erase (C7h / 60h) . (54)8.2.21 Erase / Program Suspend (75h) (55)- 3 -8.2.22 Erase / Program Resume (7Ah) ......................................................................................... 57 8.2.23 Power-down (B9h) .............................................................................................................. 58 8.2.24 Release Power-down / Device ID (ABh) ............................................................................. 59 8.2.25 Read Manufacturer / Device ID (90h) ................................................................................. 61 8.2.26 Read Manufacturer / Device ID Dual I/O (92h) ................................................................... 62 8.2.27 Read Manufacturer / Device ID Quad I/O (94h) ................................................................. 63 8.2.28 Read Unique ID Number (4Bh)........................................................................................... 64 8.2.29 Read JEDEC ID (9Fh) ........................................................................................................ 65 8.2.30 Read SFDP Register (5Ah) ................................................................................................ 66 8.2.31 Erase Security Registers (44h) ........................................................................................... 67 8.2.32 Program Security Registers (42h) ...................................................................................... 68 8.2.33 Read Security Registers (48h) ........................................................................................... 69 8.2.34 Set Read Parameters (C0h) ............................................................................................... 70 8.2.35 Burst Read with Wrap (0Ch) ............................................................................................... 71 8.2.36 Enter QPI Mode (38h) ......................................................................................................... 72 8.2.37 Exit QPI Mode (FFh) ........................................................................................................... 73 8.2.38 Individual Block/Sector Lock (36h) ..................................................................................... 74 8.2.39 Individual Block/Sector Unlock (39h) .................................................................................. 75 8.2.40 Read Block/Sector Lock (3Dh) ........................................................................................... 76 8.2.41 Global Block/Sector Lock (7Eh) .......................................................................................... 77 8.2.42 Global Block/Sector Unlock (98h) ....................................................................................... 77 8.2.43 Enable Reset (66h) and Reset Device (99h) . (78)9. ELECTRICAL CHARACTERISTICS ............................................................................................... 79 9.1 Absolute Maximum Ratings ................................................................................................ 79 9.2 Operating Ranges............................................................................................................... 79 9.3 Power-Up Power-Down Timing and Requirements ............................................................ 80 9.4 DC Electrical Characteristics .............................................................................................. 81 9.5 AC Measurement Conditions .............................................................................................. 82 9.6 AC Electrical Characteristics .............................................................................................. 83 9.7 AC Electrical Characteristics (cont’d) ................................................................................. 84 9.8 Serial Output Timing ........................................................................................................... 85 9.9 Serial Input Timing .............................................................................................................. 85 9.10 HOLD Timing ...................................................................................................................... 85 9.11WP Timing .......................................................................................................................... 85 10. PACKAGE SPECIFICATIONS ........................................................................................................ 86 10.1 8-Pin SOIC 208-mil (Package Code S) .............................................................................. 86 10.2 8-Pin VSOP 208-mil (Package Code T) ............................................................................. 87 10.38-Pin PDIP 300-mil (Package Code A) (88)10.4 8-Pad WSON 6x5-mm (Package Code P) ......................................................................... 89 Publication Release Date: October 01, 2012- 4 - Revision D10.5 8-Pad WSON 8x6-mm (Package Code E) ......................................................................... 90 10.6 16-Pin SOIC 300-mil (Package Code F) ............................................................................ 91 10.7 24-Ball TFBGA 8x6-mm (Package Code B, 5x5-1 ball array) ............................................ 92 10.824-Ball TFBGA 8x6-mm (Package Code C, 6x4 ball array) ............................................... 93 11. ORDERING INFORMATION .......................................................................................................... 94 11.1Valid Part Numbers and Top Side Marking (95)12. REVISION HISTORY (96)- 5 -1. GENERAL DESCRIPTIONSThe W25Q128FV (128M-bit) Serial Flash memory provides a storage solution for systems with limited space, pins and power. The 25Q series offers flexibility and performance well beyond ordinary Serial Flash devices. They are ideal for code shadowing to RAM, executing code directly from Dual/Quad SPI (XIP) and storing voice, text and data. The device operates on a single 2.7V to 3.6V power supply with current consumption as low as 4mA active and 1µA for power-down. All devices are offered in space-saving packages.The W25Q128FV array is organized into 65,536 programmable pages of 256-bytes each. Up to 256 bytes can be programmed at a time. Pages can be erased in groups of 16 (4KB sector erase), groups of 128 (32KB block erase), groups of 256 (64KB block erase) or the entire chip (chip erase). The W25Q128FV has 4,096 erasable sectors and 256 erasable blocks respectively. The small 4KB sectors allow for greater flexibility in applications that require data and parameter storage. (See Figure 2.)The W25Q128FV support the standard Serial Peripheral Interface (SPI), Dual/Quad I/O SPI as well as 2-clocks instruction cycle Quad Peripheral Interface (QPI): Serial Clock, Chip Select, Serial Data I/O0 (DI), I/O1 (DO), I/O2 (/WP), and I/O3 (/HOLD). SPI clock frequencies of up to 104MHz are supported allowing equivalent clock rates of 208MHz (104MHz x 2) for Dual I/O and 416MHz (104MHz x 4) for Quad I/O when using the Fast Read Dual/Quad I/O and QPI instructions. These transfer rates can outperform standard Asynchronous 8 and 16-bit Parallel Flash memories. The Continuous Read Mode allows for efficient memory access with as few as 8-clocks of instruction-overhead to read a 24-bit address, allowing true XIP (execute in place) operation.A Hold pin, Write Protect pin and programmable write protection, with top or bottom array control, provide further control flexibility. Additionally, the device supports JEDEC standard manufacturer and device ID and SFDP Register, a 64-bit Unique Serial Number and three 256-bytes Security Registers.2. FEATURES• New Family of SpiFlash Memories – W25Q128FV: 128M-bit / 16M-byte– Standard SPI: CLK, /CS, DI, DO, /WP, /Hold – Dual SPI: CLK, /CS, IO 0, IO 1, /WP, /Hold – Quad SPI: CLK, /CS, IO 0, IO 1, IO 2, IO 3 – QPI: CLK, /CS, IO 0, IO 1, IO 2, IO 3 – Software & Hardware Reset• Highest Performance Serial Flash – 104MHz Single, Dual/Quad SPI clocks – 208/416MHz equivalent Dual/Quad SPI – 50MB/S continuous data transfer rate – More than 100,000 erase/program cycles – More than 20-year data retention• Efficient “Continuous Read” and QPI Mode– Continuous Read with 8/16/32/64-Byte Wrap– As few as 8 clocks to address memory – Quad Peripheral Interface (QPI) reducesinstruction overhead– Allows true XIP (execute in place) operation– Outperforms X16 Parallel Flash• Low Power, Wide Temperature Range – Single 2.7 to 3.6V supply– 4mA active current, <1µA Power-down (typ.) – -40°C to +85°C operating range• Flexible Architecture with 4KB sectors– Uniform Sector/Block Erase (4K/32K/64K-Byte) – Program 1 to 256 byte per programmable page – Erase/Program Suspend & Resume• Advanced Security Features– Software and Hardware Write-Protect– Power Supply Lock-Down and OTP protection – Top/Bottom, Complement array protection – Individual Block/Sector array protection – 64-Bit Unique ID for each device– Discoverable Parameters (SFDP) Register– 3X256-Bytes Security Registers with OTP locks– Volatile & Non-volatile Status Register Bits• Space Efficient Packaging – 8-pin SOIC / VSOP 208-mil – 8-pin PDIP 300-mil – 8-pad WSON 6x5-mm / 8x6-mm– 16-pin SOIC 300-mil (additional /RESET pin) – 24-ball TFBGA 8x6-mm– Contact Winbond for KGD and other optionsPublication Release Date: October 01, 2012- 6 - Revision D3. PACKAGE TYPES AND PIN CONFIGURATIONS 3.1 Pin Configuration SOIC / VSOP 208-milFigure 1a. W25Q128FV Pin Assignments, 8-pin SOIC / VSOP 208-mil (Package Code S, T)3.2 Pad Configuration WSON 6x5-mm / 8x6-mmFigure 1b. W25Q128FV Pad Assignments, 8-pad WSON 6x5-mm / 8x6-mm (Package Code P, E)3.3 Pin Description SOIC / VSOP 208-mil, WSON 6x5-mm / 8x6-mmPIN NO.PIN NAMEI/OFUNCTION1 /CSI Chip Select Input2DO (IO1)I/O Data Output (Data Input Output 1)(1)3 /WP (IO2) I/O Write Protect Input ( Data Input Output 2)(2)4 GND Ground5 DI (IO0) I/O Data Input (Data Input Output 0)(1)6 CLKI Serial Clock Input7/HOLD or /RESET(IO3)I/OHold or Reset Input (Data Input Output 3)(2)8 VCC Power SupplyNotes:1. IO0 and IO1 are used for Standard and Dual SPI instructions2. IO0 – IO3 are used for Quad SPI instructions, /WP & /HOLD (or /RESET) functions are only available for Standard/Dual SPI.- 7 -3.4 Pin Configuration SOIC 300-milFigure 1c. W25Q128FV Pin Assignments, 16-pin SOIC 300-mil (Package Code F)3.5 Pin Description SOIC 300-milPIN NO.PIN NAMEI/OFUNCTION1 /HOLD (IO3)I/OHold Input (Data Input Output 3)(2)2 VCC Power Supply3 /RESET I Reset Input (3)4 N/C No Connect5 N/C No Connect6 N/C No Connect7 /CS I Chip Select Input8DO (IO1)I/O Data Output (Data Input Output 1)(1)9 /WP (IO2)I/OWrite Protect Input (Data Input Output 2)(2)10 GND Ground 11 N/C No Connect 12 N/C No Connect 13 N/C No Connect 14 N/C No Connect 15 DI (IO0) I/O Data Input (Data Input Output 0)(1)16 CLKISerial Clock InputNotes:1. IO0 and IO1 are used for Standard and Dual SPI instructions2. IO0 – IO3 are used for Quad SPI instructions, /WP & /HOLD (or /RESET) functions are only available for Standard/Dual SPI.3. The /RESET pin on SOIC-16 package is independent of the HOLD/RST bit and QE bit settings in the Status Register.Publication Release Date: October 01, 2012- 8 - Revision D3.6 Ball Configuration TFBGA 8x6-mm (5x5 or 6x4 Ball Array)Figure 1d. W25Q128FV Ball Assignments, 24-ball TFBGA 8x6-mm (Package Code B & C)3.7 Ball Description TFBGA 8x6-mmBALL NO.PIN NAMEI/OFUNCTIONB2CLKISerial Clock InputB3 GND Ground B4 VCC Power Supply C2 /CS I Chip Select InputC4 /WP (IO2) I/O Write Protect Input (Data Input Output 2)(2)D2 DO (IO1) I/O Data Output (Data Input Output 1)(1)D3 DI (IO0) I/O Data Input (Data Input Output 0)(1)D4/HOLD or /RESET(IO3)I/OHold or Reset Input (Data Input Output 3)(2)Multiple NC No Connect Notes:1. IO0 and IO1 are used for Standard and Dual SPI instructions2. IO0 – IO3 are used for Quad SPI instructions, /WP & /HOLD (or /RESET) functions are only available for Standard/Dual SPI.- 9 -3.8 Pin Configuration PDIP 300-milFigure 1e. W25Q128FV Pin Assignments, 8-pin PDIP (Package Code A)3.9 Pin Description PDIP 300-milPIN NO.PIN NAMEI/OFUNCTION1 /CSI Chip Select Input2DO (IO1)I/O Data Output (Data Input Output 1)(1)3 /WP (IO2) I/O Write Protect Input ( Data Input Output 2)(2)4 GND Ground5 DI (IO0) I/O Data Input (Data Input Output 0)(1)6 CLKI Serial Clock Input7/HOLD or /RESET(IO3)I/OHold or Reset Input (Data Input Output 3)(2)8 VCC Power SupplyNotes:1. IO0 and IO1 are used for Standard and Dual SPI instructions2. IO0 – IO3 are used for Quad SPI instructions, /WP & /HOLD (or /RESET) functions are only available for Standard/Dual SPI.4.PIN DESCRIPTIONS4.1Chip Select (/CS)The SPI Chip Select (/CS) pin enables and disables device operation. When /CS is high the device is deselected and the Serial Data Output (DO, or IO0, IO1, IO2, IO3) pins are at high impedance. When deselected, the devices power consumption will be at standby levels unless an internal erase, program or write status register cycle is in progress. When /CS is brought low the device will be selected, power consumption will increase to active levels and instructions can be written to and data read from the device. After power-up, /CS must transition from high to low before a new instruction will be accepted. The /CS input must track the VCC supply level at power-up and power-down (see “Write Protection” and Figure 58). If needed a pull-up resister on the /CS pin can be used to accomplish this.4.2Serial Data Input, Output and IOs (DI, DO and IO0, IO1, IO2, IO3)The W25Q128FV supports standard SPI, Dual SPI and Quad SPI operation. Standard SPI instructions use the unidirectional DI (input) pin to serially write instructions, addresses or data to the device on the rising edge of the Serial Clock (CLK) input pin. Standard SPI also uses the unidirectional DO (output) to read data or status from the device on the falling edge of CLK.Dual and Quad SPI instructions use the bidirectional IO pins to serially write instructions, addresses or data to the device on the rising edge of CLK and read data or status from the device on the falling edge of CLK. Quad SPI instructions require the non-volatile Quad Enable bit (QE) in Status Register-2 to be set. When QE=1, the /WP pin becomes IO2 and /HOLD pin becomes IO3.4.3Write Protect (/WP)The Write Protect (/WP) pin can be used to prevent the Status Register from being written. Used in conjunction with the Status Register’s Block Protect (CMP, SEC, TB, BP2, BP1 and BP0) bits and Status Register Protect (SRP) bits, a portion as small as a 4KB sector or the entire memory array can be hardware protected. The /WP pin is active low. When the QE bit of Status Register-2 is set for Quad I/O, the /WP pin function is not available since this pin is used for IO2. See Figure 1a-c for the pin configuration of Quad I/O operation.4.4HOLD (/HOLD)The /HOLD pin allows the device to be paused while it is actively selected. When /HOLD is brought low, while /CS is low, the DO pin will be at high impedance and signals on the DI and CLK pins will be ignored (don’t care). When /HOLD is brought high, device operation can resume. The/HOLD function can be useful when multiple devices are sharing the same SPI signals. The /HOLD pin is active low. When the QE bit of Status Register-2 is set for Quad I/O, the /HOLD pin function is not available since this pin is used for IO3. See Figure 1a-c for the pin configuration of Quad I/O operation.4.5Serial Clock (CLK)The SPI Serial Clock Input (CLK) pin provides the timing for serial input and output operations. ("See SPI Operations")4.6Reset (/RESET)The /RESET pin allows the device to be reset by the controller. For 8-pin packages, when QE=0, the IO3 pin can be configured either as a /HOLD pin or as a /RESET pin depending on Status Register setting. When QE=1, the /HOLD or /RESET function is not available for 8-pin configuration. On the 16-pin SOIC package, a dedicated /RESET pin is provided and it is independent of QE bit setting.5.BLOCK DIAGRAM ArrayFigure 2. W25Q128FV Serial Flash Memory Block Diagram6.FUNCTIONAL DESCRIPTIONS6.1SPI / QPI OperationsFigure 3. W25Q128FV Serial Flash Memory Operation Diagram6.1.1Standard SPI InstructionsThe W25Q128FV is accessed through an SPI compatible bus consisting of four signals: Serial Clock (CLK), Chip Select (/CS), Serial Data Input (DI) and Serial Data Output (DO). Standard SPI instructions use the DI input pin to serially write instructions, addresses or data to the device on the rising edge of CLK. The DO output pin is used to read data or status from the device on the falling edge of CLK.SPI bus operation Mode 0 (0,0) and 3 (1,1) are supported. The primary difference between Mode 0 and Mode 3 concerns the normal state of the CLK signal when the SPI bus master is in standby and data is not being transferred to the Serial Flash. For Mode 0, the CLK signal is normally low on the falling and rising edges of /CS. For Mode 3, the CLK signal is normally high on the falling and rising edges of /CS. 6.1.2Dual SPI InstructionsThe W25Q128FV supports Dual SPI operation when using instructions such as “Fast Read Dual Output (3Bh)” and “Fast Read Dual I/O (BBh)”. These instructions allow data to be transferred to or from the device at two to three times the rate of ordinary Serial Flash devices. The Dual SPI Read instructions are ideal for quickly downloading code to RAM upon power-up (code-shadowing) or for executing non-speed-critical code directly from the SPI bus (XIP). When using Dual SPI instructions, the DI and DO pins become bidirectional I/O pins: IO0 and IO1.6.1.3Quad SPI InstructionsThe W25Q128FV supports Quad SPI operation when using instructions such as “Fast Read Quad Output (6Bh)”, “Fast Read Quad I/O (EBh)”, “Word Read Quad I/O (E7h)” and “Octal Word Read Quad I/O (E3h)”. These instructions allow data to be transferred to or from the device four to six times the rate of ordinary Serial Flash. The Quad Read instructions offer a significant improvement in continuous and random access transfer rates allowing fast code-shadowing to RAM or execution directly from the SPI bus (XIP). When using Quad SPI instructions the DI and DO pins become bidirectional IO0 and IO1, and the /WP and /HOLD pins become IO2 and IO3 respectively. Quad SPI instructions require the non-volatile Quad Enable bit (QE) in Status Register-2 to be set.6.1.4QPI InstructionsThe W25Q128FV supports Quad Peripheral Interface (QPI) operations only when the device is switched from Standard/Dual/Quad SPI mode to QPI mode using the “Enter QPI (38h)” instruction. The typical SPI protocol requires that the byte-long instruction code being shifted into the device only via DI pin in eight serial clocks. The QPI mode utilizes all four IO pins to input the instruction code, thus only two serial clocks are required. This can significantly reduce the SPI instruction overhead and improve system performance in an XIP environment. Standard/Dual/Quad SPI mode and QPI mode are exclusive. Only one mode can be active at any given time. “Enter QPI (38h)” and “Exit QPI (FFh)” instructions are used to switch between these two modes. Upon power-up or after a software reset using “Reset (99h)” instruction, the default state of the device is Standard/Dual/Quad SPI mode. To enable QPI mode, the non-volatile Quad Enable bit (QE) in Status Register-2 is required to be set. When using QPI instructions, the DI and DO pins become bidirectional IO0 and IO1, and the /WP and /HOLD pins become IO2 and IO3 respectively. See Figure 3 for the device operation modes.6.1.5Hold FunctionFor Standard SPI and Dual SPI operations, the /HOLD signal allows the W25Q128FV operation to be paused while it is actively selected (when /CS is low). The/HOLD function may be useful in cases where the SPI data and clock signals are shared with other devices. For example, consider if the page buffer was only partially written when a priority interrupt requires use of the SPI bus. In this case the/HOLD function can save the state of the instruction and the data in the buffer so programming can resume where it left off once the bus is available again. The /HOLD function is only available for standard SPI and Dual SPI operation, not during Quad SPI or QPI. The Quad Enable Bit QE in Status Register-2 is used to determine if the pin is used as /HOLD pin or data I/O pin. When QE=0 (factory default), the pin is /HOLD, when QE=1, the pin will become an I/O pin, /HOLD function is no longer available.To initiate a/HOLD condition, the device must be selected with /CS low. A/HOLD condition will activate on the falling edge of the /HOLD signal if the CLK signal is already low. If the CLK is not already low the /HOLD condition will activate after the next falling edge of CLK. The/HOLD condition will terminate on the rising edge of the/HOLD signal if the CLK signal is already low. If the CLK is not already low the/HOLD condition will terminate after the next falling edge of CLK. During a/HOLD condition, the Serial Data Output (DO) is high impedance, and Serial Data Input (DI) and Serial Clock (CLK) are ignored. The Chip Select (/CS) signal should be kept active (low) for the full duration of the/HOLD operation to avoid resetting the internal logic state of the device.。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。