RT-3.30524中文资料

RTC-8564JEB3ROHS;RTC-8564NBB3ROHS;RTC-8564JE0ROHS;RTC-8564NBB0ROHS;中文规格书,Datasheet资料

CLKOUT CLKOE

Hours OUTPUT CONTROL DIVIDER Days Weekdays Month / Century Years

32.768 kHz frequency output function

•CLKOUT pin output (C-MOS output ), CL=30 pF •CLKOE pin enables output on/off control. •Output selectable <32.768kHz,1024Hz,32Hz,1Hz>

12.

6.00.2

11.

5.00.2

/INT VDD GND

Output -

Interrupt output

(N-ch open drain)

VSOJ20 pin

SON22 pin

VSOJ12pin

Connected to a positive power supply. Connected to a ground.

Unit

fSCL=0Hz

IBK CLKOUT;

CLKOE=GND

nA 275 700

VDD output OFF(LOW ) =3V VDD =5V

Condition Ta=-20C+70C Ta=-40 C+85C Ta=-20C+70C Ta=-40 C+85C

GND (GND) N.C. SDA SCL CLKOUT VDD CLKOE N.C. N.C.

17. 16. 15.

19. 18. 17.

Output

3. 4. 5. 6.

N.C. N.C. /INT GND

T8534中文资料

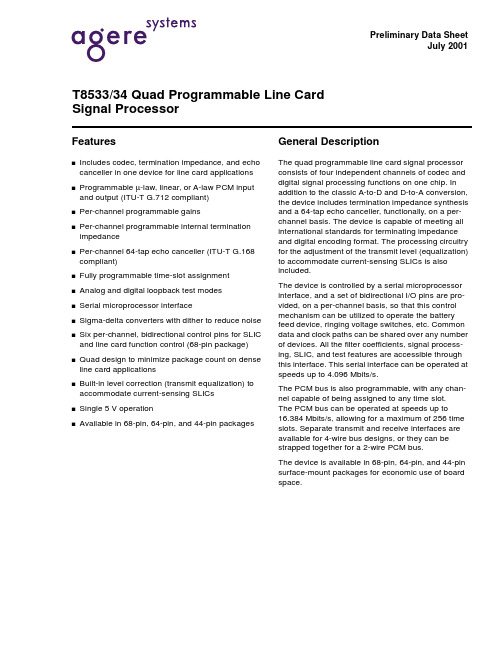

T8533/34 Quad ProgramProcessor

The PCM bus is also programmable, with any channel capable of being assigned to any time slot. The PCM bus can be operated at speeds up to 16.384 Mbits/s, allowing for a maximum of 256 time slots. Separate transmit and receive interfaces are available for 4-wire bus designs, or they can be strapped together for a 2-wire PCM bus.

s Programmable µ-law, linear, or A-law PCM input and output (ITU-T G.712 compliant)

s Per-channel programmable gains s Per-channel programmable internal termination

Preliminary Data Sheet July 2001

T8533/34 Quad Programmable Line Card Signal Processor

Features

s Includes codec, termination impedance, and echo canceller in one device for line card applications

普源rogal示波器中文手册

特有的内置函数/任意波形发生器模块

■ 业界第一个嵌入到数字存储示波器的函数/任意波形发生器模块 ■ 采用先进的DDS技术,得到精确、稳定、低失真的输出信号 ■ 200MSa/S采样率,12bits垂直分辨率 ■ 10MHz / 20MHz / 40MHz正弦波/方波信号最高频率 ■ 10MHz的脉冲信号最高频率 ■ 内置最高频率为1MHz的三角波、抽样函数、梯形波等30种常用波形 ■ 内置AM、FM、PWM、FSK、PSK和偏置调制等丰富的调制功能 ■ 1u~10MHz/1u~20MHz/1u~40MHz的扫频,可以正向扫描、

图9 X-Y模式测量李沙育图形 图10 视频触发测量全电视信号

更多功能

数字滤波器 仪器提供多种数字滤波器选择,包括低通、高通、带通和带阻滤 波器。您可以对采集信号按要求进行滤波处理以获得希望的结果。 可以利用数字滤波器来模拟硬件滤波的效果;利用数字滤波器滤 除混叠的噪声或误差信号以清楚地观察感兴趣的信号等。 可任意设定所需数字滤波器的3dB上限或下限截止频率。

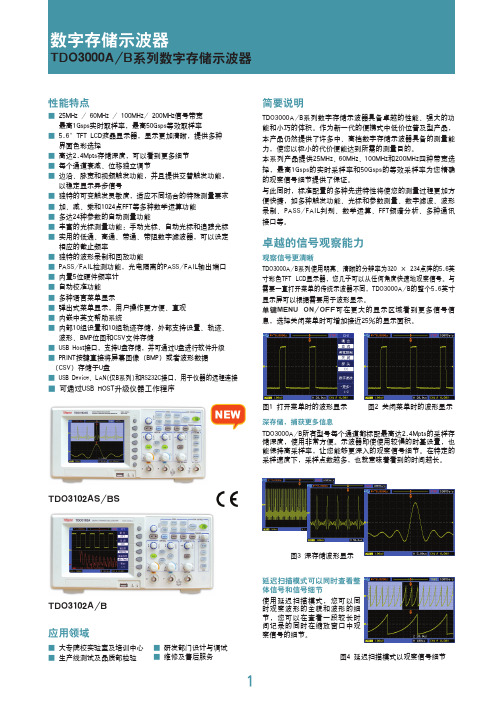

卓越的信号观察能力

观察信号更清晰 TDO3000A/B系列使用明亮、清晰的分辨率为320 × 234点阵的5.6英 寸彩色TFT LCD显示器,您几乎可以从任何角度快速地观察信号。与 需要一直打开菜单的传统示波器不同,TDO3000A/B的整个5.6英寸 显示屏可以根据需要用于波形显示。 单键MENU ON/OFF可在更大的显示区域看到更多信号信 息,选择关闭菜单时可增加接近25%的显示面积。

距屏幕中心±8格

×1,×10,×100,×1000

1MΩ||18pF

两个通道刻度和耦合设置相同的时候±150ps

400V(DC+AC峰值,@1MΩ)

ST SG3524 REGULATING PULSE WIDTH MODULATORS 数据手册

SG3524REGULATING PULSE WIDTH MODULATORSCOMPLETE PWM POWER CONTROL CIR-CUITRYUNCOMMITTED OUTPUTS FOR SINGLE-ENDED OR PUSH PULL APPLICATIONS LOW STANDBY CURRENT 8mA TYPICAL OPERATION UP TO 300KHz1% MAXIMUM TEMPERATURE VARIATION OF REFERENCE VOLTAGEDESCRIPTIONThe SG3524 incorporates on a single monolithic chip all the function required for the construction of regulating power suppies inverters or switching regulators. They can also be used as the control element for high power-output applications. The SG3524 family was designed for switching regu-lators of either polarity, transformer-coupled dc-to-dc converters, transformerless voltage dou-blers and polarity converter applications employing fixed-frequency, pulse-width modula-tion techniques. The dual alternating outputs al-lows either single-ended or push-pull applications.Each device includes an on-ship reference, error amplifier, programmable oscillator, pulse-steering flip flop, two uncommitted output transistors, a high-gain comparator, and current-limiting and shut-down circuitry.This is advanced information on a new product now in development or undergoing evaluation. Details are subject to change without notice.July 2000®BLOCK DIAGRAMDIP16 SO16ORDERING NUMBERS: SG3524N (DIP16) SG3524P (SO16)1/9ABSOLUTE MAXIMUM RATINGSSymbol Parameter Value Unit V IN Supply Voltage40VI C Collector Output Current100mAI R Reference Output Current50mAI T Current Through C T Terminal– 5mAP tot Total Power Dissipation at T amb = 70°C1000mW T stg Storage Temperature Range– 65 to 150°C T op Operating Ambient Temperature Range: 0 to 70°CTHERMAL DATASymbol Parameter DIP16SO16UnitR th j-amb R th j-alumina Thermal Resistance Junction-ambient Max.Thermal Resistance Junction-alumina (*) Max.80––50°C/W°C/W(*) Thermal resistance junction-alumina with the device soldered on the middle of an alumina supporting substrate measuring 15 x 20mm;0.65mm thickness with infinite heatsink.PIN CONNECTION(Top view)ELECTRICAL CHARACTERISTICS (unless otherwise stated, these specifications apply for Tj = 0 to 70°C, V IN = 20V, and f = 20KHz).Symbol Parameter Test Condition Min.Typ.Max.Unit REFERENCE SECTIONV REF Output Voltage 4.65 5.4V ∆V REF Line Regulation V IN = 8 to 40V1030mV ∆V REF Load Regulation I L = 0 to 20mA2050mV Ripple Rejection f = 120Hz, T j = 25°C66dBShort Circuit Current Limit V REF = 0, T j = 25°C100mA∆V REF/∆T Temperature Stability Over Operating Temperature range0.31%∆V REF Long Term Stability Tj = 125°C, t = 1000Hrs20mV OSCILLATOR SECTIONf MAX Maximum Frequency C T = 0.001µF, R T = 2KΩ300KHzInitial Accuracy R T and C T Constant5%Voltage Stability V IN = 8 to 40V, T j = 25°C1%∆f/∆T Temperature Stability Over Operating Temperature Range2% Output Amplitude Pin 3, T j = 25°C 3.5VOutput Pulse Width C T = 0.01µF, T j = 25°C0.5µs ERROR AMPLIFIER SECTIONV OS Input Offset Voltage V CM = 2.5V210mVI b Input Bias Current210µAG V Open Loop Voltage Gain6080dBCMV Common Mode Voltage T j = 25°C 1.8 3.4V CMR Common Mode Rejection T j = 25°C70dBB Small Signal Bandwidth A V = 0dB, T j = 25°C3MHzV O Output Voltage T j = 25°C0.5 3.8V COMPARATOR SECTIONDuty-cycle% Each Output On045% V IT Input Threshold Zero Duty-cycle1VMaximum Duty-cycle 3.5VI b Input Bias Current1µA CURRENT LIMITING SECTION180200220mV Sense Voltage Pin 9 = 2V with Error Amp. Set forMax. Out.T j = 25°CSense Voltage T.C.0.2mV/°C CMV Common Mode Voltage–11OUTPUT SECTION(each output)Collector-emitter Voltage40VCollector Leackage Curr.V CE = 40V0.150µASaturation Voltage I C = 50mA12VEmitter Output Voltage V IN = 20V1718V t r Rise Time R C = 2KΩ, T j = 25°C0.2µs t f Fall Time R C = 2KΩ, T j = 25°C0.1µsI q (*)Total Standby Current V IN = 40V810mA (*) Excluding oscillator charging current, error and current limit dividers, and with outputs open.Figure 1: Open-loop Voltage Amplification of Error Amplifier vs. Frequency Figure 2: Oscillator Frequency vs. TimingComponents.Figure 3: Output Dead Time vs. TimingCapacitance Value.Figure 4: Output Saturation Voltage vs. load Current.Figure 5: Open Loop Test Circuit.PRINCIPLES OF OPERATIONThe SG3524 is a fixed frequency pulse-with-modulation voltage regulator control circuit. The regulator operates at a frequency that is pro-grammed by one timing resistor (R T) and one tim-ing capacitor (C T). R T established a constant charging current for C T. This results in a linear voltage ramp at C T, which is fed to the compara-tor providing linear control of the output pulse width by the error amplifier. the SG3524 contains, an on-board 5V regulator that serves as a refer-ence as well as powering the SG3524’s internal control circuitry and is also useful in supplying ex-ternal support functions. This reference voltage is lowered externally by a resistor divider to provide a reference within the common mode range the error amplifier or an external reference may be used. The power supply output is sensed by a second resistor divider network to generale a feedback signal to error amplifier. The amplifier output voltage is then compared to the linear volt-age ramp at C T. The resulting modulated pulse out of the high-gain comparator is then steered to the appropriate output pass transistors (Q A or Q B) by the pulse-steering flip-flop, which is synchro-nously toggled by the oscillator output. The oscil-lator output pulse also serves as a blanking pulse to assure both output are never on simultane-ously during the transition times. The width of the blanking pulse is controlled by the value of C T. The outputs may be applied in a push-pull con-figuration in which their frequency is half that of the base oscillator, or paralleled for single-ended applications in which the frequency is equal to that of the oscillator. The output of the error am-plifier shares a common input to the comparator with the current limiting at shutdown circuitry and can be overridden by signals from either of these inputs. This common point is also available exter-nally and may be employed to control the gain of, or to compensate, the error amplifier, or to pro-vide additional control to the regulator.RECOMMENDED OPERATING CONDITIONS Supply voltage V IN8 to 40V Reference Output Current0 to 20mA Current trough C T Terminal- 0.03 to -2mA Timing Resistor, R T 1.8 to 100KΩTiming Capacitor, C T0.001 to 0.1µF TYPICAL APPLICATIONS DATA OSCILLATORThe oscillator controls the frequency of the SG3524 and is programmed by R T and C T ac-cording to the approximate formula:f =1.18R T C Twhere:R T is in KΩC T is in µFf is in KHzPratical values of C T fall between 0.001 and 0.1µF. Pratical values of R T fall between 1.8 and 100KΩ. This results in a frequency range typically from 120Hz to to 500KHz.BLANKINGThe output pulse of oscillator is used as a blank-ing pulse at the output. This pulse width is con-trolled by the value of C T.If small values of C T are required for frequency control, the oscillator out-put pulse width may still be increased by applying a shunt capacitance of up to 100pF from pin 3 to ground. If still greater dead-time is required, it should be accomplished by limiting the maximum duty cycle by clamping the output of the error am-plifier. This can easily be done with the circuit be-low:SYNCRONOUS OPERATIONWhen an external clock is desired, a clock pulse of approximately 3V can be applied directly to the oscillator output terminal. The impedance to ground at this point is approximately 2KΩ. In this configuration R T C T must be selected for a clock period slightly greater than that the external clock. If two more SG2524 regulators are to be operated synchronously, all oscillator output terminals should be tied together, all C T terminals con-nected to a single timing capacitor, and timing re-sistor connected to a single R T terminal. The other R T terminals can be left open or shorted to V REF. Minimum lead lengths should be used be-tween the C Tterminals.Figure 6.Figure 7: Flyback Converter Circuit.Figure 8: PUSH-PULL Transformer-coupled circuit.DIP16DIM.mm inch MIN.TYP.MAX.MIN.TYP.MAX.a10.510.020B 0.771.650.0300.065b 0.50.020b10.250.010D 200.787E 8.50.335e 2.540.100e317.780.700F 7.10.280I 5.10.201L 3.30.130Z1.270.050OUTLINE ANDMECHANICAL DATASO16 NarrowDIM.mm inch MIN.TYP.MAX.MIN.TYP.MAX.A 1.750.069a10.10.250.0040.009a2 1.60.063b 0.350.460.0140.018b10.190.250.0070.010C 0.50.020c145˚ (typ.)D (1)9.8100.3860.394E 5.8 6.20.2280.244e 1.270.050e38.890.350F (1) 3.840.1500.157G 4.6 5.30.1810.209L 0.4 1.270.0160.050M 0.620.024S(1) D and F do not include mold flash or protrusions. Mold flash or potrusions shall not exceed 0.15mm (.006inch).OUTLINE AND MECHANICAL DATA8˚(max.)Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.The ST logo is a registered trademark of STMicroelectronics© 2000 STMicroelectronics – Printed in Italy – All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco -Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A.。

ADATE305BSVZ资料

250 MHz Dual Integrated DCL with LevelSetting DACs, Per Pin PMU, and Per Chip VHHADATE305 Rev. 0Information furnished by Analog Devices is believed to be accurate and reliable. However, noresponsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 Fax: 781.461.3113 ©2008 Analog Devices, Inc. All rights reserved.FEATURESDriver3-level driver with high-Z mode and built-in clamps Precision trimmed output resistanceLow leakage mode (typically <10 nA)Voltage range: up to −2.0 V to +6.0 V1.6 ns minimum pulse width, 2 V terminated2.1 ns minimum pulse width, 3 V terminated ComparatorWindow and differential comparator500 MHz input equivalent bandwidthLoad±12 mA maximum current capabilityPer pin PMUForce voltage range: up to −2.0 V to +6.0 V5 current ranges: 32 mA, 2 mA, 200 μA, 20 μA, 2 μA Levels14-bit DAC for DCL levelsTypically < ±5 mV INL (calibrated)16-bit DAC for PMU levelsTypically < ±1.5 mV INL (calibrated) linearity in FV mode HVOUT output buffer0 V to 13.5 V output range100-lead, 14 mm × 14 mm, TQFP_EP package900 mW per channel with no loadAPPLICATIONSAutomatic test equipmentSemiconductor test systemsBoard test systemsInstrumentation and characterization equipment GENERAL DESCRIPTIONThe ADATE305 is a complete, single-chip solution that performs the pin electronic functions of the driver, the comparator, and the active load (DCL), per pin PMU, and dc levels for ATE appli-cations. The device also contains an HVOUT driver with a VHH buffer capable of generating up to 13.5 V.The driver features three active states: data high mode, data low mode, and term mode, as well as an inhibit state. The inhibit state, in conjunction with the integrated dynamic clamp, facili-tates the implementation of a high speed active termination. The ADATE305 supports two output voltage ranges: −2.0 Vto +6.0 V and −1.5 V to +6.0 V by adjusting the positive and negative supply voltages.The ADATE305 can be used as either a dual single-ended drive/ receive channel or a single differential drive/receive channel. Each channel of the ADATE305 features a high speed window comparator per pin for functional testing, as well as a per pin PMU with FV, or FI and MV, or MI functions. All necessary dc levels for DCL functions are generated by on-chip 14-bit DACs. The per pin PMU features an on-chip 16-bit DAC for high accuracy and contains integrated range resistors to minimize external component counts.The ADATE305 uses a serial bus to program all functional blocks and has an on-board temperature sensor for monitoring the device temperature.ADATE305Rev. 0 | Page 2 of 56TABLE OF CONTENTSFeatures .............................................................................................. 1 Applications ....................................................................................... 1 General Description ......................................................................... 1 Revision History ............................................................................... 2 Functional Block Diagram .............................................................. 3 Specifications ..................................................................................... 4 Total Function ............................................................................... 4 Driver ............................................................................................. 5 Reflection Clamp .......................................................................... 7 Normal Window Comparator .................................................... 7 Differential Comparator .............................................................. 9 Active Load .................................................................................. 11 PMU ............................................................................................. 12 External Sense (PMUS_CHx) ................................................... 16 DUTGND Input ......................................................................... 16 Serial Peripheral Interface ......................................................... 17 HVOUT Driver ........................................................................... 17 Overvoltage Detector (OVD) ................................................... 18 16-Bit DAC Monitor MUX ....................................................... 18 Absolute Maximum Ratings ......................................................... 19 Thermal Resistance .................................................................... 19 Explanation of Test Levels ......................................................... 19 ESD Caution................................................................................ 19 Pin Configuration and Function Descriptions ........................... 20 Typical Performance Characteristics ........................................... 23 SPI Details ....................................................................................... 34 Definition of SPI Word .............................................................. 35 Write Operation.......................................................................... 36 Read Operation........................................................................... 37 Reset Operation .......................................................................... 38 Register Map ................................................................................... 39 Details of Registers ......................................................................... 40 User Information ............................................................................ 42 Details of DACs vs. Levels ......................................................... 43 Recommended PMU Mode Switching Sequences ................. 46 Block Diagrams ............................................................................... 49 Outline Dimensions ....................................................................... 53 Ordering Guide .. (53)REVISION HISTORY8/08—Revision 0: Initial VersionADATE305Rev. 0 | Page 3 of 56FUNCTIONAL BLOCK DIAGRAMTEMPSENSEHVOUTDUT0OVD_CH007280-001*ONE PER DEVICE.Figure 1. One of Two Channels Is ShownADATE305Rev. 0 | Page 4 of 56SPECIFICATIONSCharacterization and production tests performed using Power Supply Range 1 (see Table 36). V DD = +10.0 V , V CC = +3.3 V , V SS = −5.25 V , V PLUS = +16.75 V , V COMP_VTT = +3.3 V , V REF = +5.0 V , V REF_GND = 0.0 V . All default test conditions are as defined in Table 38. All specified values are at T J = 70°C, where T J corresponds to the internal temperature sensor, unless otherwise noted. Temperature coefficients are measured at T J = 70°C ± 20°C, unless otherwise noted. Typical values are based on design, simulation analyses, and/or limited bench evaluations. Typical values are not tested or guaranteed. Test levels are specified in the Explanation of Test Levels section.TOTAL FUNCTIONTable 1.Parameter Min Typ Max Unit TestLevel Conditions/Comments TOTAL F UNCTION Output Leakage Current PE Disable Range E −20.0 5.3 +20.0 nA P −1.5 V < V DUTx < +6.0 V; PMU and PE disabled via SPI; PMURange E, VCH = 7.0 V, VCL = −2.5 VPE Disable Range A, B, C, D 5.3 nA C T −1.5 V < V DUTx < +6.0 V; PMU and PE disabled via SPI; PMURange A, PMU Range B, PMU Range C, and PMU Range D, VCH = +7.0 V, VCL = −2.5 VHigh-Z Mode −400 5.4 +400 nA P −1.5 V < V DUTx < +6.0 V; PMU disabled and PE enabled via SPI;RCV active, VCH = +7.0 V, VCL = −2.5 VOutput Capacitance 4 pF S VTERM mode operation DUT Pin Range −1.5 +6.0 V D POWER SUPPLIES Total Supply Range, V PLUS to V SS 22.5 23.25 V D Defines PSRR conditions VPLUS Supply, V PLUS 16.25 16.75 17.25 V D Defines PSRR conditionsPositive Supply, V DD 9.5 10.0 10.5 V D Defines PSRR conditions Negative Supply, V SS −5.50 −5.25 −5.00 V D Defines PSRR conditions Logic Supply, V CC 3.1 3.3 3.5 V D Defines PSRR conditions Comparator Termination, V COMP_VTT 3.3 5.0 V D V PLUS Supply Current, I PLUS −1.0 +1.3 +3.0 mA P HVOUT disabled V PLUS Supply Current, I PLUS 4.0 12.7 17.0 mA P HVOUT enabled, RCV active, no load, VHH = 12 V Logic Supply Current, I CC 1.0 2.7 10.0 mA P Quiescent (SPI is static)Comparator Termination Current,I COMP_VTT10.0 17 26.0 mA P Positive Supply Current, I DD 72 92 105 mA P Load power down (IOH = IOL = 0 mA) Negative Supply Current, I SS 100 119 135 mA P Load power down (IOH = IOL = 0 mA) Total Power Dissipation 1.0 1.7 1.9 W P Load power down (IOH = IOL = 0 mA) Positive Supply Current, I DD 102 133 154 mA P Load active off (IOH = IOL = 12 mA) Negative Supply Current, I SS 130 158 183 mA P Load active off (IOH = IOL = 12 mA) Total Power Dissipation 1.8 2.2 2.5 W P Load active off (IOH = IOL = 12 mA) TEMPERATURE MONITORS Temperature Sensor Gain 10 mV/K C T Temperature Sensor Accuracy Without Calibration over25°C to 100°C6 °C C TTemperature voltage available on Pin 3 at all times and Pin 28 when selected (see Table 24 and Table 36) VREF INPUT Reference Input Voltage Range for DACs (VREF Pin) 4.95 5 5.05 V D Referenced to V REF_GND ; not referenced to V DUTGND Input Bias Current 0.1 100 μA P Tested with 5 V appliedADATE305Rev. 0 | Page 5 of 56DRIVERVH − VL ≥ 200 mV (to meet dc/ac specifications).Table 2.Parameter Min Typ Max Unit Test Level Conditions/Comments DC SPECIFICATIONS High-Speed Differential Logic Input Characteristics (DATA, RCV) Input Termination Resistance 92 100 108 Ω P Push 6 mA into xP pins, force 1.3 V on xN pins; measure voltagefrom xP to xN, calculate resistance (ΔV/ΔI)1Input Voltage Differential 0.2 1.0 V P F Common-Mode Voltage 0.85 2.35 V P F Input Bias Current −20.0 +2.2 +20.0 μA P Each pin tested at 2.85 V and 0.35 V, while the other high speedpin remains openPin Output Characteristics Output High Range, VH −1.4 +6.0 V D Output Low Range, VL −1.5 +5.9 V D Output Term Range, VT −1.5 +6.0 V D Functional Amplitude (VH − VL) 0.0 7.5 V D Amplitude can be programmed to VH = VL, accuracy specsapply when VH − VL ≥ 200 mVDC Output Current Limit Source75 100 120 mA P Driver high, VH = 6.0 V, short DUTx pin to −2.0 V, measure current DC Output Current Limit Sink −120 −100 −75 mA P Driver low, VL = −1.5 V, short DUTx pin to 6.0 V, measure current Output Resistance, ±50 mA 45.0 47.0 49.0 Ω P Source: driver high, VH = 3.0 V, I DUTx = 1 mA and 50 mA;sink: driver low, VL = 0.0 V, I DUTx = −1 mA and −50 mA; ΔV DUT /ΔI DUTABSOLUTE ACCURACY VH tests done with VL = −2.5 V and VT= −2.5 V;VL tests done with VH = 7.5 V and VT = 7.5 V;VT tests done with VL = −2.5 V and VH = +7.5 V; unless otherwise specifiedVH, VL, VT Uncalibrated Accuracy −250 ±75 +250 mV P Error measured at calibration points of 0 V and 5 V VH, VL, VT Offset Tempco ±450 μV/°C C T Measured at calibration points VH, VL, VT DNL ±1 mV C T After two-point gain/offset calibration VH, VL, VT INL −10 ±2.5 +10 mV P After two-point gain/offset calibration; measured over driveroutput rangesVH, VL, VT Resolution 0.6 +1 mV P F After two-point gain/offset calibration; range/number of DACbits as measured at calibration points of 0 V and 5 VDUTGND Voltage Accuracy −7 ±1.3 +7 mV P Over ±0.1 V range; measured at end points of VH, VL, and VTfunctional rangeVH, VL, VT Crosstalk ±2 mV C T VL = −1.5 V: VH = −1.4 V → 6.0 V, VT = −1.5 V → 6.0 V;VH = 6.0 V: VL = −1.5 V → 5.9 V, VT = −1.5 V → 6.0 V;VT = 1.5 V: VL = −1.5 V → 5.9 V, VH = −1.4 V → 6.0 V; dc crosstalk on VL, VH, VT output level when other driver DACs are variedOverall Voltage Accuracy ±10 mV C T Sum of INL, crosstalk, DUTGND, and tempco over ±5°C, aftergain/offset calibrationVH, VL, VT DC PSRR ±15 mV/V C T Measured at calibration points AC SPECIFICATIONS Rise/F all Times Toggle DATAxx 0.2 V Programmed Swing 1000 ps C B VH = 0.2 V, VL = 0.0 V, terminated; 20% to 80% 1.0 V Programmed Swing 800 ps C B VH = 1.0 V, VL = 0.0 V, terminated; 20% to 80% 2.0 V Programmed Swing 950 ps C B VH = 2.0 V, VL = 0.0 V, terminated; 20% to 80% 3.0 V Programmed Swing 1000 1175 1500 ps P/C B VH = 3.0 V, VL = 0.0 V, terminated; 20% to 80% 3.0 V Programmed Swing 1650 ps C B VH = 3.0 V, VL = 0.0 V, unterminated; 10% to 90% 5.0 V Programmed Swing 2350 ps C B VH = 5.0V, VL = 0.0 V, unterminated; 10% to 90% Rise to Fall Matching 30 ps C B VH = 3.0 V, VL = 0.0 V, terminated; rise to fall within one channelADATE305Rev. 0 | Page 6 of 56Parameter Min Typ Max Unit TestLevel Conditions/Comments Minimum Pulse Width Toggle DATAxx 1.0 V Programmed Swing 1.4 ns C B VH = 1.0 V, VL = 0.0 V, terminated; timing error ±75 ps 1.6 ns C B VH = 1.0 V, VL = 0.0 V, terminated; less than 10% amplitudedegradation2.0 V Programmed Swing 1.6 ns C B VH = 2.0 V, VL = 0.0 V, terminated; timing error ±75 ps 1.8 ns C B VH = 2.0 V, VL = 0.0 V, terminated; less than 10% amplitudedegradation3.0 V Programmed Swing 2.1 ns C B VH = 3.0 V, VL = 0.0 V, terminated; timing error ±75 ps 2.3 ns C B VH = 3.0 V, VL = 0.0 V, terminated; less than 10% amplitudedegradationMaximum Toggle Rate 2.0 V Programmed Swing 250 MHz C B VH = 2.0 V, VH = 0.0 V, terminated, 10% amplitude degradation 3.0 V Programmed Swing 200 MHz C B VH = 3.0 V, VH = 0.0 V, terminated, 10% amplitude degradation Dynamic Performance, Drive (VH to VL and VL to VH) Toggle DATAxx Propagation Delay Time 3.0 ns C B VH = 3.0 V, VL = 0.0 V, terminated Propagation Delay Tempco 3.0 ps/°C C T VH = 3.0 V, VL = 0.0 V, terminated Delay Matching VH = 3.0 V, VL = 0.0 V, terminated Edge to Edge 115 ps C B Rising vs. falling Channel to Channel 30 ps C B Rising vs. rising, falling vs. falling Delay Change vs. Duty Cycle 30 ps C B VH = 3.0 V, VL = 0.0 V, terminated; 5% to 95% duty cycle; 1 MHz Overshoot and Undershoot 20 mV C B VH = 3.0 V, VL = 0.0 V, terminated Settling Time (VH to VL) Toggle DATAxx To Within 3% of Final Value 5 ns C B VH = 3.0 V, VL = 0.0 V, terminated To Within 1% of Final Value 35 ns C B VH = 3.0 V, VL = 0.0 V, terminated Dynamic Performance, VT (VH or VL to VT and VT to VH or VL)Toggle RCVx Propagation Delay Time 3.3 ns C B VH = 3.0 V, VT = 1.5 V, VL = 0.0 V, terminated Delay Matching, Edge to Edge 100 ps C B VH = 3.0 V, VT = 1.5 V, VL = 0.0 V, terminated; rising vs. falling Propagation Delay Tempco 4.0 ps/°C C T VH = 3.0 V, VT = 1.5 V, VL = 0.0 V, terminated Transition Time, Active to VT and VT to Active 0.85 ns C B VH = 3.0 V, VT = 1.5 V, VL = 0.0 V, terminated; 20% to 80%Dynamic Performance, Inhibit (VH or VL to/from Inhibit)Toggle RCVx Propagation Delay Time VH = +1.0 V, VL = −1.0 V, terminated Active to Inhibit 4.5 ns C B Inhibit to Active 6.9 ns C B Transition Time VH =+1.0 V, VL = −1.0 V, terminated; 20% to 80% Active to Inhibit 2.6 ns C B Inhibit to Active 0.75 ns C B I/O Spike 190 mV C B VH = 0.0 V, VL = 0.0 V, terminated1The xP pins include DATA0P, DATA1P, RCV0P, and RCV1P; the xN pins include DATA0N, DATA1N, RCV0N, and RCV1N. For example, push 6 mA into the DATA0P pin, force 1.3 V into DATA0N, and measure the voltage from DATA0P to DATA0N.ADATE305Rev. 0 | Page 7 of 56REFLECTION CLAMPClamp accuracy specifications apply when VCH > VCL. Table 3.Parameter Min Typ Max Unit TestLevel Conditions/CommentsVCH Range −1.0 +6.0 V D Uncalibrated Accuracy −200 ±50 +200 mV P Driver high-Z, sinking 1 mA; VCH error measured at thecalibration points of 0.0 V and 5.0 VResolution 0.6 0.75 mV P F Driver high-Z, sinking 1 mA; after two-point gain/offsetcalibration; range/number of DAC bits as measured at the calibration points of 0.0 V and 5.0 VDNL ±1 mV C T Driver high-Z, sinking 1 mA; after two-point gain/offsetcalibrationINL −40 ±2 +40 mV P Driver high-Z, sinking 1 mA; after two-point gain/offsetcalibration; measured over VCH range of −1.0 V to +6.0 VTempco −0.3 mV/°C C T Measured at calibration points VCL Range −1.5 +5.0 V D Uncalibrated Accuracy −200 ±50 +200 mV P Driver high-Z, sourcing 1 mA; VCL error measured at thecalibration points of 0.0 V and 5.0 VResolution 0.6 0.75 mV P F Driver high-Z, sourcing 1 mA; after two-point gain/offsetcalibration; range/number of DAC bits as measured at the calibration points of 0.0 V and 5.0 VDNL ±1 mV C T Driver high-Z, sourcing 1 mA; after two-point gain/offsetcalibrationINL −40 ±2 +40 mV P Driver high-Z, sourcing 1 mA; after two-point gain/offsetcalibration; measured over VCL range of −1.5 V to +5 VTempco 0.5 mV/°C C T Measured at calibration points DC CLAMP CURRENT LIMIT VCH −120 −85 −60 mA P Driver high-Z, VCH = 0 V, VCL = −1.5 V, V DUTx = +5 V VCL 60 85 120 mA P Driver high-Z, VCH = 6.0 V, VCL = 5.0 V, V DUTx = 0.0 V DUTGND VOLTAGE ACCURACY −7 ±1 +7 mV P Over ±0.1 V range; measured at the end points of VCHand VCL functional rangeNORMAL WINDOW COMPARATORVOH tests done with VOL = −1.5 V; VOL tests done with VOH = 6.0 V , unless otherwise specified. Table 4.Parameter Min Typ Max Unit TestL evel Conditions/Comments DC SPECI FICATIONS Input Voltage Range −1.5 +6.0 V D Differential Voltage Range ±0.1 ±7.5 V D Comparator Input Offset Vol-tage Accuracy, Uncalibrated −150 ±30 +150 mV P Offset measured at the calibrationpoints of 0.0 V and 5.0 V Comparator Threshold Resolution 0.6 1 mV P F After two-point gain/offset calibration; range/number of DAC bits as measuredat the calibration points of 0 V and 5 VComparator Threshold DNL ±1 mV C T After two-point gain/offset calibration Comparator Threshold INL −7 ±1.3 +7 mV P After two-point gain/offset calibration;measured over VOH, VOL range of −1.5 V to +6.0 VComparator Input Offset Voltage Tempco±100 μV/°C C T Measured at calibration points DUTGND Voltage Accuracy −7 ±0.5 +7 mV P Over ±0.1 V range; measured at endpoints of VOH and VOL functional rangeADATE305Rev. 0 | Page 8 of 56Parameter Min Typ Max Unit TestL evel Conditions/Comments Comparator Uncertainty Range 6.0 mV C B V DUTx = 0 V, sweep comparatorthreshold to determine uncertainty regionDC Hysteresis 0.5 mV C B V DUTx = 0 V DC PSRR ±5 mV/V C T Measured at calibration points Digital Output Characteristics Internal Pull-Up Resistance to Comparator, COMP_VTT Pin 40 50 60 Ω P Pull 1 mA and 10 mA from Logic 1 leg and measure ΔV to calculate resis-tance; measured ΔV/9 mA; done forboth comparator logic statesV COMP_VTT Range 3.3 5.0 V D Common-Mode Voltage V COMP_VTT − 1.88 V C T Measured with 100 Ω differentialterminationV COMP_VTT − 2.075 V COMP_VTT − 1.675 V P Measured with no external termination Differential Voltage 250 mV C T Measured with 100 Ω differentialtermination400 500 600 mV P Measured with no external termination Rise/Fall Time, 20% to 80% 450 ps C B Measured with each comparator legterminated 50 Ω to GNDAC SPECIFICATIONS Input transition time = 800 ps, 10% to90%; measured with each comparator leg terminated 50 Ω to GND; unless otherwise specifiedPropagation Delay, Input to Output 1.75 ns C B V DUTx = 0 V to 1.5 V swing, Driver VTERM mode, VT = 0.0 V; high-sidemeasurement: VOH = 0.75 V, VOL = −1.5 V; low-side measurement: VOH = 6.0 V, VOL = 0.75 VPropagation Delay Tempco 5 ps/°C C T V DUTx = 0 V to 1.5 V swing, DriverVTERM mode, VT = 0.0 V; high-side measurement: VOH = 0.75 V, VOL = −1.5 V; low-side measurement: VOH = 6.0 V, VOL = 0.75 VPropagation Delay Matching V DUTx = 0 V to 1.5 V swing, DriverVTERM mode, VT = 0.0 V; high-sidemeasurement: VOH = 0.75 V, VOL = −1.5 V; low-side measurement: VOH = 6.0 V, VOL = 0.75 VHigh Transition to Low Transition200 ps C B High to Low Comparator 50 ps C B Propagation Delay Change (with Respect To)Slew Rate, 800 ps, 1 ns, 1.2 ns, and 2.2 ns (10% to 90%) 50 ps C B V DUTx = 0 V to 1.5 V swing, Driver VTERM mode, VT = 0.0 V; high-sidemeasurement: VOH = 0.75 V, VOL = −1.5 V; low-side measurement: VOH = 6.0 V, VOL = 0.75 VOverdrive, 250 mV and 1.5 V 75 ps C B For 250 mV: V DUTx = 0 V to 0.5 V swing;for 1.5 V: V DUTx = 0 V to 1.75 V swing; Driver VTERM mode, VT = 0.0 V; high-side measurement: VOH = 0.25 V, VOL = −1.5 V; low-side measurement: VOH = 6.0 V, VOL = 0.25 VPulse Width, Sweep 1.6 ns to 10 ns 75 ps C B V DUTx = 0 V to 1.5 V swing @ 32.0 MHz, Driver VTERM mode, VT = 0.0 V; high-side measurement: VOH = 0.5 V, VOL =−1.5 V; low-side measurement: VOH = 6.0 V, VOL = 0.5 VADATE305Rev. 0 | Page 9 of 56Parameter Min Typ Max Unit TestLevel Conditions/CommentsDuty Cycle, 5% to 95% 50 ps C B V DUTx = 0 V to 1.5 V swing @ 1.0 MHz,Driver VTERM mode, VT =0.0 V; high-side measurement: VOH = 0.75 V, VOL = −1.5 V; low-side measurement: VOH = 6.0 V, VOL = 0.75 VMinimum Pulse Width 2.0 ns C B V DUTx = 0 V to 1.5 V swing, DriverVTERM mode, VT = 0.0 V; less than 12% amplitude degradation measured by shmooInput Equivalent Bandwidth, Terminated 500 MHz C B V DUTx = 0 V to 1.5 V swing, Driver VTERM mode, VT = 0.0 V; as measuredby shmooERT High-Z Mode, 3 V, 20% to 80% 2.5 ns C B V DUTx = 0 V to 3.0 V swing, driver high-Z; as measured by shmoo; input transitiontime of ~2000 ps, 10% to 90%DIFFERENTIAL COMPARATORVOH tests done with VOL = −1.1 V , VOL tests done with VOH = +1.1 V , unless otherwise specified. Table 5.Parameter Min Typ Max Unit Test L evel Conditions/Comments DC SPECIFICATIONS Input Voltage Range −1.25 +4.5 V D Operational Differential Voltage Range±0.05 ±1.1 V D Maximum Differential Voltage Range ±8 V D Comparator Input Offset Voltage Accuracy, Uncalibrated −150 ±35 +150 mV P/C T Offset measured at differential calibration points +1.0 V and −1.0 V, with common mode = 0.0 V VOH, VOL Resolution 0.6 1 mV P F After two-point gain/offset calibration; range/number ofDAC bits as measured at differential calibration points +1.0 V and −1.0 V, with common mode = 0.0 VVOH, VOL DNL ±1 mV C T After two-point gain/offset calibration; common mode = 0.0 VVOH, VOL INL −15 ±2.0 +15 mV P After two-point gain/offset calibration; measured over VOH,VOL range of −1.1 V to +1.1 V, common mode = 0.0 VVOH, VOL Offset Voltage Tempco ±200 μV/°C C T Measured at calibration points Comparator Uncertainty Range 18 mV C B V DUTx = 0 V, sweep comparator threshold to determineuncertainty regionDC Hysteresis 0.5 mV C B V DUTx = 0 V CMRR 0.15 1 mV/V P Offset measured at common-mode voltage points of−1.5 V and +4.5 V, with differential voltage = 0.0 VDC PSRR ±1.5 mV/V C T Measured at calibration points AC SPECIFICATIONS Input transition time = 800 ps, 10% to 90%, measuredwith each comparator leg terminated 50 Ω to GNDPropagation Delay, Input to Output 1.7 ns C B V DUT0 = 0 V, V DUT1 = −0.5 V to +0.5 V swing, Driver VTERMmode, VT = 0.0 V; high-side measurement: VOH = 0.0 V, VOL = −1.1 V; low-side measurement: VOH = 1.1 V, VOL = 0.0 V; repeat for other DUT channelPropagation Delay Tempco 5 ps/°C C T V DUT0 = 0 V, V DUT1 = −0.5 V to +0.5 V swing, Driver VTERMmode, VT = 0.0 V; high-side measurement: VOH = 0.0 V, VOL = −1.1 V; low-side measurement: VOH = 1.1 V, VOL = 0.0 V; repeat for other DUT channelPropagation Delay Matching V DUT0 = 0 V, V DUT1 = −0.5 V to +0.5 V swing, Driver VTERMmode, VT = 0.0 V; high-side measurement: VOH = 0.0 V, VOL = −1.1 V; low-side measurement: VOH = 1.1 V, VOL = 0.0 V; repeat for other DUT channelHigh Transition to Low Transition 100 ps C B High-to-Low Comparator 50 ps C BADATE305Rev. 0 | Page 10 of 56Parameter Min Typ Max Unit TestLevel Conditions/Comments Propagation Delay Change (with Respect To) V DUT0 = 0 V, V DUT1 = −0.5 V to +0.5 V swing, Driver VTERM mode, VT = 0.0 V; high-side measurement: VOH = 0.0 V,VOL = −1.1 V; low-side measurement: VOH = 1.1 V, VOL = 0.0 V; repeat for other DUT channelSlew Rate, 800 ps, 1ns, 1.2ns, and 2.2 ns (10% to 90%) 60 ps C B V DUT0 = 0 V, V DUT1 = −0.5 V to +0.5 V swing, Driver VTERM mode, VT = 0.0 V; high-side measurement: VOH = 0.0 V,VOL = −1.1 V; low-side measurement: VOH = 1.1 V, VOL = 0.0 V; repeat for other DUT channelOverdrive, 250 mV and 750 mV 100 ps C B V DUT0 = 0 V, for 250 mV: V DUT1 = 0 V to 0.5 V swing; for750 mV: V DUT1 = 0 V to 1.0 V swing, Driver VTERM mode, VT = 0.0 V; VOH = −0.25 V; repeat for other DUT channel with comparator threshold = +0.25 VPulse Width, Sweep from 1.6 ns to 10 ns 75 ps C B V DUT0 = 0 V, V DUT1 = −0.5 V to +0.5 V swing @ 32 MHz, Driver VTERM mode, VT = 0.0 V; high-side measurement: VOH =0.0 V, VOL = −1.1 V; low-side measurement: VOH = 1.1 V, VOL = 0.0 V; repeat for other DUT channelDuty Cycle, 5% to 95% 60 ps C B V DUT0 = 0 V, V DUT1 = −0.5 V to +0.5 V swing @ 1 MHz, DriverVTERM mode, VT = 0.0 V; high-side measurement: VOH = 0.0 V, VOL = −1.1 V; low-side measurement: VOH = 1.1 V, VOL = 0.0 V; repeat for other DUT channelMinimum Pulse Width 2.5 ns C B V DUT0 = 0 V, V DUT1 = −0.5 V to +0.5 V swing, Driver VTERMmode, VT = 0.0 V; high-side measurement: VOH = 0.0 V, VOL = −1.1 V; low-side measurement: VOH = 1.1 V, VOL = 0.0 V; less than 10% amplitude degradation measured by shmoo; repeat for other DUT channelInput Equivalent Bandwidth, Terminated 400 MHz C B V DUT0 = 0 V, V DUT1 = −0.5 V to +0.5 V swing, Driver VTERM mode, VT = 0.0 V; high-side measurement: VOH = 0.0 V,VOL = −1.1 V; low-side measurement: VOH = 1.1 V, VOL = 0.0 V; less than 22% amplitude degradation measured by shmoo; repeat for other DUT channelACTIVE LOADSee Table 29 for load control information. Table 6.Parameter Min Typ Max Unit TestLevel Conditions/Comments DC SPECIFICATIONS Load active on, RCV active, unless otherwise noted Input Characteristics VCOM Voltage Range −1.25 +5.75 V D V DUT Range −1.5 +6.0 V D VCOM Accuracy, Uncalibrated −200 ±30 +200 mV P IOH = IOL = 6 mA, VCOM error measured at the calibrationpoints of 0.0 V and 5.0 VVCOM Resolution 0.6 1 mV P F IOH = IOL = 6 mA, after two-point gain/offset calibration;range/number of DAC bits as measured at the calibration points of 0.0 V and 5.0 VVCOM DNL ±1 mV C T IOH = IOL = 6 mA, after two-point gain/offset calibration VCOM INL −7 ±2 +7 mV P IOH = IOL = 6 mA, after two-point gain/offset calibration;measured over VCOM range of −1.25 V to +5.75 VDUTGND Voltage Accuracy −7 ±1 +7 mV P Over ±0.1 V range; measured at end points of VCOM functionalrangeOutput Characteristics IOL Maximum Source Current 12 mA D Uncalibrated Offset −600.0 ±100 +600.0 μA P IOH = 0 mA, VCOM = 1.5 V, V DUTx = 0.0 V, IOL offset calculatedfrom the calibration points of 1 mA and 11 mAUncalibrated Gain −12 ±4 +12 % P IOH = 0 mA, VCOM = 1.5 V, V DUTx = 0.0 V, IOL gain calculated fromthe calibration points of 1 mA and 11 mAResolution 1.5 2 μA P F IOH = 0 mA, VCOM = 1.5 V, V DUTx = 0.0 V, after two-point gain/offset calibration; range/number of DAC bits as measured at the calibration points of 1 mA and 11 mADNL ±3.0 μA C T IOH = 0 mA, VCOM = 1.5 V, V DUTx = 0.0 V, after two-pointgain/offset calibrationINL −80 ±20 +80 μA P IOH = 0 mA, VCOM = 1.5 V, V DUTx = 0.0 V, after two-point gain/offset calibration; measured over IOL range of 0 mA to 12 mA90% Commutation Voltage 0.25 V P IOH = IOL = 12 mA, VCOM = 2.0 V, measure IOL reference atV DUTx = −1.0 V, measure IOL current at V DUTx = 1.75 V, ensure > 90% of reference currentIOH Maximum Sink Current 12 mA D Uncalibrated Offset −600.0 ±100 +600.0 μA P IOL = 0 mA, VCOM = 1.5 V, V DUTx = 3.0 V, IOH offset calculatedfrom the calibration points of 1 mA and 11 mAUncalibrated Gain −12 ±4 +12 % P IOL = 0 mA, VCOM = 1.5 V, V DUTx = 3.0 V, IOH gain calculated fromthe calibration points of 1 mA and 11 mAResolution 1.5 2 μA P F IOL = 0 mA, VCOM = 1.5 V, V DUTx = 3.0 V, after two-pointgain/offset calibration; range/number of DAC bits as measured at the calibration points of 1 mA and 11 mADNL ±3.0 μA C T IOL = 0 mA, VCOM = 1.5 V, V DUTx = 3.0 V, after two-pointgain/offset calibrationINL −80 ±20 +80 μA P IOL = 0 mA, VCOM = 1.5 V, V DUTx = 3.0 V, after two-point gain/offset calibration; measured over IOH range of 0 mA to 12 mA90% Commutation Voltage 0.25 V P IOH = IOL =12 mA, VCOM = 2.0 V, measure IOH reference atV DUTx = 5.0 V, measure IOH current at V DUTx = 2.25 V, ensure > 90% of reference currentOutput Current Tempco ±1.5 μA/°C C T Measured at calibration points。

RP-3.305S中文资料

Total Output current (%)

Total Output current (%)

Deviation / Load

25.000 20.000 25.000 20.000

Deviation / Load

25.000 20.000

Deviation / Load

Deviation from Nominal (%)

100%

RP-xx05D

Efficiency / Load

100 80 60 40 100

RP-xx12D

Efficiency / Load

100 80 60

RP-xx15D

Efficiency / Load

80 60 40

1205

0512

1212

0515

0505 Efficiency %

40

1215

0515

1205

1212

1215

0% 20% 40% 60% Total Output current (%)

80%

100%

0% 20% 40% 60% Total Output current (%)

80%

100%

0% 20% 40% 60% Total Output current (%)

80%

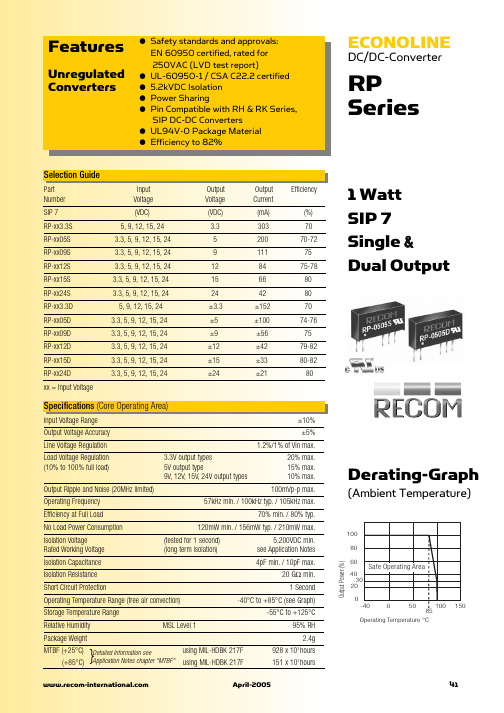

1 Watt SIP 7 Single & Dual Output

Specifications (Core Operating Area)

Input Voltage Range Output Voltage Accuracy Line Voltage Regulation Load Voltage Regulation (10% to 100% full load) Output Ripple and Noise (20MHz limited) Operating Frequency Efficiency at Full Load No Load Power Consumption Isolation Voltage Rated Working Voltage Isolation Capacitance Isolation Resistance Short Circuit Protection Operating Temperature Range (free air convection) Storage Temperature Range Relative Humidity Package Weight MTBF (+25°C) (+85°C) MSL Level 1 using MIL-HDBK 217F using MIL-HDBK 217F April-2005 (tested for 1 second) (long term isolation) 3.3V output types 5V output type 9V, 12V, 15V, 24V output types ±10% ±5% 1.2%/1% of Vin max. 20% max. 15% max. 10% max. 100mVp-p max. 57kHz min. / 100kHz typ. / 105kHz max. 70% min. / 80% typ. 120mW min. / 156mW typ. / 210mW max. 5.200VDC min. see Application Notes

XP固有值一览 Type-III V1.51

http://www.fuji.co.jp/Copyright © 2007 by Fuji Machine Manufacturing Co., Ltd. All Rights Reserved版本升级报告附加资料 No. 07031A发 行 日: 2007 年 8月 2日对 应 机 型: XP-143E/243E (后期机型) (控制软件)新 版 本 号: V1.51(已发行的版本号:V1.50)下页开始为版本升级报告 No.07031 的附加资料“XP 固有值一览 Type-III V1.51”的内容。

Fuji Machine Mfg.XP 固有値一覧 Type-III V1.512007-12-4現在XP固有值一览表Type-III V1.51//_/_/_/_/_/_/_/ Proper data /_未使用●XP启动时检查范围。

请必须设定在范围以内的值。

即使没有输入范围的记述,在整数型时-2147483648~2147483647,小数型时按整数的11位到小数点以下4位为止,字符串型到31个字符为止。

项目XP-143E XP243E输入范围测定值User编辑重新接通电源解说________MACHINE_TYPE_______=__xpMachineTypeA=121~3---否需要机种选择项目 XP14*:1 XP24*:2 XP34*:3__xpMachineTypeB=444---否需要机种选择项目 全机种:4 电路板搬运尺寸__xpMachineTypeC=331~3---否需要机种选择项目 TypeI:1 TypeII:2 TypeIII:3__xpMachineTypeD=11没有范围---否需要一般:1 批量机(1)和试验机(0)的区別,(区别使用的IO)__xpTI1200A=110~1---否1:相机TI-1200A__xpSetCVA1Cam=49610~255---否需要相机的设定(高分辨率相机建立与相机相对应的比特)第1比特:相机1第2比特:相机2第3比特:相机3第4比特:相机4第5比特: 将低分辨率相机作为HR-50处理第6比特: 将高分辨率相机作为G20U20处理第7比特: 将低分辨率相机作为XC-56处理__ServoPulseReduce=000~1---否0 : Pn201 = 16384 1 : Pn201 = 8192__DispMode=000~2---可XP141选择项目 0:影像处理中一切不显示 1:仅仅在覆盖式中显示 2:全部显示__CornerRearSide=220~2---否需要参照内侧的Corner Pattern进行补正处理的标记的指定 0:没有Corner Dog 1:Corner Dog __PanelReverseFlow=000~2---否电路板搬运方向的指定 0:左→右 1:右→左 (与FUJI标准机器同等) 2:右→左__RevolverInterLock=000~2---否需要增加了供料器浮起传感器和变更了吸嘴上升确认传感器 [T1.12e,T1.09h] 变更为0。

RT314024中文资料

018 = 18VDC 048 = 48VDC 024 = 24VDC

4

012

Stock Items

RT114012 RT114024 RT134012

RT134024 RTB14005 RTB14012

RTB14024 RTB34012 RTB34024

RT314012 RT314024 RT334012

90

4.2

66.7

009

202

6.3

44.4

012

360

8.4

33.3

018

810

12.6

22.2

024

1,440

16.8

16.7

048

5,760

33.6

8.3

Applied Coil Voltage (% of rated nom.)

Max. Ambient Temp. vs. Coil Voltage

B300, 360VA @ 240VAC*

TV-3 @120VAC*

Type Resistive/GP

Resistive Resistive/GP

Resistive Motor Motor Motor Motor

Tungsten Pilot Duty

Resistive/GP Resistive/GP

300

260

220

180

0A

8A

140

12A 16A

100 60

0

B

A

20

40

60

80

100

Max. Allowable Ambient Temp. (°C)

A: Coil temperature = Ambient temperature. B: 110% of nominal coil voltage at rated contact load.

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ECONOLINE - DC/DC-Converter

RT Series, 1 Watt, DIP14, Isolated Outputs (Dual Output) Features

● ● ● ● ●

Twin Independent Outputs Output/Output Isolation 1kVDC Power Sharing on Outputs Input/Output Isolation 1kVDC No Heatsink Required

14 PIN DIP Package

3rd angle projection

1

7

Bottom View

14 11 10 9 8

Pin Connections Pin # 1 7 8 Dual –Vin NC –Vout 2 +Vout 2 –Vout 1 +Vout 1 +Vin

19.90

RT-051212 RECOM ****

● ● ● ● ●

Toroidal Magnetics No Extern. Components Required Custom Solutions Available

UL94V-0 Package Material Efficiency to 80%

Selection Guide

Part Number DIP 14 RT-XX1.81.8 RT-XX3.33.3 RT-XX0505 RT-XX0909 RT-XX1212 RT-XX1515 RT-XX0524 Input Voltage (VDC) 1.8, 3.3, 5, 9, 12, 24 1.8, 3.3, 5, 9, 12, 24 1.8, 3.3, 5, 9, 12, 24 1.8, 3.3, 5, 9, 12, 24 1.8, 3.3, 5 9, 12, 24 1.8, 3.3, 5, 9, 12, 24 1.8, 3.3, 5, 9, 12, 24 Output Voltage (V1VDC) 1.8 3.3 5 9 12 15 24 Output Voltage (V2VDC) 1.8 3.3 5 9 12 15 24 Ouput Current (mA) 278/278 132/152 100/100 55/55 42/42 33/33 21/21 Efficiency (%) 70 70 70-78 75-80 78-84 80-84 80-84

August 2002

EC 37

Specifications (Core Operating Area) and Operating Temperature / Derating-Graph

Input Voltage Input Filter Output Voltage Accuracy Line Voltage Regulation Load Voltage Regulation (10% to 100% full load) Ripple and Noise (20MHz limited) Efficiency at Full Load Isolation Voltage Isolation Resistance (Viso = 500VDC) Isolation Capacitance Short Circuit Protection Switching Frequency at Full Load Operating Temperature Storage Temperature Package Weight 1.8V, 3.3V output types 5V output type 9V, 12V, 15V, 24V output types ±10% Capacitor Type ±5% 1,2%/1% V Input 20% max. 15% max. 10% max.

9 10 11 14 NC = No Connection

10.00

7.62

7.10

2.0

15.24

3.05

Recommended Footprint Details

2.54

2.54

1.00 ø+0.15/–0

XX.X ± 0.5 mm XX.XX ± 0.25 mm

Output Power (Watts) 2.0 1.5 1.0 Safe Operating Area 0.5 0 -40 0 50 100 125 150 85 Operating Temperature ˚C

100mVp-p max. 70% min. 1.000VDC min. 10 GΩ min. 20pF min./94pF max. 1 Second 100kHz typ. –40°C to +85°C (see Graph) -55°C to +125°C 2.7g

EC 36

August 2002

元器件交易网

ECONOLINE - DC/DC-Converter

RT Series, 1 Watt, DIP14, Isolated Outputs (Dual Output) Package Style and Pinning (mm)