芯片资料386

Multisim中LM386芯片的构建步骤

Multisim中LM386芯片的构建步骤The LM386 is a low voltage audio power amplifier integrated circuit (IC). To be able to simulate the component in Multisim and use it in Ultiboard PCB designs, it needs to be created using the Component Wizard in Multisim. Files needed: Symbol file (LM386.sym) and SPICE model(LM386.cir).Start Multisim. Under "Tools", choose "Component Wizard".Step 1: Enter component information.Step 2: Enter footprint information.Click on "Select a footprint".There are some 5000 footprints in the Master Database. To find the one that we need more easily, click on "Filter". Click on "Add row" and select "Footprint" from the drop down menu under "Column". Set the "Operator" to "Contains" and enter "DIP8" under "Value" as shown below.Select the "Ultiboard DIP8" footprint.Click on "Select". In the footprint information window set the number of pins to 8.Step 3: Enter symbol information.Click on "Edit" to open the Symbol Editor.Download the file LM386.sym and remember the location where you put it. In the Symbol Editor click on "File" and "Open..." and open theLM386.sym file.Do not change any of the pin information that appears at the bottom of the symbol editor. Click on "Exit" and answer "Yes" to the "Save changes?" question. Now the symbol information window should look like this:Step 4: Set pin parameters. Click on "Next" and change the pinTypes for the different pins (from "BIDIRECTIONAL") to the values shown below.Step 5: Set mapping information between symbol and layout footprint. Click "Next" and fill in the footprint pins in as shown next.Step 6: Select simulation model. Click "Next" to obtain the "Select simulation model" window.Download the file LM386.cir and remember the location where you put it. Then click on "Load from file" and open the LM386.cir file. You should see a window with the LM386 SPICE model filled in as shown below.Step 7: Mapping information between symbol and simulation model. Click "Next" and fill in the Model nodes in the Pin mapping table as follows. (Note: The model nodes are numbered 1,2,3,... from left to right in the .SUBCKT specification, irrespective of the pin numbers in the footprint mapping.)Step 8: Save component to database. Click "Next" and in the next window click on "User Database" and select "Analog".Click on "Add family" and enter "Amplifier" for the family name.Finally, click "Finish" and you are done with LM386 component creation. Check that you can select the component in Multisim.Then place the component on a schematic.。

功率放大器LM386的工作原理

功率放大器LM386的工作原理LM386是一种经典的功率放大器,广泛应用于音频放大和功率放大器电路中。

其工作原理如下:1.内部结构:LM386是一款单声道的音频功率放大器芯片,内部包含多个电路模块,如放大器、调节增益、音量控制等。

其主要特点是使用方便、稳定性好、功耗低等。

2.输入级:LM386的输入级主要是一个可控增益的放大器,用于接收音频信号。

它包括一个开环放大器和一个反馈电阻,通过调节反馈电阻的阻值可以改变放大倍数。

当输入的音频信号经过放大器放大后,将进入下一级电路。

3.中间级:LM386的中间级是一个用于控制增益并产生电流的电路。

它主要由两个电阻和一个电容组成,通过调节这两个电阻的阻值和电容的容值,可以控制功率放大器的增益和频率响应。

4.输出级:LM386的输出级主要是一个功率放大器,用于放大中间级输出信号的电流。

它包含一个输出电感和一个输出电容,通过调节这两个元件的参数可以控制输出信号的频率响应和幅度。

同时,输出级还包括一个管脚用于连接外部负载。

5.反馈回路:LM386的反馈回路主要是通过改变反馈电阻的阻值,将一部分输出信号重新引入到输入级,从而实现对放大倍数的控制。

当反馈电阻的阻值增大时,放大倍数将减小;反之,当阻值减小时,放大倍数将增大。

6.供电电路:LM386的供电电路主要是外部提供的两个直流电源,一个是正电源VCC,一个是负电源VSS。

这两个电源用于给芯片的不同部分提供正负的直流电压,从而使芯片能够正常工作。

在工作时,LM386将外部输入的音频信号经过放大、控制增益、输出等一系列处理后,输出到外接负载上。

通过控制芯片内部的电路结构和元件参数,可以调节放大倍数、频率响应和音量等参数,从而满足不同应用的需求。

总之,LM386功率放大器的工作原理主要是通过控制输入级、中间级和输出级之间的相互作用,将输入信号放大并输出到负载上。

同时,通过反馈回路和供电电路的控制,实现对放大倍数、频率响应和音量等参数的调节。

MS90C386B_datasheet LVDS转TTL芯片

参数 输入高电平 输入低电平 输出高电平 输出低电平 输入电流 输出短路电流

-0.3V - 4.0V -0.3V - (VCC+0.3V) -0.3V - (VCC+0.3V) -0.3V - (VCC+0.3V) +150℃ -65℃ - 150℃ +260℃

1.4W

条件

IOH = -0.4mA IOL = 2mA 0≤VIN≤VCC VOUT = 0V

ICCRP

接收器供电电流 (Power Down)

PDN=0V

10

Max Units mA

mA

uA

开关特性

符号 TRCP TRCH TRCL TRS TRH TTLH TTHL TRCD TRDP5 TRDP6 TRDP0 TRDP1 TRDP2 TRDP3 TRDP4 TTPLLS

参数

输出时钟周期

MS90C386B

——+3.3V 100MHz 的 24bit 平板显示器(FPD)LVDS 信号接收器

功能概述

MS90C386B 芯片能够将 4 通道的低压差分信号(LVDS)转换成 28bit 的 TTL 数据。时钟 通道经过锁相之后与数据通道并行输出。在时钟频率为 85MHz 时,24bit 的 RGB 数据、3bit 的 LCD 时序数据和 1bit 的控制数据以 595Mbps 的速率在每个 LVDS 数据通道中传输。输入时 钟频率为 85MHz 时,数据的传输速率为 297.5Mbytes/sec。此款芯片配合 MS90C385,是解决 高带宽、高速 TTL 信号层面的电磁干扰和电缆长度问题的理想产品。

RX24 HSYNC RX25 VSHNC

RX26 DE

lm386中文资料_数据手册_参数

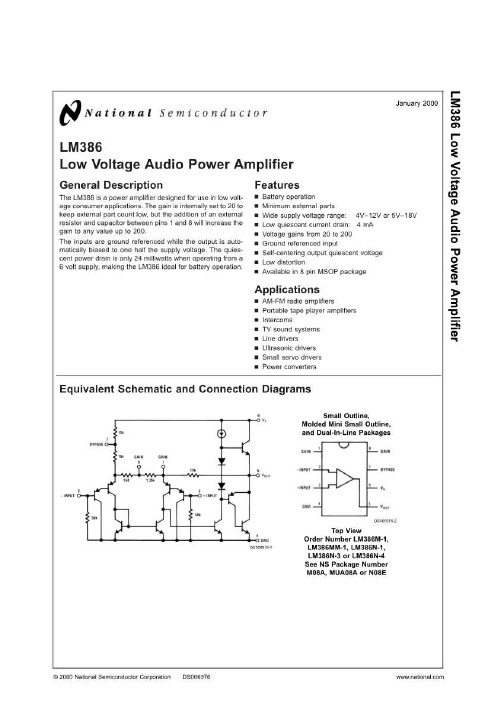

LM386低压音频功率放大器一般描述 LM386是一款功率放大器,设计用于低压,年龄消费者应用.增益内部设置为20至保持外部 零件数量低,但增加了外部引脚1和8之间的电阻和电容会增加获得高达200的任何值.输入以地为参考,输出为自动输入,基本 偏置到电源电压的一半.静止 - 从A.工作时仅消耗24毫瓦的功率 6伏电源,使LM386成为电池操作的理想选择.特征 ?电池操作 ?小 的外部零件 ?宽电源电压范围: 4V-12V或5V-18V ?低静态电流消耗: 4毫安 ?电压从20增加到200 ?接地参考输入 ?自对中输出静态 电压 ?低失真 ?采用8引脚MSOP封装应用 ? AM-FM无线电放大器 ?便携式磁带放大器 ?对讲机 ?电视音响系统 ?线驱动程序 ?超声波 驱动程序 ?小型伺服驱动器 ?电源转换器等效原理图和连接图 DS006976-1小轮廓,被铸造的微型小大纲,和双列直插式封装 DS006976-2顶视图订单号码LM386M-1, LM386MM-1,LM386N-1, LM386N-3或LM386N-4参见NS包装号码 M08A,MUA08A或 N08E 2000年1月 ?2000 NATIONAL SEMICONDUCTOR CORPORATION DS006976 (LM386N-1,-3,LM386M-1) 15V电源电压(LM386N-4) 22V封装耗散(注3) (LM386N) 1.25W (LM386M) 0.73W (LM386MM-1) 0.595W输入电压 ± 0.4V储存温度 -65?C至+150?C工作温度 0?C至+70?C结温 + 150焊接信息双列直插式封装焊接 (10秒) + 260C小外形包装 (SOIC和MSOP)气相(60秒) + 215C红外线(15秒) + 220C参见AN-450“表面安装方法及其作用 关于产品可靠性“的其他焊接方法表面贴装器件.热阻 θ JC (DIP) 37?C/ W θ JA (DIP) 107C / W θ JC (SO包) 35°C / W θ JA (SO包) 172C / W θ JA (MSOP) 210C / W θ JC (MSOP) 56C / W 电气特性 (注1,2) ? A =25?C参数条件敏典型马克 斯单位工作电源电压(V S ) LM386N-1,-3,LM386M-1,LM386MM-1 4 12 V LM386N-4 518 V静态电流(I Q )V S = 6V,V IN = 04 8嘛输出功率(P OUT ) LM386N-1,LM386M-1,LM386MM-1 V S = 6V,R L =8Ω,THD = 10% 250 325毫瓦 LM386N-3 V S = 9V,R L =8Ω,THD = 10% 500 700毫瓦 LM386N-4 V S = 16V,R L =32Ω,THD = 10% 700 1000毫瓦电压增益(A V )V S = 6V,f = 1kHz 26分贝从引脚1到8的10μF 46分贝带宽(BW) V S = 6V,引脚1和8打开 300千赫总谐波失真(THD) V S = 6V,R L =8Ω,P OUT = 125mW 0.2 % f = 1 kHz,引脚1和8打开电源抑制比(PSRR) V S = 6V,f = 1kHz,C BYPASS =10μF 50分贝引脚1 和8打开,参考输出输入电阻 应用提示增益控制为了使LM386成为更通用的放大器,两个引脚(1和8)用于增益控制.引脚1和8打开 1.35 k Ω电阻将增益设置 为20(26 dB).如果是电容从引脚1到8,绕过1.35 k Ω电阻,增益将达到200(46 dB).如果电阻串联放置与电容器,增益可以设 置为从20的任何值增益控制也可以通过电容式cou-将引脚1的电阻(或FET)接地.额外的外部组件可以并行放置通过内部反馈电 阻来调整增益和频率,针对个别应用程序的响应.例如,我们可以通过fre- quency形成反馈路径.这是一系列的 RC从引脚1到5(并 联内部15 k Ω电阻).对于6 dB有效低音提升:R ?15kΩ ,低值为了良好的稳定运行,R = 10k如果管脚8打开,则为Ω.如果针脚 1 和8旁路,然后R低至2 k可以使用Ω.这个限制是因为放大器只能被补偿闭环增益大于9.输入偏移原理图显示了两个输入都被偏置 到地 witha50k Ω电阻.输入变压器的基极电流,电阻约为250 nA,因此输入电压约为12.5 mV当打开时.如果直流源电阻驱动LM386 高于250 k它会贡献很少额外的偏移量(输入端约为2.5 mV,输出端为50 mV).如果直流源电阻小于10k Ω,然后短路未使用的 接地输入将保持偏移量低(约2.5 mV)在输入端,输出端为50 mV).直流源电阻从未使用的输入到地电阻,等于值到直流电源 电阻.当然,如果输入电容耦合,则会消除电源.当使用具有较高增益的LM386(绕过 1.35 k引脚1和8之间的Ω电阻)传递未使用 的输入,防止增益的降低可能的不稳定.这是用0.1μF电容或根据直流源电阻上的接地短路驱动输入

CPU详细资料

1992年,笔记本电脑的处理器以下列为主:25MHz的386SX/386SL、20MHz的386SX/386SL以及25MHz 的486DX组成。

1993年,市场主要以33MHz的486DX处理器为主。

1994年,Intel推出了配备双时钟与数字协处理器的486DX2芯片,在其中运用了V oltageReduction技术,可根据运行环境自动调节电压、降低处理器功耗。

1995年,33MHz的486SL和250MHz的486DX因为性价比高,成为了市场低价机型的首选。

Mobile Pentium 75处理器则成为主流本本的配置。

1996年,市面上的笔记本电脑已大量采用Intel的Pentium处理器,其中以Pentium 100为入门型号,而Pentium133/150则装配了很多中高档笔记本。

该年Intel的处理器新技术以能自动调整处理器主频、控制发热量的ClockGating技术为亮点。

1997年,Intel推出了Mobile Pentium MMX120/133/150/166/200系列处理器。

4M速率的FIR红外开始装备笔记本。

下半年,Intel发布了代号为Tillamook的CPU,它首次采用0.25微米技术工艺制造,内部运行电压为1.8V,外部运行电压为2.5V,大幅度地延长了电池使用时间,并且首次内置了512K L2缓存(只能以内存同速的66MHz访问)。

硬盘方面开始迈进过G级的台槛,高档机型已经装备达3G的硬盘了。

13.3寸的显示屏也正式开始装备笔记本。

1998年,Mobile Pentium MMX 233/266/300推出、166MHz的Pentium MMX已成为入门笔记本电脑的配置。

到年底,随着桌面Pentium II处理器系列的诞生,Intel公司其基础上研发了Mobile Pentium II、Mobile Celeron两款移动处理器。

Mobile Pentium II按主频分为:233/266/300/333/366/400Hz六种,首次采用了0.25微米的制造工艺。

正确识别各种80X86微处理器

初入计算机领域的人,一般都知道386、486之分的不同。

(张强)

80486DX是标准的80486。80486SX与80486DX的主要区别是486SX没有数学协处理器。其性能接近486而价格接近386。486SL是低功耗节能型的486DX芯片,其集成度较486DX更高,适用于便携机。

INTEL对80486芯片采用了提高主频_即倍频技术,以提高CPU的工作效率。倍频是指CPU工作时,内部以系统时钟两倍的速度运行。而外部仍以原来的时钟速度工作。

80386SL芯片主要用于便携机以及节能型台式机。

80386DL是一种标准的32位总线的微处理器,与SL相似也是节能型的CPU。应用场合也与SL相同。

80486CPU内集成了120万个晶体管,其时钟频率主要有33、50、66以及80MHz,现在又有100甚至高达150MHz的486CPU。从结构上说,486=386+387+8KBCache,即把386CPU与数学协处理器387以及8KB的超高速缓冲存储器集成在一个芯片上。80486仍然属于32位微处理器。

具有倍频的CPU分别标有SX2、DX2。而80486DX4的内部时钟频率为外部时钟的3倍,因此称为三倍频。目前该芯片的时钟频率为100MHz,其运行速度比486DX266快40%。

除了INTEL公司外,AMD公司生产的芯片有AM386DXL_40与INTEL的80386DX属于同一档次,但性能优于INTEL的386DX。AM386SXL_40则是节能型芯片,与80386SX属同一档次。AM486DXL2_80也使用了倍频技术,其工作频率比INTEL的80486DX2高得多。

lm386原理

lm386原理LM386是一款具有低电压操作的音频功放芯片,被广泛应用于电子设备中,如小型收音机,CD玩家,电子琴,小型音箱等。

LM386的特点是使用方便、价格便宜、性能稳定,由于体积小巧,而且使用简单,因此被称为最简单的音频功放。

LM386的原理是将声音信号经过放大,达到可以听到的声音水平。

它采用了NPN三极管为主放大器,因此其输出是单极性,即仅有正极性输出。

LM386由电源电压端口、反馈电路、主放大器和输出电路组成。

LM386使用的电源电压是低电压,具有良好的电源电压抑制能力,可以使用电池供电。

一般使用9V电池供电,如果需要更大的输出功率,可以使用两个9V电池并联或使用其他更高电压电源。

在反馈电路中,将放大器的输出信号通过电阻R2反馈到输入端,起到放大倍数的控制作用。

输出电路中,主放大器的输出被连接到电解电容C2,电容的另一端接到喇叭的正极,然后将喇叭的负极接地。

LM386的主放大器采用了直流耦合方式,可以从低频到高频放大声音信号。

输出电容C2起到隔直流的作用,使得输出电路只能通过交流声音信号工作,其容量大小可以根据需要进行选择。

在使用LM386进行音频放大的过程中要注意几个问题:1.输入信号的幅值不要过大,应该控制在0.1到1V之间,太大的输入信号会导致放大器进入饱和状态,降低放大器的工作效率。

2.输出负载要匹配合适,输出负载太小,会加大输出电容的容量,影响低频响应。

输出负载太大,会导致放大器输出功率不足。

3.LM386放大器的输入阻抗较低,应该将输入信号接在电阻分压电路上,以降低输入信号的幅值和防止输入信号干扰放大器的工作。

4.输出电容应该选择低阻抗电解电容,避免电容的内阻对系统电路的影响。

总之,LM386是一款功能强大而且易于使用的音频放大器,可以广泛应用于各种电子设备中,让我们畅听优美的音乐。

LM386资料

⒉语音放大电路语音放大电路如图所示,我们采用小功率音频放大集成电路LM386来实现音频放大。

图3.20这个音频放大电路中,输出信号的放大倍数由LM386的引脚①和⑧的外接情况决定。

一般,这两个引脚通过串联一个电阻R和一个电容C连接起来,这个RC网络正决定了电路的增益。

当①脚和⑧脚开路时,比如我们此次设计的电路(图3.20),电路电压增益为20;如果仅用C=10UF时,增益为200,如图3.21所示;用R=1.2K和C=10UF串接时,增益为50。

图3.21下面我们就介绍一下LM386这块芯片:LM386是目前颇为流行的小功率音频放大集成电路,它广泛运用于各种语音电路中。

它的突出优点是频响宽、功耗低,电源电压适应范围宽,外接元件少。

①LM386集成功率放大器的性能●额定工作电压:4——16V。

●额定电流:当电源电压为6V时,静态工作电流为4mA,适合用电池供电。

●增益:①脚与⑧脚之间不接外部阻容元件时,电压增益为20;接元件时,可提供增益到20——200之间的任何值。

●频响:可达数百kHz。

●最大允许功耗为(25℃)600mA,使用时不用散热片。

负载电阻4Ω时,输出功率(失真为10%)为300mA。

②LM386集成功率放大器的特征LM386有两个信号输入端。

当信号从②脚输入时,构成反相放大器;从③脚输入时,构成正相放大器。

本设计中,信号从③脚输入,为正相放大器。

每个输入端的输入阻抗都为50KΩ,而且输入端对地的直流电位接近为零,即使对地短路,输出直流电平也不会产生大的偏离。

③LM386的内部电路LM386的内部电路如图3.22:图3.22④LM386的引脚图(图3.23)其中:1号脚是放大器1的输出端,2号和3号脚是放大器的输入端;7号脚是放大器2的输出端,5号和6号脚是放大器2的输入端。

图3.23。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Intel® 440BX AGPset Design Guide UpdateMay 1999Notice: The Intel® 440BX AGPset may contain design defects or errors known as erratawhich may cause the product to deviate from published specifications. Currentcharacterized errata are documented in this Specification Update.ROrder Number: 290641-004Intel® 82443BX R Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or oth erwise, to any intellectual property rights is granted by this document. Except as provided in Intel’s Terms and Conditions of Sale for such products, Inte l assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitnessfor a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.Intel may make changes to specifications and product descriptions at any time, without notice.Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.The Intel® 440BX AGPset may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained by calling1-800-548-4725 or by visiting Intel’s website at .*Third-party brands and names are the property of their respective owners.Copyright © Intel Corporation 1998, 19992Design Guide UpdateR Intel® 82443BX ContentsRevision History (4)Preface (5)General Design Considerations (9)Schematic, Layout and Routing Updates (11)Documentation Changes (12)Design Guide Update3Intel® 82443BX R 4Design Guide Update Revision History Rev.Draft/Changes Date 001Initial Release September 1998002Added 440BX General Design Consideration #2. Added 440BX Schematic,Layout, and Routing Updates #3 along with Documentation Change #11.October 1998003Added 440BX General Design Consideration #3 and #4.February 1999004Added 440BX General Design Consideration #5.May 1999R Intel® 82443BX PrefaceThis document is an update to the specifications contained in the Intel® 440BX AGPset Design GuideRev 1.0, April 1998, order number 290634-001.References may also be made to the following documents: the Intel® 440BX AGPset: 82443BX HostBridge Controller data sheet, order number 290633-001, and the 82371AB (PIIX4) data sheet section ofthe Platform Components data book, order number 296467-009.It is intended for hardware system manufacturers and software developers of applications, operatingsystems, or tools. This design guide is primarily targeted at the PC market segment and was firstpublished in 1998. Those using this design guide should check for device availability before designing inany of the components included in this documentNomenclatureGeneral Design Considerations includes system level considerations that the system designershould account for when developing hardware or software products using the Intel® 82440BX AGPset.Schematic, Layout and Routing Updates include suggested changes to the current publishedschematics or layout, including typos, errors, or omissions from the current published documents.Documentation Changes include suggested changes to the current published design guide notincluding the above.Design Guide Update5Intel® 82443BX R Summary Table of ChangesThe following table indicates the Specification Changes, Errata, Specification Clarifications orDocumentation Changes, which apply to the listed Intel® 440BX AGPset stepping. Intel intends to fixsome of the errata in a future stepping of the component and to account for the other outstanding issuesthrough documentation or Specification Changes as noted. This table uses the following notations:Codes Used in Summary TableDoc:Document change or update that will be implemented.Shaded:This item is either new or modified from the previous version of thedocument.NO.Plans GENERAL DESIGN CONSIDERATIONS1Doc Implementing a RESET BUTTON for Desktop Based Systems2Doc PCIRST# Load Sensitivity on PIIX4/PIIX4E3Doc SPD EEPROM Write Protection.4Doc Execute the WBINVD Instruction to Save Cache State to Memory Before Initiating an S2 orS3 Sleep State.5Doc SLP# Connectivity in Multi-processor SystemsNO.Plans SCHEMATIC, LAYOUT AND ROUTING UPDATES1Doc Guidelines to minimize ESD events that may cause loss of CMOS contents is added.2Doc Correct Strapping for SMC FDC37C932FR Ultra IO device VBAT pin.3Doc Removal of DCLKRD Connection to DCLKWRNO.Plans DOCUMENTATION CHANGES1Doc Design Checklist, section 3.12, IDE Interface, bullet 6, concerning the recommendation for10K Ohm pull-down resistors on PDD7 and SDD7 is modified.2Doc Motherboard Layout & Routing Guidelines, section 2.9.2, 3 DIMM Memory Layout & RoutingConsiderations.3Doc Motherboard Layout & Routing Guidelines, section 2.9.3, 4 DIMM Memory Layout & RoutingConsiderations.4Doc Design Checklist, section 3.3.7, Voltage Regulator Module, VRM8.2, bullet 4.5Doc Design Checklist, section 3.7.2, IDE Routing Guidelines6Doc Design Checklist, section 3.11, USB Interface, bullet 1.7Doc Design Checklist, section 3.16, Miscellaneous, bullet 1.6Design Guide UpdateR Intel® 82443BX NO.Plans DOCUMENTATION CHANGES8Doc Design Checklist, section 3.17, 82093AA (IOAPIC), bullet 6 & 10.9Doc Design Checklist, section 3.20, Thermals/Cooling Solutions, bullet 3.10Doc Design Checklist, section 3.16, Pulldown resistor for Ultra IO VBAT pin11Doc Motherboard Layout and Routing Guidelines, section 2.9.7.4, SDRAM Clock Layout,DCLKRDDesign Guide Update7Intel® 82443BX R 8Design Guide UpdateR Intel® 82443BX General Design Considerations1. Implementing a RESUT BUTTON for Desktop Based SystemsThe following should be considered when implementing a RESET BUTTON for desktop based systems:The system reset button has typically been connected indirectly to the PWROK input of thePiiX4/PiiX4E. This technique will not reset the suspend well logic, which includes the SMBus Host andSlave controllers. To reset the hardware in the suspend well, the reset button should be connected to theRSMRST# input of the PiiX4/PiiX4E. Assertion of RSMRST#, via a reset button, will result in acomplete system reset. RSMRST# assertion will cause SUS[A-C]# to assert which results in thedeassertion of PWROK if SUS[A-C]# controls the power supply PS-ON control signal. The deassertionof PWROK will cause the PiiX4/PiiX4E to assert PCIRST#, RSTDRV, and CPURST.For mobile based systems, the Power Button is typically connected to the RSMRST# input of thePiiX4/PiiX4E. Consult the appropriate design related collateral’s regarding this implementation whendesigning mobile based platforms.2. PCIRST# Load Sensitivity on PIIX4/PIIX4EA specific board sensitivity has been identified by PCD that may result in a low going glitch on adeasserted PCIRST# signal when it is lightly loaded. This glitch may occur as a result of VCC droopcaused by simultaneous switching of most/all AD[31:0] signals from 0 to 1. This glitch can in somedesigns be low enough (below 1.7V) to interfere with proper operation of the Host PCI BridgeController component.This sensitivity manifests itself on designs where PCIRST# is lightly loaded with less than approximately50pF, or is not driving the entire PCI bus. Design features that could aggravate the problem are; an in-line active component on the PCIRST# signal, such as an AND gate or, lack of a series terminationresistor on the PCIRST# signal at the PIIX4 or PIIX4E.There are several improvements that can be implemented individually or in any combination. First, aseries termination resistor between 22 and 33 ohms placed close to the PIIX4/PIIX4E will help reducethe glitch. Second, an external capacitor of approximately 47pF will help reduce the glitch. Third, if thedesign currently uses an in-line active gate/buffer on PCIRST# to drive the PCI bus, consider removal ofthis gate/buffer entirely. The PIIX4/PIIX4E is designed to drive the entire PCI bus.Design Guide Update9Intel® 82443BX R3. SPD EEPROM Write ProtectionThe PC SDRAM Unbuffered DIMM Specification, Rev 1.0, dated Feb 1998, shows pin 81 of the DIMMmodule is the WP (write protect) pin for the SPD EEPROM. The block diagrams show there is a 47Kpull-down resistor tied to the WP pin. This allows the DIMM manufacturers to write SPD data to theEEPROM.An OEM may wish to use the SPD EEPROM to write information into the DIMMs at production forsystem level checkout to identify the DIMM installed as being shipped with the system. For this reason,the OEM may wish to include some logic to control the level on pin 81 of the DIMM modules so thatafter the DIMM is tagged, they can be write protected again. If this pin is pulled high on themotherboard, the DIMM SPD EEPROM is write protected.Pin 81 of the DIMM sockets on both the 82440BX dual processor reference schematics and the uni-processor reference schematics currently are shown as “NC”, no connects. If an OEM wishes to writeprotect the SDRAM SPD EEPROMS, then these pins should be pulled high.4. Execute the WBINVD Instruction to Save Cache State to Memory BeforeInitiating an S2 or S3 Sleep StateIf a system design requires that the hardware platform be capable of flushing the processor caches, thenFLUSH# must be asserted a minimum of one BSCLCK before STPCLK#. Power management softwareshould perform a WBINVD on each processor for the S2 and S3 sleep states. Flushing the cache on eachprocessor is not necessary for the S1 sleep state.5. SLP# Connectivity in Multi-processor SystemsFor multi-processor systems using the PIIX4/PIIX4E, the SLP# signal may be asserted to one of theprocessors before it is in a processor sleep state 3, and therefore not yet acknowledged. This could resultin a wakeup problem.Specifically, For PIIX4/PIIX4E based platforms, STPCLK# from the PIIX4E is connected to allprocessors, and SLP# from the PIIX4E is connected to all processors. The following sequence occurs:1.OS writes to PMCNTRL register2.PIIX4E asserts STPCLK#, then waits for Stop Grant3.The processor acknowledges with a Stop Grant Acknowledge4.PIIX4E asserts SLP# after receiving Stop Grant AcknowledgeWhile this sequence works for uni-processor systems, processors are put into Processor Sleep State 3,not State 5, during ACPI S1 state. This means that the SLP# signal must not be connected to anyprocessor in multi-processor systems.Note that disabling the SLEEP_EN bit in the PIIX4E Processor Control register is not an acceptableworkaround for this issue since this bit only controls SLP# assertion in C3 state, not in S1 state.10Design Guide UpdateR Intel® 82443BX Schematic, Layout and Routing Updates1. Guidelines to Minimize ESD Events That May Cause Loss of CMOS ContentsRecommendations for New Board Designs:1) Provide a 1uF X5R dielectric, monolithic, ceramic capacitor between the VCCRTC pin of thePiiX4/PiiX4E and the ground plane. This capacitor’s positive connection should not be stubbed off thetrace run and must be as close as possible to the PiiX4/PiiX4E. The capacitor must be no further than 0.5inch from the PiiX4/PiiX4E. If a stub is required, it should be kept to a few mm maximum length. Theground connection should be made through a via to the ground plane, with no or minimal trace betweenthe capacitor pad and the via.2) Place the battery, 1K Ohm series current limit resistor, and the common-cathode isolation diode veryclose to the PiiX4/PiiX4E. If this is not possible, place the common-cathode diode and the 1K Ohmresistor as close to the 1uF capacitor as possible. Do not place these components between the capacitorand the PiiX4. The battery can be placed remotely from the PiiX4/PiiX4E.3) On boards that have chassis-intrusion utilizing external logic powered by the VCCRTC pin, place theinverters as close to the common-cathode diode as possible. If this is not possible, keep the trace run nearthe center of the board.4) Keep the PiiX4/PiiX4E VCCRTC trace away from the board edge. If this trace must run fromopposite ends of the board, keep the trace run towards the board center, away from the board edge wherepeople and equipment that handle the board could make contact.Recommendations for Existing Board Designs:1) The effectiveness of adding a 1uF capacitor, as identified above, needs to be determined by examiningthe routing and placement. For example, placing the capacitor far from the PiiX4 reduces itseffectiveness.2. Correct Strapping for SMC FDC37C932FR Ultra IO Device VBAT PinWhen the PIIX4/PIIX4E internal RTC is used, the SMC Ultra IO device, FDC37C932FR, VBAT pinmust be connected to ground through between a 1K and 0 ohm pull-down resistor.3. Removal of DCLKRD Connection to DCLKWRReference the Intel® 440BX AGPset Design Guide, dated April 1998, order number 290634-001,section 6, Reference Design Schematics. Sheet 8 of 40 in the dual processor schematics and sheet 6 of34 in the uni-processor schematics show DCLKRD (pin AB22) connected to DCLKWR (AD25).Effective with the 82443BX C-1 stepping of the device, DCLKRD is no longer internally connected toDCLKWR. See item #11 in the 440BX Documentation Section of this Design Guide Update document. Design Guide Update11Intel® 82443BX R Documentation Changes1. Design Checklist, section 3.12, IDE Interface, bullet 6, concerning therecommendation for 10K Ohm pull-down resistors on PDD7 and SDD7 ismodified.This bullet indicated above is changed to read:“There is no internal pull-up or down on PDD7 or SDD7 of the PIIX4/PIIX4E. The ATA3 specificationrecommends a 10K Ohm pull-down on DD7 in section 4.3.1. Devices shall not have a pull-up resistor onDD7. It is recommended that a host have a 10K Ohm pull-down resistor on PDD7 and SDD7 to allowthe host to recognize the absence of a device at power-up. This pull-down resistor allows the BIOS torecognize the absence of an IDE slave device. Without this pull-down, some BIOSes may take up to 30seconds to recognize that there is no slave device, or some BIOSes may hang the system.”2. Motherboard Layout & Routing Guidelines, section 2.9.2, 3 DIMM MemoryLayout & Routing ConsiderationsFigure 2-19This figure should show the polarity of the B-copy of memory address bit 13 as MAB13.Table 2-33This table should show the polarity of the B-copy of memory address bit 13 as MAB13.3. Motherboard Layout & Routing Guidelines, section 2.9.3, 4 DIMM MemoryLayout & Routing ConsiderationsFigure 2-21This figure should show the polarity of the B-copy of memory address bit 13 as MAB13.Figure 2-22The recommended trace length from the FET Switch to the third DIMM socket should be 1.1” -2.0”.Table 2-48This table should show the polarity of the B-copy of memory address bit 13 as MAB13.4. Design Checklist, section 3.3.7, Voltage Regulator Module, VRM8.2, bullet 4.This bullet indicated above is changed to read:“VRM8.2 is modified from VRM8.1 to provide up to 18A of ICCcore for processors beyond the PentiumII processor.”5. Design Checklist, section 3.7.2, IDE Routing Guidelines.Figure 3-5The figure should show a 10k-ohm pulldown on PDD7 as described in Documentation Change #1.12Design Guide UpdateR Intel® 82443BX6. Design Checklist, section 3.11, USB Interface, bullet 1.This bullet indicated above is changed to read:“Please contact your local INTEL Field Sales representative for the following Application Note:82371AB PIIX4 Application Note #1: USB Design Guide And Checklist Rev 1.1. This documentdiscusses details of the PIIX4/PIIX4E implementation of the Universal Serial Bus. Included in thediscussion are motherboard layout guidelines, options for USB connector implementation, USB clockingguidelines and a design checklist.”7. Design Checklist, section 3.16, Miscellaneous, bullet 1.This bullet indicated above is changed to read:“The 32 kHz oscillator is always required by the PIIX4/PIIX4E, even if the internal RTC is not used.Also, if the internal RTC in the PIIX4/PIIX4E is not used, an on board battery is not required at thePIIX4/PIIX4E, but is required for an external implementation of the RTC[e.g. RTC in the Super I/O]. Inthis case, connect VCC(RTC) pin of the PIIX4/PIIX4E directly to 3VSB voltage.”8. Design Checklist, section 3.17, 82093AA (IOAPIC), bullet 6&10.This bullets indicated above are changed to read:Bullet 6“SMI support - The option to route SMI through the IOAPIC in a Dual-Processor system isnot recommended due to timing constraints between the PIIX4/PIIX4E and the Slot1 processors”Bullet 10“The SMI# signal from the PIIX4/PIIX4E should be connected directly to both processors in a DPsystem. The option to generate an SMI using the SMIOUT# signal from the IOAPIC is not recommendedbecause of timing delays through the IOAPIC.”9. Design Checklist, section 3.20, Thermals/Cooling Solutions, bullet 3.This bullet indicated above is changed to read:“Verify that all major components, including the 82443BX can be cooled the way they are placed. Pleasecontact your local INTEL Field Sales representative for the following Application Note:FW82443BX/FW82443GX PCI/AGP Controller Application Note #2: Thermal Design ConsiderationsRev2.0. This thermal application note contains thermal specifications, thermal solutions and the thermaltest methodology for the 82443BX component.”10. Design Chcklist, section 3.16, Pulldown Resistor for Ultra IO VBAT Pin.A new bullet will be added to section 3.16 as described below.“When the PIIX4/PIIX4E internal RTC is used, ensure that the VBAT pin of the SMC Ultra IO device,FDC37932FR, is connected to ground through a pull-down resistor between 1K and 0 ohms. Consultyour IO device vendor for implementation guidelines for this or other IO devices.”Design Guide Update13Intel® 82443BX R 11. Motherboard Layout and Routing Guidelines, section 2.9.7.4, SDRAM ClockLayout, DCLKRD.The 82443BX C1 stepping component does not have an internal connection for pin AB22 (oldDCLKRD). Existing 82443BX B1 stepping designs connected DCLKRD and DCLKWR nets on themotherboard. Removal of the DCLKRD connection on 82443BX C1 will cause a slightly reduced loadcapacitance on this net.In order to avoid additional clock skew on existing Intel® 82440BX AGPset designs that will use the82443BX C1 stepping, a discrete capacitor larger than the 20pF capacitor recommended in Note 1 maybe required.14Design Guide UpdateIntel around the worldUnited States and CanadaIntel CorporationRobert Noyce Building2200 Mission College BoulevardP.O. Box 58119Santa Clara, CA 95052-8119USAPhone: (800) 628-8686EuropeIntel Corporation (U.K.) Ltd.Pipers WaySwindonWiltshire SN3 1RJUKPhone:England(44) 1793 403 000Germany(49) 89 99143 0France(33) 1 4571 7171Italy(39) 2 575 441Israel(972) 2 589 7111Netherlands(31) 10 286 6111Sweden(46) 8 705 5600Asia PacificIntel Semiconductor Ltd.32/F Two Pacific Place88 Queensway, CentralHong Kong, SARPhone: (852) 2844 4555JapanIntel Kabushiki KaishaP.O. Box 115 Tsukuba-gakuen5-6 Tokodai, Tsukuba-shiIbaraki-ken 305JapanPhone: (81) 298 47 8522South AmericaIntel Semicondutores do BrazilRua Florida 1703-2 and CJ22CEP 04565-001 Sao Paulo-SPBrazilPhone: (55) 11 5505 2296For More InformationTo learn more about Intel Corporation, visit our site on the World Wide Web at R。