Quartus II LPM使用指南(FIFO篇)

quartus 异步fifo用法

quartus 异步fifo用法在Quartus中使用异步FIFO,可以通过IP Core Catalog中的"ALTAsyncFIFO"来实现。

以下是使用异步FIFO的步骤:1. 打开Quartus Prime软件。

点击"File"菜单,选择"New Project"来创建一个新的项目。

2. 在"New Project Wizard"中,选择项目的名称、储存位置和顶层实体的文件。

点击"Next"继续。

3. 在"Add Files"步骤中,添加设计文件,包括顶层实体和其他组件文件。

点击"Next"继续。

4. 在"Family and Device Settings"步骤中,选择您的目标FPGA 器件。

点击"Next"继续。

5. 在"EDA Tool Settings"步骤中,选择Quartus使用的EDA工具。

点击"Next"继续。

6. 在"Summary"步骤中,查看项目设置的摘要。

点击"Finish"完成项目创建。

7. 在Quartus主界面的左侧面板中,点击"IP"选项卡,然后选择"Library"。

在IP Core Library窗口中,搜索"ALTAsyncFIFO"。

8. 在搜索结果中,选择"ALTAsyncFIFO"并点击"OK"来添加该IP到项目中。

9. 在设计文件中实例化ALTAsyncFIFO组件。

可以使用Quartus的"IP Catalog"来生成实例化代码。

10. 配置ALTAsyncFIFO的参数,包括FIFO大小、输出宽度、寄存器位宽等。

quartus 异步fifo用法 -回复

quartus 异步fifo用法-回复quartus异步FIFO用法引言:在数字电路设计中,FIFO(First In First Out)是一种常见的数据存储器,它允许数据以先进先出的顺序进出。

在使用Quartus进行FPGA设计时,异步FIFO是一种非常有用的工具,它可以帮助我们处理不同速度的数据流,并实现数据的缓冲和流量控制。

本文将介绍Quartus异步FIFO的基本概念和使用方法,并给出一些实例。

第一部分:Quartus异步FIFO概述1.1 什么是异步FIFO?异步FIFO是一种数据存储器,在其中数据可以以不同速度进入和退出。

与同步FIFO不同,异步FIFO的读写时钟可以是不同的,这使得它可以处理速度不匹配的数据流。

Quartus提供了异步FIFO的库函数和IP核,使得它可以在FPGA设计中方便地使用。

1.2 Quartus异步FIFO的特点Quartus异步FIFO具有以下特点:- 可以使用不同的时钟频率进行读写操作。

- 可以配置不同的缓冲深度来满足特定的设计需求。

- 可以实现流量控制和数据的重排序。

- 可以支持并行读写和读写使能信号。

- 可以适应不同的数据宽度和时钟域要求。

第二部分:Quartus异步FIFO的使用方法2.1 创建异步FIFO在Quartus中创建异步FIFO的方式有两种:使用库函数和使用IP核。

使用库函数创建异步FIFO的步骤如下:- 首先,在Quartus中打开设计工程,并创建一个新的源文件。

- 然后,将异步FIFO的库函数导入到源文件中,以便在设计中调用它。

- 接着,实例化异步FIFO,并通过参数配置其属性,例如宽度,深度,时钟域等。

- 最后,将异步FIFO连接到其他逻辑模块,完成设计。

使用IP核创建异步FIFO的步骤如下:- 首先,在Quartus中打开设计工程,并创建一个新的IP核。

- 然后,在IP核的界面中选择合适的FIFO类型和配置参数。

- 接着,将异步FIFO实例化到设计中,将其连接到其他逻辑模块。

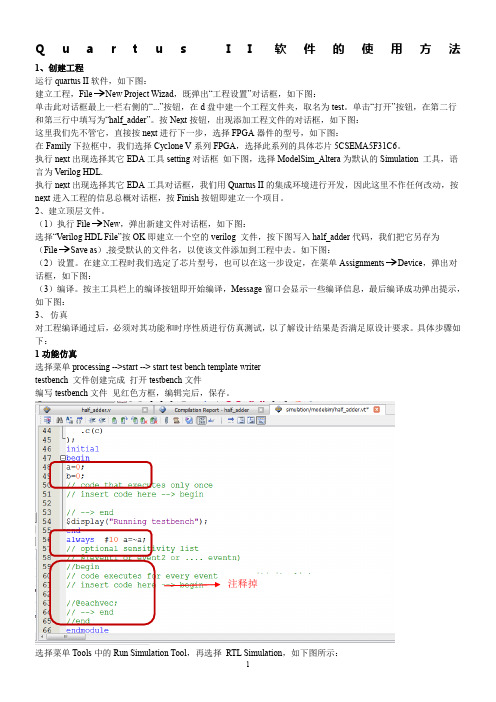

Quartus-II软件的使用方法

Q u a r t u s I I软件的使用方法1、创建工程运行quartus II软件,如下图:建立工程,File New Project Wizad,既弹出“工程设置”对话框,如下图:单击此对话框最上一栏右侧的“...”按钮,在d盘中建一个工程文件夹,取名为test。

单击“打开”按钮,在第二行和第三行中填写为“half_adder”。

按Next按钮,出现添加工程文件的对话框,如下图:这里我们先不管它,直接按next进行下一步,选择FPGA器件的型号,如下图:在Family下拉框中,我们选择Cyclone V系列FPGA,选择此系列的具体芯片5CSEMA5F31C6。

执行next出现选择其它EDA工具setting对话框如下图,选择ModelSim_Altera为默认的Simulation 工具,语言为Verilog HDL.执行next出现选择其它EDA工具对话框,我们用Quartus II的集成环境进行开发,因此这里不作任何改动,按next进入工程的信息总概对话框,按Finish按钮即建立一个项目。

2、建立顶层文件。

(1)执行File New,弹出新建文件对话框,如下图:选择“Verilog HDL File”按OK即建立一个空的verilog 文件,按下图写入half_adder代码,我们把它另存为(File Save as),接受默认的文件名,以使该文件添加到工程中去。

如下图:(2)设置。

在建立工程时我们选定了芯片型号,也可以在这一步设定,在菜单Assignments Device,弹出对话框,如下图:(3)编译。

按主工具栏上的编译按钮即开始编译,Message窗口会显示一些编译信息,最后编译成功弹出提示,如下图:3、仿真对工程编译通过后,必须对其功能和时序性质进行仿真测试,以了解设计结果是否满足原设计要求。

具体步骤如下:1功能仿真选择菜单processing -->start --> start test bench template writertestbench 文件创建完成打开testbench文件编写testbench文件见红色方框,编辑完后,保存。

Quartus II 使用方法(2)

本课内容

QII使用方法 使用方法

QII设计流程详解 设计流程详解 SignalTap II应用介绍 应用介绍 LPM_ROM模块应用 模块应用 原理图设计方法

3

LPM_ROM宏模块应用 4.4 LPM_ROM宏模块应用

LPM: LPM: Library of Parameterized Modules

9

LPM_ROM宏模块应用 4.4 LPM_ROM宏模块应用

4.4.2 定制初始化数据文件

2.建立.hex格式文件 .建立 格式文件

方法一:

将波形数据填入.hex文件表中 图4-40 将波形数据填入 文件表中

10

LPM_ROM宏模块应用 4.4 LPM_ROM宏模块应用

4.4.2 定制初始化数据文件

LPM_ROM宏模块应用 4.4 LPM_ROM宏模块应用

BEGIN

LPM_ROM宏模块应用 4.4 q LPM_ROM0); <= sub_wire0(7 DOWNTO 宏模块应用

altsyncram_component : altsyncram GENERIC MAP ( intended_device_family => "Cyclone", --参数传递映射 width_a => 8, --数据线宽度 数据线宽度8 数据线宽度 widthad_a => 6, --地址线宽度 地址线宽度6 地址线宽度 numwords_a => 64, --数据数量 数据数量64 数据数量 operation_mode => "ROM", --LPM模式 模式ROM 模式 参数的设置 outdata_reg_a => "UNREGISTERED", --输出无锁存 address_aclr_a => "NONE", --无异步地址清0 outdata_aclr_a => "NONE", --无输出锁存异步清0 width_byteena_a => 1, -- byteena_a输入口宽度1 init_file => "./dataHEX/SDATA.hex", --ROM初始化数据文件 初始化数据文件 lpm_hint => "ENABLE_RUNTIME_MOD=YES, INSTANCE_NAME=NONE", lpm_type => "altsyncram" ) --LPM类型 PORT MAP ( clock0 => inclock, address_a => address,q_a => sub_wire0 ); END SYN;

QUARTUSII操作

:为选定的信号赋予高电平;

:为选定的信号不进行赋值;

:为选定的信号赋原值的相反值;

:专门设置时钟信号;

:把选定的信号用一个时钟信号或是周期性信号来 代替; :为总线信号赋值; :为选定的信号随机赋值;

保存好文件, 默认文件名

单击“assignments”菜单下的“settings”令,在弹 出的“settings”对话框中进行设置。如上图,单击左侧 标题栏中的“simulator settings”选项后,在右侧的 “simulator mode”下拉菜单中 选择“functional”选 项即可,单击“ok” 按钮后完成设置。

在上页的界面中,你可以添加已经写好的程 序模块,实现模块共享,如果需要添加直接点 击“Add”按 选择 芯片 钮就可以 了,如果不 需要直接点 击 “next”, 出现这个 界面:

点击进入下 一界面

点击完成

选择VHDL FILE

点击进 入编辑 界面

输入文 本文件

保存文件,注意保存 的文件名要和文本 的实体名一致

启动编译

编译成功

建立仿真文件

设置仿真时间区域,并进行波 形文件存盘(选择File中的Save as)

设置仿真结束时间为100US

设置仿真 结束时间

在空白处双击 鼠标左键

选 择”NODE FINDER”

点击”LIST”

选择需要 的信号

接下来分别对各输入端口进行设置,完成之 后,单击保存文件按钮进行保存。

:在波形文件中添加注释; :修改信号的波形值,设定选定区域的波形; :放大,缩小波形; :全屏显示波形文件;

:在波形文件信号栏中查找信号名,可以快 捷地找到待观察信号; :将信号栏中的名称用另一个名称代替; :为选定的信号赋予未初始化状态; :为选定的信号赋予不定状态;

Quartus II使用指南(非常详细)

图 22

Quartus II 的 FPGA 设计手册--------王兴权(030320122)2007 年 4 月 桂林电子科技大学计算机与控制学院(自动化专业)-------- 用喜悦振奋精神,用成绩增添信心!

第7页

安装向导。在 Choose Destination Location 对话框上,点击 Next 按钮,安装到 默认路径;

第5页

图 17 14、在 Custom Iformation 对话框上输入客户信息,User Name:欣欣工作室, Company Name:/,点击 Next 按钮,进入下一步;

图 18 15、在 Choose Destination Location 对话框上,输入安装路径,也可以使用默认 路径,点击直 Next 按钮,进入下一步;

页 第12 12页

图 48:Edit 菜单

图 29

图 32

Quartus II 的 FPGA 设计手册王兴权(030320122)2007 年 4 月 桂林电子科技大学计算机与控制学院(自动化专业)-------- 用喜悦振奋精神,用成绩增添信心!

第9页

图 33 图 35:将你改好的 Licenst.dat 文 件 导入 进 来 哦 ! ! !

图 30

图 27 2、把 sys_cpt.dll 复制到你所安装的目录中,我的目录是 D:\QuartusII 5_0\bin\ 下覆盖同名文件;

图 31 4. 启动 QuartusII 6.0,遇到如下对话框时选择 Specify valid license file 选 项,点击 OK 按钮;

图 28

图8 8、在 Setup Type 对话框上选中 Complete 选项(表示完全安装) ,点击 Next 按 钮,进入下一步;

quartus II使用手册

( 2)点击 OK

37

进入编译器

选择命令Processing︱Compiler Tool ,打开编译器窗口:

编译器包含5个主模块,可以连续运行5个模块,也可以单 独运行某模块。

38

编译器的 5 个主模块

分析和综合(Analysis & Synthesis)模块:把原始描述转 化为逻辑电路,映射到所选定的可编程器件。 装配(Fitter)模块:将前一步确定的逻辑元件在目标芯 片上布局、布线; 组装(Assembler)模块:形成编程文件; 时序分析(Timing Analyzer)模块; 产生EDA工具网表(EDA Netlist Writer)模块:目的是 与其他EDA工具相衔接。

23

从库中调入元件及引脚符号(续)

选择引脚符号名

调入该引脚符号

24

绘制原理图(本例为半加器)

连线; 给引脚命名 ;

25

绘制原理图中的其他操作

删除符号或连线; 复制元件符号 ; 橡皮筋功能:打开橡皮筋功能时,拖动元件符号或连线时, 原理图拓扑关系保持不变。

26

设计的VHDL描述

27

16

和项目版本管理有关的文件

文件类型

Quartus II 项目文件 (.qpf) (Quartus II Project File) Quartus II 项目设置文件(.qsf) (Quartus II Setting File) Quartus II 项目默认设置文件(.qdf) (Quartus II Default Settings File)

LIBRARY ieee; USE ieee.std_logic_1164.ALL; USE ieee.std_logic_unsigned.ALL; ENTITY Adder4 IS GENERIC cin: ( width : integer := 4 ); IN std_logic; 0) -- 定义一个类属参数 width,其默认值为 4 0 ); PORT ( a, b: IN std_logic_vector ( width - 1 DOWNTO cout: OUT std_logic; Sum: OUT std_logic_vector ( width - 1 DOWNTO ); END Adder4; -- operator '+' is overwrited in the package -- 第 1 行 -- 第 2 行

实验一_QuartusII的使用

实验一_QuartusII的使用引言:Quartus II是一款由美国Intel公司开发的FPGA设计软件,广泛应用于数字集成电路设计和原型验证。

本实验将介绍Quartus II的基本使用方法,包括项目创建、设计输入、约束设置、编译与仿真等。

一、环境准备二、项目创建1.启动Quartus II软件,选择"File" -> "New Project Wizard"创建新项目。

在弹出的对话框中,选择项目的存储位置和名称,并选择合适的目标设备和设计流程。

点击"Next"进入下一步。

2.在第二步中,选择项目的项目类型和是否要添加预定义的IP (Intellectual Property)核。

IP核是现成的、可重用的模块,可以简化设计。

根据自己的需求进行选择,点击"Next"。

3.在第三步中,选择顶层设计文件的命名,并点击"Next"。

5.在第五步中,对项目的设置进行回顾,并点击"Finish"完成项目创建。

三、设计输入1.双击项目中的顶层设计文件,打开Design Entry工具。

在Design Entry工具中,可以通过图形界面或者Verilog/VHDL语言进行设计输入。

a.如果选择使用图形界面,可以在左侧工具栏中选择需要的元件,然后在设计区域中拖拽放置,最终形成需要的电路结构。

b.如果选择使用Verilog/VHDL语言,可以在设计区域中输入相应的代码,然后进行语法检查。

2.在设计完成后,可以使用编译按钮对设计进行编译。

编译过程中,Quartus II会对设计进行分析、优化和进行布线等操作,生成逻辑网表。

四、约束设置1.双击项目中的顶层设计文件,打开Design Constraints工具。

在Design Constraints工具中,可以设置时钟频率、信号约束、引脚约束等。

QuartusII使用指南

1.建立原理图文件

编辑设计文件

图8 执行File-New…命令

§2

1.建立原理图文件

弹出新建文件对话框如图2.9

编辑设计文件

AHDL文本文件 流程图和原理图文件 网表文件 在线系统文件 Verilog HDL文本文件 VHDL文本文件

图9 新建文件对话框

重复-插入模式选否 作为流程图模块插入符号选否 图13 Symbol对话框

§2

2.编辑输入原理图文件

1)元件的选择与放置

编辑设计文件

其它元件可以通过复制和 选择重新插入新元件得到

图14 放置元件后的界面图

§2

2.编辑输入原理图文件

1)元件的选择与放置

编辑设计文件

打开pin引脚子库,选择input管脚和插入逻辑 元件一样插入原理图中

可以在File空白处选择添入已存

在的设计文件加入到这个工程

中,也可以使用User Library Pathnames按钮把用户自定义 的库函数加入到工程中使用, 完成后按Next按钮进入下一步。

图4 加入文件对话框

§ 1 建立工程项目

一、Quartus II设计流程介绍

4)如图2.5所示是选择可编程逻辑器件对话框,选Yes为手动选择 需要的器件,选No则由编译器自动选择。

§ 1 建立工程项目

一、 Quartus

II设计流程介绍

2)选择项目存放目录、填写项目名称,注意项目顶层设计实

体名称必须和项目名称保持一致。

工程项目目录 项目名称 项目顶层设计实体名称

图3

工程项目基本设置

§ 1 建立工程项目

一、Quartus II设计流程介绍

3)完成上述操作后,按Next按钮将会弹出加入文件对话框,如图 2.4所示。

QUARTUSII使用说明

逻辑设计的输入方法

QuartusⅡ所能接受的输入方式有:原理图(*.bdf 文 件 ) 、 波 形 图 (*.vwf 文 件 ) 、 VHDL(*.vhd 文 件 ) 、 Verilog HDL(*.v文件)、Altera HDL(*.tdf文件)、符号图 (*.sym文件)、EDIF网表(*.edf文件)、Verilog Quartus 映 射文件(*.vqf)等。 EDIF是一种标准的网表格式文件, 因此EDIF网表输入方式可以接受来自许多第三方EDA 软件(Synopsys、Viewlogic、Mentor Graphics等)所生成 的设计输入。在上述众多的输入方式中,最常用的是原 理图、HDL文本和层次化设计时要用的符号图。

编译

QuartusⅡ编译器主要完成设计工程的检查和逻辑综合,将工 程最终设计结果生成器件的下载文件,并为仿真和编程产生输出文 件。 第一步 打开编译器窗口 在管理器窗口中选择菜单“Processing”→“Compiler Tool”,则 出现编译器窗口,如下图。从图中可以看出,编译包括分析与综合 (Analysis & Synthesis)、适配器(Fitter)、汇编器(Assembler) 和时序分析器(Timing Analyzer)等。

第二步 输入元件和模块

1)在图形编辑窗口空白处双击鼠标左键或选择菜单 “Edit”→“Insert Symbol…”,也可直接在工具栏上点击按 钮,便打开了“Symbol”对话框,如图所示。

2)选择适当的库及所需的元件(模块)。

3)点击“OK”。

这样所选元件(模块)就会出现在编辑窗口中。重 复这一步,选择需要的所有模块。相同的模块可以采用 复制的方法产生。用鼠标左键选中器件并按住左键拖动, 可以将模块放到适当的位置。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

下图中是 SCFIFO 和 DCFIFO 的框图,其中,SCFIFO 中读写双方信号与时钟 clock 同步,DCFIFO 读写双方信号分别与读写时钟同步。

表一中列出 FIFO 中各个 IO 的详细描述: 表一 端口描述

端口

类型 是否必选

描述

Clock

输入

是

上升沿触发时钟

Wrclk

当该信号有效时,FIFO 会被认为已经读空,此时不能 再进行读操作;

准装满信号,当 usedw 大于参数 almost_full_value 或 相同时,该信号被激活,即是 full 信号被激活的预示; 准读空信号,当 usedw 小于参数 almost_empty_value 或相同时,该信号被激活,即是 empty 信号被激活的 预示; 显示当前 FIFO 中数据存量。

Rdreq

输入

是

Sclr

输入

非

Aclr

Q

输出

是

Full Wrfull Rdfull Empty Wrempty Rdempty Almost_full

输出

非

输出

非

输出

非

Almost_empty

输出

否

Usedw Wrusedw Rdusedw

输出

否

FIFO 篇

第 -5- 页

Rdreq Rdfull Rdempty Rdusedw 当 wrreq 有效时数据线上的数据通过 DATA 端口被写 入 FIFO 中 写请求信号,激发写入操作。 1.当 full(对于 SCFIFO)或 wrfull(对于 DCFIFO)有 效时,不能激活 wrreq 信号,参数 overflow_checking 设置为 ON,即在 full 状态下 FIFO 会自动无视写请求; 2.不能再 aclr 有效期间激活 wrreq 信号; 3. 使 用 Stratix 和 Cyclone 系 列 器 件 ( 除 了 Stratix, Stratix GX, 和 Cyclone 系 列 以 外 ) 需 要 将 write_aclr_synch 参数选择位 ON,确保符合限制条件。 读请求信号,激发读出操作。 1. 该信号 的作用在正 常模式下和 在预读模式 下的作用 有很多不同(详情见后文); 2.当 empty(对于 SCFIFO)或 rdempty(对于 DCFIFO) 有效时,不能激活 rdreq 信号,参数 underflow_checking 设置为 ON,即在 full 状态下 FIFO 会自动无视读请求; 清零端口,详情见后文

1.SCFIFO:单时钟 FIFO; 2.DCFIFO:双时钟 FIFO,数据输入和输出的宽度相同; 3.DCFIFO_MIXED_WIDTHS:双时钟 FIFO,输入输出数据位宽可以不同。 在本文中,如无特殊说明,DCFIFO 通指上述两种双时钟 FIFO。

笔者博客 /wg2011/

1.3 时序要求

1.如果设置了溢出保护电路或设置 overflow_checking 参数为 ON,则在 FIFO 满时会自动无视 wrreq 信号,FIFO 空时同理; 2.如果没有做上述两种措施中的任意一种,则当 FIFO 在装满时的同一时钟周期内不能对 wrreq 信号 做出相应,即在此期间不能拉高 wrreq,FIFO 空时同理。 3.下面通过两幅时序图来具体说明:

输入

是

上升沿触发时钟,下列信号与之同步:

data wrreq

Wrfull

Wrempty

wrusedw

Rdclk

输入

是

上升沿触发时钟,下列信号与之同步:

Q

笔者博客 /wg2011/

Quartus II LPM 使 用 指 南

Data Wrreq

输入

是

输入

是

Quartus II LPM 使 用 指 南

FIFO 篇

第 -4- 页

第一章 FIFO 配置全攻略

1.1 如何配置自己需要的 FIFO

配置 FIFO 的方法有两种,一种是通过 QUARTUS II 中 TOOLS 下的 MegaWizard Plug-In Manager 中选择 FIFO 参数编辑器来搭建自己需要的 FIFO,这是自动生成 FIFO 的方法,另外如果你是大师 级选手(对 LPM-FIFO 参数十分熟悉)还可以通过手动编写 HDL 来实现需要的 FIFO。在此笔者建 议大家,尤其是初学者使用自动方式来配置需要的 FIFO,配置界面简洁明了十分容易上手。

参考文献

第 -1- 页

-2-3-4-4-5-8-8-9-9- 10 - 10 - 11 - 11 - 11 - 11 - 12 - 13 - 13 - 14 - 15 - 15 - 16 - 17 - 18 - 19 - 19 - 21 -

笔者博客 /wg2011/

表二中列出配置 FIFO 的各个参数详细说明:

笔者博客 /wg2011/

Quartus II LPM 使 用 指 南

FIFO 篇

第 -6- 页

参数 Lpm_width

Lpm_width_r Lpm_widthu

类型 整数

整数 整数

Lpm_widthu_r Lpm_numwords

笔者博客 /wg2011/

Quartus II LPM 使 用 指 南

1.4 输出状态标记和潜伏期

对于 DCFIFO,输出潜伏期如下图所示:

FIFO 篇

第 -8- 页

1.5 避免亚稳态

1.6 同步复位及异步复位的影响

在不同模式下,同步、异步复位的影响不同,SCFIFO 支持同步或异步复位,DCFIFO 支持异步复位, 且该复位信号与写时钟同步。具体不同影响见表三(SCFIFO),表四(DCFIFO):

度;

是

对于 SCFIFO,该参数定义了 usedw 端口的位宽,对

于 DCFIFO,定义了 rdusedw 和 wrusedw 的位宽,对

于 DCFIFO_MIXED_WIDTHS,于 DCFIFO_MIXED_WIDTHS,定义了 rdusedw 端

口的位宽;

读取第二个数据;

非

识别 FIFO 型号的参数,SCFIFO 或者是 DCFIFO

非

空间或速度优化度参数,当值为 0--5 时为空间优化,

6--10 时为速度优化。

非

是否开启溢出检测,溢出时无视 wrreq,值为 NO 或

OFF,缺省值为 ON;

非

是否开启下溢检测,下溢(读空)时无视 rdreq,值为

笔者博客 /wg2011/

Quartus II LPM 使 用 指 南

FIFO 篇

第 -9- 页

预读模式下对 q 输出的影响

是

定义了 FIFO 深度,值至少为 4,需要满足如下关系

2^(LPM_WIDTHU-1) < LPM_NUMWORDS£ < 2^(LPM_WIDTHU)

.

是

模式开关,选择正常模式或者是预读模式。

在正常模式下,rdreq 有效时才读出数据;

在预读模式下,自 动读出当前 FIFO 中第一个数据

(FIFO 不空时),当 rdreq 信号有效时,开始继续往后

文档版本 V1.0 笔者将随时可能对本教程中的内容进行更改,恕不事先通知。

笔者博客 /wg2011/

Quartus II LPM 使 用 指 南

FIFO 篇

摘要

第 -3- 页

ALTERA 在 LPM 库中提供了参数可配置的单时钟 FIFO(SCFIFO)和双时钟 FIFO(DCFIFO)。 FIFO 主要应用在需要数据缓冲且数据符合先进先出规律的同步或异步场合。LPM 中的 FIFO 包含以 下几种:

输出由读操作而从 FIFO 中读出的数据。 1.SCFIFO 和 DCFIFO 中,输入输出数据的位宽必须相 同; 2.DCFIFO_MIXED_WIDTHS 型 FIFO 输入输出位宽可 以不同,但是根据使用 RAM 的类型不同,输入输出 位宽比率有不同的限制; 当该信号有效时,FIFO 会被认为已经装满,此时不能 再进行写操作;

整数

Write_aclr_synch

Clocks_are_synchro nized Ram_block_type

表二 参数说明

是否必选

描述

是

对于 SCFIFO 和 DCFIFO,该参数定义了 data 和 q 的

位宽,对于 DCFIFO_MIXED_WIDTHS 该参数定义了

data 的宽度;

是

对于 DCFIFO_MIXED_WIDTHS 该参数定义了 q 的宽

Quartus II LPM 使用指南 FIFO 篇

BY WG /wg2011/

Quartus II LPM 使 用 指 南

FIFO 篇

目录

说明 摘要 第一章 FIFO 配置全攻略

1.1 如何配置自己需要的 FIFO 1.2 输入输出端口 1.3 时序要求 1.4 输出状态标记和潜伏期 1.5 避免亚稳态 1.6 同步复位及异步复位的影响 1.7 不同的输入输出位宽 1.8 约束设置

整数 整数

Lpm_showhead

Lpm_type Maximize_speed

整数

Overflow_checking

Underflow_checking

Delay_rdusedw Delay_wrusedw Add_usedw_msb_bit

Rdsync_delaypipe Wrsync_delaypipe Use_eab

NO 或 OFF,缺省值为 ON;

非

非

用于增加 rdusedw 和 wrusedw 的位宽(1bit)防止 FIFO

满时翻转为 0,该参数值为 ON 或 OFF,缺省值为 OFF, 该参数仅针对某些系列器件有效。