单片机课件第七章

合集下载

07 单片机.

要

/WR2: 写控制信号2,低有效 /XFER: 数据传送控制信号 Iout1: 电流输出端1 Iout2: 电流输出端2

技 术 指

Rfb: 内置反馈电阻端

标

Vref: 参考电压源,-10~+10V

DGND: 数字量地

AGND: 模拟量地

Vcc: +5~+15V单电源供电端

7.2 MCS-51单片机和D/A转换器的接口

8位D/A,分辨率=Vref/256

CMOS低功耗器件,+5~+15V,单电源

DAC0832

供电

电流输出型器件(需外接运放)

具有双缓冲控制输出

采用T型电阻解码网络结构

参考电压源,-10~+10V

D0—D7:8位数字量输入端 /CS: 片选端,低有效

的

ILE: 数据锁存允许,高有效

主

/WR1: 写控制信号1,低有效

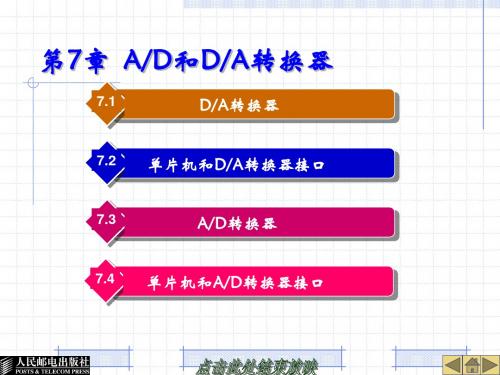

第7章 A/D和D/A转换器

7.1

D/A转换器

7.2 单片机和D/A转换器接口

7.3

A/D转换器

7.4 单片机和A/D转换器接口

7.1 D/A转换器

7.1.1 D/A转换器的原理 7.1.2 D/A转换器的性能指标 7.1.3 典型的D/A转换器芯片DAC0832

7.1.1 D/A转换器的原理

转换结果读取方式: ①延时读数 ②查询EOC=1 ③EOC申请中断

CLOCK

START

1N0 IN1 IN2 IN3 IN4 IN5 IN6 IN7

ADDA ADDB ADDC ALE

通道 选择 开关

定时和控制

逐次逼近 寄存器SAR

比较器

地址锁存 和译码

单片机课件第7章

第7章 MCS-51系列单片机的串行接口 ⑦ SM2:多机通信控制位,主要用于方式2和方式3。在 方式0时,SM2不用,一定要设置为0。在方式1中,SM2也应 设置为0,当SM2 = 1时,只有接收到有效停止位时,RI才置1。 当串行口工作于方式2或方式3时,若SM2 = 1,只有当接收到 的第9位数据(RB8)为1时,才把接收到的前8位数据送入SBUF, 且置位RI发出中断申请,否则会将接收到的数据放弃;当 SM2 = 0时,不管第9位数据是0还是1,都将接收到的前8 位数 据送入SBUF,并发出中断申请。

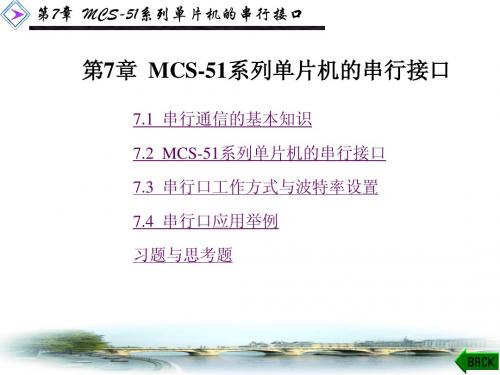

第7章 MCS-51系列单片机的串行接口

图7-2 串行通信数据传送的制式

第7章 MCS-51系列单片机的串行接口 半双工制式(Half Duplex):数据可实现双向传送,但不能 同时进行,实际的应用采用某种协议实现收/发开关转换。如 图7-2(b)所示,数据传送是双向的,但任一时刻数据只能是从 甲站发至乙站,或者从乙站发至甲站,也就是说只能是一方发 送另一方接收。因此,甲、乙两站之间只需一条信号线和一条 接地线。收/发开关是由软件控制的,通过半双工通信协议进 行功能切换。

第7章 MCS-51系列单片机的串行接口 SBUF为串行口的收/发缓冲寄存器,它是可寻址的专用寄 存器,其中包含了发送寄存器SBUF(发送)和接收寄存器 SBUF(接收),可以实现全双工通信。这两个寄存器具有相同名 字和地址(99H)。但不会出现冲突,因为它们一个只能被CPU 读出数据,另一个只能被CPU写入数据,CPU通过执行不同的 指令对它们进行存取。CPU执行“MOV SBUF,A”指令,产生 “写SBUF”脉冲,把累加器A中欲发送的字符送入SBUF(发送) 寄存器中;CPU执行“MOV A,SBUF”指令,产生读SBUF脉 冲,把SBUF(接收)寄存器中已接收到的字符送入累加器A中。 所以,MCS-51的串行数据传输很简单,只要向发送缓冲器 SBUF写入数据即可发送数据。而从接收缓冲器SBUF读出数据 即可接收数据。

单片机第七章ppt

2

定时/计数的方法

实现定时功能,比较方便的办法是利用单片机内 部的定时/计数器。也可以采用下面三种方法:

软件定时:软件定时不占用硬件资源,但占用了

CPU时间,降低了CPU的利用率。 时基电路定时:例如采用555电路,外接必要的元 器件(电阻和电容),即可构成硬件定时电路。但 在硬件连接好以后,定时值与定时范围不能由软件 进行控制和修改,即不可编程。 可编程芯片定时:这种定时芯片的定时值及定时 范围很容易用软件来确定和修改,此种芯片定时功 能强,使用灵活。在单片机的定时/计数器不够用时, 可以考虑进行扩展。

17

7.4 定时/计数器用于外部中断扩展

利用计数器方式,计数初值设定为满程,将待扩 展的外部中断源接到外部计数引脚。当该引脚输入一 个下降沿信号时,计数器便加1,并产生溢出中断。

外部信号

加1计数->溢出->中断

18

例,利用T0扩展一个外部中断源。设置T0为方式2工 作,TH0、TL0的初值均为0FFH,允许中断。其初始 化程序如下: TMOD=0x06 ; 0000 0110置T0为计数器方式2 TL0=0x0FF ; 计数初值为满程 TH0=0x0FF TR0=1 ;启动T0工作 ET0=1 ;允许T0中断 EA =1 ;CPU开中断

3

7.1 定时/计数器的结构和工作原理

一、定时/计数器的结构

定时/计数器的实质是加1计数器(16位),由高8位和低8位 两个寄存器组成。TMOD是定时/计数器的工作方式寄存器, 确定工作方式和功能;TCON是控制寄存器,控制T0、T1的 启动和停止及设置溢出标志。

T1引脚 T0引脚

机器周 期脉冲

TH1

11

三、计数寄存器TH、TL

定时/计数的方法

实现定时功能,比较方便的办法是利用单片机内 部的定时/计数器。也可以采用下面三种方法:

软件定时:软件定时不占用硬件资源,但占用了

CPU时间,降低了CPU的利用率。 时基电路定时:例如采用555电路,外接必要的元 器件(电阻和电容),即可构成硬件定时电路。但 在硬件连接好以后,定时值与定时范围不能由软件 进行控制和修改,即不可编程。 可编程芯片定时:这种定时芯片的定时值及定时 范围很容易用软件来确定和修改,此种芯片定时功 能强,使用灵活。在单片机的定时/计数器不够用时, 可以考虑进行扩展。

17

7.4 定时/计数器用于外部中断扩展

利用计数器方式,计数初值设定为满程,将待扩 展的外部中断源接到外部计数引脚。当该引脚输入一 个下降沿信号时,计数器便加1,并产生溢出中断。

外部信号

加1计数->溢出->中断

18

例,利用T0扩展一个外部中断源。设置T0为方式2工 作,TH0、TL0的初值均为0FFH,允许中断。其初始 化程序如下: TMOD=0x06 ; 0000 0110置T0为计数器方式2 TL0=0x0FF ; 计数初值为满程 TH0=0x0FF TR0=1 ;启动T0工作 ET0=1 ;允许T0中断 EA =1 ;CPU开中断

3

7.1 定时/计数器的结构和工作原理

一、定时/计数器的结构

定时/计数器的实质是加1计数器(16位),由高8位和低8位 两个寄存器组成。TMOD是定时/计数器的工作方式寄存器, 确定工作方式和功能;TCON是控制寄存器,控制T0、T1的 启动和停止及设置溢出标志。

T1引脚 T0引脚

机器周 期脉冲

TH1

11

三、计数寄存器TH、TL

单片机原理与应用 第七章 优质课件

上一页 下一页 返回

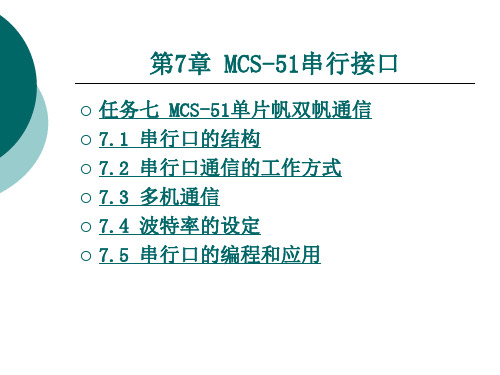

任务七 MCS-51单片帆双帆通信

LOOP:JNB TZI,$ CLTZ RI

MOV A,SBUF MOV 60H,A

TCALL DISP DISP:MOV A , 60H

M()V DPTR, #TAB MOVC A,@A+DPTR MOV PO,A RET

TAB:DB OCOH,OF9H,OA4H,OBOH,99 H_92 H_82 H_OFBH DB 80H,90 H,88H,83H,OC6H OA1H_RhH_REH END;结束伪指令

TAB:DB OCOH,OF9H,OA4H,OBOH,99H,92 H,82 H,OFBH, DB 80H,90H,88H,83H,OC6H,OA1H,86H,8EH, END

这段程序烧到一个实验板上,开机时显示“o 0},当按下 一个键是显示对应 的键号,与此同时通过TXD发送所显示数据的BCD码。此板就作 为发送机。

上一页 下一页 返回

任务七 MCS-51单片帆双帆通信

KEY4:LCALL DEL JB P3.5,KEYEXIT MOV 60H,#4

KEY44:JNB P3.5,$ LCALL DEL JNB P3.5 , KEY44 LJMP KEYEXIT

SEND:MOV A , 60H CJNE A , #1 , SEND1 LCALL SENDBYTE

任务描述

1.按下按键,数码管显示其键号 2.与此同时发送其键号的BCD码 3.接收机显示收到BCD的数值

下一页 返回

任务七 MCS-51单片帆双帆通信

1.电路原理图 串行通信电路原理图见图7-1所示。

2.参考程序

ORG

OOOOH

MOV TMOD,#20 H

任务七 MCS-51单片帆双帆通信

LOOP:JNB TZI,$ CLTZ RI

MOV A,SBUF MOV 60H,A

TCALL DISP DISP:MOV A , 60H

M()V DPTR, #TAB MOVC A,@A+DPTR MOV PO,A RET

TAB:DB OCOH,OF9H,OA4H,OBOH,99 H_92 H_82 H_OFBH DB 80H,90 H,88H,83H,OC6H OA1H_RhH_REH END;结束伪指令

TAB:DB OCOH,OF9H,OA4H,OBOH,99H,92 H,82 H,OFBH, DB 80H,90H,88H,83H,OC6H,OA1H,86H,8EH, END

这段程序烧到一个实验板上,开机时显示“o 0},当按下 一个键是显示对应 的键号,与此同时通过TXD发送所显示数据的BCD码。此板就作 为发送机。

上一页 下一页 返回

任务七 MCS-51单片帆双帆通信

KEY4:LCALL DEL JB P3.5,KEYEXIT MOV 60H,#4

KEY44:JNB P3.5,$ LCALL DEL JNB P3.5 , KEY44 LJMP KEYEXIT

SEND:MOV A , 60H CJNE A , #1 , SEND1 LCALL SENDBYTE

任务描述

1.按下按键,数码管显示其键号 2.与此同时发送其键号的BCD码 3.接收机显示收到BCD的数值

下一页 返回

任务七 MCS-51单片帆双帆通信

1.电路原理图 串行通信电路原理图见图7-1所示。

2.参考程序

ORG

OOOOH

MOV TMOD,#20 H

(单片机完整课件PPT)第七章

当SM2=1时,只有当接收到第9位数据(RB8)为1时,才将接 收到的前8位数据送入SBUF,并置位RI;否则,将接收到的8位 数据丢弃。当SM2=0时,则不论第9位数据为0还是为1,都将8 位数据装入SBUF中,并置位RI。 REN:允许/禁止接收控制位 0—禁止接收; 1—允许接收。 TB8:发送数据第9位。 RB8:接收数据第9位。 TI: 发送中断标志 RI: 接收中断标志。

(2)输入(接收) 设置:SM0=0,SM1=0,SM2=0,REN=1。

时序:

RXD TXD D0 D1 D2 D3 D4 D5 D6 D7

7.2 MCS-51串行口的结构

内部含有1个可编程全双工串行通信接口,4种工作方式。

1.串行口数据缓冲器SBUF

8位发送/接收缓冲器SBUF,在物理上是独立的两个,包括 发送缓冲器SBUF和接收缓冲器SBUF,只是共用地址 99H,这样可以同时进行发送、接收。 发送缓冲器SBUF只能写入不能读出,接收缓冲器SBUF只能 读出不能写入。

(1)输出(发送)

设置:SM0=0,SM1=0,SM2=0,REN=0。 时序:

RXD TXD D0 D1 D2 D3 D4 D5 D6 D7

串口方式0发送数据时序

发送完8位数据,即SBUF为空,硬件自动置“1”中断标志位TI,

CPU响应中断后必须软件清“0”TI。

应用:扩展一并行口,“串入并出”。

2.串行通信的分类

异步通信(Asynchronous Communication)

数据以字节为单位组成字符帧传送。字符帧由发送端一帧 一帧地发送。两相邻字符帧之间可以无空闲位,也可以有若干 空闲位。这就是异步概念。发送端和接收端的时钟各自独立。 实现双方同步接收是靠字符帧的起始位和停止位。

精品课件-新编单片机原理与应用-第7章

11

3. 关键器件的选择 在选定单片机类型后,通常还要对系统中一些严重影响系 统性能指标的器件(如传感器、微弱信号放大器件等)进行选择。 例如,一个设计合理的测控系统往往因传感器件的精度或使用 条件等因素的限制而达不到应有的效果。

12

4. 软硬件功能划分 同一般的计算机系统一样,单片机应用系统的软件和硬件 在逻辑功能上是等效的。具有相同功能的单片机应用系统,其 软硬件功能可以在很宽的范围内变化。一些硬件电路的功能可 以由软件来实现,反之亦然。例如,系统日历时钟可以用实时 /日历时钟芯片(如MC146818、PCF8563)实现,也可以用定时中 断方式实现;又如无线或红外解码电路,既可由相应解码芯片 承担,也可以通过软件方式(如利用具有上升、下降沿触发捕 获功能的定时器)实现。

14

7.3 硬 件 设 计

硬件设计的任务就是依据总体设计要求,在选定单片机类 型基础上,规划出系统的硬件电路框图、所用元器件及电气连 接关系,生成系统的电原理图;根据经验或经过计算确定系统 中每一元器件的参数(如电阻阻值及公差、耗散功率、耐压)、 型号及封装形式。

15

必要时通过仿真或实验方式对系统内局部电路进行验证,确保 电原理图的正确性和可靠性。在系统原理图及元器件参数、型 号、封装形式完全确定情况下,就可进入印刷电路板设计(也 涉及工艺结构设计内容)阶段。

1) 货源充足、稳定 所选单片机芯片在国内元器件市场上货源要稳定、充足, 有成熟的开发设备(主要指仿真器和编程器)。 对于MCS-51及其兼容芯片来说,在研制阶段可选择带 Flash ROM存储器的CPU芯片,如89C5×系列中的 89C51/52/54/58、89C5××2系列中的 89C51×2/52×2/54×2/58×2、89C51RX系列中的89C51RD2芯 片、SST89E5XRD2系列芯片等,借助通用编程器即可反复修改 监控程序,便于调式;在小批量试产时,可换上相应型号、价 格更低的OTP ROM存储器芯片,如87C××系列中的 87C51/52/54/58或87C5××2系列芯片即可,无须修改硬件(如 PCB)和软件。

单片机第7章

为解决这个问题, 为解决这个问题,才发展了中断的概 中断系统是计算机的重要组成部分。 念。中断系统是计算机的重要组成部分。 实时控制、 实时控制、故障自动处理往往采用中断系 统,计算机与外围设备间传送数据及实现 人机联系也常采用中断方式。 人机联系也常采用中断方式。

图7-1

中断处理过程

2.中断的特点

C :功能选择位。 / T = 0 时,设置 功能选择位。 为定时器工作方式; 为定时器工作方式;C / T = 1 时,设置为计 数器工作方式。 数器工作方式。 M1M0:工作方式选择位。共有4 M1M0:工作方式选择位。共有4种工作 方式,如表7 所示。 方式,如表7-3所示。

C/T

表7-3

2.中断服务程序部分

① 在相应的中断入口地址单元设置一 条跳转指令, 条跳转指令,使程序转移到中断服务程序 的入口处。 的入口处。 ② 根据需要保护现场。 根据需要保护现场。 若为电平触发的外部中断, ③ 若为电平触发的外部中断,应有中 断信号撤除操作。 断信号撤除操作。

安排中断服务所做的操作。 ④ 安排中断服务所做的操作。 恢复现场。 ⑤ 恢复现场。 中断返回。 ⑥ 中断返回。 下面给出一个中断系统的应用实例。 下面0溢出标志位。其功能及操 : 溢出标志位 作情况同TF1。 作情况同 。 TR0:T0运行控制位 运行控制位。 ④ TR0:T0运行控制位。其功能及操 作情况同TR1。 作情况同 。 ⑤ IE1:外部中断 ( INT1)请求标志 :外部中断1( 位。 ⑥ IT1:外部中断1触发方式选择位。 :外部中断 触发方式选择位。 触发方式选择位

7.3.3

定时器的工作方式

1.方式0(M1M0=00) 方式0 M1M0=00)

方式0构成一个13位定时器, 方式0构成一个13位定时器, 13位定时器

《单片机原理与技术》课件第7章-中断

1.定时器/计数器控制寄存器TCON

位7

位6

位5

位4

位3

位2

位1

位0

TF1

TR1

TF0

TR0

IE1

IT1

IE0

IT0

IT0:外部中断INT0触发方式选择 位。可由用户用软件选择。 • IT0=1:设定外部中断引脚信号为下降 沿触发方式。 •

IT1:外部中断INT1触发方式选择 位,其功能类似于IT0。 • IE0:外部中断INT0触发有效标志 位。 • IE1:外部中断INT1触发有效标志 位,其功能类似于IE0。 •

•

定时器0与定时器1标志为TF0与TF1, 在定时器溢出周期的S5P2设置。然后其值 在下一周期由电路查询。然而,定时器2标 志TF2是在S2P2设置且在定时器溢出的同 一周期内被查询。 Nhomakorabea•

若请求有效且响应的条件正确,至请 求的服务例程的硬件子例程调用将是下一 条要执行的指令。CALL自己需要两个周期。 因此,在外部中断请求的激活与服务例程 的第一条指令的执行开始之间,至少需要3 个完整的机器周期。图7-9所示为中断响应 时序。

图7-4 中断响应、服务及返回流程图

7.3 80C51中的中断结构

7.3.1 中断启用

图7-5 MCS-51中断源

图7-6 80C51中的IE(中断启用)寄存器

7.3.2

中断优先权

图7-7 80C51中的IP(中断优先级)寄存器

7.3.3

•

中断如何处理

在操作中,所有中断标志在每个机器 周期的S5P2期间被采样。在下一个机器周 期期间查询采样。若找到一启用的中断的 标志已设置,中断系统生成一LCALL至在 程序存储器中的适当单元,至中断服务例 程的LCALL的生成,由以下3个条件中的任 一个阻断:

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

线选法是将高位地址线直接连到存储器芯片的片选端,如图7-2所示。图中

芯片6264是8K×8位存储器芯片,高位地址线P2.5、P2.6、P2.7实现片选,

均为低电平有效:低位地址线A0~A12实现片内寻址。为了不出现寻址错误, 要求在同一时刻P2.5、P2.6、P2.7中只允许有一根为低电平,另二根必须为

当P0、P2、P3口用作系统总线时,就不能再作为输入/输出接口使用,程序

中尽量不要出现对P0、P2、P3口的操作指令,以免造成总线的混乱。

3.单片机的串行扩展技术 串行扩展是通过串行接口实现的,这样可以减少芯片的封装引脚,降低成本,

简化系统结构,增加系统扩展的灵活性。在第10章会详细介绍串行扩展技术。

高电平,否则寻址会出现错误。三片存储器芯片地址分配如表7-1所示。

表 7-1 图 7-3 中各 6264 芯片的地址空间分配 P2.7 0 1 1 P2.6 1 0 1 P2.5 1 1 0 选中芯片 3#6264 2#6264 1#6264 地址范围 6000H~7FFFH A000H~BFFFH C000H~DFFFH 存储容量 8KB 8KB 8KB

2. 总线构造

(1)数据总线

AT89S51单片机数据总线是由P0口提供的,由P0口引出8根线作为数据总线。 (2)地址总线 AT89S51单片机地址总线为16根,其中高8位由P2口提供,低8位由P0口。 P0口既作为数据总线,又作为低8位地址总线,采用分时复用技术,对地址 和数据进行分离。

器是在EPROM与E2PROM基础上发展起来的,读写速度都很快,存取时间可达70ns,而且 成本却比普通的E2PROM低得多,所以目前大有取代E2PROM的趋势。

EPROM芯片是常用程序存储器芯片之一,是系列器件,以27×××命名,

其中×××代表存储器的容量,单位为Kbit即千位。常见的有2716,2732,

但有时片内资源不能满足系统的设计需求,就需要扩展存储器,AT89S51单 片机数据存储器和程序存储器的最大扩展空间都是64KB。为了使一个存储单 元唯一的对应一个地址,这就要求合理的使用系统提供的地址线,通过适当 的连接来达到要求,这就是编址。内存储单元已经编址,只有扩展存储器才 有编址问题。常用的编址方法有两种,即:线选法和译码法。

单片机的程序存储器扩展使用只读存储器芯片。只读存储器简称为ROM。ROM中

的信息一但写入之后就不能随意更改,特别是不能在程序的运行过程中写入新的

内容,而只能读存储单元内容,故称之为只读存储器。根据编程方式的不同, ROM共分为以下5种:

1)掩模ROM

掩模ROM由芯片制造商在制造时写入内容,以后只能读而不能再次写入。基本

AT89S51单片机系统的扩展结构如图7-1所示,单片机扩展是以单片机为核

心进行的,主要包括ROM、RAM和I/O接口电路的扩展。

1.系统总线

总线就是连接计算机各部件的一组公共信号线。AT89S51单片机使用的是并

行总线结构,按功能分为地址总线、数据总线和控制总线三组。

(1)数据总线DB(Data Bus)

1 1 1 1 1 1 0 1 1 1 1

Y3

1 1 1 1 1 1 1 0 1 1 1

Y3

1 1 1 1 1 1 1 1 0 1 1

Y3

1 1 1 1 1 1 1 1 1 0 1

Y3

1 1 1 1 1 1 1 1 1 1 0

1 0 0 0 0 0 0 0 0

1 0 0 0 0 0 0 0 0

2764,27128,27256,27512,其容量分别为2 KB,4 KB,8 KB, 16 KB,32 KB,64 KB。下面以2764为典型芯片进行说明。

2764的引脚如图7-8所示,引脚功能如下:

数据总线用于数据传送,AT89S51单片机是8位字长,数据总线有8根,存

储单元和I/O端口等数据单元的各位由低到高分别与8根线相连。数据传输是 双向的。但某一时刻只能有一个存储单元或外设与总线信号相通,其它单元

尽管连接在数据总线上,但与数据总线的信息是隔离的。

(2)地址总线AB(Address Bus)

从表 7-1 中看出 3 个存储器片内地址线 A0~ Al2 都是从 0000000000000 到 1111111111111(共 13 位) ,为 8K 空间;而 P2.5、P2.6、P2.7 分别连接 3 个芯片 的片选端,也就是用来区别是哪一片存储器芯片。

连接简单,缺点是芯片的地址空间相互之间可能不连续,致使存储空间得不

由于P0口在扩展存储器时既做地址总线的低8位,又做数据总线,为了将他

们分离出来,需要在单片机外部增加地址锁存器,以锁存低8位地址。一般

可采用74LS373。74LS373逻辑符号如图7-7所示。

74LS373 的引脚说明如下: D0~D7:数据输入端。 Q0~Q7:数据输出端。 :三态输出允许,低电平有效,高电平时输出呈高阻态。 LE:数据锁存端。 74LS373 有 8 个带三态输出的锁存器, 适用于总线结构的系统。 地址锁存信 号 LE 由单片机 ALE 控制线提供,当 ALE 为高电平时,锁存器传输数据,输出 端(Q0~Q7)的状态和输入端(D0~D7)的状态相同。ALE 下降沿时,锁存低 8 位地址。

(1)74LS139译码器

74LS139片中共有两个2-4译码器,其引脚排列如图7-4所示。 其中:G为使能端,低电平有效。

A、B为选择端,即译码输入,控制译码输出的有效性。

Y0、Y1、Y2、Y3为译码输出信号,低电平有效。 74LS139对两个输入信号译码后得4个输出状态,其真值表如表7-2所示。

(3)控制总线 AT89S51 单片机控制线有 W R 、 RD 、 P SEN 、ALE、 EA 等,分别说明如下: ① W R 、 RD 为读、写信号。用于扩展片外数据存储器及 I/O 端口的读写选 通信号, 当执行外部数据存储器操作 MOVX 指令时, 这两个信号分别自动生成。 ② EA 为片外 ROM 选通信号。 ③ P SEN 为外部 ROM 读选通信号。用于片外扩展程序存储器的读选通信 号,执行片外程序或查表指令 MOVC 时,该信号自动生成。 P SEN 与扩展的程 序存储器输出允许端相接。 ④ ALE 为地址锁存允许信号。

存储原理是:以元器件的“有/无”来表示存储的信息(“1”或“0”),可以 用二极管或晶体管作为元件。 2)可编程PROM (Programmable ROM) PROM可由用户根据自己的需要来确定ROM中的内容。常见的熔丝式PROM是 以熔丝的接通和断开来表示所存的信息(“1”或“0”)。显而易见,断开后的 熔丝是不能再接通了,因此,它是一次性写入的存储器。

存储器扩展是单片机系统扩展的主要内容,因为扩展是在单片机芯片之外进

行的,因此通常把扩展的程序存储器ROM称之为外部ROM,把扩展的数据存

储器RAM称之为外部RAM。

AT89S51单片机片内集成了4KB的Flash存储器和128字节的数据存储器,

外部存储器结构采用的是哈佛结构,即程序存储器和数据存储器是分开的。

表 7-2 74LS139 真值表 输入端 使能

G

输出端

选择 B A

Y0

1 0 1 1 1

Y1

Y2

Y3

1 1 1 1 0

1 0 0 0 0

0 0 1 1

0 1 0 1

1 1 0 1 1

1 1 1 0 1

74LS138 是 3-8 译码器, 即对 3 个输入信号进行译码, 得到 8 个输出状态。 74LS138 的引脚排列如图 7-5 所示。 其中: E1 、 E2 、 E3 为使能端,用于引入控制信号。 E1 、 E2 如表7-4所示。

表 7-4 图 7-6 中各 6264 芯片的地址空间分配 P2.7 0 1 1 P2.6 1 0 1 P2.5 1 1 0 选中芯片 3#6264 2#6264 1#6264 地址范围 6000H~7FFFH A000H~BFFFH C000H~DFFFH 存储容量 8KB 8KB 8KB

E3 高电平有效。

A、B、C 为选择端,即译码信号输入端。 Y7~Y0 为译码输出信号,低电平有效。 74LS138 的真值表如表 7-3 所示。

输入端 使能 选择

输出端

E3

0

E2

E1

C

B

A 1 1 1 0 1 0 1 0 1 0 1

Y0

1 1 1 0 1 1 1 1 1 1 1

Y1

Y2

Y3

E2PROM也称EEPROM,是可电擦除的可编程只读存储器。E2PROM的编程原理与EPROM

相同,但擦除原理完全不同,它利用电信号擦除数据,并能对单个存储单元擦除和写入,使 用十分方便。 5)闪速存储器(Flash Memory)

E2PROM虽然具有可读又可写的特点,但是写入的速度较慢,使用起来不太方便。闪速存储

7.2程序存储器EPROM的扩展

7.3静态数据存储器RAM的扩展 7.4 AT89S51扩展并行I/O接口芯片82C55的设计 7.5案例:使用EPROM扩展AT89S51单片机程序存储器

7.1.1系统扩展结构

在构建单片机应用系统时,许多情况下只靠片内资源是不够的。为此经常需

要对单片机进行扩展,其中主要是存储器扩展和I/O接口扩展,以构成一个满 足需要功能更强的单片机应用系统。

3)紫外线擦除可编程EPROM(Erasable Programmable ROM)

EPROM中的内容可多次修改。这种芯片的上面有一个透明窗口,紫外线照射后能擦除芯