数字逻辑电路课件第五章习题

数字电子技术黄瑞祥 第五章习题答案

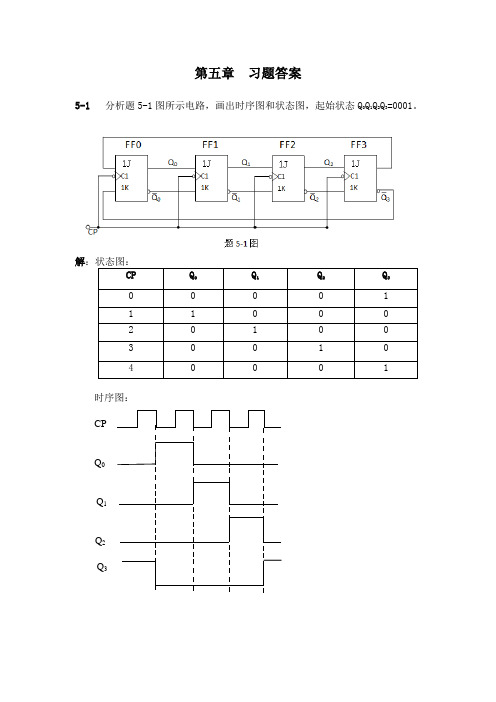

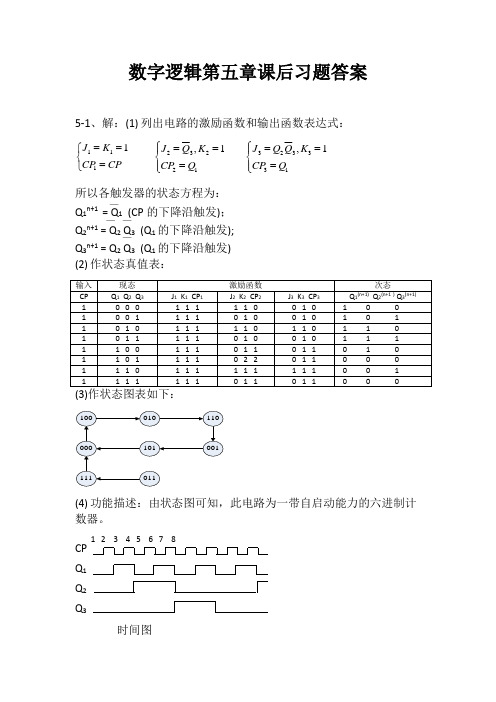

第五章习题答案5-1分析题5-1图所示电路,画出时序图和状态图,起始状态Q0Q1Q2Q3=0001。

解CP Q0 Q1Q2Q30 0 0 0 11 1 0 0 02 0 1 0 03 0 0 1 04 0 0 0 1 时序图:CPQ0Q1Q2Q35-2分析题5-2图所示电路,画出电路的状态图。

解CP Q0 Q1 Q20 0 0 01 1 0 02 0 1 03 0 0 14 0 0 05-3 JK触发器组成5-3图所示电路。

分析该电路为几进制计数器,并画出电路的状态图。

CP Q1 Q2Q30 0 0 01 1 0 02 0 1 03 1 1 04 0 0 15 0 0 0 该电路为五进制计数器5-4JK触发器促成如图5-4图所示的电路。

(1)分析该电路为几进制计数器,画出状态图。

(2)若令K3= 1,电路为几进制计数器,画出其状态图。

解:(1CP Q1 Q2Q30 1 2 3 4 5 6 7 0 0 01 0 00 1 01 1 00 0 11 0 1 0 1 1 0 0 0为7进制计数器CP Q1 Q2Q30 1 2 3 4 5 0 0 01 0 00 1 01 1 00 0 11 0 0为4进制计数器5-5 试画出题5-5图(a)所示电路中B,C端的波形。

输入端A,CP波形如题5-5图(b)所示,触发器的起始状态为零。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19CPAQ0Q1BC5-6分析题5-6图所示电路,画出电路的状态图,说明电路能否自启动。

CP Q1 Q2Q3Z0 1 2 3 4 5 6 7 0 1 0 0 0 01 0 1 0 1 1 1 00 1 1 11 0 0 0 1 1 0 00 1 0 01 0 1 00 0 1 01 0 0 0该电路能够自启动5-7 分析题5-7图所示电路,画出电路的状态图,说明电路能否自启动。

CP Q4 Q3Q2Q11234 567111111111 0 0 0 00 0 0 11 0 0 11 1 0 11 1 1 00 1 1 11 0 1 11 1 0 10 0 1 00 0 0 10 0 1 11 0 0 10 1 0 00 0 1 10 1 0 11 0 1 10 1 1 00 0 1 11 0 0 00 1 0 11 0 1 00 1 0 11 1 0 00 1 1 11 1 1 1 1 1 1 0由状态图可见,电路图能够自启动5-8画出题5-8图所示电路的状态图和时序图,简要说明电路的基本功能。

数电第五章习题答案精编版

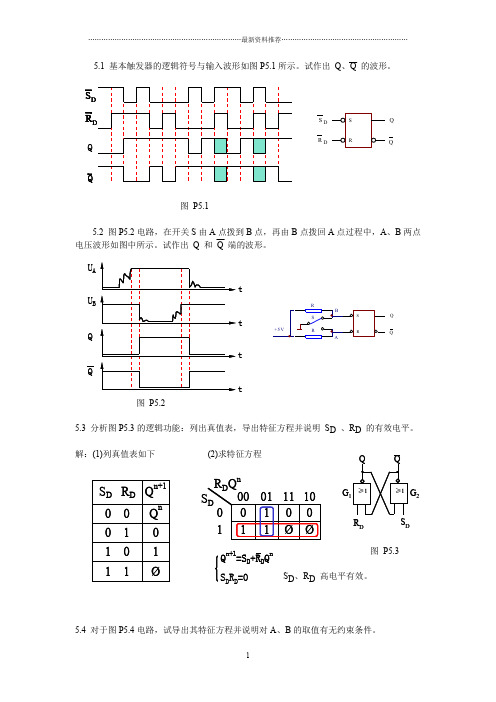

5.4 对于图P5.4电路,试导出其特征方程并说明对A、B的取值有无约束条件。

Q图P5.11P5.125.12 画出图P5.12电路中Q 1、Q 2 的波形。

解:特征方程为: ,Q 端波形如图P5.12所示。

=[D]·CP 1,Q 1n+1Q 2n+1= Q 1n[]·CP 2图P5.14 图P5.155.15 画出图P5.15电路中Q 端的波形。

解:Q 端波形如图P5.15所示。

5.16 试作出图P5.16电路中Q A 、Q B 的波形。

解:特征方程为: , ,Q 端波形如图P5.16所示。

图P5.16 图P5.17Q A n+1= Q B n[]·A Q B n+1= Q A n []·BA R DB Q A Q BR D CP CP ⊕Q 2Q 1Q 25.17 试作出图P5.17电路中Q 1、Q 2 的波形。

解:特征方程为: , ,Q 端波形如图P5.17所示。

5.18 试作出图P5.18电路中Q 1和Q 2的波形(设Q 1和Q 2的初态均为“0”),并说明Q 1和 Q 2对于CP 2各为多少分频。

解:特征方程为: , ,Q 端波形如图P5.18所示。

Q 1和Q 2对于CP 2都是4分频,即图P5.18 图P5.195.19 已知电路如图P5.19,试作出Q 端的波形。

设Q 的初态为“0”。

解:特征方程为: ,Q 端波形如图P5.19所示。

5.20 已知输入u I 、输出u O 波形分别如图P5.20所示,试用两个D 触发器将该输入波形u I 转换成输出波形u O 。

解:输出u O 是对输入u I 的4分频,而采用1个DFF 可实现2分频,故实现电路如图P5.20所示。

图P5.205.21 试分别用公式法和列表图解法将主从SR 触发器转换成JK 触发器。

解1:Q 1n+1= Q 1n []·(CP ⊕Q 2)Q 2n+1= Q 2n []·Q 1?)?,(2221==CP Q CP Q f f f f Q 1n+1= Q 1n []·CP 1Q 2n+1= ·Q 2n []·CP 2Q 1n CP 2CP 1Q 1Q 241,412221==CP Q CP Q f f f f Q n+1= [ A ]·CP CP A Qu Iu OQ n+1=S+RQ n SR =0Q n+1=JQ n +KQn令新老触发器的次态方程相等,则有S=JQ n ,R=K但不满足约束条件SR =0。

数电第五版(阎石)第五章课后习题及答案pptx

03

习题三答案ຫໍສະໝຸດ 习题三第1题答案1.1 逻辑函数的表示方法 1.1答案:逻辑函数有多种表示方法, 如真值表、逻辑表达式、波形图和卡

诺图等。

1.2 逻辑函数的化简方法

1.2答案:逻辑函数的化简方法包括代 数法、公式法和卡诺图法等。

1.3 逻辑函数的运算规则

1.3答案:逻辑函数的运算规则包括与、 或、非等基本运算,以及与或、与非、 或非等复合运算。

习题一第3题答案

总结词

卡诺图化简

答案

通过卡诺图化简,我们得到最简的逻 辑表达式为(F = A'B + A'C + BC)。

02

习题二答案

习题二第1题答案

总结词

逻辑函数的表示方法

详细描述

逻辑函数的表示方法有真值表、逻辑表达式、逻辑图和波形图等。这些表示方法各有特 点,可以根据具体需求选择使用。真值表可以清晰地表示输入和输出之间的逻辑关系; 逻辑表达式简化了函数表示,便于分析和计算;逻辑图能够直观地展示逻辑函数的结构

习题三第2题答案

在此添加您的文本17字

2.1 逻辑函数的化简步骤

在此添加您的文本16字

2.1答案:逻辑函数的化简步骤包括合并项、消去项和简 化表达式等。

在此添加您的文本16字

2.2 逻辑函数的化简技巧

在此添加您的文本16字

2.2答案:逻辑函数的化简技巧包括利用运算规则、消去 项和合并项等。

在此添加您的文本16字

和功能;波形图则可以反映函数在时间序列上的动态变化。

习题二第2题答案

总结词

逻辑函数的化简方法

详细描述

逻辑函数的化简方法有多种,包括公式化简法、卡诺 图化简法和布尔代数化简法等。公式化简法基于逻辑 代数的基本公式和规则,通过简化表达式得到最简结 果;卡诺图化简法利用卡诺图的性质,通过图形直观 地找出最小项的组合,从而得到最简逻辑函数表达式 ;布尔代数化简法则通过代数运算简化逻辑函数。这 些化简方法各有优缺点,应根据具体情况选择使用。

数电第五版第五章课后习题及答案演示精品PPT课件

【题5.15】已知CMOS边沿触发方式JK触发器各输入端 的电压波形如图P5.15所示,试画出Q,Q’端对应的电压 波形。

20

解:根据JK触发器逻辑功能的定义和边沿触发方式的动作特 点,画出的Q,Q’ 端电压波形如图A5.15。

21

【题5.18】设图P5.18中各触发器的初始状态皆为Q=0,试画 出在CLK信号连续作用下各触发器输出端的电压波形

10

解:根据SR触发器逻辑功能的定义及脉冲触发方式的动作特 点,即可画出图A5.8中Q和Q’的电压波形。

11

【题5.9】 若主从结构SR触发器的CLK,S,R, 各输入端电压波 形如图P5.9所示, =1,试画出Q,Q’ 端对应的电压波形。

12

解:根据SR触发器逻辑功能的定义及脉冲触发方式的动作特 点,即可画出Q,Q’的电压波形,如图A5.9所示。

学习要点: 1、不同电路结构触发器的动作 特点; 2、不同逻辑功能触发器的特性;

1

【题5.1】 画出图P5.1由与非门组成的SR锁存器输出端Q,Q’的 电压波形,输入端 , 的电压波形如图中所示。 解:见图A5.1.

No Image

2

3

【题5.4】图P5.4所示为一个防抖动输出的开关电路。当拨动 开关S时,由于开关触点接通瞬间发生振颤 , 和 的电压波 形如图中所示,试画出Q,Q’端对应的电压波形。

从高电平跳变成低电平以后电路的工作过程与上述过 程类似。这样就得到了图A5.20的 电压波形。

25

【题5.21】 在图P5.21所示的主从JK触发器电路中,CLK 和 A 的电压波形如图中所示,试画出 Q 端对应的电压波形。设触 发器的初始状态为 Q = 0.

26

写在最后

经常不断地学习,你就什么都知道。你知道得越多,你就越有力量 Study Constantly, And You Will Know Everything. The More

数字逻辑第5章习题参考解答

5.31BUT门的可能定义是:“如果A1和B1为1,但A2或B2为0,则Y1为1;Y2的定义是对称的。

”写出真值表并找出BUT门输出的最小“积之和”表达式。

画出用“与非-与非”电路实现该表达式的逻辑图,假设只有未取反的输入可用。

你可以从74x00、04、10、20、30组件中选用门电路。

解:真值表如下利用卡诺图进行化简,可以得到最小积之和表达式为Y1=A1·B1·A2’+A1·B1·B2’Y2=A1’·A2·B2+B1’·A2·B2Y2采用74x04得到各反相器采用74x10得到3输入与非采用74x00得到2输入与非5.32做出练习题5.31定义的BUT门的门级设计,要求以cmos实现时使用的晶体管数目最少,可以从74x00、04、10、20、30组件中选用门电路.写出输出表达式(不一定是二级“积之和”)并画出逻辑图。

解:cmos晶体管用量:反相器2个2输入与非门4个3输入与非门6个为了尽量减少晶体管用量,可以采用下列表达式,以便实现器件的重复使用:F1=(A1·B1)·(A2’+B2’)=(A1·B1)·(A2·B2)’=[(A1·B1)’+(A2·B2)’’]’F2=[(A2·B2)’+(A1·B1)’’]’电路图:晶体管用量:20只(原设计中晶体管用量为40只)5.34已知函数,,,(3,7,11,12,13,14)W X Y Z F =∑,说明如何利用练习题5.31定义的单个BUT 门和单个二输入或门实现F.解:BUT 门输出采用最小项和的形式表达为()∑=2,2,1,114,13,121B A B A Y ,()∑=2,2,1,111,7,32B A B A Y将两个输出相或就可以得到要求实现的函数。

5.19指出用一块或多块74x138或74x139二进制译码器以及与非门,如何构建下面每个单输出或多输出的逻辑功能(提示:每个实现等效于一个最小项之和)。

数电第五章习题答案 .doc

自我检查题5.1 时序电路和组合电路的根本区别是什么?同步时序电路与异步时序电路有何不同?解答:从功能上看,时序电路任何时刻的稳态输出不仅和该时刻的输入相关,而且还决定于该时刻电路的状态,从电路结构上讲,时序电路一定含有记忆和表示电路状态的存储器。

而组合电路任何时刻的稳态输出只决定于该时刻各个输入信号的取值,由常用门电路组成则是其电路结构的特点。

在同步时序电路中,各个触发器的时钟信号是相同的,都是输入CP 脉冲,异步时序电路则不同,其中有的触发器的时钟信号是输入cp 脉冲,有的则是其他触发器的输出,前者触发器的状态更新时同步的,后者触发器状态更新有先有后,是异步的。

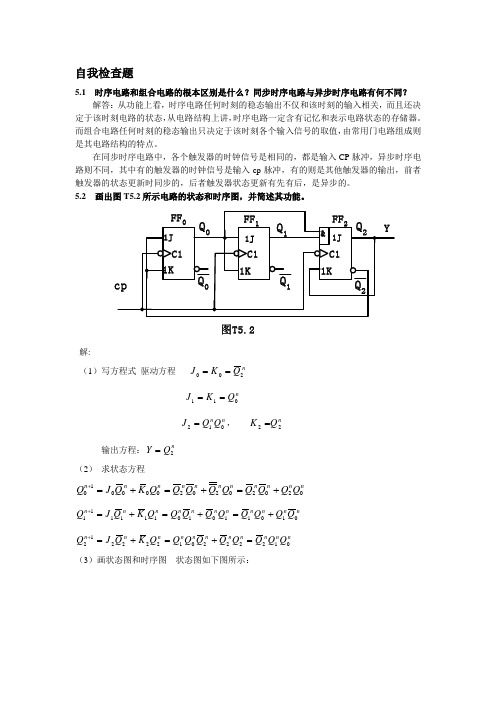

5.2 画出图T5.2所示电路的状态和时序图,并简述其功能。

图T5.2解:(1)写方程式 驱动方程 nQ K J 200==n Q K J 011==n n Q Q J 012=, n Q K 22=输出方程:nQ Y 2= (2) 求状态方程nn n n n n n n n n n Q Q Q Q Q Q Q Q Q K Q J Q 02020202000010+=+=+=+ n n n n n n n n n n n Q Q Q Q Q Q Q Q Q K Q J Q 01011010111111+=+=+=+ n n n n n n n n n n n Q Q Q Q Q Q Q Q Q K Q J Q 01222201222212=+=+=+(3)画状态图和时序图 状态图如下图所示:101时序图如下图所示:CP Q 0Q 1Q 25.3 试用边沿JK 触发器和门电路设计一个按自然态序进行计数的七进制同步加法计数器。

解:(1)状态图如下图:(2)求状态方程、输出方程CQ Q Q n n n /101112+++的卡诺图如下图所示:输出方程为nn Q Q C 12=状态方程:n n n n n Q Q Q Q Q 120112+=+ n n n n n n Q Q Q Q Q Q 0120111+=+ n n n n n Q Q Q Q Q 120110+=+驱动方程:n n n n n n n n n n n n n n n Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q 0122120121220112)(++=++=+n n n n n n Q Q Q Q Q Q 1021011+=+n n n n n Q Q Q Q Q 0012101)(++=+与JK 触发器的特性方程 比较,可以得到驱动方程 n n Q Q J 012= 、 n Q K 12=n Q J 01= 、n n Q Q K 021=n n n n Q Q Q Q J 12120=+= 10=K(4) 无效状态转换情况 111/1000 能自启动(5) 逻辑图如下图所示:5.4 画出用时钟脉冲上升沿触发的边沿D 触发器组成的4位二进制异步加法计数器和减法计数器的逻辑电路图。

数字逻辑第五章课后习题答案

&

&

&

&

X1

X2

X3

设计的脉冲异步时序电路

5-3、解:

X1

X3 x2 >

X3

A/0

<

X1

B/0

X3 X2

D/1

X1 X3

X1

X2

X2

C/0

原始状态图

现态

y A B C D

次态 yn+1

x1

x2

x3

B

A

A

B

C

A

B

A

D

B

A

A

原始状态表

输出

Z 0 0 0 1

5-4、解:(1)写出电路的激励函数和输出函数表达式: Y2=x2+x1y2 y—1+x—1y1; Y1=x2x1+x1y2—+x2—y1;Z=x2—y1 —

x2x1=11 c/-

c/-

c/-

○c /1

○c /1

最简流程表

x2x1=10 b/○b /1 b/-

12 3 45 67 8

CP Q1 Q2 Q3

时间图

5-2、解:表所示为最小化状态表,根据状态分配原则,无“列”相

邻(行相邻在脉冲异步时序电路中不适用。),在“输出”相邻

中,应给 AD、AC 分配相邻代码。取 A 为逻辑 0,如下卡诺图所示,

状态赋值为:A=00,B=11;C=01;D=10。于是,二进制状态表如

J3 K3 CP3 010 010 110 010 011 011 111 011

次态

Q1(n+1) Q2(n+1 ) Q3(n+1)

数字逻辑电路课件第五章

0

1

与非门构成SR锁存器

0 1

SD ' 0, RD ' 1 Q 1, Q ' 0 SET

1

0

与非门构成SR锁存器

1

S D ' 1, RD ' 1

1

Q保持不变

与非门构成SR锁存器

0 1

S 0, R 0

' D ' D

0 1

Q 1, Q ' 1,矛盾

3状态转换图

状态转移方向 转移条件

触发器状态

JK触发器

1特性表

J K Q Q*

2.特性方程 : Q* JQ K Q

0 保持 置1 清0 翻转

0

0 0

0

1 1 0

0 1

0 0 0 1 1 0

1

1 1 0

3状态转移图

0 1

1

1 1 1 0

1 1

0 1

0

D触发器

1特性表

D Q Q*

2.特性方程 : Q* D

CLK输入端的 :触发器为上升沿触发方式; 若CLK端加了小圆圈:下降沿触发;

有异步置,置0端 1

二、边沿触发的动作特点 1)Q*变化发生在clk的上升沿(下降沿) 而与此前、后的状态无关

2)Q*仅取决于上升沿(下降沿)到达时输入的状态,

5.6 触发器的逻辑功能及其描述方法

SR触发器 JK触发器 T触发器

3状态转移图

0 0 1 1

0 0 1 0 0 1 1 1

T触发器

Q

0 1 0 1 0 1 0 1 0 1

Q*

0 1 0 保持 1 1 置1 1 0 清0 0 1① 不允许 1①