计算机组成原理实验三数据输出移位门

计算机组成原理实验

实验一算术逻辑运算单元实验一.实验目的1、掌握简单运算器的数据传输方式2、掌握74LS181的功能和应用二.实验要求完成不带进位位算术、逻辑运算实验。

按照实验步骤完成实验项目,了解算术逻辑运算单元的运行过程。

三.实验说明3.1 ALU单元实验构成(如图2-1-1)(1)、运算器由2片74LS181构成8位字长的ALU单元。

(2)、2片74LS374作为2个数据锁存器(DR1、DR2),8芯插座ALU-IN作为数据输入端,可通过短8芯扁平电缆,把数据输入端连接到数据总线上。

(3)器的数据输出由一片74LS244(输出缓冲器)来控制,8芯插座ALU-OUT作为数据输出端,可通过短8芯扁平电缆把数据输出端连接到数据总线上。

图2-1-1图2-1-23.2 ALU单元的工作原理(如图2-1-2)数据输入锁存器DR1的EDR1为低电平,并且D1CK有上升沿时,把来自数据总线的数据打入锁存器DR1。

同样使EDR2为低电平、D2CK有上升沿时把数据总线上的数据打入数据锁存器DR2。

算术逻辑运算单元的核心是由2片74LS181组成,它可以进行2个8位二进制数的算术逻辑运算,74LS181的各种工作方式可通过设置其控制信号来实现(S0、S1、S2、S3、M、CN)。

当实验者正确设置了74LS181的各个控制信号,74LS181会运算数据锁存器DR1、DR2内的数据。

由于DR1、DR2已经把数据锁存,只要74LS181的控制信号不变,那么74LS181的输出数据也不会发生改变。

输出缓冲器采用74LS244,当控制信号ALU-O为低电平时,74LS244导通,把74LS181的运算结果输出到数据总线;当ALU-O为高电平时,74LS244的输出为高阻。

3.3 控制信号说明四.实验步骤实验1、不带进位位逻辑或运算实验●把ALU-IN(8芯的盒型插座)与CPT-B板上的二进制开关单元中J01插座相连(对应二进制开关H16~H23),把ALU-OUT(8芯的盒型插座)与数据总线上的DJ02相连。

计算机组成原理实验

二、通用寄存器单元实验

3.实验说明 (2)通用寄存器单元的工作原理

二、通用寄存器单元实验

3.实验说明 (2)通用寄存器单元的工作原理 通用寄存器单元的核心部件为2片GAL16V8,它 具有锁存、左移、右移、保存等功能。各个功能 都由X1、X2信号和工作脉冲RACK来决定。当置 ERA=0、X0=1、X1=1,RACK有上升沿时,把总线上 的数据打入通用寄存器。可通过设置X0、X1来指 定通用寄存器工作方式,通用寄存器的输出端Q0-Q7接入判零电路。LED(ZD)亮时,表示当前通用 寄存器内数据为0。

A+B

CN=0,M=0 A+1 (A+B)+1

(A+B) + 1

0

0

AB

B A⊕B A B A +B A⊕B

A+AB (A+B)+AB

A-B-1

AB- 1

A+AB+ 1 (A + B )+ A B +1

A-B

A B

A+AB A+B AB-1 A+A (A+B)+A

(A+B)+A

(A+B)+AB

A+AB+1 A+B+1

一、算术逻辑运算单元实验

4.实验步骤 (2)不带进位位加法 74LS181的M=0,CN=1,S3S2S1S0=1110,则 74LS181工作在无进位位加法运算状态,运算为 F=A加B 本实验中,A=33H,B=55H 应得结果为:F=33H加55H=88H LED显示结果:88H 结果正确?

一、算术逻辑运算单元实验

一、算术逻辑运算单元实验

《计算机组成原理》实验

实验一、运算实验算术逻辑一、实验目的1、掌握简单运算器的数据传送通路2、验证运算功能发生器(74LS181)的组合功能二、实验设备CCT-IV计算机组成原理教学实验系统一台,排线若干。

三、实验原理实验中的运算器由两片74LS181构成。

运算器的输出经过一个三态门74LS245和数据总线相连,运算器的两个数据输入端,分别由二个锁存器74LS273锁存,锁存器的输入端和数据总线相连,数据输入输出都通过总线完成;数据显示灯(“BUS UNIT”)与数据总线相连,用来显示数据总线内容。

实验中的数据输入由数据开关(“INPUT DEVICE”)给出,并经过三态门74LS245和数据总线相连,数据输出可以经总线输出至七段数码管(“OUTPUT DEVICE”)显示S3S2S1S0MLDDR1 T4 LDDR2SW-B图1-2运算器数据通路图1-2中T4为脉冲信号,其它均为电平信号。

在实验中,只需将“W/R UNIT”的T4接至“STATE UNIT”的微动开关KK2的输出端,按动微动开关,即可获得实验所需的单脉冲,而S3、S2、S1、S0、Cn、M、LDDR、ALU-B、SW-B各电平控制信号用“SWITCH UNIT”中的二进制数据开关来模拟,其中Cn、ALU-B、SW-B为低电平有效,LDDR1,LDDR2为高电平有效进位控制运算的实验,是在前面实验的基础上增加进位控制部分(如1-3图所示),其中181的进位进入一个74锁存器,其写入是由T4的AR信号控制,T4是脉冲信号,实验时将T4连至“STATE UNIT”的微动开关KK2上。

AR是电平控制信号,可用于实现带进位控制实验,而T4脉冲是将本次运算的进位结果锁存到进位锁存器中。

四、实验内容1、按图1-1实验接线图连接线路,仔细查线无误后,接通电源。

2、用二进制数码开关分别向DR1和DR2寄存器臵数01100101,10100111。

①打开数据输入三态门SW-B=0 关闭运算器输出三态门ALU-B=1②向寄存器DR1传送数据,数据开关臵01100101,LDDR1=1,LDDR2=0,按下KK2,产生T4信号③向寄存器DR2传送数据,数据开关臵10100111,LDDR1=0,LDDR2=1,按下KK2,产生T4信号④关闭数据输入三态门SW-B=1,打开运算器输出三态门ALU-B=0⑤当臵S3、S2、S1、S0、M为11111时,总线指示灯DR1中的数,而臵成10101时总线指示DR2中的数。

计算机组成原理实验报告

计算机组成原理实验报告实验报告运算器实验⼀、实验⽬的掌握⼋位运算器的数据传输格式,验证运算功能发⽣器及进位控制的组合功能。

⼆、实验要求完成算术、逻辑、移位运算实验,熟悉ALU运算控制位的运⽤。

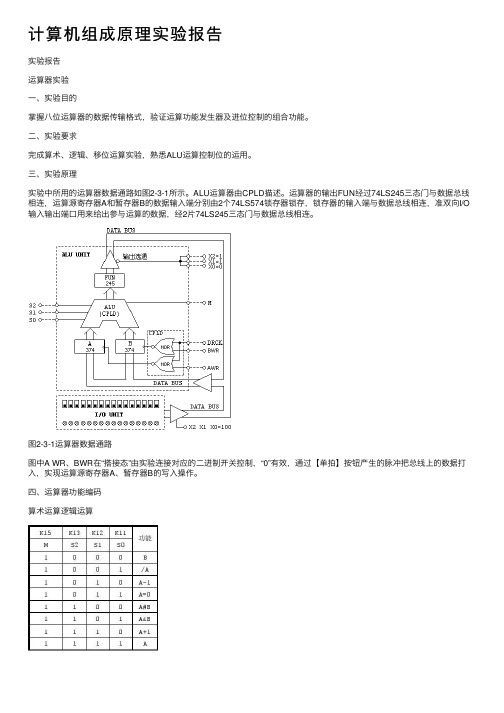

三、实验原理实验中所⽤的运算器数据通路如图2-3-1所⽰。

ALU运算器由CPLD描述。

运算器的输出FUN经过74LS245三态门与数据总线相连,运算源寄存器A和暂存器B的数据输⼊端分别由2个74LS574锁存器锁存,锁存器的输⼊端与数据总线相连,准双向I/O 输⼊输出端⼝⽤来给出参与运算的数据,经2⽚74LS245三态门与数据总线相连。

图2-3-1运算器数据通路图中A WR、BWR在“搭接态”由实验连接对应的⼆进制开关控制,“0”有效,通过【单拍】按钮产⽣的脉冲把总线上的数据打⼊,实现运算源寄存器A、暂存器B的写⼊操作。

四、运算器功能编码算术运算逻辑运算K23~K0置“1”,灭M23~M0控位显⽰灯。

然后按下表要求“搭接”部件控制路。

表2.3.2 运算实验电路搭接表算术运算1.运算源寄存器写流程通过I/O单元“S7~S0”开关向累加器A和暂存器B置数,具体操作步骤如下:2.运算源寄存器读流程关闭A、B写使能,令K18=K17=“1”,按下流程分别读A、B。

3.加法与减法运算令M S2 S1 S0(K15 K13~K11=0100),为算术加,FUN及总线单元显⽰A+B的结果令M S2 S1 S0(K15 K13~K11=0101),为算术减,FUN及总线单元显⽰A-B的结果。

逻辑运算1.运算源寄存器写流程通过“I/O输⼊输出单元”开关向寄存器A和B置数,具体操作步骤如下:2.运算源寄存器读流程关闭A、B写使能,令K17= K18=1,按下流程分别读A、B。

①若运算控制位设为(M S2 S1 S0=1111)则F=A,即A内容送到数据总线。

②若运算控制位设为(M S2 S1 S0=1000)则F=B,即B内容送到数据总线。

计算机组成原理实验报告

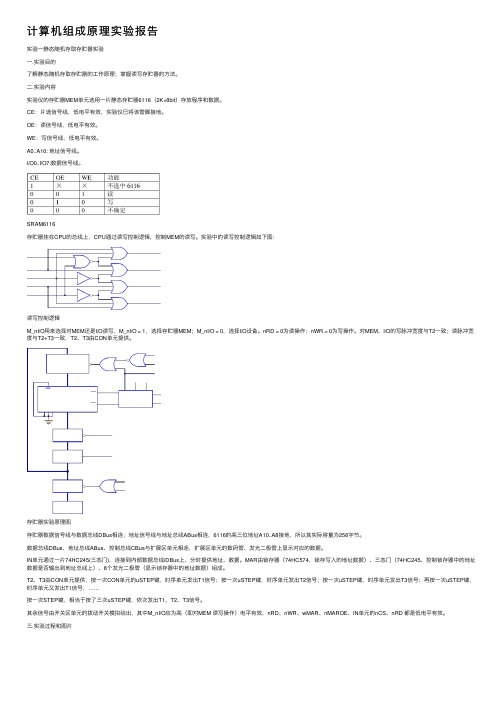

计算机组成原理实验报告实验⼀静态随机存取存贮器实验⼀.实验⽬的了解静态随机存取存贮器的⼯作原理;掌握读写存贮器的⽅法。

⼆.实验内容实验仪的存贮器MEM单元选⽤⼀⽚静态存贮器6116(2K×8bit)存放程序和数据。

CE:⽚选信号线,低电平有效,实验仪已将该管脚接地。

OE:读信号线,低电平有效。

WE:写信号线,低电平有效。

A0..A10: 地址信号线。

I/O0..I/O7:数据信号线。

SRAM6116存贮器挂在CPU的总线上,CPU通过读写控制逻辑,控制MEM的读写。

实验中的读写控制逻辑如下图:读写控制逻辑M_nI/O⽤来选择对MEM还是I/O读写,M_nI/O = 1,选择存贮器MEM;M_nI/O = 0,选择I/O设备。

nRD = 0为读操作;nWR = 0为写操作。

对MEM、I/O的写脉冲宽度与T2⼀致;读脉冲宽度与T2+T3⼀致,T2、T3由CON单元提供。

存贮器实验原理图存贮器数据信号线与数据总线DBus相连;地址信号线与地址总线ABus相连,6116的⾼三位地址A10..A8接地,所以其实际容量为256字节。

数据总线DBus、地址总线ABus、控制总线CBus与扩展区单元相连,扩展区单元的数码管、发光⼆极管上显⽰对应的数据。

IN单元通过⼀⽚74HC245(三态门),连接到内部数据总线iDBus上,分时提供地址、数据。

MAR由锁存器(74HC574,锁存写⼊的地址数据)、三态门(74HC245、控制锁存器中的地址数据是否输出到地址总线上)、8个发光⼆极管(显⽰锁存器中的地址数据)组成。

T2、T3由CON单元提供,按⼀次CON单元的uSTEP键,时序单元发出T1信号;按⼀次uSTEP键,时序单元发出T2信号;按⼀次uSTEP键,时序单元发出T3信号;再按⼀次uSTEP键,时序单元⼜发出T1信号,……按⼀次STEP键,相当于按了三次uSTEP键,依次发出T1、T2、T3信号。

其余信号由开关区单元的拨动开关模拟给出,其中M_nI/O应为⾼(即对MEM 读写操作)电平有效,nRD、nWR、wMAR、nMAROE、IN单元的nCS、nRD 都是低电平有效。

计算机组成原理移位运算实验报告

计算机组成原理移位运算实验报告移位运算是计算机中非常基础的运算之一,用于将二进制数的位数进行移动。

移位运算可分为左移和右移两种,左移是将二进制数的位数向左移动,右移则是将二进制数的位数向右移动。

移位运算通常用于二进制数的乘除运算、数据压缩、程序优化等方面。

在本次实验中,我们将通过Verilog HDL 设计一个移位器,实现移位运算。

1. 实验原理和设计设计移位器需要对移位运算的原理有一定的理解。

在二进制数的移位运算中,移位的方向和位移的距离都是明确的,因此我们可以通过调整输入信号的位置,分别实现左移和右移。

具体实现方法可以采用逻辑门电路实现,也可以采用移位指令指令直接实现。

在本次实验中,我们采用逻辑门的实现方法。

移位器的设计主要分为以下几个步骤:1. 采用Verilog HDL 自定义输入端口和输出端口。

2. 采用逻辑门电路实现移位器,包括左移和右移两种方式。

3. 对移位器进行仿真调试,验证移位器的正确性。

以下是实验所采用的Verilog HDL 代码:module shifter(input [15:0] in_data,input [1:0] shift_direction,input [3:0] shift_distance,output [15:0] out_data);wire [15:0] shift_out;assign shift_out = shift_direction[0] ? (in_data << shift_distance) : (in_data >> shift_distance);assign out_data = shift_direction[1] ? (in_data << shift_distance) : (in_data >> shift_distance);endmodule代码中定义了4 个输入端口和一个输出端口,在输入端口中,`in_data` 为需要进行移位的二进制数,`shift_direction` 为移动方向(0 为右移,1 为左移),`shift_distance` 为移动的距离。

计算机组成原理实验报告

实验1 通用寄存器实验一、实验目的1.熟悉通用寄存器的数据通路。

2.了解通用寄存器的构成和运用。

二、实验要求掌握通用寄存器R3~R0的读写操作。

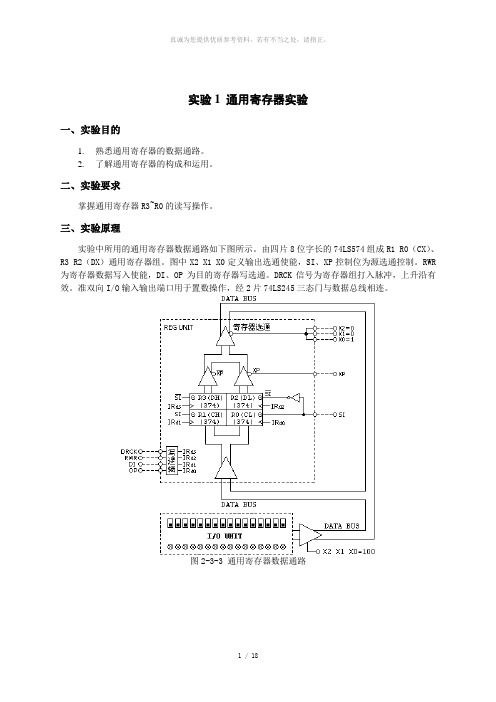

三、实验原理实验中所用的通用寄存器数据通路如下图所示。

由四片8位字长的74LS574组成R1 R0(CX)、R3 R2(DX)通用寄存器组。

图中X2 X1 X0定义输出选通使能,SI、XP控制位为源选通控制。

RWR 为寄存器数据写入使能,DI、OP为目的寄存器写选通。

DRCK信号为寄存器组打入脉冲,上升沿有效。

准双向I/O输入输出端口用于置数操作,经2片74LS245三态门与数据总线相连。

图2-3-3 通用寄存器数据通路四、实验内容1.实验连线K23~K0置“1”,灭M23~M0控位显示灯。

然后按下表要求“搭接”部件控制电路。

2.寄存器的读写操作①目的通路当RWR=0时,由DI、OP编码产生目的寄存器地址,详见下表。

通用寄存器“手动/搭接”目的编码②通用寄存器的写入通过“I/O输入输出单元”向R0、R1寄存器分别置数11h、22h,操作步骤如下:通过“I/O输入输出单元”向R2、R3寄存器分别置数33h、44h,操作步骤如下:③源通路当X2~X0=001时,由SI、XP编码产生源寄存器,详见下表。

通用寄存器“手动/搭接”源编码④通用寄存器的读出关闭写使能,令K18(RWR)=1,按下流程分别读R0、R1、R2、R3。

五、实验心得通过这个实验让我清晰的了解了通用寄存器的构成以及通用寄存器是如何运用的,并且熟悉了通用寄存器的数据通路,而且还深刻的掌握了通用寄存器R3~R0的读写操作。

实验2 运算器实验一、实验目的掌握八位运算器的数据传输格式,验证运算功能发生器及进位控制的组合功能。

二、实验要求完成算术、逻辑、移位运算实验,熟悉ALU运算控制位的运用。

三、实验原理实验中所用的运算器数据通路如图2-3-1所示。

ALU运算器由CPLD描述。

运算器的输出FUN经过74LS245三态门与数据总线相连,运算源寄存器A和暂存器B的数据输入端分别由2个74LS574锁存器锁存,锁存器的输入端与数据总线相连,准双向I/O输入输出端口用来给出参与运算的数据,经2片74LS245三态门与数据总线相连。

指导-组成原理DICE-CP226实验一至五

实验指导DICE-CP226系统概述1.1 DICE-CP226特点1、采用总线结构DICE-CP226实验系统使用三组总线即地址总线ABUS、数据总线DBUS、指令总线IBUS和控制信号,CPU、主存、外设和管理单片机等部件之间通过外部数据总线传输,CPU内部则通过内部数据总线传输信息。

各部件之间,通过三态缓冲器作接口连接。

2、计算机功能模块化设计DICE-CP2226为实验者提供运算器模块ALU,众多寄存器模块(A,W,IA ,ST,MAR,R0…R3等),程序计数器模块PC,指令部件模块IR,主存模块EM,微程序控制模块〈控存〉uM,微地址计数器模块UPC,组合逻辑控制模块及I/O等控制模块。

各模块间的电源线、地线、地址总线和数据总线等已分别连通,模块内各芯片间数据通路也已连好,各模块的控制信号及必要的输出信号已被引出到主板插孔,供实验者按自己的设计进行连接。

3、智能化控制系统在单片机监控下,管理模型机运行和读写,当模型机停机时,实验者可通过系统键盘,读写主存或控存指定单元的内容,使模型机实现在线开发。

模型机运行时,系统提供单步一条微指令(微单步)、单步一条机器指令(程单步),连续运行程序及无限止暂停等调试手段,能动态跟踪数据,流向、捕捉各种控制信息。

4、提供两种实验模式①手动运行“Hand……”:通过拨动开关和发光二极管二进制电平显示,支持最底层的手动操作方式的输入/输出和机器调试。

②自动运行:通过系统键盘及液晶显示器或PC机,直接接输入或编译装载用户程序<机器码程序和微程序>,实现微程序控制运行。

5、开放性设计运算器采用了EDA技术设计,随机出厂时,已提供一套已装载的方案,能进行加、减、与、或、带进位加、带进位减、取反、直通八种运算方式,若用户不满意该套方案,可自行重新设计并通过JTAG 口下载。

用户还可以设计自己的指令/微指令系统。

系统中已带三套指令/微程序系统,用户可参照来设计新的指令/微程序系统。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1

R-OE 右

(1) 按照下表 0 1 移门

连接线。

1

L-OE 左

1 0 移门

1

没有输

11 出

连信 接 接 号孔 入孔

作用

状态说明

J

J

将 K23-K26 接

实验模式:手

1

1 座 3 座 入 DBUS[7:0]

动

X

K

寄存器输出选

2

0

5

择

X

K

寄存器输出选

3

1

6

择

X

K

寄存器输出选

4

2

7

择

A

K

5

EN 3

分析 首先设置手动模式:按[TV/ME]键三次,进入"Hand......"手动状态。 系统清零 K23-K16 开关置零,按[RST]钮。将 55H 写入 A 寄存器,二进 制开关 K23-K16 依次置为:01010101,控制信号 K3,K2,K1,KO 依次为:0111。按住 STEP 脉冲键,CK 由高变低,这时寄存器 A 的黄色选择指示灯亮,表明选择 A 寄 存器。放开 STEP 键,CK 由低变高,产生一个上升沿,数据 55H 被写入 A

据总线 DBUS 上;观察移位门输出结果。

2、实验电路

CPTH 中有 7 个寄存器可以向数据总线输出数据,但在某一特定时刻

只能有一个寄存器输出数据,由 X2,X1,X0 决定那一个寄存器输出数据 ,

下表是 X2,X1,X0 与各个寄存器的关系表。图 8 是总线上的 7 个寄存器的

控制端原理图。

X

输出寄

寄存器。S2S1S0=111 时运算器结果为寄存器 A 内容。

CC

N y IN

L

D

R

AA

55

2A

0 X 1010 1010 0101 0101 0010 1010

010 0101 0101 0010 1010

AB

55

AA

1 1 1010 1011 0101 0101 1010 1010

置控制信号为:

按住 STEP 脉冲键,CK 由高变低,这时寄存器 A 的黄色选择指示灯亮, 表明选择 A 寄存器。放开 STEP 键,CK 由低变高,产生一个上升沿,数据

55H 被写入 A 寄存器。 S2S1S0=111 时运算器结果为寄存器 A 内容。

实验结果及分析: 结果 根据实验步骤连接好实际电路,按内容要求利用 CPTH 实验仪的 开关做为控制信号,将指定寄存器的内容读到数据总线 DBUS 上;观察移位 门输出结果。 完成结果如下图所示:

ALU 直接输出和零标志位产生原理图如图 9 所示。

图 9 ALU 直接输出和零标志位产生原理图 ALU 左移输出原理图、ALU 右移输出原理图分别如图 10 和图 11 所

示。

图 ALU 左 原理图

10 移输出

图 11 ALU 右移输出原理图 直通门将运算器的结果不移位送总线。当 X2X1X0=100 时运算器结 果通过直通门送到数据总线。同时,直通门上还有判 0 电路,当运算器的结 果 为 全 0 时 , Z=1, 右 移 门 将 运 算 器 的 结 果 右 移 一 位 送 总 线 。 当 X2X1X0=101 时运算器结果通过右通门送到数据总线。 (3)将 55H 写入 A 寄存器。 二进制开关 K23-K16 用于 DBUS[7:0]的数据输入,置数据 55H

←左移

右移→

其中移位与输出门是否打开无关,无论运算器结果如何,移位门都会

给出移位结果。

实验总结: 这 次 电 路 实 验 做 的 很 顺 利 , 根 据 实 验 步 骤 很 快 完 成 了 实 验 , 掌握 模型机中数据总线的原理;掌握运算器中移位功能的实现方法。明 白 了 理 论课程的重要性,也增加了我对模拟电路实验的兴趣喜爱,也要好好 学习计算机组成原理这门课程。

2X1X 存器

0

0

IN-OE 外

0 0 部输入门

0

IA-OE 中

0 1 断向量

0

ST-OE 堆

1 0 栈寄存器

0

PC-OEP

图8 数

据输出选择器原理图 1 1 C 寄存器

3、实验步骤

1

D-OE 直

首先设置手动模式: 0 0 通门

按 [TV/ME]键 三 次 , 进

入"Hand......"手动状态。

2 1O

色)

选通数据总线

0 0 0 IN 指示

输入门(K23-K16)

中断向量(由拨动开 0 0 1 IA 指示

关给出)

0 1 0 ST 指示

堆栈寄存器

0 1 1 PC 指示

PC 寄存器

D 直通门 100

指示

D 直通门

R 右移门 191

指示

R 右移门

L 左移门 110

指示

L 左移门

111

没有输出

(2) 移位。

选通 A

低电平有效

C

6

N

9

K 移位是否带进 位

0:不带进位 1: 带进位

C

K

7

移位进位输入

y IN 8

S

K 运算器功能选

8

2

2

择

S

K 运算器功能选

9

1

1

择

1S

K 运算器功能选

0O

0

择

1C

已

1K

连

ALU 工作脉冲

上升沿打入

(2)数据输出。 置下表的控制信号,检验输出结果。

X X X 指示灯(红

洛阳理工学院实验报告 3

系计

班

学

别 算机系 级

号

课程

计算机组成与系统结构

名称

实验 名称

数据输出/移位门

实验目的:

姓

名

实验

2015

日期

.4.27

成

绩

1、掌握模型机中数据总线的原理。

2、掌握运算器中移位功能的实现方法。

实验条件:CPTH 实验仪 实验内容:

1、实验要求

利用 CPTH 实验仪的开关做为控制信号,将指定寄存器的内容读到数