输入输出延迟单元IODELAY简介

io工作原理

io工作原理

IO(输入/输出)是计算机系统中的一种重要的技术,它负责

将数据传输到计算机的外部设备(输入)或从计算机传输数据到外部设备(输出)。

IO的工作原理可以分为输入和输出两

个步骤。

在输入过程中,计算机通过接口与外部设备连接,如键盘、鼠标或是传感器。

当用户操作这些设备时,设备会向计算机发送相应的信号。

计算机的IO控制器负责接收这些信号,并将其

转换为计算机可读取的二进制数据。

随后,这些数据会被传输到计算机的内存中,供CPU使用。

在输出过程中,计算机的CPU根据需要将数据从内存中读取

出来。

然后,CPU将这些数据传输给IO控制器。

IO控制器再将数据转换为适合外部设备的形式,并发送给相应的外部设备。

外部设备根据接收到的数据进行相应的操作,如显示、打印等。

IO的工作原理主要涉及到计算机的硬件和软件层面。

硬件层

面包括IO接口、IO控制器和外部设备等,这些元件协同工作

以完成输入输出操作。

软件层面则需要通过驱动程序来控制硬件,以实现数据的传输和处理。

总之,IO的工作原理是通过接口、控制器和外部设备等硬件

组件,配合驱动程序来实现计算机与外部设备之间的数据传输。

通过输入和输出过程,计算机可以与用户进行交互,并将数据传输到外部设备或从外部设备中获取数据。

1794各模块介绍

一、处理器整个系统中分布式I/O采用Rockwell公司生产的FlexLogix系列模块,分布式I/O系统由控制器、I/O模块、通信模块、电源、端子型I/O基座、安装导轨组成。

一个简单的FlexLogix系统可由一个控制器和最多8个模块组成。

分布式I/O系统既可作为I/O站通过控制总线由现场控制站控制;又可作为独立的分布式PLC直接控制本地I/O独立工作。

通信模块支持控制总线、现场总线、设备总线。

全部模块可带电插拔(RIUP)。

1. FlexLogix控制器模块1794-L33、1794-L34△内存:64KB;或512KB;△可同时运行8个任务,包括1个连续任务;△内置1个RS-232串口,可组态成DF1或ASCII方式;Flex Logix5433?△通过设备网可做成冗余方式;△编程软件与ControlLogix是同一软件,提高了编程效率。

二、I/O模块1.数字输入模块:1794-IB8、1794-IB16●输入点数:8点或16点;●输入电压:24VDC;●信号延时(max):256us或512us;●可拆卸端子块:1794-TB3;●具有光电隔离、状态指示功能;●具有CSA认证、UL认证、CE认证;2.数字输入模块:1794-IM8●输入点数:8点;●输入电压:220VAC;●信号延时(max):7.5ms(on),26.5ms(off);●可拆卸端子块:1794-TBN;●具有光电隔离、状态指示功能;●具有CSA认证、UL认证、CE认证;3. 数字输出模块:1794-OB8、1794-OB16●输出点数:8点或16点;●输入电压:24VDC;●输出电流:4A或8A;●输出信号延时(max):off→on=0.5ms,on→off=1.0ms;●可拆卸端子块:1794-TB3;●具有光电隔离、状态指示功能;●具有CSA认证、UL认证、CE认证;4. 开关量输出模块:1794-OW8●输出点数: 8点;●电压类型:AC/DC继电器;●输出信号延时(max):off→on=8ms,on→off=26ms;●最大开闭能力:2A/240VAC,2A/24VDC;●可拆卸端子块:1794-TBNF;●具有光电隔离、状态指示功能;●具有CSA认证、UL认证、CE认证;5.模拟输入模块:1794-IE8●输入路数:8路;●电流范围:4~20mA;●分辨率:12位;●转换速度:≤256us/路;●精度(25℃):≤0.29%满量程;●可拆卸端子块:1794-TB3;●具有光电隔离、状态指示功能;●具有CSA认证、UL认证、CE认证;6. 模拟输入模块:1794-IE12●输出路数:12路;●电流范围:4~20mA;●分辨率:16位;●转换速度:≤667us /路;●精度(25℃):≤0.1%满量程;●可拆卸端子块:1794-TB3G;●具有光电隔离、状态指示功能;●具有CSA认证、UL认证、CE认证;6. 模拟输出模块:1794-OE12●输出路数:12路;●电流范围:4~20mA;●分辨率:16位;●精度(25℃):≤0.1%满量程;●可拆卸端子块:1794-TB3G;●具有光电隔离、状态指示功能;●具有CSA认证、UL认证、CE认证;7.模拟输出模块:1794-OE4●输出路数:4路;●电流范围:4~20mA;●分辨率:12位;●转换速度:≤1.0ms/路;●精度(25℃):≤0.425%满量程;●可拆卸端子块:1794-TB3;●具有光电隔离、状态指示功能;●具有CSA认证、UL认证、CE认证;8.RTD热电阻输入模块:1794-IR8●输入路数: 8路;●分辨率:16位;●支持100Ω、200Ω、500Ω、1000Ω铂电阻,100Ω、120Ω、200Ω、500Ω镍电阻,10Ω铜电阻;●精度(25℃):≤0.05%满量程●可拆卸端子块:1794-TB3●具有光电隔离、状态指示功能;●具有CSA认证、UL认证、CE认证;9. 热电阻输入模块:1794-IT8●输入路数:8路热电偶;●支持的热电偶:B型(300℃-1800℃)、C型(0℃-2315℃)、E型(-270℃-1000℃)、J型(-210℃-1200℃)、K型(-270℃-1372℃)、N型(-270℃-1300℃)、R型(-50℃-1768℃)、S型(-50℃-1768℃)、T型(-270℃-400℃);●分辨率:16位;●系统吞吐量:325ms(1通道被扫描),编程为28ms;2.6s(8通道被扫描),编程为224ms;●冷端补偿范围:0~70℃●具有带电插拨功能;●可拆卸端子块:1794-TB3;●具有CSA、UL、CE认证;10.通讯模块a)控制网通讯模块:1788-CNCb)冗余控制网通讯模块:1788-CNCRc)设备网通讯模块:1788-DNBO●通讯速率:125Kbps/250Kbps/500Kbps●最大功耗:1.3KW●具有CSA认证、UL认证、CE认证;d)以太网通讯模块:1788-ENBT●通讯速率:10、100Mbps●功耗:2.4W●接口:RJ485●具有CSA认证、UL认证、CE认证;e)控制网适配器:1794-ACN15f)冗余控制网适配器:1794-ACNR15g)设备网适配器:1794-ANDh)以太网适配器:1794-AENTi)远程I/O适配器:1794-ASBj)扩展模块适配器:1794-FLA●本地扩展模块;●最大功耗:6.5KW;●最大背板电流:653mA●具有CSA认证、UL认证、CE认证;9.其它1. 高速计数器模块:1794-VHSC●计数数量:2个;●输入电压:5Vdc或15 24Vdc;●工作方式:计数器→最大1MHz,速度测量→最大500KHz,编码器→最大250KHz;●信号延时时间:off→on=25us,on→off=150us;●背板负载电流:0.5A@5V,1.0A@24V;●可拆卸端子块:1794-TB3G;●具有光电隔离、状态指示功能;●具有CSA认证、UL认证、CE认证;10.软件编程软件用RSLogix5000。

iic io模拟延时计算

iic io模拟延时计算(最新版)目录1.IIC 总线的概述2.IIC io 模拟延时的原理3.计算 IIC io 模拟延时的方法4.IIC io 模拟延时的应用实例5.总结正文一、IIC 总线的概述IIC(Inter-Integrated Circuit),又称为 I2C(Inter IC),是一种串行双向通信总线,它是由 Philips 公司(现在的 NXP 半导体公司)于 1980 年代研发的。

IIC 总线主要用于低速度、短距离的双向通信,特别适合于连接微处理器和外围设备,如存储器、传感器、LCD 驱动器等。

二、IIC io 模拟延时的原理在 IIC 总线通信过程中,由于信号传输和处理的时延,会产生一定的延时。

IIC io 模拟延时是指通过硬件或软件模拟的方式,在 IIC 总线上增加一定的延时,以满足通信需求。

模拟延时的原理是通过插入一定数量的时钟周期,使得数据传输过程中的时序关系得以满足。

三、计算 IIC io 模拟延时的方法计算 IIC io 模拟延时的方法通常分为两步:1.计算总线时钟周期总线时钟周期是指 IIC 总线上一个时钟周期的时间长度。

根据 IIC 总线的时钟频率和总线宽度,可以计算出总线时钟周期。

例如,如果 IIC总线的时钟频率为 1MHz,总线宽度为 3 位,那么总线时钟周期为1/1000000 秒。

2.计算延时时间延时时间是指 IIC io 模拟延时所需的时间。

根据通信协议和总线时钟周期,可以计算出延时时间。

例如,如果 IIC 协议要求数据传输时延为 3 个时钟周期,那么延时时间为 3*1/1000000 秒。

四、IIC io 模拟延时的应用实例在实际应用中,IIC io 模拟延时可以用于测试和调试 IIC 总线通信系统。

通过模拟延时,可以观察通信系统在不同延时时间的工作状态,从而找出最佳的延时参数。

此外,IIC io 模拟延时还可以用于解决通信冲突和保证数据传输的可靠性。

xilinxFPGASelectIO模块

5.1.6 SelectIO模块Virtex-6每个I/O片(I/O Tile)包含两个IOB、两个ILOGIC、两个OLOGIC 和两个IODELAY,如图5-24 所示。

图5-24 I/O 片结构图本小节就以下几个方面介绍Virtex-6 的SelectIO 资源。

(1) SelectIO 的电气特性。

(2) SelectIO 的逻辑资源——ILOGIC 资源和OLOGIC 资源。

(3) SelectIO 的高级逻辑资源——ISERDES 资源、OSERDES 资源和Bitslip。

一、SelectIO IO 的电气特性所有的Virtex-6 FPGA 有高性能的可配置SelectIO 驱动器与接收器,支持非常广泛的接口标准。

强大的功能SelectIO 包括输出强度和斜率的可编程控制以及使用数控阻抗(DCI)的片上终端。

IOB 包含输入、输出和三态SelectIO 驱动器。

支持单端I/O 标准(LVCMOS、HSTL、SSTL)和差分I/O 标准(LVDS、HT、LVPECL、BLVDS、差分HSTL 和SSTL)。

注意:差分输入和VREF 相关输入由VCCAUX 供电。

IOB、引脚及部逻辑的连接如图5-25 所示。

图5-25 IOB、引脚及部逻辑连接图IOB 直接连接ILOGIC/OLOGIC 对,该逻辑对包含输入和输出逻辑资源,可实现数据和三态控制。

ILOGIC和OLOGIC可分别配置为ISERDES和OSERDES。

Xilinx软件库提供了大量与I/O相关的原语,在例化这些原语时,可以指定I/O标准。

与单端I/O相关的原语包括IBUF(输入缓冲器)、IBUFG(时钟输入缓冲器)、OBUF(输出缓冲器)、OBUFT(三态输出缓冲器)和IOBUF(输入/输出缓冲器)。

与差分I/O相关的原语包括IBUFDS(输入缓冲器)、IBUFGDS (时钟输入缓冲器)、OBUFDS(输出缓冲器)、OBUFTDS(三态输出缓冲器)、IOBUFDS(输入/输出缓冲器)、IBUFDS_DIFF_OUT(输入缓冲器)和IOBUFDS_DIFF_OUT(输入/输出缓冲器)。

GW1N系列FPGA产品数据手册说明书

GW1N系列FPGA产品数据手册DS100-1.6, 2019-02-14版权所有© 2019广东高云半导体科技股份有限公司未经本公司书面许可,任何单位和个人都不得擅自摘抄、复制、翻译本文档内容的部分或全部,并不得以任何形式传播。

免责声明本文档并未授予任何知识产权的许可,并未以明示或暗示,或以禁止发言或其它方式授予任何知识产权许可。

除高云半导体在其产品的销售条款和条件中声明的责任之外,高云半导体概不承担任何法律或非法律责任。

高云半导体对高云半导体产品的销售和/或使用不作任何明示或暗示的担保,包括对产品的特定用途适用性、适销性或对任何专利权、版权或其它知识产权的侵权责任等,均不作担保。

高云半导体对文档中包含的文字、图片及其它内容的准确性和完整性不承担任何法律或非法律责任,高云半导体保留修改文档中任何内容的权利,恕不另行通知。

高云半导体不承诺对这些文档进行适时的更新。

版本信息目录目录 (i)图目录 (iv)表目录 (vi)1 关于本手册 (1)1.1 手册内容 (1)1.2 适用产品 (1)1.3 相关文档 (1)1.4 术语、缩略语 (1)1.5 技术支持与反馈 (3)2 产品概述 (4)2.1 特性概述 (4)2.2 产品信息列表 (6)2.3 封装信息列表 (7)3 结构介绍 (8)3.1 结构框图 (8)3.2 可配置功能单元 (10)3.2.1 可配置逻辑单元 (11)3.2.2 布线资源单元 (12)3.3 输入输出模块 (13)3.3.1 I/O电平标准 (14)3.3.2 真LVDS设计 (18)3.3.3 I/O逻辑 (19)3.3.4 I/O逻辑工作模式 (21)3.4 块状静态随机存储器模块 (26)3.4.1 简介 (26)3.4.2 存储器配置模式 (27)3.4.3 存储器混合数据宽度配置 (28)3.4.4 字节使能功能配置 (28)3.4.6 同步操作 (29)3.4.7 上电情况 (29)3.4.8 存储器操作模式 (29)3.4.9 B-SRAM操作模式 (33)3.4.10 时钟模式 (35)3.5 用户闪存资源(GW1N-1) (36)3.5.1 简介 (36)3.5.2 端口信号 (37)3.5.3 数据位宽选择 (38)3.5.4 操作模式 (38)3.5.5 读操作 (38)3.5.6 写操作 (39)3.6 用户闪存资源(GW1N-2/2B/4/4B/6/9) (39)3.6.1 简介 (39)3.6.2 端口信号 (40)3.6.3 操作模式 (41)3.7 数字信号处理模块 (41)3.7.1 简介 (41)3.7.2 DSP操作模式配置 (44)3.8 时钟 (44)3.8.1 全局时钟网络 (45)3.8.2 锁相环 (48)3.8.3 高速时钟 (50)3.8.4 延迟锁相环 (50)3.9 长线 (51)3.10 全局复置位 (51)3.11 编程配置 (51)3.11.1 SRAM编程 (51)3.11.2 Flash编程 (51)3.12 片内晶振 (52)4 电气特性 (54)4.1 工作条件 (54)4.2 ESD性能 (55)4.3 DC电气特性 (59)4.4 开关特性 (62)4.4.2 外部开关特性 (63)4.5 用户闪存电气特性 (65)4.5.1 DC电气特性1 (65)4.5.2 时序参数1,5,6 (66)4.5.3 操作时序图(GW1N-1) (68)4.5.4 操作时序图(GW1N-2/2B/4/4B/6/9) (69)4.6 编程接口时序标准 (70)4.6.1 JTAG模式接口时序标准 (70)4.6.2 AUTO BOOT模式接口时序标准 (71)4.6.3 SSPI模式接口时序标准 (72)4.6.4 MSPI模式接口时序标准 (74)4.6.5 DUAL BOOT模式 (75)4.6.6 CPU模式 (75)4.6.7 SERIAL模式 (75)5 器件订货信息 (76)5.1 器件命名 (76)5.2 器件封装标识 (78)图目录图3-1 GW1N-1器件结构示意图 (8)图3-2 GW1N-4器件结构示意图 (9)图3-3 CFU结构示意图 (10)图3-4 CLS中的寄存器示意图 (11)图3-5 IOB结构示意图 (13)图3-6 GW1N系列FPGA产品I/O Bank分布示意图 (14)图3-7真LVDS设计参考框图 (18)图3-8 I/O逻辑输出示意图 (19)图3-9 I/O逻辑输入示意图 (19)图3-10 IODELAY示意图 (19)图3-11 GW1N的I/O寄存器示意图 (20)图3-12 GW1N的IEM示意图 (20)图3-13普通模式下的I/O逻辑结构示意图 (21)图3-14 SDR模式下的I/O逻辑结构示意图 (22)图3-15 I/O逻辑的DDR输入示意图 (22)图3-16 I/O逻辑的DDR输出示意图 (23)图3-17 I/O逻辑的IDES4输入示意图 (23)图3-18 I/O逻辑的OSER4输出示意图 (23)图3-19 I/O逻辑的IVideo输入示意图 (24)图3-20 I/O逻辑的OVideo输出示意图 (24)图3-21 I/O逻辑的IDES8输入示意图 (24)图3-22 I/O逻辑的OSER8输出示意图 (24)图3-23 I/O逻辑的IDES10输入示意图 (25)图3-24 I/O逻辑的OSER10输出示意图 (25)图3-25 I/O逻辑的IDES16输入示意图 (25)图3-26 I/O逻辑的OSER16输出示意图 (25)图3-27单端口存储模式框图 (29)图3-28双端口存储模式框图 (30)图3-29伪双端口存储模式框图1 (32)图3-30只读模式存储框图 (33)图3-31单端口、伪双端口及双端口模式下的流水线模式 (34)图3-32独立时钟模式 (35)图3-33读写时钟模式 (36)图3-34单端口时钟模式 (36)图3-35 GW1N-1用户闪存端口信号 (37)图3-36 GW1N-4用户闪存端口信号 (40)图3-37 DSP宏单元 (42)图3-38 GW1N-1器件时钟资源 (45)图3-39 GW1N-2/2B/4/4B器件时钟资源 (45)图3-40 GCLK象限分布示意 (46)图3-41 DQCE结构示意图 (46)图3-42 DCS接口示意图 (47)图3-43 DCS Rising Edge模式下的时序示意图 (47)图3-44 DCS Falling Edge模式下的时序示意图 (47)图3-45 PLL示意图 (48)图3-46 GW1N-1 HCLK示意图 (50)图3-47 GW1N-2/2B/4 /4BHCLK示意图 (50)图3-48 GW1N的延迟锁相环示意图 (51)图4-1读操作模式 (68)图4-2写入页锁存模式 (68)图4-3清除页锁存模式 (69)图4-4高电平周期 (69)图4-5用户闪存读操作时序 (69)图4-6用户闪存编程操作时序 (70)图4-7用户闪存擦除操作时序 (70)图4-8 JTAG编程模式时序示意图 (71)图4-9重新上电时序图 (72)图4-10 RECONFIG_N触发时序图 (72)图4-11 SSPI编程模式时序图 (73)图4-12 MSPI编程模式时序示意图 (74)图5-1器件命名方法–ES (76)图5-2器件命名方法–Production (77)图5-3器件封装标识示例 (78)表目录表目录表1-1术语、缩略语 (1)表2-1产品信息列表 (6)表2-2产品封装和最大用户I/O信息、LVDS对数 (7)表3-1 CLS中寄存器模块信号说明 (11)表3-2 GW1N系列FPGA产品支持的输出I/O类型及部分可选配置 (14)表3-3 GW1N支持的输入I/O类型及部分可选配置 (17)表3-4 B-SRAM信号功能 (26)表3-5存储器配置列表 (27)表3-6双端口混合读写数据宽度配置列表 (28)表3-7伪双端口混合读写数据宽度配置列表 (28)表3-8单端口存储配置模式列表 (30)表3-9双端口存储配置模式列表 (30)表3-10伪双端口存储配置模式列表 (32)表3-11只读配置模式列表 (33)表3-12时钟模式配置列表 (35)表3-13用户闪存模块信号说明 (37)表3-14输出位宽选择 (38)表3-15输入位宽选择 (38)表3-16操作模式选择 (38)表3-17用户闪存模块信号说明 (40)表3-18用户模式真值表 (41)表3-19 DSP端口描述 (42)表3-20内部寄存器描述 (43)表3-21 PLL端口定义 (49)表3-22 GW1N-1/6/9片内晶振的输出频率选项 (52)表3-23 GW1N-2/2B/4/4B片内晶振的输出频率 (52)表4-1绝对最大范围 (54)表4-2推荐工作范围 (54)表4-3热插拔特性 (55)表目录表4-4 GW1N ESD - HBM (55)表4-5 GW1N ESD – CDM (55)表4-6推荐工作范围内的直流电气特性 (56)表4-7静态电流(Static Supply Current) (57)表4-8 I/O推荐工作条件 (59)表4-9 IOB单端DC电气特性(IOB Single‐Ended DC Electrical Characteristic) (60)表4-10 I/O差分DC电气特性(IOB Differential Electrical Characteristics) (61)表4-11 CFU 内部时序参数 (62)表4-12 B-SRAM内部时序参数 (62)表4-13 DSP内部时序参数 (62)表4-14 Gearbox内部时序参数 (63)表4-15外部开关特性 (63)表4-16片内晶振输出频率 (63)表4-17锁相环相关参数 (64)表4-18 GW1N-1器件用户闪存DC电气特性 (65)表4-19 GW1N-2/2B/4/4B/6/9器件用户闪存DC电气特性 (65)表4-20 GW1N-1器件用户闪存时序参数 (66)表4-21 GW1N-2/2B/4/4B/6/9器件用户闪存时序参数 (66)表4-22 JTAG编程模式时序参数 (71)表4-23重新上电和RECONFIG_N触发时序参数 (72)表4-24 SSPI编程模式时序参数 (73)表4-25 MSPI编程模式时序参数 (74)1关于本手册 1.1手册内容1关于本手册1.1手册内容GW1N系列FPGA产品数据手册主要包括高云半导体GW1N系列FPGA产品特性概述、产品资源信息、内部结构介绍、电气特性、编程接口时序以及器件订货信息。

GPIO

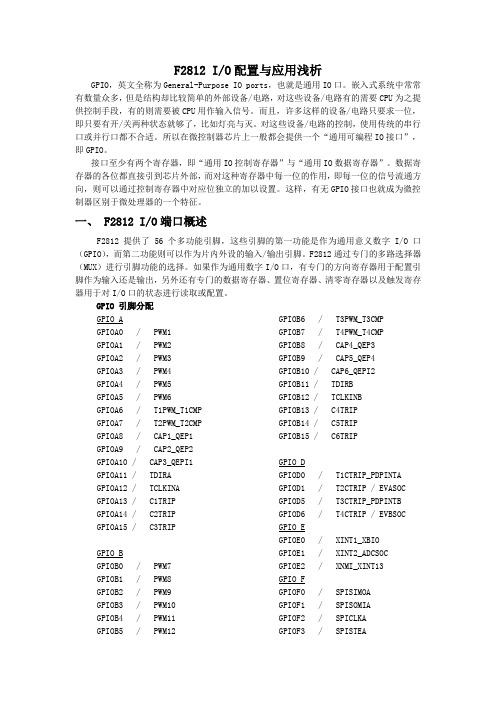

F2812 I/O配置与应用浅析GPIO,英文全称为General-Purpose IO ports,也就是通用IO口。

嵌入式系统中常常有数量众多,但是结构却比较简单的外部设备/电路,对这些设备/电路有的需要CPU为之提供控制手段,有的则需要被CPU用作输入信号。

而且,许多这样的设备/电路只要求一位,即只要有开/关两种状态就够了,比如灯亮与灭。

对这些设备/电路的控制,使用传统的串行口或并行口都不合适。

所以在微控制器芯片上一般都会提供一个“通用可编程IO接口”,即GPIO。

接口至少有两个寄存器,即“通用IO控制寄存器”与“通用IO数据寄存器”。

数据寄存器的各位都直接引到芯片外部,而对这种寄存器中每一位的作用,即每一位的信号流通方向,则可以通过控制寄存器中对应位独立的加以设置。

这样,有无GPIO接口也就成为微控制器区别于微处理器的一个特征。

一、 F2812 I/O端口概述F2812提供了56个多功能引脚,这些引脚的第一功能是作为通用意义数字I/O口(GPIO),而第二功能则可以作为片内外设的输入/输出引脚。

F2812通过专门的多路选择器(MUX)进行引脚功能的选择。

如果作为通用数字I/O口,有专门的方向寄存器用于配置引脚作为输入还是输出,另外还有专门的数据寄存器、置位寄存器、清零寄存器以及触发寄存器用于对I/O口的状态进行读取或配置。

GPIO 引脚分配GPIO AGPIOA0 / PWM1 GPIOA1 / PWM2 GPIOA2 / PWM3 GPIOA3 / PWM4 GPIOA4 / PWM5 GPIOA5 / PWM6 GPIOA6 / T1PWM_T1CMP GPIOA7 / T2PWM_T2CMP GPIOA8 / CAP1_QEP1 GPIOA9 / CAP2_QEP2 GPIOA10 / CAP3_QEPI1 GPIOA11 / TDIRA GPIOA12 / TCLKINA GPIOA13 / C1TRIP GPIOA14 / C2TRIP GPIOA15 / C3TRIPGPIO BGPIOB0 / PWM7 GPIOB1 / PWM8 GPIOB2 / PWM9 GPIOB3 / PWM10 GPIOB4 / PWM11 GPIOB5 / PWM12 GPIOB6 / T3PWM_T3CMP GPIOB7 / T4PWM_T4CMP GPIOB8 / CAP4_QEP3 GPIOB9 / CAP5_QEP4 GPIOB10 / CAP6_QEPI2 GPIOB11 / TDIRBGPIOB12 / TCLKINBGPIOB13 / C4TRIPGPIOB14 / C5TRIPGPIOB15 / C6TRIPGPIO DGPIOD0 / T1CTRIP_PDPINTA GPIOD1 / T2CTRIP / EVASOC GPIOD5 / T3CTRIP_PDPINTB GPIOD6 / T4CTRIP / EVBSOC GPIO EGPIOE0 / XINT1_XBIO GPIOE1 / XINT2_ADCSOC GPIOE2 / XNMI_XINT13 GPIO FGPIOF0 / SPISIMOAGPIOF1 / SPISOMIAGPIOF2 / SPICLKAGPIOF3 / SPISTEAGPIOF4 / SCITXDAGPIOF5 / SCIRXDAGPIOF6 / CANTXAGPIOF7 / CANRXAGPIOF8 / MCLKXAGPIOF9 / MCLKRAGPIOF10 / MFSXAGPIOF11 / MFSRAGPIOF12 / MDXAGPIOF13 / MDRAGPIOF14 / XFGPIO GGPIOG4 / SCITXDBGPIOG5 / SCIRXDBNote: GPIO are pinfunctions at reset GPIO A, B, D, E include Input Qualification feature二、GPIO寄存器控制2、1 GPxMUX寄存器通用输入输出多路选择寄存器I/O是工作在通用数字IO还是外围IO信号引脚就有GPxMUX决定。

通用输入输出(GPIO)

1.2 各种模式下的 GPIO

在 Stellaris 系列 ARM 里,GPIO 管脚可以被配置为多种工作模式,其中有 3 种比较常 用:高阻输入、推挽输出、开漏输出。

1. 高阻输入(Input)

Internal Bus Read Pulse U1

Pin

图 1.1 GPIO 高阻输入模式结构示意图

如图 1.1 所示,为 GPIO 管脚在高阻输入模式下的等效结构示意图。这是一个管脚的情 况,其它管脚的结构也是同样的。输入模式的结构比较简单,就是一个带有施密特触发输入 (Schmitt-triggered input)的三态缓冲器(U1),并具有很高的输入等效阻抗。施密特触发 输入的作用是能将缓慢变化的或者是畸变的输入脉冲信号整形成比较理想的矩形脉冲信号。 执行 GPIO 管脚读操作时,在读脉冲(Read Pulse)的作用下会把管脚(Pin)的当前电平状 态读到内部总线上(Internal Bus)。在不执行读操作时,外部管脚与内部总线之间是隔离的。

51单片机IO口工作原理

51单片机IO口工作原理51单片机(英文名为8051 Microcontroller)是一种由Intel公司于1980年推出的8位单片机,广泛应用于嵌入式系统中。

作为一种高性能、低功耗的单片机,其周围有多个IO口(Input/Output ports),可以用来实现数字输入、输出、模拟输入、输出等功能。

下面将详细介绍51单片机IO口的工作原理。

1.51单片机的IO口介绍51单片机共有4个8位的IO口,依次为P0、P1、P2和P3、每个IO 口都是一个8位的寄存器,称为端口寄存器(port register),用于和外部设备进行数据通信。

其中,P0是一个具有双重输入和输出特性的端口,可以配置为输入口或输出口;P1和P3是纯输出端口;P2是输入输出混合端口。

2.IO口的工作模式IO口的工作模式由P0、P1、P2和P3的寄存器位来配置。

每个IO口的寄存器位都有对应的功能和控制位,通过设置这些位可以控制IO口的工作模式和输出状态。

2.1输入模式在输入模式下,IO口作为输入口,接受来自外部器件的信号。

通过将对应的寄存器位设置为1,可以将IO口配置为输入模式。

在输入模式下,端口寄存器的位对应的为悬空状态,可以通过主动上拉或下拉方法来确保IO口的状态。

2.2输出模式在输出模式下,IO口作为输出口,通过控制寄存器位的值可以输出高电平或低电平信号。

将对应的寄存器位设置为0,可以将IO口配置为输出模式。

在输出模式下,直接修改端口寄存器的位即可改变IO口的输出状态。

对于纯输出端口,即P1和P3,更方便地改变IO口的状态可以通过直接操作对应的位。

2.3产生中断IO口还可以通过设置为中断产生源的方式来实现中断功能。

在输入模式下,将对应的寄存器位设置为1,即可配置IO口为中断输入。

当IO口检测到中断触发条件(例如边沿触发、电平触发等),会触发相应的中断服务程序(ISR)。

3.IO口的读取和写入操作为了读取和写入IO口的状态,可以直接访问相应的寄存器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

IODELAY 属性 表 1-5 列出了 IODELAY 的属性。

表 1-5:IODELAY 属性概述

IDELAY_TYPE 属性 IDELAY_TYPE 属性设置所用延迟的类型。此属性的值是 DEFAULT、FIXED 和

VARIABLE。当设置成 DEFAULT 时,选择零保持时间延迟单元。当在没有 DCM 的情况下 使用全局时钟采集数据(引脚到引脚参数)时,用这种延迟单元提供非正保持时间。

在活动用户数据通过 IODELAY 单元时,用户可以实时动态调整 IODELAY 的 tap 设置, 不会扰乱活动用户数据。

当在时钟信号通路中使用 IODELAY 单元时,也适用无毛刺行为。调整 tap 设置不会在 输出上引起毛刺或混乱。可以调整时钟通路中 IODELAY 单元的 tap 设置,不会扰乱可能正 在该时钟上运行的状态机。 IDELAYCTRL 概述

至此,输出已经稳定在 tap 1,因而完成了递增操作。输出无限期地保持在 tap 1,直到 RST、CE 或 INC 引脚上有进一步活动。 递增/递减操作后的稳定性

图 1-2 显示了输出从一个 tap 向另一个变化时的不稳定时段。显然,当 tap 0 处的数据值 与 tap 1 处的数据值不同时,输出必须改变状态。然而,如果 tap 0 和 tap 1 处的数据值相同 (例如两者都是 0 或 1),则从 tap 0 到 tap 1 的过渡就不会在输出上造成毛刺或混乱。这一

如果用设置为 FIXED 或 VARIABLE 的 IOBDELAY_TYPE 属性例化 IODELAY 或 ISERDES 基元,则必须在代码中例化 IDELAYCTRL 模块。IDELAYCTRL 模块在其区域内 连续标定各延迟单元(IODELAY)(见图 1-5),以减少随工艺、电压和温度变化的影响。 IDELAYCTRL 模块使用用户提供的 REFCLK 标定 IODELAY。 IDELAYCTRL 基元

当设置为 TRUE 时,此属性减少输出抖动。输出抖动减少导致 IODELAY 单元的功率 耗散略有上升。 SIGNAL_PATTERN 属性

SIGNAL_PATTERN 属性致使时序分析器计入数据或时钟通路中的相应延迟链抖动量。 IODELAY 时序

表 1-6 为 IODELAY 开关特性。

表 1-6:IODELAY 开关特性

IDELAY_VALUE 属性指定初始 tap 延迟数。可能的值是 0 到 63 之间的任意整数。默 认值是零。当 tap 延迟复位时,tap 延迟值恢复到 IDELAY_VALUE。在可变模式下,此属 性确定延迟线的初始设置。 ODELAY_VALUE 属性

ODELAY_VALUE 指定 tap 延迟数。可能的值是 0 到 63 之间的任意整数。默认值是零。 当 tap 延迟复位时,tap 延迟值恢复到 ODELAY_VALUE。 HIGH_PERFORMANCE_MODE 属性

计指导原则”。 • 可变 IDELAY(IDELAY_TYPE = VARIABLE)和固定 ODELAY 模式 在这种模式下,只有 IDELAY 值可以在配置后通过操控控制信号 CE 和 INC 来动态更

改。IODELAY 基元中 T 引脚的逻辑级别动态确定模块是 IDELAY 模式还是 ODELAY 模式。 在这种模式下使用时,必须例化 IDELAYCTRL 基元。有关更多详情,请见“IDELAYCTRL 用法及设计指导原则”。

IODELAY 复位信号 RST 将延迟单元复位到由 IDELAY_VALUE 或 ODELAY_VALUE 属性设置的值。如果未指定这些属性,则假定该值为零。RST 信号是高有效复位,与 输入时钟信号(C)同步。 表 1-3 概述了控制引脚的功能。

表 1-3:控制引脚描述

递增/递减信号– CE、INC 递增/递减由使能信号(CE)控制。当 IDELAY_TYPE = VARIABLE 时,此接口只可用

表 1-1 列出了 IODELAY 支持的配置。

表 1-1:IODELAY 支持的配置

IODELAY 基元 图 1-1 所示为 IODELAY 基元。

图 1-1:IODELAY 基元

表 1-2 列出了 IODELAY 基元中的可用端口。所有端口均为 1 位宽。

表 1-2:IODELAY 基元端口

IODELAY 端口 来自 IOB 的数据输入-IDATAIN

图 1-2 所示为 IDELAY 时序图。假设 IDELAY_VALUE = 0。

图 1-2:IDELAY 时序图

时钟事件 1 在 C 的上升沿上检测到复位,致使输出 O 选择 tap 0 为 64 tap 链的输出(假设

IDELAY_VALUE = 0)。 时钟事件 2

在 C 的上升沿上检测到 CE 和 INC 的脉冲。这说明是递增操作。输出从 tap 0 到 tap 1 无毛刺变化。请见“递增/递减操作后的稳定性”。 时钟事件 3

1、当用作 IDELAY 时,数据从 IBUF 或内部资源输入,然后输出到 ILOGIC/ISERDES。 有三种可用操作模式:

• 零保持时间延迟模式(IDELAY_TYPE = DEFAULT) 这种操作模式允许向后兼容,以使用 Virtex-II、Virtex-II Pro 和 Virtex-4 器件中的零保 持时间延迟功能的设计。当在没有 DCM 的情况下使用全局时钟采集数据(引脚到引脚参数) 时,用这种延迟单元提供“非正保持时间”。在这种模式下使用时,不需要例化 IDELAYCTRL 基元。有关更多详情,请见“IDELAYCTRL 用法及设计指导原则”。 • 固定延迟模式(IDELAY_TYPE = FIXED) 在固定延迟模式下,配置时将延迟值预设置成由属性 IDELAY_VALUE 确定的 tap 数。 此值配置后不可更改。在这种模式下使用时,必须例化 IDELAYCTRL 基元。有关更多详情, 请见“IDELAYCTRL 用法及设计指导原则”。 • 可变延迟模式(IDELAY_TYPE = VARIABLE) 在可变延迟模式下,可以在配置后通过操控控制信号 CE 和 INC 来改变延迟值。在这 种模式下使用时,必须例化 IDELAYCTRL 基元。有关更多详情,请见“IDELAYCTRL 用法及设计指导原则”。 2、当用作 ODELAY 时,数据从 OLOGIC/OSERDES 输入,然后输出到 OBUF。有一种 可用操作模式: • 固定延迟输出模式 在固定延迟输出模式下,配置时将延迟值预设置成由属性 ODELAY_VALUE 确定的 tap 数。此值配置后不可更改。在这种模式下使用时,必须例化 IDELAYCTRL 基元。有关更多 详情,请见“IDELAYCTRL 用法及设计指导原则”。 3、当用作双向延迟时,将 IOB 配置成双向模式。IODELAY 交替延迟输入通路和输出 通路上的数据。有两种可用操作模式: • 固定 IDELAY(IDELAY_TYPE = FIXED)和固定 ODELAY 模式 在 这 种 模 式 下 , IDELAY 和 ODELAY 的 值 都 是 在 配 置 时 预 设 置 , 分 别 由 IDELAY_VALUE 和 ODELAY_VALUE 属性确定。此值配置后不可更改。在这种模式下使 用时,必须例化 IDELAYCTRL 基元。有关更多详情,请见“IDELAYCTRL 用法及设

IDATAIN 输 入 由 相 应 的 IOB 驱 动 。 在 IDELAY 模 式 下 , 可 以 将 数 据 驱 动 到 ILOGIC/ISERDES 模块或直接驱动到 FPGA 内部资源中,也可以通过 DATAOUT 端口 按照由 IDELAY_VALUE 设置的延迟将数据同时驱动到这二者。 来自 FPGA 内部资源的数据输入-ODATAIN ODATAIN 输入由 OLOGIC/OSERDES 驱动。在 ODELAY 模式下,ODATAIN 按照由 ODELAY_VALUE 设置的延迟驱动连接到 IOB 的 DATAOUT 端口。 来自 FPGA 内部资源的 IODELAY 的数据输入-DATAIN DATAIN 输入直接由 FPGA 内部资源驱动,以提供一条可访问内部资源逻辑的延迟线。 数据按照由 IDELAY_VALUE 设置的延迟通过 DATAOUT 端口返回到内部资源中。 DATAIN 可以在芯片内反转。数据不能驱动到 IOB。 数据输出-DATAOUT 来自三个数据输入端口的延迟数据。DATAOUT 连接到内部资源(IDELAY 模式)或 IOB(ODELAY 模式),或同时连接到这二者(双向延迟模式)。如果在双向延迟模 式下使用,则 T 端口在 IDATAIN 和 ODATAIN 通路之间动态切换,根据来自 OLOGIC 模块的三态信号 T 所指示的方向交替提供输入/输入延迟。 三态输入-T 这是三态输入控制端口。对于双向操作,T 引脚信号还控制 OBUFT 的 T 引脚。 时钟输入-C 对 IODELAY 基元的所有控制输入(RST、CE 和 INC)均与时钟输入(C)同步。当 I ODELAY 配置成可变模式时,必须将一个时钟连接到此端口。C 可以在芯片内反转。 模块复位-RST

于 IDELAY 模式。 只要 CE 保持为 High,IDELAY 就会每时钟(C)周期按 IDELAYRESOLUTION 递增

或递减。INC 的状态确定 IDELAY 是递增还是递减:INC = 1 为递增,INC = 0 为递减,与 时钟(C)同步。如果 CE 为 Low,则通过 IDELAY 的延迟不变,与 INC 的状态无关。

当 CE 转为 High 时,在下一个时钟上升沿上开始递增/递减操作。当 CE 转为 Low 时, 在下一个时钟上升沿上停止递增/递减操作。

IODELAY 是环绕可编程延迟单元。当达到延迟单元的末尾(tap 63)时,随后的递增 功能就会返回到 tap0。同样的规则也适用于递减功能,即低于零的递减会转到 tap 63。表 1-4 概述了递增/递减操作。

概念可以通过设想 IODELAY 的 tap 链中的接收器数据信号来理解。如果 tap 0 和 tap1 都靠 近接收器数据眼的中心,则在 tap 0 处采样的数据应与在 tap 1 处采样的数据没有区别。在这 种情况下,从 tap 0 到 tap 1 的过渡不会引起输出变化。为了确保这种情况,IODELAY 的递 增/递减操作设计成了无毛刺操作。