Cadence基于CIS的模块复用

Allegro软件设计PCB时的模块和复用问题

使用Cadense公司的ORCAD和Allegro软件设计PCB时的模块和复用问题PCB的模块化设计,可能通常我们的工程师还用得不多,但它在某些场合下还是很有用的,一个是它能减少我们重复性的工作,可以重用的原理图和PCB我们就不需要重复设计了,也就是REUSE。

还有就是它能让我们设计的电路板整齐化一。

还有也减少了设计中重复的检查工作。

但有时有些工程师在使用Cadense的ORCAD和ALLegro这套工具来设计时会遇到一些问题,有时会让人望而却步,“这么麻烦,还是用笨办法吧!”。

在这里贡献我在使用中的体会,相信对大家会很有帮助。

我们在设计电路板时,经常会遇到一些重复的电路,比如,一块电话交换机用户板卡,可能会有8路16路会更多,如果我们重复做,会浪费我们大量的时间,如果用模块化的设计就会简单多了。

在一个电路中会有重复的部分也有不重复的或公共的部分。

我们在设计时可以将重复的部分,制做成模块。

模块化设计可以分为原理图的模块化和PCB设计的模块化,最好的设计当然是都模块化和重用(Reuse)了。

另外还有器件的多个相同部分的模块化和复用,一个Package分成几个相同或近似的Part。

如何在Orcad和Allegro下实现完整的模块化设计呢?让我慢慢说来。

我先说Orcad的原理图设计。

Orcad在设计时分了几个层次。

多个器件(Part)可以放置在一个页(Page)中,器件的管脚可以用连线(wire)连接起来。

几个页可以组成一个Schematic,页与页之间是用Off-page connector建立连接关系。

一个Schematic可形成一个Hierarchical Block或Hierarchical Port。

Block之间是依靠各个Block的Port来建立连接关系。

几个Schematic又组成了Design,Design与前面的一个区别是它可以一个文件的形式存在,并可生成网络表(NetList),多个Schematic时,有一个Schematic为Root。

Cadence SPB Capture CIS配置本地元器件数据库

如何在Capture CIS配置本地元器件数据库每个工程师在做原理图后,都要生成BOM,以方便焊版调试或生产使用。

传统的方法就是一个一个零件输入核对,此方法累人且效率低。

Capture CIS可以提供这个强大的功能,很方便的在做原理图的同时,即可利用元器件数据库的信息来设定元器件的所有需要的参数。

这样可以定制你自己的元器件数据库。

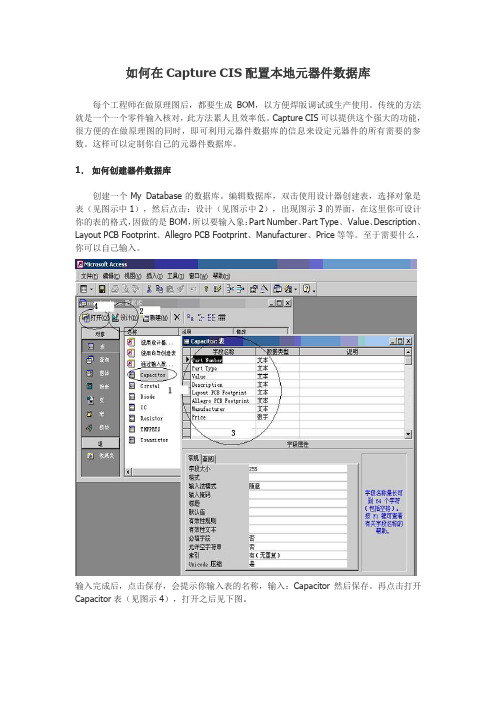

1.如何创建器件数据库创建一个My Database的数据库。

编辑数据库,双击使用设计器创建表,选择对象是表(见图示中1),然后点击:设计(见图示中2),出现图示3的界面,在这里你可设计你的表的格式,因做的是BOM,所以要输入象:Part Number、Part Type、Value、Description、Layout PCB Footprint、Allegro PCB Footprint、Manufacturer、Price等等。

至于需要什么,你可以自己输入。

输入完成后,点击保存,会提示你输入表的名称,输入:Capacitor然后保存。

再点击打开Capacitor表(见图示4),打开之后见下图。

在表格中你输入每个零件参数的详细资料,最后保存即可。

2.如何配置ODBC数据源你找到控制面板下的管理工具,里面有个数据源(ODBC),双击打开如下图界面:用户DSN和系统DSN是有区别,如果在用户DSN下创建的数据库,那么所创建的数据库只用被当前用户所使用,其他的用户不能使用。

我们选择在系统DSN下创建数据库,点击:添加,弹出下图。

选择你想要的数据源驱动程序。

选择如图所示,点击完成后。

弹出定义数据源名称,见下图。

数据源名输入:My Database,说明文字你可以写也可以不写。

然后点击选择,找到你创建的数据库文件,最后点击确定,完成数据源配置。

3.如何配置CIS文件打开Capture CIS, 见下图。

点击菜单Options/CIS Configuration…然后弹出下图,点击:New,建立一个新的CIS配置文件。

Cadence使用

第二章 Cadence的原理图设计2.1Design Entry CIS软件概述Cadence软件系统有两套电路原理图的设计工具,一套是Design Entry HDL,另一套就是我们马上要开始学习的Design Entry CIS。

其中Design Entry HDL 是Cadence公司原本的原理图设计软件,可以用于芯片电路和板级电路的设计,其长处在于可以把芯片的电路原理图和板级电路原理图结合在一起,进行综合设计;而Design Entry CIS主要用于常规的板级电路设计2.2初识Design Entry CIS一.启动Design Entry CIS我们在电脑上点击“开始→所有程序→Cadence SPB 16.2→Design Entry CIS”,如下图所示:图2-1 启动Design Entry CIS这时将弹出如下对话框:图2-2 选择工作内容在这里我们选择“OrCAD Capture CIS”一项,点击“OK”按钮后,就实际启动了Design Entry CIS,出现如下界面:图2-3 OrCAD Capture CIS软件界面OrCAD Capture CIS软件也是以项目方式管理我们的设计文件的。

在OrCAD Capture CIS软件中,一个项目可以包含若干个设计,每个设计对应一个PCB板,所以一个项目通常对应一个由多块电路板构成的产品;而每个设计可以由若干张原理图构成。

STC系列单片机下载器该产品只包含一块电路板,只有一张原理图。

我们将首先要新建一个项目:在窗体上点击“File→New→Project”出现如下对话框:图2-4 新建项目在“Name”中输入项目名称,“Location”中输入项目文件的存放位置(最好给每一个项目建立一个文件夹,把项目中的所有文件都放入该文件夹),在“Create a New Project Using”栏目中,选择“Schematic”(因为我们要进行电路原理图的设计)。

Altium Designer之相同模块复用

Altium Designer之相同模块复用

1. 首先要有至少两个完全相同的模块。

原理图和PCB封装都需要一致。

2.在PCB中先布局好其中一个模块,然后在打开交互式布局模式,在原理图里选中已经布局好的一个模块。

(快捷键T+S)

回到PCB界面,点击右下角PCB按钮,然后再选择PCB list

3.在PCB list窗口下面分别把三个选项分别设为“edit”,“selected objects”,“Components”.然后可以看到PCB list中只显示一个模块的器件。

首先,我们在name一栏点击一下让器件按位号排序。

然后再复制Channel offset一列的编号。

4.同样的方法,选中还没布局的一个模块,按照同样的位号排序顺序排列好。

然后把刚才复制的Channel offset编号粘贴到本模块的Channel offset.

5.完成通道号复制后,放置两个ROOM。

一个覆盖在已经完成布局的模块上,另一个放在空白处备用。

随后按顺序先点击已经布局好的模块的Room、空白的Room。

跳出来的窗口不用理会,直接点OK。

7.点完OK之后还会有一个小窗口弹出,直接关掉。

这时候可以看到另一个功能模块被移动到了空白的Room里,而且布局和另一个模块完全相同。

Cadence 设计中的模块应用

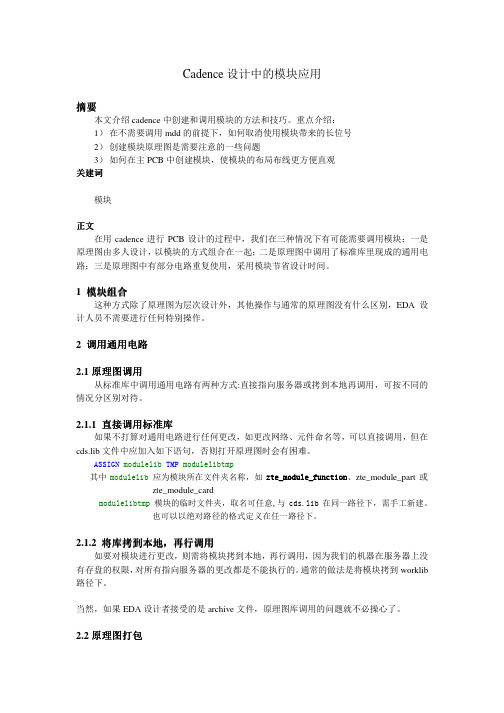

Cadence设计中的模块应用摘要本文介绍cadence中创建和调用模块的方法和技巧。

重点介绍:1)在不需要调用mdd的前提下,如何取消使用模块带来的长位号2)创建模块原理图是需要注意的一些问题3)如何在主PCB中创建模块,使模块的布局布线更方便直观关建词模块正文在用cadence进行PCB设计的过程中,我们在三种情况下有可能需要调用模块:一是原理图由多人设计,以模块的方式组合在一起;二是原理图中调用了标准库里现成的通用电路;三是原理图中有部分电路重复使用,采用模块节省设计时间。

1 模块组合这种方式除了原理图为层次设计外,其他操作与通常的原理图没有什么区别,EDA设计人员不需要进行任何特别操作。

2 调用通用电路2.1原理图调用从标准库中调用通用电路有两种方式:直接指向服务器或拷到本地再调用,可按不同的情况分区别对待。

2.1.1 直接调用标准库如果不打算对通用电路进行任何更改,如更改网络、元件命名等,可以直接调用,但在cds.lib文件中应加入如下语句,否则打开原理图时会有困难。

ASSIGN modulelib TMP modulelibtmpzte_module_function、zte_module_part或其中modulelib应为模块所在文件夹名称,如zte_module_functionzte_module_cardmodulelibtmp模块的临时文件夹,取名可任意,与cds.lib在同一路径下,需手工新建。

也可以以绝对路径的格式定义在任一路径下。

将库拷到本地,,再行调用2.1.2 将库拷到本地如要对模块进行更改,则需将模块拷到本地,再行调用,因为我们的机器在服务器上没有存盘的权限,对所有指向服务器的更改都是不能执行的。

通常的做法是将模块拷到worklib 路径下。

当然,如果EDA设计者接受的是archive文件,原理图库调用的问题就不必操心了。

2.2原理图打包EDA设计者一般只进行主原理图的打包。

allegro 模块复用

在你遇到如上图所示的dsp阵列PCB时,如果你的layout软件支持模块复用,你会感觉到自己的心里比吃了蜜还要甜!下图是老牛的memory模块复用。

下面的复用内容来自网络,按照这个说明可以实现模块复用。

本人正在按照这个方法进行尝试,后续会写出带图的详细设计。

show下本人的复用电路:=============================================================================== ====module生成1、在orcad中画好模块的原理图,设定好封装,做好drc,做好元件编号。

2、检查元件属性是否设为current properties,其它设定可能出错。

3、在annotate-->allegro reuse中,选中generate reuse module,renumber design for usingmodules,选中unconditional,其它不选。

4、生成netlist.5、将netlist导入到allegro,布线,布局,若无rename等需要与orcad交互的动作,选tools-->creat modules生成mdd文件.mdd文件的文件名一定要定义为:DSN NAME_ROOT SCHEMATIC NAME.mdd。

DSN NAME为你定义的orcad中的dsn文件名,ROOT SCHEMATIC NAME是这个文件中的页名字。

这里若定义不对,在reuse时找不到mdd文件。

之后跳到第7步。

6、在allegro中export logic,然后在orcad中back annotate,并再次drc。

这一步很关键。

7、模块制作完成。

使用生成的模块1、在新的orcad设计中,选place-->herarhical block,reference中填入BLK?(注意,这里使用BLK是为了与原理图中的U?R?C?区别,保证BLK这个名字专用于moduel,不然在做完allegro后,rename 时,导回到orcad中出问题。

Orcad CIS 元件库使用及BOM生成

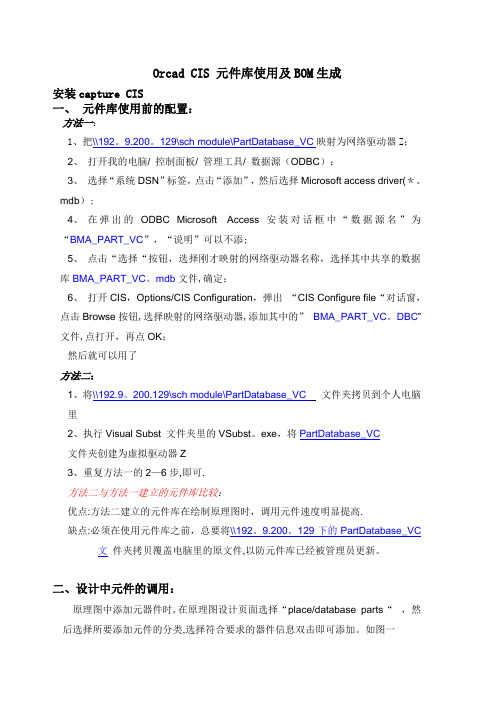

Orcad CIS 元件库使用及BOM生成安装capture CIS一、元件库使用前的配置:方法一:1、把\\192。

9.200。

129\sch module\PartDatabase_VC映射为网络驱动器Z;2、打开我的电脑/ 控制面板/ 管理工具/ 数据源(ODBC);3、选择“系统DSN”标签,点击“添加”,然后选择Microsoft access driver(*。

mdb);4、在弹出的ODBC Microsoft Access安装对话框中“数据源名”为“BMA_PART_VC”,“说明”可以不添;5、点击“选择“按钮,选择刚才映射的网络驱动器名称,选择其中共享的数据库BMA_PART_VC。

mdb文件,确定;6、打开CIS,Options/CIS Configuration,弹出“CIS Configure file“对话窗,点击Browse按钮,选择映射的网络驱动器,添加其中的”BMA_PART_VC。

DBC”文件,点打开,再点OK;然后就可以用了方法二:1、将\\192.9。

200.129\sch module\PartDatabase_VC 文件夹拷贝到个人电脑里2、执行Visual Subst 文件夹里的VSubst。

exe,将PartDatabase_VC文件夹创建为虚拟驱动器Z3、重复方法一的2—6步,即可.方法二与方法一建立的元件库比较:优点:方法二建立的元件库在绘制原理图时,调用元件速度明显提高.缺点:必须在使用元件库之前,总要将\\192。

9.200。

129下的PartDatabase_VC 文件夹拷贝覆盖电脑里的原文件,以防元件库已经被管理员更新。

二、设计中元件的调用:原理图中添加元器件时,在原理图设计页面选择“place/database parts“,然后选择所要添加元件的分类,选择符合要求的器件信息双击即可添加。

如图一图一(注:如果显示的不是绿色,则说明原件数据库中信息不全,需和管理员联系添加)三、原理图中元件链接到元件数据库原理图中的所有元件必须保证和元件数据库中的信息一一对应,才会在生成BOM 时自动调取元件数据库中的全部信息.原理图中有些元件可能是从其它地方拷贝过来的,这时需要将这些元件与元件数据库中的信息建立连接。

Cadence 16.5 Design Entry CIS层次化电路设计详解

1 orca 也会独2 (的对名复量式模块当前概述Allegro D orcad Captur 也会简化绘图Design E 独立的工程本文假定子电路设a )建立b )将默(见图1)的对象,不改c )d ) 对子○1在对话框名复位为待定点“确定○2 再次在对话框量式自动编号切换至对模块;(对当前图纸中无Cadenc (Cadeegro Design En apture 工具进化绘图工作sign Entry CIS 工程opj 文件和文假定大家对电路设计建立子电路工将默认的SCH ;Cadence 不改倒也无碍在PAGE1图纸对子电路进执行Tools->An 对话框的Pack 为待定;确定”执行标再次执行Too 对话框的Pack 动编号;换至对话框的对Renumber纸中无复用模块adence 16.5 D Cadence 软件gn Entry CIS 工具进行了多方;y CIS 的层次化文件和设计大家对Cadence 设计步骤电路工程、子电SCHEMATIC1ence 是用图纸倒也无碍,但图纸上设计子电路进行元件序>Annotate Packaging 设置执行标注任务Tools->Anno Packaging 设置话框的PCB Edito mber Design 复用模块,则不16.5 Design 软件子电路CIS 工具是Cad 了多方面演进层次化电路设计设计dsn dence 基子电路MATIC1夹来代将来出现 图设计子电路,元件序号标注ate (小细节置页下注任务,元Annotate (见图置页下B Editor Reuse ign ……项可酌选该项esign Entry C 电路复用实战笔Cadence SPB 演进;合理应路设计总体上分文件存在。

本的的平坦式图dsn 文件;图纸夹改名为电名来代表一份图会出现很1 子电路工程,外引接口标注(这步很关细节,需选到页面下选中Res 所有元件名即变见图2页面下选中Incr euse 页面,项可酌情考虑该项); ntry CIS 层次实战笔记之原ce SPB 16.5最新理的应验层次体上分为子电路坦式图纸设计;采用平坦式名为电路名(一份图纸的,多SCHEMAITC 路工程结构及接口点添加端步很关键)点选到要标注Reset part re 名即变成附有)Incremental ,选中Gener 考虑,该项对当层次化电路之原理最新推出的验层次化电路设子电路设计和纸设计已经掌握式设计的(如Blk_Tra ,这里MAITC1结构及端口添加端口名,要标注的图纸夹art referances 成附有”?”的待ental reference Generate Reus 项对当前图纸电路设计图篇 by 李雪推出的电路图设电路设计会图设计和主电路设经掌握,计的基开始k_Transceiver 改名主为貌似不是很爽口标注,定义好各元图纸夹或工程ances to “的待定rence update Reuse Module前图纸中的复用设计详解李雪雷)路图设计工具会让图纸条理电路设计两步若不懂可先初步本开始步骤;eiver ),PAGE1要是为了引用时很爽;好各元件封装工程,菜单才被?”选项,定状态;date ,设为对元odule ,允许生的复用模块重新工具,它纸条理更加清晰,子电路名不用时区(见图才被激活,设为将元件为对元件进行成可块编号,基于原加清晰,电路以学习; 不用管分引用1); 激活); 将元件进行增可复用,若F o l l o w M e !3 点“确定e )主电路设a )建立b )执行系统Refenen Implame ImplamePath and 确定”执行标最后,电路设计建立主电路工执行菜单Pla 会弹出fenence :输入plamenation Ty plamentation Nth and Filenem 执行标注任务存盘,关闭子电设计步骤 电路工程、主电Place->Hiera 模块设置对话输入模块在主ion Type :选择tion Name :eneme :输入子图注任务,元子电路工程主电路的Hierarchical B 对话框,各参块在主电路中的子电路输入子电路子电路在2 子电路元件所有元件名自路工程;路的dsn 文件cal Block 工各参数置如路中的元件名电路的方子电路中复用模所在的图3 子路元件标注对名即自动编号文件,正常绘制或工具栏设置如下:元件名,如”实现方式,选复用模块名,dsn 文件路径插入子电路示标注对话框动编号,成主电路 B?”;Schematic ,输入路名(注意浏电路示意图并生成该图纸的电路; 的图标子 matic View 图纸夹注意浏览时调图纸的复用模块插入子电路模块 名称(如Blk_Tra 览时调整文件类复用模块;路模块(见图lk_Transceiver 类型为见图3); eiver ); .dsn );F o l l o w M e !边界作多处名复refe Renu 图纸并选路块当前号动打电路3 3.1 件重对话框中框;画完结束;c )调整d )子引用(e )对主○1在对话框名复位为待定点“确定○2再次执在对话框reference upd 切换至对Renumber De 图纸中的复用中Selec 路块名(对已经是主点“确定号,且(开子电电路元件逻辑生成主电路生复、缺失话框中画完后系统调整边界把子电路(如图4对主电路进行执行Tools->An 对话框的Pack 为待定; 确定”执行标再次执行Tools 对话框的Pack update ,设为换至对话框的ber Design for U 的复用模块Select Module 对于Genera 经是主电路确定”执行对各个此时,在其子电路件有不的编号辑生电路生成成时无需缺失等错误完成设置后,系统即自动在界框形状及框中路符像元件一样);路进行元件序号>Annotate Packaging 设置执行标注任务Tools->Annota Packaging 设置设为对元件话框的PCB Ed n for Using Reu 模块重新编号odule to Mark enerate Reuse 电路啦,呵呵执行标注任务复用模块重新编如果在主电路中路查看,就会发同的编号) 成及调用 网络表特殊操作,等错误;系统边添及各的在主电图4 层次化件序号标注ate (需中置页下注任务,元nnotate (见图置页对元件进行量CB Editor Reu g Reused modu 编号,Action Mark for 中Reuse Module ); 注任务,元编号;电路中双击子电现,不 ,由于的鼠标光标框上添加子电路端口的位布在主电路中用层次化设计主标注(这步很关先选中图纸页面下选中Res 所有元件名即变见图5)面下选中Incre 行增量式自动编r Reuse 面 module ,on 选为Uncon 窗中自动dule 项可所有元件名 击子电路块不同 在标注时确变为虚十字状子电路的外引位置布局,使其中使用,参与主计主电路原理步很关键) 纸夹) Reset part re 名即变成附有 Incremental 自动编号;页面,选中请求对当前Unconditional 动出现的子电可不选,因为件名即自动编路块,系统自的引用处的子 已经确定了层次十字状态,需要外引端口及更主电路的绘路图art referances 成附有”?”的待ental ; 当前onal ,子电动编统 了层次需要接及显示美观;的绘制示例 ances to “的待定 图5 主电关系,所网接着在主电路中要素(见图,而且可拷贝?”选项,定状态; 主电路标注以在网络表中不电路中画出见图3);插入、,设为将元件标注中不会模块插入操粘贴,将元件出现元F o l l o w M e !执行Tools->Create Netlist…,系统即生成网表;应注意的是此前对子电路中元件封装属性等描述将被主电路引用时继承;3.2 网表调用在PCB Editor中执行import logic即可导入逻辑网表及元件封装(基本的PCB设置及生成操作此处不表),跟平坦时设计时相同;--------------------------------------------- The End,敬请关注PCB篇-----------------------------------!eMwolloF。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

关于allegro模块复用问题

孙海峰在使用Allegro PCB进行复杂电路设计时候,往往会遇到一部分电路被反复使用的情况,设计者可以按照之前的经验很快的做出相同的设计,但是这无疑浪费了不少时间。

尤其对于大规模复杂设计,如果设计者浪费时间在反复的工作上,这是严重的损失。

Allegro PCB允许设计者一开始就将复用模块设计好,以后只要直接调用复用模块就可以直接用以设计更复杂的电路板了。

这对于大规模集成设计无疑是非常好的选择,它不仅让设计者不必花费时间在相同模块反复设计上,更有利于电路的模块化设计和团队合作设计。

接下来我从Allegro PCB出发,详细阐述模块复用设计的具体步骤。

一、设计复用模块

首先在复杂设计之初,确定复用模块,然后对它进行设计。

复用模块的设计与普通PCB设计流程相似,包括原理图设计,DRC检查,导出网表,PCB设计和原理图反标的整个流程。

1、在Capture页面中画好复用模块的原理图,设定好元件封装,完成DRC 检查,做好元件编号等原理图设计如下图;

注意:检查元件属性是否设为current properties,其它设定可能出错。

2、对设计执行Tools/Annotate进行原理图标注,在PCB Editor Reuse选项卡中勾选Generate reuse module,Renumber design for using modules,选中Unconditional如下图。

3、执行Tools/Design Rules Check进行电路DRC检查,正确无误后执行

Tools/Create Netlist命令生成网表,并导入PCB设计中。

4、复用模块的PCB设计

在Allegro PCB Editor中对该复用模块进行设计,完成设计后执行

Tools/Create Module命令,并框选复用模块所有元件、网络、连线等信息。

然后输入坐标值,或者按Enter键即开始对该模块进行保存,这里注意模块的取名。

该复用模块文件(*.mdd)的文件名一定要定义为:DSN NAME_ROOT SCHEMATIC NAME.mdd——DSN NAME为该复用模块对应的原理图设计*.dsn文件名,ROOT SCHEMATIC NAME是该模块原理图所在页面的名称。

这里若定义不对,模块复用时找不到mdd文件。

如图按照原理图的模块设计和对应页面名称为该模块mdd文件取名。

5、模块原理图反标

在模块的PCB设计中,执行File/Export/Logic命令导出PCB设计网表,在原理图设计页面执行Tools/Back Annotate对原理图进行反标。

反标完成后,模块内的元件将添加REUSE_ID、REUSE_ANNOTATE等复用属性。

这样下来,这个模块的设计完成了,接下来在设计中就可以直接调用该模块了。

二、模块调用

上面的模块已经完成制作,然后新建原理图工程,直接可以调用模块电路进行原理图、PCB设计。

1、在新的原理图设计中,执行Place/Hierarchical Block,Reference中写入新建模块名,Implementation Type中选schematic view,Implementtation name中填入先前模块原理图设计中的页面名称,Path and filename中选择相应的原理图设计文件(*.dsn),然后在新建原理图中画出Block,然后自动形成模块对应Block如下图。

2、完成新的电路原理图设计,然后执行Tools/Annotate命令,对所有元件(包括module内元件)的标示符重新排列。

3、执行Tools/annotate命令,在PCB Editor Reuse选项卡中,选择 Renumber design for using modules,Incremental以及Select modules to mark for 栏中的模块设计;在Packaging选项卡中选择Do not change the page number,如下图所示的设置。

4、原理图DRC检查,并导出网表,将它导入PCB Editor,执行Place/Manually 命令,弹出的Placement对话框如下图所示,复用模块内的元件呈黄色,并出现M字符。

图,显示出电路中的复用模块。

5、选择Module instances中的复用模块,即可放到电路板合适的位置,也

可以通过坐标精确定位。

注意:mdd文件路径的设定,不正确会找不到mdd 文件的。

模块复用的几个注意事项:

1、当复用模块已经放在电路中使用,重新修改复用模块的port口后,在使用的原理中右击这个模块,选synchronize up,则实现修改的同步。

2、在复用模块中,不能使用room属性,不然可能与使用复用的电路图混淆。

3、复用模块中不能使用全局变量,特别是电源和地,使用port口传递数据。

4、复用模块内部修改后,只要port口没有变,则在使用它的原理图不用同步。

5、做好的模块文件用在pcb中后,若需要修改这部分文件,在修改完成后,在原pcb中使用update symbol功能,选相应的moddle,之后更新就行了,注意生成mdd文件时,原点的选择,否则更新后会出现走线错位。