中南大学大规模集成电路考试及答案合集

中南大学《计算机基础》在线考试题库(200题)(有答案)

计算机基础01一. 单选题(共40题,共100分)1. 不是Modem传输率一般标识参数的是()。

(2.5分)A.1KpbsB.14.4KpbsC.56KpbsD.9600pbs★标准答案:A2. “P4-1.7GHz/128MB/60G/40X/15"/多媒体”是某微机广告,从中可以看出此微机的内存为()。

(2.5分)A.128MBB.1.7GHzC.60GBD.40X★标准答案:A3. 微型计算机的性能主要由()决定。

(2.5分)A.CPUB.主板C.价格D.控制器★标准答案:A4. 微型计算机的总线结构是指()。

(2.5分)A.AB、DB、CB总线B.内部总线C.数据总线D.I/O总线★标准答案:A5. 下列说法中错误的是()。

(2.5分)A.指令系统有一个统一的标准,所有的计算机指令系统相同B.简单地来说,指令就是给计算机下达的一道命令C.指令是一组二进制代码,规定由计算机执行程序的操作D.为解决某一问题而设计的一系列指令就是程序★标准答案:A6. 当前使用的微型计算机,其主要元器件是由()组成的。

(2.5分)A.大规模和超大规模集成电路B.晶体管C.集成电路D.电子管★标准答案:A7. 仓库管理软件属于()。

(2.5分)A.应用软件B.工具软件C.系统软件D.字处理软件★标准答案:A8. 底部装有一个滚动小球的机械式鼠标器,在使用时()。

(2.5分)A.不需要专门的鼠标感应装置B.需要专门的鼠标感应装置C.使用方式特殊D.需要专门的电源供电★标准答案:A9. 下列关于计算机病毒的叙述中,正确的是()。

(2.5分)A.计算机病毒可以通过读写软件、光盘或Internet网络进行传播B.计算机病毒是通过电力网进行传播的C.计算机病毒只感染.exe或.com文件D.计算机病毒是由于软件片表面不清洁而造成的★标准答案:A10. 文件型病毒的主要传播对象是()。

(2.5分)A.EXE和COM文件B.EXE和PRG文件C.DBF和COM文件D.EXE和DAT文件★标准答案:A11. 扩展名为TXT的文件,下列可以与它关联的程序是()。

《超大规模集成电路设计》考试习题(含答案)完整版分析

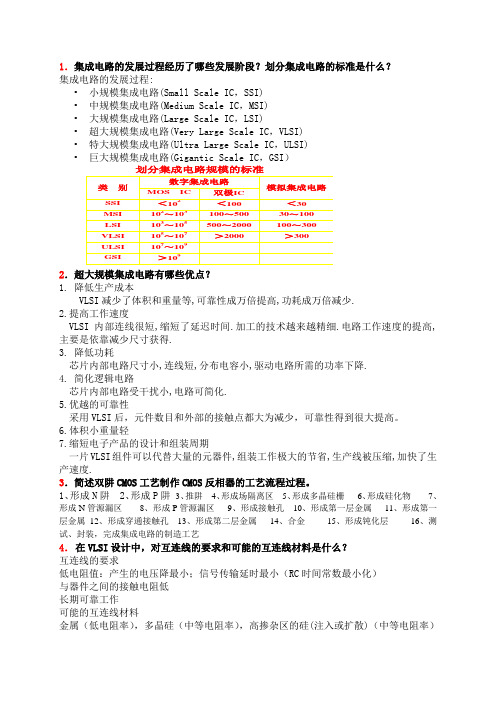

1.集成电路的发展过程经历了哪些发展阶段?划分集成电路的标准是什么?集成电路的发展过程:•小规模集成电路(Small Scale IC,SSI)•中规模集成电路(Medium Scale IC,MSI)•大规模集成电路(Large Scale IC,LSI)•超大规模集成电路(Very Large Scale IC,VLSI)•特大规模集成电路(Ultra Large Scale IC,ULSI)•巨大规模集成电路(Gigantic Scale IC,GSI)划分集成电路规模的标准2.超大规模集成电路有哪些优点?1. 降低生产成本VLSI减少了体积和重量等,可靠性成万倍提高,功耗成万倍减少.2.提高工作速度VLSI内部连线很短,缩短了延迟时间.加工的技术越来越精细.电路工作速度的提高,主要是依靠减少尺寸获得.3. 降低功耗芯片内部电路尺寸小,连线短,分布电容小,驱动电路所需的功率下降.4. 简化逻辑电路芯片内部电路受干扰小,电路可简化.5.优越的可靠性采用VLSI后,元件数目和外部的接触点都大为减少,可靠性得到很大提高。

6.体积小重量轻7.缩短电子产品的设计和组装周期一片VLSI组件可以代替大量的元器件,组装工作极大的节省,生产线被压缩,加快了生产速度.3.简述双阱CMOS工艺制作CMOS反相器的工艺流程过程。

1、形成N阱2、形成P阱3、推阱4、形成场隔离区5、形成多晶硅栅6、形成硅化物7、形成N管源漏区8、形成P管源漏区9、形成接触孔10、形成第一层金属11、形成第一层金属12、形成穿通接触孔13、形成第二层金属14、合金15、形成钝化层16、测试、封装,完成集成电路的制造工艺4.在VLSI设计中,对互连线的要求和可能的互连线材料是什么?互连线的要求低电阻值:产生的电压降最小;信号传输延时最小(RC时间常数最小化)与器件之间的接触电阻低长期可靠工作可能的互连线材料金属(低电阻率),多晶硅(中等电阻率),高掺杂区的硅(注入或扩散)(中等电阻率)5.在进行版图设计时为什么要制定版图设计规则?—片集成电路上有成千上万个晶体管和电阻等元件以及大量的连线。

中南大学数电考题全四套(含答案)

中南大学信息院《数字电子技术基础》期终考试试题(110分钟)(第一套)一、填空题:(每空1分,共15分)1.逻辑函数Y=AB+C的两种标准形式分别为()、()。

2.将2004个“1”异或起来得到的结果是()。

3.半导体存储器的结构主要包含三个部分,分别是()、()、()。

4.8位D/A转换器当输入数字量10000000为5v。

若只有最低位为高电平,则输出电压为()v;当输入为10001000,则输出电压为()v。

5.就逐次逼近型和双积分型两种A/D转换器而言,()的抗干扰能力强,()的转换速度快。

6.由555定时器构成的三种电路中,()和()是脉冲的整形电路。

7.与PAL相比,GAL器件有可编程的输出结构,它是通过对()进行编程设定其()的工作模式来实现的,而且由于采用了()的工艺结构,可以重复编程,使它的通用性很好,使用更为方便灵活。

二、根据要求作题:(共15分)1.1.将逻辑函数P=AB+AC写成与或非型表达式,并用集电极开路门来实现。

2.2.图1、2中电路均由CMOS门电路构成,写出P、Q的表达式,并画出对应A、B、C的P、Q波形。

三、分析图3所示电路,写出F1、F2的逻辑表达式,说明电路的逻辑功能。

图中所用器件是8选1数据选择器74LS151。

(10分)四、设计一位十进制数的四舍五入电路(采用8421BCD码)。

要求只设定一个输出,并画出用最简与非门实现的逻辑电路图。

(15分)五、已知电路及CP、A的波形如图5(a)(b)所示,设触发器的初态均为“0”,试画出输出端B和C的波形。

(8分)BC六、用T触发器和异或门构成的某种电路如图6(a)所示,在示波器上观察到波形如图6(b)所示。

试问该电路是如何连接的?请在原图上画出正确的连接图,并标明T的取值。

(6分)七、电路如图7所示,其中RA=RB=10kΩ,C=0.1μf,试问:1.在Uk为高电平期间,由555定时器构成的是什么电路,其输出U0的频率f0=? 2.分析由JK触发器FF1、FF2、FF3构成的计数器电路,要求:写出驱动方程和状态方程,列出状态转换表,画出完整的状态转换图;3.设Q3、Q2、Q1的初态为000,Uk所加正脉冲的宽度为T w=6/f0,脉冲过后Q3、Q2、Q1将保持在哪个状态?(共15分)八、图8所示是16*4位ROM和同步十六进制加法计数器74LS161组成的脉冲分频电路。

中南大学模电试题四套

---○---○------○---○---………… 评卷密封线 ……………… 密封线内不要答题,密封线外不准填写考生信息,违者考试成绩按0分处理 ……………… 评卷密封线 ………… 中南大学考试试卷 2011 ~2012 学年2学期 模电II 课程 时间100分钟 48 学时, 3 学分,闭卷,总分100分,占总评成绩 70 %—、填空题(10分,每空1分) 1.在本征半导体中加入__五价___元素可形成N 型半导体,加入__三价___元素可形成P 型半导体。

2.集成运放的输入级采用差动放大电路的原因是__减小温漂__。

3.对于放大电路,所谓开环是指 _无反馈通路_,而所谓闭环是指 __存在反馈通路__。

4.交流负反馈是指__在交流通路中的负反馈___。

5.为了稳定静态工作点,应引入 直流负反馈 ;为了稳定放大倍数,应引入 交流负反馈 。

6.为了获得输入电压中的低频信号,应选用 低通滤波电路。

7.功率放大电路的转换效率是指__最大输出功率与电源提供的平均功率之比_。

二、已知稳压管的稳定电压U Z =6V ,稳定电流的最小值I Zmin =5mA ,最大功耗P ZM =150mW 。

试求图所求电路中电阻R 的取值范围。

(10分) 解:稳压管的最大稳定电流 I ZM =P ZM /U Z =25mA 电阻R 的电流为I ZM ~I Zmin ,所以其取值范围为 Ω=-=k 8.136.0Z Z I ~I U U R三、电路如图所示,晶体管的β=60,r bb '=100Ω。

求解Q 点、u A 、R i 和R o ; (15分)解:Q 点:A R R U V I e b BEQ CC BQ μβ31)1(≈++-= mA I I BQ CQ 86.1≈=βV R R I V U e c EQ CC CEQ 56.4)(=+-≈ u A 、R i 和R o 的分析: Ω≈++=952mV 26)1(EQ bb'be I r r β Ω≈=952be b i r R R ∥95)(be L c -≈-=r R R A u ∥β Ω==k 3c o R R四、通用型集成运放一般由几部分电路组成?每一部分常采用哪种基本电路?通常对每一部分性能的要求分别是什么? (10分)解: 通用型集成运放通常由输入级、中间级、输出级和偏置电路等四部分组成。

武汉理工大学《超大规模集成电路设计》考试习题及答案

15.什么是可测性设计?可测性设计包括哪些技术?可测试性包括哪些 重要方面? • 在尽可能少地增加附加引线脚和附加电路, 并使芯片性能损失最小的 情况下,满足电路可控制性和可观察性的要求 • 可测性设计技术:主要包括分块测试技术、扫描测试技术、特征量分 析分块测试技术、边界扫描分块测试技术等。 测试生成、测试验证和测试设计 16.目前 VLSI 系统设计普遍采用的方法是什么?它的基本思想什么?试 列举几种设计方法。 目前 VLSI 系统设计最流行的是自顶向下(Top-Down)的结构设计. 它的基 本思想是将一个复杂系统的功能分成可以独立的简单部分,然后将各部分 拼接起来,可完成整个系统的设计,实际上就是模块化的结构设计.根据不 同要求,现有许多方法,如:全定制设计方法、半定制设计方法、定制设计 方法、可编程设计方法等。 17.半定制设计方法可分为哪几种方法?它们各自的特点和不足之处是 什么? 半定制设计方法分为门阵列法和门海法 .门阵列方法的设计特点:设计周 期短,设计成本低,适合设计适当规模、中等性能、要求设计时间短、 数 量相对较少的电路 • 不足:设计灵活性较低;门利用率低;芯片面积浪费 ;速度较低;功 耗较大。 门海法具有门利用率较高、 集成密度较大、 布线灵活和保证布线布通率等 方面的优点,并能实现存储器这类电路。但它也有不足之处,一是它仍有 布线通道, 而且增加的布线通道只能是基本单元高度内所含通道数的整倍 数,这往往使增加的通道数超过实际的需要,造成面积浪费,另一是布线 通道下的晶体管不能再用来实现逻辑,因此门的利用率仍不很高。 18.试分析提高 MOS 管工作速度方法。 1. 提高 IC 加工精度 减小沟道长度. 2. 加强 MOS 管的驱动电压 (Vgs-Vt) , 可以减小管子的内阻,加快工作速 度。 3. 由于 µn ≈ 2.5µ p ,所以 NMOS 管的工作速度比 PMOS 管快得多。 可以用 NMOS 工艺代替 PMOS 工艺。 19.画出 19.画出 CMOS 反相器电压传输特性曲线图,并写出相应的电流方程。 反相器电压传输特性曲线图,并写出相应的

中南大学EDA VerilogHDL试题(附答案)

一、填空题(10分,每小题1分)1.用EDA技术进行电子系统设计的目标是最终完成的设计与实现。

2.可编程器件分为和。

3.随着EDA技术的不断完善与成熟,的设计方法更多的被应用于Verilog HDL设计当中。

4.目前国际上较大的PLD器件制造公司有和公司。

5.完整的条件语句将产生电路,不完整的条件语句将产生电路。

6.阻塞性赋值符号为,非阻塞性赋值符号为。

二、选择题(10分,每小题2分)1.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是。

A.FPGA全称为复杂可编程逻辑器件;B.FPGA是基于乘积项结构的可编程逻辑器件;C.基于SRAM的FPGA器件,在每次上电后必须进行一次配置;D.在Altera公司生产的器件中,MAX7000系列属FPGA结构。

2.基于EDA软件的FPGA / CPLD设计流程为:原理图/HDL文本输入→综合→_____→→适配→编程下载→硬件测试。

正确的是。

①功能仿真②时序仿真③逻辑综合④配置⑤分配管脚A.③①B.①⑤C.④⑤D.④②3.子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行速度(即速度优化);指出下列哪些方法是面积优化。

①流水线设计②资源共享③逻辑优化④串行化⑤寄存器配平⑥关键路径法A.①③⑤B.②③④C.②⑤⑥D.①④⑥4.下列标识符中,__________是不合法的标识符。

A.9moon B.State0 C.Not_Ack_0 D.signall5.下列语句中,不属于并行语句的是:_______A.过程语句B.assign语句C.元件例化语句D.case语句三、EDA名词解释(10分)写出下列缩写的中文含义:ASIC:RTL:FPGA:SOPC:CPLD:LPM:EDA:IEEE:IP:ISP:四、简答题(10分)1、简要说明仿真时阻塞赋值与非阻塞赋值的区别(本题4分)。

答:非阻塞(non-blocking)赋值方式 ( b<= a):b的值被赋成新值a的操作, 并不是立刻完成的,而是在块结束时才完成;块内的多条赋值语句在块结束时同时赋值;硬件有对应的电路。

集成电路设计岗位招聘笔试题及解答(某世界500强集团)2024年

2024年招聘集成电路设计岗位笔试题及解答(某世界500强集团)(答案在后面)一、单项选择题(本大题有10小题,每小题2分,共20分)1、下列晶体管类型的半导体材料中,通常用于集成电路制造中的集电极,其来源最为广泛且成本较低的是?A. 氮化镓 (GaN)B. 硅 (Si)C. 锗 (Ge)D. 金刚石2、在集成电路设计行业中,总线宽度是指一次可以传输的信号数量。

下列总线的有效性排列中,哪一组是可以用在8位处理器的?A. 1位或4位总线B. 4位或8位总线C. 8位或16位总线D. 4位或16位总线3、下列哪种电路拓扑结构通常用于实现高增益放大器?A.மமமமமமமமமமB. 喜欢的肯定是什么?4、CMOS工艺中,为降低漏电流和提高开关速度,通常采用什么措施?A. 增加阈值电压B. 减少阈值电压C. 降低工作电压D. 提高工作电压5.在集成电路设计中,以下哪个因素对芯片的性能有最大影响?A. 电流大小B. 电压水平C. 晶体管尺寸D. 电阻值6.在设计集成电路时,以下哪种布局方法可以最小化信号传输延迟?A. 混合布局B. 紧凑布局C. 顺序布局D. 扇形布局7、数字选数字。

在模拟到数字转换电路中,使用最多的技术是()。

A、反相放大器B、运算放大器C、二极管放大器D、集成运放放大器8、数字选数字。

双极型晶体管在半导体工艺中,通常使用()掺杂技术。

A、P区掺杂B、N区掺杂C、平面掺杂D、表面掺杂9、设一款MMIC Amplifier电路的截止频率为10GHz,其放大倍数为20dB,则该放大器在1kHz处的增益 (以分贝为单位)A.约为20dBB.约为1.2dBC.约为0dBD.约为200dB 10、下列哪种晶体管的工作原理是基于电流的控制效果?A.MOSFETB.BJTTFETD.FinFET二、多项选择题(本大题有10小题,每小题4分,共40分)1.集成电路设计中,以下哪个因素对芯片性能影响最大?A. 电流大小B. 电压频率C. 电磁干扰D. 噪声大小2.在CMOS工艺中,以下哪种器件主要用于实现逻辑非功能?A. 二极管B. 晶体管C. 互连D. 电容3、集成电路设计中,每种不同类型的门电路都有其组成形式和特性方程,其中三态门(Out,tree)电路的特性方程,下述的英文表达准确的为:() A) Out = (A!) B) Out = ( *mc*ai) C) Out = ( ) is not the right choice D)Out = 0并且向上false4、某一电路的表达式为 Out = ( * ),( ) 表示废物符号,关于此电路的描述正确的是哪些?( ) A)只要有一个输入为1,则 Out=1,其 Low电平比单输出 t 高B)当 A,B,C 三个输入都为 0 时, Out=0 C)若 C=0,无论输入为0,1均不产生 anything D)三种输入相等时,三种条件下的结果一样5、下列关于 CMOS 集成电路的描述,哪些是正确的?( )A. CMOS 电路采用互补型 MOSFET 作为开关元件B. CMOS 电路在高速工作时功耗较低C. CMOS 电路主要用于模拟信号处理D. CMOS 电路在静态功耗方面较低6、下列关于设计流程中布局規劃的描述,哪些是正确的?( )A. 布局规划直接影响到芯片的性能B. 布局规划需要考虑每一级线路的容量C. 布局规划主要关心电路的功能实现D. 布局规划阶段可以随意修改电路结构7、在数字电路设计中,以下哪些电压类型是常见的逻辑门电压()。

(完整版)集成电路设计复习题及解答

集成电路设计复习题绪论1.画出集成电路设计与制造的主要流程框架。

2.集成电路分类情况如何?集成电路设计1.层次化、结构化设计概念,集成电路设计域和设计层次2.什么是集成电路设计?集成电路设计流程。

(三个设计步骤:系统功能设计逻辑和电路设计版图设计)3.模拟电路和数字电路设计各自的特点和流程4.版图验证和检查包括哪些内容?如何实现?5.版图设计规则的概念,主要内容以及表示方法。

为什么需要指定版图设计规则?6.集成电路设计方法分类?(全定制、半定制、PLD)7.标准单元/门阵列的概念,优点/缺点,设计流程8.PLD设计方法的特点,FPGA/CPLD的概念9.试述门阵列和标准单元设计方法的概念和它们之间的异同点。

10.标准单元库中的单元的主要描述形式有哪些?分别在IC设计的什么阶段应用?11.集成电路的可测性设计是指什么?Soc设计复习题1.什么是SoC?2.SoC设计的发展趋势及面临的挑战?3.SoC设计的特点?4.SoC设计与传统的ASIC设计最大的不同是什么?5.什么是软硬件协同设计?6.常用的可测性设计方法有哪些?7. IP的基本概念和IP分类8.什么是可综合RTL代码?9.么是同步电路,什么是异步电路,各有什么特点?10.逻辑综合的概念。

11.什么是触发器的建立时间(Setup Time),试画图进行说明。

12.什么是触发器的保持时间(Hold Time),试画图进行说明。

13. 什么是验证,什么是测试,两者有何区别?14.试画图简要说明扫描测试原理。

绪论1、 画出集成电路设计与制造的主要流程框架。

2、集成电路分类情况如何?集成电路设计1. 层次化、结构化设计概念,集成电路设计域和设计层次分层分级设计和模块化设计.将一个复杂的集成电路系统的设计问题分解为复杂性较低的设计级别,⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎩⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎨⎧⎪⎪⎪⎪⎩⎪⎪⎪⎪⎨⎧⎩⎨⎧⎩⎨⎧⎪⎪⎪⎪⎩⎪⎪⎪⎪⎨⎧⎪⎪⎪⎪⎪⎪⎩⎪⎪⎪⎪⎪⎪⎨⎧⎩⎨⎧⎪⎪⎪⎪⎩⎪⎪⎪⎪⎨⎧⎩⎨⎧⎪⎩⎪⎨⎧按应用领域分类数字模拟混合电路非线性电路线性电路模拟电路时序逻辑电路组合逻辑电路数字电路按功能分类GSI ULSI VLSI LSI MSI SSI 按规模分类薄膜混合集成电路厚膜混合集成电路混合集成电路B iCMOS B iMOS 型B iMOS CMOS NMOS PMOS 型MOS双极型单片集成电路按结构分类集成电路这个级别可以再分解到复杂性更低的设计级别;这样的分解一直继续到使最终的设计级别的复杂性足够低,也就是说,能相当容易地由这一级设计出的单元逐级组织起复杂的系统。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

中南大学大规模集成电路考试及答案合集————————————————————————————————作者:————————————————————————————————日期:---○---○--- 学 院专业班级学 号姓 名………… 评卷密封线 ……………… 密封线内不要答题,密封线外不准填写考生信息,违者考试成绩按0分处理 ……………… 评卷密封中南大学考试试卷 时间110分钟题 号一 二 三 合 计得 分评卷人2013 ~2014 学年一学期大规模集成电路设计课程试题 32学时,开卷,总分100分,占总评成绩70 %一、填空题(本题40分,每个空格1分)1. 所谓集成电路,是指采用 ,把一个电路中所需的二极管、 、电阻、电容和电感等元件连同它们之间的电气连线在一块或几块很小的 或介质基片上一同制作出来,形成完整电路,然后 在一个管壳内,成为具有特定电路功能的微型结构。

2. 请写出以下与集成电路相关的专业术语缩写的英文全称:ASIC : ASSP : LSI : 3. 同时减小 、 与 ,可在保持漏源间电流不变的前提下减小器件面积,提高电路集成度。

因此,缩短MOSFET 尺寸是VLSI 发展的趋势。

4. 大规模集成电路的设计流程包括:需求分析、 设计、体系结构设计、功能设计、 设计、可测性设计、 设计等。

5. 需求规格详细描述系统顾客或用户所关心的内容,包括 及必须满足的 。

系统规格定义系统边界及系统与环境相互作用的信息,在这个规格中,系统以 的方式体现出来。

6. 根据硬件化的目的(高性能化、小型化、低功耗化、降低成本、知识产权保护等)、系统规模/性能、 、 、 等确定实现方法。

7. 体系结构设计的三要素为: 、 、 。

8. 高位综合是指从 描述自动生成 描述的过程。

与人工设计相比,高位综合不仅可以尽可能地缩短 ,而且可以生成在面积、性能、功耗等方面表现出色的电路。

9. 逻辑综合就是将 变换为 ,根据 或 进行最优化,并进行特定工艺单元库 的过程。

10. 逻辑综合在推断RTL 部品时,将值的变化通过时钟触发的信号推断为 ,得 分评卷人下生成‘Z ’的信号推断为 ,将其它的推断为 。

11. 构造化法是目前可测性设计的主要方法,可以细分为: 法、边界扫描测试法、 法、静止电源电流法。

12. 布局布线的步骤分为: 、电源布线、 、时钟布线、 等。

13. 为了进行时序验证、功耗验证、信号完整性验证及电子迁移性验证,需要从版图结果中提取 。

二、选择题(可多选,每题2分,合计40分)1. 集成电路进入纳米尺寸时代后,将面临以下主要挑战: ( ) A. 漏电流增大导致总功耗增加; B. 栅极氧化膜厚度接近物理极限;C. 电路规模增大导致动态功耗增加;D. 配线延迟不能相应降低从而影响性能;2. 以下哪几项是集成电路制作工艺的?( )A. SOP;B. BCD;C. BMOS;D. CMOS;E. BiMOS;F. BCG 3. MOSFET 的温度特性体现为:( )A. 温度升高,载流子迁移率升高,跨导升高,阀值电压升高;B. 温度升高,载流子迁移率升高,跨导下降,阀值电压下降;C. 温度升高,载流子迁移率下降,跨导下降,阀值电压升高;D. 温度升高,载流子迁移率下降,跨导下降,阀值电压下降; 4. 关于CMOS 反相器,以下描述中哪些是正确的?( )A. V tn ≤ V i ≤ ½ V dd ,NMOS 导通,等效于电流源,PMOS 等效于非线性电阻;B. V i ≈ ½ V dd ,NMOS 和PMOS 都处于饱和区,等效于非线性电阻;C. V dd /2 ≤ V i ≤ V dd /2 +V tp , PMOS 导通,等效于电流源,NMOS 等效于非线性电阻;D. V i ≥ V dd +V tp ,NMOS 导通,PMOS 截止;5. 以下哪些描述符合通用性设计七原则?( )A. 无论使用者的经验、文化水平、语言技能、使用时的注意力集中程度如何,都能容易地理解设计物的使用方式。

B. 设计物对于不同能力的人们来说都是有用而适合的。

C. 提供合适的尺度和空间以便于接近、到达、操控和使用,无论使用者的生理尺寸、体态和动态。

D. 设计物应该降低由于偶然动作和失误而产生的危害及负面后果。

得分评卷人6. 以下哪些为微处理器IP必须具备的功能?( )A. Fetch;B. Decode;C. Execute;D. Encode;E. Writeback;pile;7. 以下关于设计抽象度的描述中,哪些是正确的?( )A. 算法级描述决定系统的实施方式(体系结构、算法);B. 门级描述是基于基本元件(AND/OR/NOT/FF等)的电路设计;C. 门级描述决定硬件的处理方式(数据电路与控制电路);D. RTL描述包括时钟级的时序设计;8. 以下描述比较不同抽象度设计的仿真速度,哪些是正确的?( )A. 算法级>门级>RTL级;B. RTL级>门级>算法级;C. 门级>算法级>RTL级;D. 算法级>RTL级>门级;9. 以下关于逻辑综合的描述,哪些是正确的? ( )A. 逻辑综合的结果是唯一的;B. 逻辑综合技术可分为生成顺序电路和生成组合电路两类;C. 布尔逻辑公式的简化一般与制造工艺无关。

D. 同一逻辑可以由多种电路实现,逻辑综合则选择与面积、延迟时间、功耗等要求最接近的电路。

10. 以下问题描述中,哪些有可能通过可测性设计发现? ( )A. 制造误差;B. 性能问题;C. 制造故障; D. 功能未满足顾客的需求;11. 以下关于可测性设计的描述中,哪些是正确的? ( )A. 可测性设计就是在设计阶段考虑测试因素,牺牲一部分芯片面积换得测试的容易化;B. 可测性设计使用自动生成工具(ATPG),易于生成故障覆盖率高的测试模式。

C. 可测性设计由于增加了设计负荷,将一定导致芯片整体开发成本的增加。

D. 可观察性与可控制性是衡量可测性设计的两个尺度。

12. 以下描述与可测性设计的设计制约相关,哪些是正确的?()A. 禁止使用循环组合电路;B. FF的时钟信号必须能够从外部端口直接控制。

C. FF的复位信号必须能够从外部端口直接控制。

D. 扫描测试时,RAM和内核需要分开进行设计。

13. 在以下关于内建自测试法的描述中,哪些是正确的? ( )A. 由于内嵌测试模式发生器,不需要额外生成测试模式;B. 由于只输出GO/NOGO,故障分析很困难;C. 由于内嵌测试输出评估部,不需要高价测试设备,可降低成本;D. 不可用于Burn-In测试;14. SOC设计采用基于IP分离的可测性设计,具体的实现手段有:()A. Distributed BIST;B.Direct Access;C. Test Bus;D.Boundary Scan;15. 以下时间因素中,会对电路最终的工作频率产生影响的有:()A. clock skew;B. 组合电路的最大延迟;C. FF的Setup时间;D. FF的Hold时间;16. 以下属于版图设计的验证科目有:()A. DRC;B. LVS;C. 时序验证;D.信号完全性17. 在以下关于布局布线算法的描述中,哪些是正确的? ( )A. 是一种高速计算近似值的算法;B. 是在实际可行的时间内计算布局布线最优解的算法;C. 是求局部最优解的算法;D. 为了让近似值接近最优解,有必要改变执行条件(初解、控制参数)多次进行重新计算;18. 在以下关于布局布线的描述中,哪些是正确的? ( )A. 布线分全局布线与详细布线两个阶段,决定布线途径;B. 当某个布线变为不可能时,确定并拆除成为其障碍物的布线群,进行重新布线,使其不再成为其它布线的障碍;C. 基于阶层的布局设计包括自顶向下的布图规划和自下向上的模块布局;D. 自顶向下的布图规划包括对阶层模块进行面积预估、确定aspect 比、放置模块及模块间时间制约的分割;19. 以下属于光刻工艺的为:( )A. 光刻胶涂覆;B. 曝光;C. 显影;D. 腐蚀; 20. 以下为封装外型的为:( )A. DIP ;B.QFP ;C. BGA ;D. CSP ;三. 以下代码描述了4位到2位的解码器模块DEC (具体见以下注释)。

请使用Verilog HDL 描述语言写出能满足下列条件的测试平台模块testbench :1.DEC 作为 testbench 的子模块,所有输入信号都由testbench 生成并供给;2.输入信号din 必须随机生成;3.必须在testbench 内部自动判定DEC 输出信号dout 正确与非;4.能够将波形保存至文件。

(20分) // decoder: dindout // 1xxx 11 // 01xx 10 // 001x 01 //000x00module DEC(clk, rstn, din, dout); input clk, rstn; input [3:0] din; output [1:0] dout; reg [1:0] dout;always@(posedge clk or negedge rstn)begin得分 评卷人if (!rstn)dout <= 2'b00;else if (din[3] == 1'b1)dout <= 2'h3;else if (din[2] == 1'b1)dout <= 2'h2;else if (din[1] == 1'b1)dout <= 2'h1;else if (din[0] == 1'b1)dout <= 2'h0;endendmodule2011-2012学年第一学期《大规模集成电路》期末考试答案一.填空题(每个空格1分,共40分)1.半导体工艺,晶体管,半导体晶片,封装。

2. ASIC:Application Specific Integrated CircuitsASSP:Application Specific Standard ProductsLSI:Large Scale Integrated Circuits3. L,t ox,W4. 系统,逻辑,版图(或软件)5.系统功能,制约,黑盒子。

6. 量产规模,弹性设计要求,开发周期。

7. 建模,探索,细化。

8. 算法级,RTL级,开发周期9. RTL描述,门电路,面积,延迟,映射10. D-FF,Latch,三状态门,组合电路11. 扫描测试法,内建自测试法12. 布图规划,布局(设计),布线(设计)13. 布线寄生参数二. 选择题(每题2分,共40分)1. A,B,D2.B,D3.D4.A,C,D5.A,B,C,D6.A,B,C,E7.A,B,D8.D9.B,C,D 10. A,C11. A,B,D 12. A,B,C,D 13. A,B,C 14.B,C,D 15. A,B,C,D16.A,B,C,D 17.A,C,D 18.A,B,C,D 19.A,B,C,D 20.A,B,C,D三、问答题(20分)答题要点包括:对大规模集成电路领域及相关产业的认识;对这门课程的讲授内容及讲解方式的看法及建议,好的可行性建议可以适当加分。