quartus 破解,7.1版本,EDA实验 电子线路课程设计

EDA技术实验讲义

E D A/S O P C技术实验讲义陕西科技大学电气与信息工程学院目录4第一章 EDA_VHDL实验/设计与电子设计竞赛4 1-1、应用QuartusII完成基本组合电路设计5 1-2. 应用QuartusII完成基本时序电路的设计6 1-3. 设计含异步清0和同步时钟使能的加法计数器7 1-4. 7段数码显示译码器设计8 1-5. 8位数码扫描显示电路设计9 1-6. 数控分频器的设计10 1-7. 32位并进/并出移位寄存器设计10 1-8. 在QuartusII中用原理图输入法设计8位全加器11 1-9. 在QuartusII中用原理图输入法设计较复杂数字系统11 1-10. 用QuartusII设计正弦信号发生器13 1-11. 8位16进制频率计设计16 1-12. 序列检测器设计16 1-13. VHDL状态机A/D采样控制电路实现18 1-14. 数据采集电路和简易存储示波器设计19 1-15. 比较器和D/A器件实现A/D转换功能的电路设计20 1-16 移位相加硬件乘法器设计24 1-17 采用流水线技术设计高速数字相关器24 1-18 线性反馈移位寄存器设计25 1-19 乐曲硬件演奏电路设计28 1-20 乒乓球游戏电路设计32 1-21 循环冗余校验(CRC)模块设计33 1-22. FPGA步进电机细分驱动控制设计(电子设计竞赛赛题)34 1-23. FPGA直流电机PWM控制实验35 1-24. VGA彩条信号显示控制器设计37 1-25. VGA图像显示控制器设计37 1-26. 清华大学学生基于GW48PK2系统VGA图像显示控制器设计示例5则38 1-27. 直接数字式频率合成器(DDS)设计实验(电子设计竞赛赛题)39 1-28. 嵌入式锁相环PLL应用实验41 1-29. 使用嵌入式锁相环的DDS设计实验(200MHz超高速DAC的PLL测试42 1-30. 基于DDS的数字移相信号发生器设计(电子设计竞赛赛题)45 1-31. 采用超高速A/D的存储示波器设计(含PLL,电子设计竞赛赛题)46 1-32. 信号采集与频谱分析电路设计(电子设计竞赛赛题)46 1-33. 等精度数字频率/相位测试仪设计实验(电子设计竞赛赛题)48 1-34. FPGA与单片机联合开发之isp单片机编程方法49 1-35. 测相仪设计(电子设计竞赛赛题)50 1-36. PS/2键盘鼠标控制电子琴模块设计50 1-37. PS/2鼠标与VGA控制显示游戏模块设计50 1-38. FPGA_单片机_PC机双向通信测频模块设计50 1-39. 10路逻辑分析仪设计(电子设计竞赛赛题)51 1-40. IP核:数控振荡器NCO应用设计52 1-41. IP核:FIR数字滤波器应用设计53 1-42. IP核:FFT应用设计53 1-43. IP核:CSC VGA至电视色制互转模块应用设计54 1-44. IP核:嵌入式逻辑分析仪SignalTapII调用55 1-45. USB与FPGA通信实验56第二章 SOPC/EDA设计实验I56 2-1 用逻辑锁定优化技术设计流水线乘法器实验57 2-2 用逻辑锁定优化技术设计16阶数字滤波器实验59 2-3 基于DSP Builder的FIR数字滤波器设计实验60 2-4 基于DSP Builder的IIR数字滤波器设计实验60 2-5 基于DSP Builder的DDS与数字移相信号发生器设计实验62 2-6 m序列伪随机序列发生器设计实验63 2-7 巴克码检出器设计实验65 2-8 RS码编码器设计实验65 2-9 正交幅度调制与解调模型设计实验67 第三章 SOPC/EDA设计实验II67 3-1 基于MATLAB/DSP Builder DSP可控正弦信号发生器设计72 3-2 32位软核嵌入式处理器系统Nios开发实验73 3-3 设计一个简单的SOPC系统74 3-4 简单测控系统串口接收程序设计74 3-5 GSM短信模块程序设计75 3-6 基于SOPC的秒表程序设计77 3-7 Nios Avalon Slave外设(PWM模块)设计78 3-8 Nios Avalon Slave外设(数码管动态扫描显示模块)设计79 3-15 DMA应用和俄罗斯方块游戏设计79第四章 SOPC/EDA设计实验III ( NiosII系统设计 ) 79 4-1、建立NIOSII嵌入式处理器硬件系统87 4-2、NIOSII软件设计与运行流程94 4-3、加入用户自定义组件设计100 4-4、加入用户自定义指令设计103 4-5、FLASH编程下载104 4-6、设计DSP处理器功能系统104 4-7、AM调制电路设计105第五章液晶接口实验105 5-1 GDM12864A液晶显示模块接口开发111 5-2 HS162-4液晶显示模块与单片机的接口114 5-3 G240-128A液晶显示模块的接口115第六章 CPU及其结构组件设计实验115 6-1 复杂指令CPU设计122 6-2 8051/89C51单片机核于FPGA中实现实验124第七章模拟EDA实验124 7-1 模拟EDA实验及其设计软件使用向导(PAC _Designer使用)124 7-2 基于ispPAC80的5阶精密低通滤波器设计126 7-3 基于ispPAC10的直流增益为9的放大器设计129附录:GW48 EDA/SOPC主系统使用说明129 第一节:GW48教学系统原理与使用介绍,132 第二节:实验电路结构图137 第三节:超高速A/D、D/A板GW-ADDA说明138 第四节:步进电机和直流电机使用说明138 第五节:SOPC适配板使用说明139 第六节:GWDVPB电子设计竞赛应用板使用说明141 第七节:GWCK/PK2/PK3系统万能接插口与结构图信号/与芯片引脚对照表第一章EDA_VHDL实验/设计与电子设计竞赛1-1. 应用QuartusII完成基本组合电路设计(1) 实验目的:熟悉QuartusⅡ的VHDL文本设计流程全过程,学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。

EDA技术与应用讲义第章第节EDA设计流程及其工具QUARTUSII快速设计指南-V1

EDA技术与应用讲义第章第节EDA设计流程及其工具QUARTUSII快速设计指南-V1EDA技术与应用讲义是关于电子设计自动化技术(EDA)的一本权威教材,其中介绍了EDA设计流程及其工具QUARTUSII的快速设计指南。

本文将重点介绍第一章第节中关于EDA设计流程及其工具QUARTUSII的内容,并提供一些快速设计指南。

一、EDA设计流程EDA设计流程是EDA设计中不可缺少的重要步骤,它主要包括如下几个步骤:1.需求分析:需求分析是整个设计流程中非常关键的一步。

在这个阶段,设计师需要了解客户需求,制定出设计目标,明确设计范围,并且向客户提供关于设计方案的报告。

2.系统级设计:在系统级设计阶段中,设计师需要通过设计文档和模块图来描述整个系统的基本框架、模块间的通信方式和模块的功能特性等。

在这一阶段需要并且经常使用的工具包括:Microsoft Office、Mindmap、XMind等。

3.算法设计与仿真:在这个阶段,设计师通过各种仿真工具对系统进行算法的仿真和验证。

在这一过程中,设计师需要熟练掌握仿真和验证工具,比如MATLAB、Verilog等。

4.电路级设计:电路级设计是EDA设计流程的重要步骤。

设计师需要在此阶段使用EDA工具来实现电路的设计,并进行SPICE仿真。

常用的工具包括SPICE仿真器、电路设计与验证工具等。

5.物理设计:在物理设计阶段中,设计师需要对电路进行物理实现和布局。

可以使用EDA工具中的Autoplacer和Autorouter等工具。

二、QUARTUSII快速设计指南QUARTUSII是EDA设计中广泛使用的FPGA开发工具,它可以从高层次的RTL代码到底层的逻辑等级进行仿真和综合,最终生成bitstream文件上传到FPGA中实现电路的设计。

QUARTUSII的快速设计指南包括:1.了解quartus ii软件:在使用QUARTUSII之前,首先需要熟悉软件的基本操作和使用流程。

EDA实验报告1组合逻辑电路的设计

学院电子系实验报告学生姓名:班级:学号:课程:EDA技术实用教程一、实验题目:组合逻辑电路的设计二、实验地点:三、实验目的:1.熟悉QuartusⅡ的VHDL文本设计流程全过程,学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。

2.加深FPGA\CPLD设计的过程,并比较原理图输入和文本输入的优劣。

四、实验内容:1.首先利用QuartusⅡ完成2选1多路选择器(如图S1-1)的文本编辑输入(mux21a.vhd)和仿真测试等步骤。

最后在实验系统上进行硬件测试,验证本项设计的功能。

图S1-12.将此多路选择器看成是一个元件mux21a,利用原理图输出法完成图s1-2,并将此文件放在同一目录中。

图s1-2编译、综合、仿真本例程,并对其仿真波形作出分析说明。

最后在实验系统上进行硬件测试,验证本项设计的功能。

3.七段数码管译码器(Decoder)七段数码管译码器(Decoder)的输入为4位二进制代码,输出为7个表征七段数码管代码的状态信号。

下面为一个七段数码管译码器的VHDL源代码模型:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY display ISPORT(A:IN STD_LOGIC_VECTOR(3 DOWNTO 0);LED7S:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END;ARCHITECTURE ONE OF display ISBEGINPROCESS(A)BEGINCASE A ISWHEN "0000"=>LED7S<="0111111";--X"3F"->0WHEN "0001"=>LED7S<="0000110";--X"06"->1WHEN "0010"=>LED7S<="1011011";--X"5B"->2WHEN "0011"=>LED7S<="1001111";--X"4F"->3WHEN "0100"=>LED7S<="1100110";--X"66"->4WHEN "0101"=>LED7S<="1101101";--X"6D"->5WHEN "0110"=>LED7S<="1111101";--X"7D"->6WHEN "0111"=>LED7S<="0000111";--X"07"->7WHEN "1000"=>LED7S<="1111111";--X"7F"->8WHEN "1001"=>LED7S<="1101111";--X"6F"->9WHEN "1010"=>LED7S<="1110111";--X"77"->10WHEN "1011"=>LED7S<="1111100";--X"7C"->11WHEN "1100"=>LED7S<="0111001";--X"39"->12WHEN "1101"=>LED7S<="1011110";--X"5E"->13WHEN "1110"=>LED7S<="1111001";--X"79"->14WHEN "1111"=>LED7S<="1110001";--X"71"->15WHEN OTHERS=>NULL;END CASE;END PROCESS;END;编译、综合、仿真本例程,并对其仿真波形作出分析说明。

EDA实验指导书全

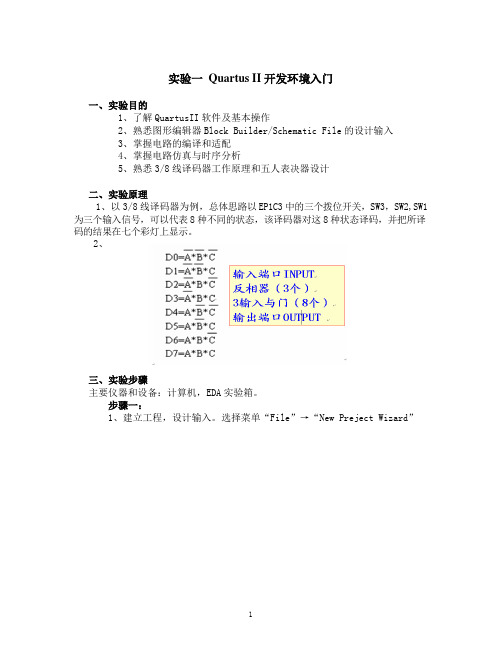

实验一Quartus II开发环境入门一、实验目的1、了解QuartusII软件及基本操作2、熟悉图形编辑器Block Builder/Schematic File的设计输入3、掌握电路的编译和适配4、掌握电路仿真与时序分析5、熟悉3/8线译码器工作原理和五人表决器设计二、实验原理1、以3/8线译码器为例,总体思路以EP1C3中的三个拨位开关,SW3,SW2,SW1为三个输入信号,可以代表8种不同的状态,该译码器对这8种状态译码,并把所译码的结果在七个彩灯上显示。

2、三、实验步骤主要仪器和设备:计算机,EDA实验箱。

步骤一:1、建立工程,设计输入。

选择菜单“File”→“New Preject Wizard”将设计文件加入工程中:点击下方的“Next” 按钮,在弹出的对话框中点击“File”栏的按钮,将此工程相关的所有VHDL文件加入进此工程(如果有的话)。

Cyclone系列的EP1C3T144C8按下“Next”后,出现仿真工具选择对话框。

不作任何选择。

4、完成设置点击“Next”后,完成工程的设定,点击“finish”。

步骤二:1、选择File/New或点击主菜单中的空白图标,进入新建程序文件状态,选择VHDL file 。

VHDL程序文件的扩展名是:* .vhd程序代码:-- A simple 3 to 8 decoderlibrary ieee;use ieee.std_logic_1164.all;entity decoder isport ( inp: in std_logic_vector(2 downto 0);outp: out std_logic_vector(7 downto 0)); end decoder;architecture behave of decoder isbeginoutp(0) <= '1' when inp = "000" else '0';outp(1) <= '1' when inp = "001" else '0';outp(2) <= '1' when inp = "010" else '0';outp(3) <= '1' when inp = "011" else '0';outp(4) <= '1' when inp = "100" else '0';outp(5) <= '1' when inp = "101" else '0';outp(6) <= '1' when inp = "110" else '0';outp(7) <= '1' when inp = "111" else '0';end behave;步骤三:1、选择菜单“File”→“New ” →“ Schematic File”,即弹出原理图编辑框。

EDA实验quartus操作流程

EDA实验quartus操作流程3.1 应⽤QuartusⅡ完成LED的驱动⼀、实验⽬的通过实验,是同学们能够逐步了解、熟悉和掌握FPGA开发软件QuartusⅡ的使⽤⽅法及VHDL语⾔的编程⽅法。

⼆、实验内容SmartSOPC核⼼上有8个发光⼆极管LED1-LED8.在QuickSOPC核⼼板上LED1-LED8分别与FPGA芯⽚的第50、53-55、176和第47-49引脚相连。

本实验的内容是建⽴可⽤控制LED亮/灭的简单硬件电路,要求点亮SmartSOPC实验箱上的4个发光⼆极管(LED1、LED3、LED5和LED7)。

具体包括:(1)使⽤QuartusⅡ建⽴⼯程;(2)QuartusⅡ⼯程设计;(3)设置编译选项并编译硬件系统;(4)下载硬件设计到⽬标FPGA;(5)观察LED状态。

三、实验原理FPGA器件同单⽚机⼀样,为⽤户提供了许多灵活独⽴的输⼊/输出I/O⼝。

FPGA每个I/O⼝可以配置为输⼊、输出、双向I/O、集电极开路和三态门等各种组态。

做输出⼝时,FPGA的I/O⼝可以吸收最⼤为24mA的电流,可以直接驱动发光⼆极管LED等器件。

所以只要正确分配并锁定引脚后,在相应的引脚上输出低电平“0”,就可实现点亮该发光⼆极管的功能。

四、实验步奏1、使⽤QuartusⅡ建⽴⼯程(1)打开QuartusⅡ软件并建⽴⼯程①打开QuartusⅡ软件,软件界⾯如图1.1所⽰。

图 1.1②选择File—New project wizard来新建⼀项⼯程(注意是新建⼯程,不是New),如图1.2。

图1.2③任何⼀项设计都是⼀项⼯程,必须⾸先为此⼯程建⽴⼀个放置与此⼯程相关的所有⽂件的⽂件夹,此⽂件夹将被QuartusⅡ默认为⼯作库。

⼀般来说,不同的设计项⽬最好放在不同的⽂件夹中,⽽同⼀⼯程的所有⽂件都必须放在同⼀⽂件夹中。

不要将⽂件夹设在计算机已有的安装⽬录中,更不要将⼯程⽂件直接放在安装⽬录中。

quartus课程设计

quartus课程设计一、课程目标知识目标:1. 理解Quartus软件的基本操作与界面布局;2. 掌握Quartus进行简单硬件描述语言(HDL)编程的方法;3. 学习并应用数字电路设计中基本的逻辑门和时序逻辑;4. 了解FPGA芯片的基本原理及其在数字电路设计中的应用。

技能目标:1. 能够独立使用Quartus软件进行基本的电路设计和仿真;2. 能够编写简单的HDL代码,实现基础的数字电路功能;3. 能够分析并优化简单的数字电路设计,以提高电路性能;4. 能够进行基本的FPGA硬件编程和调试。

情感态度价值观目标:1. 培养学生对数字电路设计及FPGA技术的兴趣和探究精神;2. 增强学生的团队协作意识和问题解决能力;3. 引导学生认识到科技发展对社会进步的重要性,培养其社会责任感;4. 通过实践操作,让学生体会知识转化为实际应用的过程,提高学习的积极性。

课程性质:本课程为电子信息类专业的选修课程,强调实践性与应用性。

学生特点:假设学生为高中二年级电子信息技术兴趣小组的成员,具备基本的电子电路知识和一定的计算机操作能力。

教学要求:结合学生特点和课程性质,课程设计需注重理论与实践相结合,鼓励学生动手实践,通过具体的案例教学,使学生在实践中掌握知识,提高技能,培养正确的情感态度价值观。

通过分解课程目标为具体的学习成果,为教学设计和评估提供明确的方向。

二、教学内容1. Quartus软件入门- 软件安装与界面认识- 基础操作与工程管理2. 硬件描述语言(HDL)基础- 常用逻辑门HDL描述- 时序逻辑电路HDL描述3. 数字电路设计原理- 逻辑门电路设计- 组合逻辑电路设计- 时序逻辑电路设计4. FPGA芯片原理与应用- FPGA基本结构与工作原理- FPGA编程与配置5. 实践项目- 简单逻辑电路设计与仿真- 组合与时序电路设计与验证- FPGA硬件编程与调试教学内容安排与进度:第一周:Quartus软件入门及基础操作第二周:硬件描述语言(HDL)基础学习第三周:数字电路设计原理学习与实践第四周:FPGA芯片原理与应用第五周:实践项目一:简单逻辑电路设计与仿真第六周:实践项目二:组合与时序电路设计与验证第七周:实践项目三:FPGA硬件编程与调试教学内容与教材关联性:本教学内容紧密围绕教材中关于数字电路设计、硬件描述语言及FPGA应用的相关章节,确保学生能够结合教材理论知识进行实践操作,提高课程的科学性和系统性。

Quartus7.1使用文档

QuartusII7.1使用文档备注:本文档仅限教研室内部学习使用,由于时间和个人能力有限,其中不够详细的地方以及错误请大家谅解。

1 QuartusII软件的介绍1.1软件简介QusrtusII 是Altera 公司针对可编程逻辑器件的高级开发工具,软件免费下载,但需要购买license 配合使用,对于非商业用户,也可以去altera 网站申请免费license,但功能会受到限制。

教研室使用的是QusrtusII7.1版的破解版,经过长时间使用,并没有发现大的问题。

1.2QuartusII的安装本版本属于破解版,安装文件一共有两个文件夹,其中文件名为quartus的文件夹为安装文件,文件名为Crack_QII7_1的文件夹为破解文件。

打开quartus文件夹,双击setup.exe文件即进入安装界面,具体安装过程本文不作详述,安装完成后会占用2.44G空间,所以安装路径不要选在C盘。

1.2QuartusII的破解破解方法在Crack_QII7_1文件夹的readme文件中有描述,大体分为两步:1 复制Crack_QII7_1文件夹中的sys_cpt.dll文件到...\altera\71\quartus\bin以覆盖sys_cpt.dll文件,注意复制前做好备份。

2 用记事本打开license文件,将其中XXXXXXXXXXXX用个人电脑的网卡号代替,注意里面有三处需要替换,运行Quartus软件,在Quartus II 7.1的Tools菜单下选择License Setup,然后选择License file,最后点击OK。

注意破解时license文件存放的路径名称不能包含汉字和空格,空格可以用下划线代替。

2QuartusII软件的使用本文用一个简单例子来介绍QuartusII 的使用方法,本实例使用QuartusII7.1 版本的软件,实现c = a & b 的功能,a、b 是两路输入信号,c 为输出信号,即输出等于两路输入相与的结果。

《FPGA系统设计》实验报告》QuartusII软件入门及组合逻辑电路设计实验

《FPGA系统设计》实验报告》QuartusII软件入门及组合逻辑电路设计实验

一.实验目的

(1)熟悉QuartusII的原理图设计流程的全过程。

(2)学习简单组合电路的设计方法、输入步骤。

(3)掌握原理图层次化设计方法。

(4)学习EDA设计的仿真和硬件测试方法。

二.实验要求

十进制计数器的设计

设计含有时钟使能的两位十进制计数器,主要通过十进制计数器74160和其他辅助元件来完成,如图1.1所示为两位十进制计数器。

图1.1 用74160设计一个有时钟使能的两位十进制计数器

三.实验操作步骤

(1). 新建项目工程:COUNTER

(2). 新建设计文件:File——New——Block Diagram/Schematic

(3). 工程的编译和综合:通过编译来检查设计文件是否存在错误。

(4). 管脚的分配与下载:在Location中分别将引脚分配芯片引脚并进行全编译,将USB-Blaster下载器与电脑相连,安装好驱动程序,将编译好的文件下载到芯片中,点击Programmer—Hardware Setup设置下载器的驱动程序,在Hardware Setup对话框中选择USB-Blaster0,点击start可完成程序下载,Progress中显示“100%successful”即为下载成功。

四.实验数据结果。