DSP试卷及答案

DSP原理期末试卷和答案

一、单项选择题:(每小题2分,共30分)1、下面对一些常用的伪指令说法正确的是:( D )A、.def所定义的符号,是在当前模块中使用,在别的模块中定义的符号;B、.ref 所定义的符号,是当前模块中定义,并可在别的模块中使用的符号;C、.sect命令定义的段是未初始化的段;D、.usect命令定义的段是未初始化的段。

2、要使DSP能够响应某个可屏蔽中断,下面的说法正确的是( B)A、需要把状态寄存器ST1的INTM位置1,且中断屏蔽寄存器IMR相应位置0B、需要把状态寄存器ST1的INTM位置1,且中断屏蔽寄存器IMR相应位置1C、需要把状态寄存器ST1的INTM位置0,且中断屏蔽寄存器IMR相应位置0D、需要把状态寄存器ST1的INTM位置0,且中断屏蔽寄存器IMR相应位置13、对于TMS320C54x系列DSP芯片,下列说法正确的是………… ( C )A、 8位DSPB、32位DSPC、定点型DSPD、浮点型DSP4、若链接器命令文件的MEMORY部分如下所示:MEMORY{PAGE 0: PROG: origin=C00h, length=1000hPAGE 1: DATA: origin=80h, length=200h}则下面说法不正确的是()A、程序存储器配置为4K字大小B、程序存储器配置为8K字大小C、数据存储器配置为512字大小D、数据存储器取名为DATA5、在串行口工作于移位寄存器方式时,其接收由()来启动。

A、RENB、RIC、REN和RID、TR6、执行指令PSHM AR5之前SP=03FEH,则指令执行后SP=( A )A、03FDHB、03FFHC、03FCHD、0400H7、TMS320C54X DSP采用改进的哈佛结构,围绕____A__组_______位总线建立。

A、8,16B、16,8C、8,8D、16,168、TMS320C54X DSP汇编指令的操作数域中, A 前缀表示的操作数为间接寻址的地址。

dsp试题及答案

dsp试题及答案一、选择题1. 数字信号处理(DSP)中,离散傅里叶变换(DFT)的基本周期是:A. 1B. 2πC. ND. 2N答案:C2. 在DSP中,快速傅里叶变换(FFT)的主要优点是:A. 提高了计算精度B. 减少了计算量C. 增加了数据的实时性D. 增强了信号的稳定性答案:B3. 下列哪个不是数字滤波器的设计方法?A. 窗函数法B. 脉冲响应不变法C. 频率采样法D. 相位锁定环法答案:D二、填空题4. 数字信号处理中,_______是一种将模拟信号转换为数字信号的过程。

答案:采样5. 离散时间信号的傅里叶变换(DTFT)的频率范围是_______。

答案:[0, π]6. 一个数字滤波器的频率响应函数H(z)可以用来描述滤波器对不同频率信号的_______。

答案:响应三、简答题7. 简述数字信号处理中的频域分析方法的主要特点。

答案:频域分析方法通过将时域信号转换到频域,利用频域的特性来分析和处理信号。

主要特点包括:能够直观地观察信号的频率成分;便于进行信号的滤波和调制;可以简化某些数学运算。

8. 解释什么是数字信号处理中的过采样,并说明其在实际应用中的优势。

答案:过采样是指采样频率远高于信号最高频率的两倍。

在实际应用中,过采样可以提高信号的分辨率,降低噪声的影响,并且有助于信号的重建和处理。

四、计算题9. 给定一个离散时间信号x[n] = {1, 2, 3, 4},计算其离散傅里叶变换(DFT)的前四个值。

答案:根据DFT的定义,x[n]的DFT X[k]为:X[0] = 1 + 2 + 3 + 4X[1] = 1 - 2 + 3 - 4X[2] = 1 + 2 - 3 - 4X[3] = 1 - 2 - 3 + 410. 已知一个低通滤波器的冲激响应h[n] = {1, 1/2, 1/4},计算其频率响应H(ω)。

答案:根据傅里叶变换的定义,H(ω)可以通过h[n]的傅里叶变换得到。

dsp原理期末考试试卷和答案

dsp原理期末考试试卷和答案**DSP原理期末考试试卷**一、单项选择题(每题2分,共20分)1. DSP芯片中,以下哪个不是其主要特点?A. 高速处理能力B. 低功耗C. 大容量存储D. 可编程性2. 在DSP系统中,以下哪个不是数据转换器的类型?A. A/D转换器B. D/A转换器C. I/O转换器D. V/F转换器3. 以下哪个不是DSP编程语言?A. C语言B. Assembly语言C. Fortran语言D. MATLAB4. DSP芯片中,哪个寄存器用于存储程序计数器?A. PCB. ARC. DRD. SR5. 在DSP中,以下哪个指令不是算术运算指令?A. ADDB. SUBC. MPYD. MOV6. DSP芯片中,以下哪个不是中断类型?A. 外部中断B. 定时器中断C. 串行通信中断D. 算术溢出中断7. 在DSP系统中,以下哪个不是模数转换器(ADC)的特性?A. 分辨率B. 采样率C. 量化误差D. 存储容量8. DSP芯片中,以下哪个不是指令周期的组成部分?A. 取指周期B. 执行周期C. 存储周期D. 写回周期9. 在DSP编程中,以下哪个不是循环控制指令?A. FORB. WHILEC. DOD. JMP10. DSP芯片中,以下哪个不是系统时钟的来源?A. 外部晶振B. 内部RC振荡器C. 外部时钟信号D. 软件生成时钟二、填空题(每题2分,共20分)1. DSP芯片的全称是__________。

2. 在DSP系统中,A/D转换器的分辨率是指能够区分的最小电压变化,通常用__________位来表示。

3. DSP编程中,汇编语言的指令通常由__________和__________两部分组成。

4. 在DSP系统中,__________是一种常用的数字信号处理算法,用于减少信号的频带宽度。

5. DSP芯片的指令集通常包括算术运算、逻辑运算、数据传输和__________等指令。

dsp试卷及答案

dsp试卷及答案【篇一:dsp试题及答案1】xt>__________班姓名 ___________学号_______________(请考生注意:本试卷共 5 页,8道大题)tms320c54x系列,所有答案均以54系列为主,特此声明)一、单项选择题: (每小题2分,总计20分)1、以下各项哪项不属于dsp芯片的主要特点答:( b )(a)哈佛结构(b)事务型处理器(c)指令系统的流水线操作(d)多总线结构 2、哈佛结构与冯.诺依曼结构的区别在于答:( a )(a)不止一条数据总线(b)多个存储器(c)允许流水线操作(d)专用的硬件乘法器3、tms320c54x的中央处理器由以下哪项组成答:( a )(a)运算部件和控制部件(b)算术逻辑单元和累加器(c)累加器和乘法器(d)st1和sto4、以下各项哪项不属于选择dsp 芯片时考虑的因素答:( d )(a)运算速度(b)精度和动态范围(c)价格(d)外观6、若使cpl=1,dp=1,sp=0100h,执行直接寻址语句:add 30h,a 后,则得到16位的数据存储器实际地址为:答:( b )(a)00b0h (b)0130h(c)0031h(d)0030h7、双数据存储器操作数间接寻址所用辅助寄存器只能是以下哪项答:( c )(a)ar0 ar1 ar2 ar3(b)ar1 ar2 ar3 ar4 (c)ar2 ar3 ar4 ar5 (d)ar0 ar1 ar6 ar78、以下段定义伪指令中哪个属于未初始化段:答:( c )(a).text (b).data (c).usect (d).sect9、dsp中c语言设计具有兼容性和可移植的优点, c代码的程序入口地址符号为答:( a )(A)_c_int00 (b)start(c)reset (d)_c_int10、在ccs中编译c程序时,必须将运行时间支持库文件添加到工程中,该文件名为:答:( b)(A)rts.src (B)rts.lib (C)rtdx.lib (d)rtdx.h二、填空题:(总计15分)1.dsp应用系统的设计流程包括4个步骤:算法模拟阶段、____2.ti的三大主力dsp3. 对54系列dsp来说,一般地,有192k字可寻址存储空间,其中包括:4.用重复指令将程序存储区从地址单元0100h到0180h区间段的内容复制到数据存储区间从1000h开始的地址单元中。

dsp大学期末考试试题及答案

dsp大学期末考试试题及答案一、选择题(每题2分,共20分)1. DSP(数字信号处理)的全称是什么?A. Digital Signal ProcessingB. Digital Sound ProcessingC. Data Signal ProcessingD. Digital Storage Processing答案:A2. 在DSP系统中,以下哪个不是数字滤波器的类型?A. 低通滤波器B. 高通滤波器C. 带通滤波器D. 线性滤波器答案:D3. 下列哪个算法不是用于数字信号处理的?A. FFT(快速傅里叶变换)B. DCT(离散余弦变换)C. JPEG(联合图像专家组)D. MDCT(修改离散余弦变换)答案:C4. 在DSP中,以下哪个是用于实现信号采样的设备?A. ADC(模数转换器)B. DAC(数模转换器)C. CPLD(复杂可编程逻辑器件)D. FPGA(现场可编程门阵列)答案:A5. 下列哪个参数不是描述数字信号的?A. 幅度B. 频率C. 相位D. 电阻答案:D6. 在DSP中,以下哪个指标用于衡量信号的频域特性?A. 幅度谱B. 相位谱C. 功率谱D. 所有选项答案:D7. 下列哪个选项不是DSP系统设计的关键考虑因素?A. 处理速度B. 内存容量C. 电源电压D. 信号带宽答案:C8. 在DSP编程中,以下哪个不是常用的编程语言?A. C语言B. C++语言C. MATLABD. VHDL答案:C9. 下列哪个不是DSP系统的应用领域?A. 音频处理B. 图像处理C. 无线通信D. 机械制造答案:D10. 在DSP系统中,以下哪个是用于实现信号放大的组件?A. 运算放大器B. 滤波器C. 调制器D. 编码器答案:A二、填空题(每题2分,共20分)1. DSP技术在______和______处理中具有广泛应用。

答案:数字信号;模拟信号2. 一个典型的DSP系统包括______、______和______。

《dsp原理及应用》期末试题及答案(一)

《dsp原理及应用》期末试题及答案(一)《dsp原理及应用》期末试题及答案:选择题1、对于TMS320C54x系列DSP芯片,下列说法正确的是 ( C )(A) 专用型DSP (B)32位DSP (C) 定点型DSP (D) 浮点型DSP2、要使DSP能够响应某个可屏蔽中断,下面的说法正确的是 (B )需要把状态寄存器ST1的INTM位置1,且中断屏蔽寄存器IMR相应位置0需要把状态寄存器ST1的INTM位置1,且中断屏蔽寄存器IMR相应位置1需要把状态寄存器ST1的INTM位置0,且中断屏蔽寄存器IMR相应位置0需要把状态寄存器ST1的INTM位置0,且中断屏蔽寄存器IMR相应位置13、若链接器命令文件的MEMORY部分如下所示:MEMORY{PAGE 0: PROG: origin=C00h, length=1000hPAGE 1: DATA: origin=80h, length=200h}则下面说法不正确的是(A)程序存储器配置为4K字大小 B、程序存储器配置为8K 字大小C、数据存储器配置为512字大小D、数据存储器取名为DATA5、C54X DSP的流水线是由( B )级(也即是由多少个操作阶段)组成。

(A) 4 (B) 6 (C) 8 (D) 106、假定AR3中当前值为200h,AR0中的值为20h,下面说法正确的是( )A、在执行指令*AR3+0B后,AR3的值是200h;B、在执行指令*AR3-0B后,AR3的值为23Fh;C、在执行指令*AR3-0B后,AR3的值是180h;7、下面对一些常用的伪指令说法正确的是:( D )A、.def所定义的符号,是在当前模块中使用,而在别的模块中定义的符号;B、.ref 所定义的符号,是当前模块中定义,并可在别的模块中使用的符号;C、.sect命令定义的段是未初始化的段;D、.usect命令定义的段是未初始化的段。

8、在采用双操作数的间接寻址方式时,要使用到一些辅助寄存器,在此种寻址方式下,下面的那些辅助寄存器如果使用到了是非法的( D )A、AR2B、AR4C、AR5D、AR6《dsp原理及应用》期末试题及答案:填空题1、DSP芯片按照其用途分类,可以分为通用型和专用型两种。

dsp技术及应用期末考试题及答案

dsp技术及应用期末考试题及答案一、选择题(每题2分,共20分)1. 数字信号处理(DSP)技术主要应用于以下哪个领域?A. 计算机编程B. 通信系统C. 机械制造D. 农业科学答案:B2. 下列哪个不是数字信号处理的基本步骤?A. 采样B. 量化C. 编码D. 滤波答案:C3. 在数字滤波器设计中,低通滤波器的截止频率通常定义为:A. 滤波器的中心频率B. 滤波器的带宽C. 滤波器的半功率点D. 滤波器的增益答案:C4. 数字信号处理中,傅里叶变换的主要作用是将信号从哪个域转换到哪个域?A. 时域到频域B. 频域到时域C. 空间域到时间域D. 时间域到空间域答案:A5. 下列哪个算法不是用于数字信号处理中的快速傅里叶变换(FFT)?A. Cooley-Tukey算法B. Rader算法C. 快速卷积算法D. 快速排序算法答案:D二、填空题(每空2分,共20分)6. 数字信号处理中,_______ 是指信号在时间上是离散的。

答案:采样7. 在数字信号处理中,_______ 是指信号在幅度上是离散的。

答案:量化8. 一个数字滤波器的阶数是指滤波器中延迟元素的_______。

答案:数量9. 数字信号处理中的窗函数用于_______ 信号,以减少频谱泄露。

答案:截断10. 快速傅里叶变换(FFT)是一种高效的算法,用于计算_______。

答案:离散傅里叶变换(DFT)三、简答题(每题10分,共30分)11. 简述数字信号处理中采样定理的重要性及其内容。

答案:采样定理是数字信号处理中的基本理论,它规定了在不失真地恢复模拟信号的条件下,采样频率应大于信号最高频率的两倍。

这一定理对于信号的数字化和信号的重建至关重要。

12. 解释什么是数字滤波器,并简述其分类。

答案:数字滤波器是一种对数字信号进行滤波处理的系统,它可以通过软件实现,也可以通过硬件实现。

数字滤波器主要分为低通滤波器、高通滤波器、带通滤波器和带阻滤波器,它们分别用于通过或阻止信号的特定频率成分。

dsp期末考试试题及答案

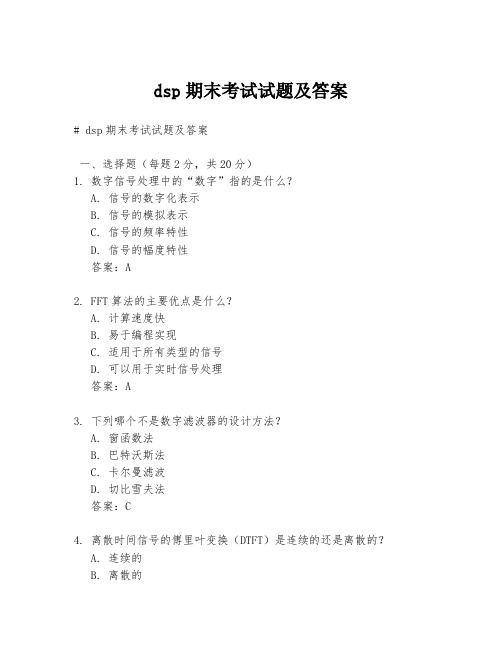

dsp期末考试试题及答案# dsp期末考试试题及答案一、选择题(每题2分,共20分)1. 数字信号处理中的“数字”指的是什么?A. 信号的数字化表示B. 信号的模拟表示C. 信号的频率特性D. 信号的幅度特性答案:A2. FFT算法的主要优点是什么?A. 计算速度快B. 易于编程实现C. 适用于所有类型的信号D. 可以用于实时信号处理答案:A3. 下列哪个不是数字滤波器的设计方法?A. 窗函数法B. 巴特沃斯法C. 卡尔曼滤波D. 切比雪夫法答案:C4. 离散时间信号的傅里叶变换(DTFT)是连续的还是离散的?A. 连续的B. 离散的C. 既连续又离散D. 都不是答案:A5. 采样定理指出,采样频率至少应该是信号最高频率的多少倍?A. 1倍B. 2倍C. 3倍D. 4倍答案:B...(此处省略其他选择题,共10题)二、简答题(每题10分,共20分)1. 解释什么是离散傅里叶变换(DFT)以及它与连续傅里叶变换(FT)的区别。

答案:离散傅里叶变换(DFT)是一种将离散时间信号转换为频域表示的方法。

它是一种离散的变换,意味着输入和输出都是离散的。

DFT通常用于数字信号处理中,可以计算出信号在各个频率上的幅度和相位。

与DFT不同,连续傅里叶变换(FT)是将连续时间信号转换为连续的频域表示,它适用于模拟信号处理。

2. 简述数字滤波器的基本概念及其分类。

答案:数字滤波器是一种对数字信号进行处理的系统,它允许某些频率的信号通过,同时抑制或减少其他频率的信号。

数字滤波器可以根据它们的频率响应特性进行分类,主要分为低通滤波器、高通滤波器、带通滤波器和带阻滤波器。

每种类型的滤波器都设计用于处理特定频率范围内的信号。

三、计算题(每题15分,共30分)1. 给定一个离散时间信号 x[n] = {1, 2, 3, 4},计算其DFT X[k]。

答案:X[k] = DFT{x[n]} = Σ_{n=0}^{N-1} x[n] * e^(-j * 2π * k * n / N)其中,N=4,计算得到 X[k] 的值。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DSP试卷1一.填空题(本题总分12分,每空1分)1.TMS320VC5402型DSP的部采用条位的多总线结构。

2.TMS329VC5402型DSP有个辅助工作寄存器。

3.在器命令文件中,PAGE 1通常指________存储空间。

4.TI公司DSP处理器的软件开发环境是__________________。

5.直接寻址中从页指针的位置可以偏移寻址个单元。

6.TMS320C54x系列DSP处理器上电复位后,程序从指定存储地址________单元开始工作。

7.MS320C54X DSP主机接口HPI是________位并行口。

8.TMS320VC5402型DSP处理器的核供电电压________伏。

9. C54x系列DSP上电复位后的工作频率是由片外3个管脚;;来决定的。

二.判断题(本题总分10分,每小题1分,正确打“√”,错误打“×”)1.DSP 处理器TMS320VC5402的供电电压为5V。

()2.TMS320VC5402型DSP部有8K字的ROM,用于存放自举引导程序、u律和A律扩展表、sin函数表以及中断向量表。

()3.MEMORY伪指令用来指定器将输入段组合成输出段方式,以及输出段在存储器中的位置。

()4. DSP的流水线冲突产生的原因是由于DSP运行速度还不够快。

()5.DSP和MCU属于软件可编程微处理器,用软件实现数据处理;而不带CPU软核的FPGA 属于硬件可编程器件,用硬件实现数据处理。

()6. C54x系列DSP的CPU寄存器及片外设寄存器映射在数据存储空间的0000h-0080h中。

()7.TMS320C54X 系列DSP可以通过设置OVL Y位实现数据存储空间和程序存储空间共享片ROM。

()8. TMS320VC5402型DSP汇编指令READA的寻址围为64K字。

()9.在TMS320VC5402型DSP所有中断向量中,只有硬件复位向量不能被重定位,即硬件复位向量总是指向程序空间的0FF80H位置。

()10. C54x系列DSP只有两个通用的I/O引脚。

()三.程序阅读题(本题总分30分,每小题10分)1. 阅读下面的程序,回答问题。

.bss x, 8LD #0001H,16,BSTM #7,BRCSTM #x,AR4RPTB next-1ADD *AR4,16,B,ASTH A,*AR4+next: LD #0,B问题:(1)寄存器“BRC”的功能是什么?(2)汇编语句“ADD *AR4,16,B,A”执行了多少次?(3)执行语句“LD #0001H,16,B”后,累加器B的容是多少?2.已知DSP的三个时钟引脚状态CLKMD1-CLKMD3=111,外部晶振=10MHz,参数设置表:Status:LDM CLKMD,AAND #01H,ABC Status,ANEQSTM #9007H,CLKMD问题(1)DSP复位后,DSP的工作时钟是多少?(2)执行上面的程序片段后,DSP的工作时钟是多少?3.阅读下面的命令连接文件(简称CMD文件)和程序文件:CMD文件:MEMORY{ PAGE 0: PROG: origin = 0x1000, length = 0x1000PAGE 1: DATA: origin = 0x2000, length = 0x1000}SECTIONS{ .text: {} > PROG PAGE 0.data: {} > DATA PAGE 1}.datatable: .word 1,2,3,4 ; 变量初始化.textstart: STM # 0,SWWSR ; 插入0个等待状态问:(1)MEMORY和SECTIONS的作用各是什么?(2)标号“table”和“start”的地址分别是什么,分别位于程序空间还是数据空间?四.简答题(本题总分48分,每小题8分)1.在C54x的汇编语言中,使用“#”、“*”、“”符号作为操作数的前缀各表示什么意思?2.简述COFF文件中“段”的概念,有哪些常用的段?3.简述·诺依曼结构、哈佛结构和改进的哈佛结构之间的区别。

4.简述C54x系列DSP定时器的组成部分、各部分分别起什么作用?5.简述DSP处理器TMS320VC5402在微计算机工作模式中上电启动的过程。

6. 简述PMST寄存器中IPTR的作用。

答案1一.填空题(本题总分12分,每空1分)1.8,16 2.8个3.数据4.答:CCS(Code Composer Studio)5.答:128 6.答:FF80h 7.答:8 8.答:1.8v9.答:CLKMD1、CLKMD2、CLKMD3二.判断题(本题总分10分,每小题1分,正确打“√”,错误打“×”)1.× 2. × 3. √ 4. × 5. √ 6. √7. ×8. ×9. √10. √三.程序阅读题(本题总分30分,每小题10分)1.(1) 寄存器“BRC”的功能是暂存块循环的次数(2) 8次(3) B=0x0100H;2. 答:(1)5MHz (2)100MHz3. 答:MEMORY和SECTIONS伪指令,用来指定目标存储器结构和地址分配。

标号table:1000h(程序空间) 标号start:2000h(数据空间)四.简答题(本题总分48分,每小题8分)1.答:使用“#”号作为前缀,汇编器将操作数作为立即数处理。

即使操作数是寄存器或地址,也将作为立即数。

使用“*”符号作为前缀,汇编器将操作数作为间接地址,即把操作数的容作为地址。

使用“”符号作为前缀,汇编器将操作数作为直接地址,即操作数由直接地址码赋值。

2.答:段是COFF文件中最重要的概念。

每个目标文件都分成若干段。

段——是存储器中占据相邻空间的代码或数据块。

一个目标文件中的每个段都是分开的和各不相同的。

.text 段(文本段),通常包含可执行代码;.data 段(数据段),通常包含初始化数据;.sect段——已初始化段,由汇编器伪指令建立的自定义段。

.bss段——未初始化段;.usect段——未初始化段,由汇编命令建立的命名段(自定义段)。

3. 答:·诺伊曼(V on Neuman)结构采用单存储空间,即程序指令和数据共用一个存储空间,使用单一的地址和数据总线,取指令和取操作数都是通过一条总线分时进行。

当进行高速运算时,不但不能同时进行取指令和取操作数,而且还会造成数据传输通道的瓶颈现象,其工作速度较慢。

哈佛(Harvard)结构采用双存储空间,程序存储器和数据存储器分开,有各自独立的程序总线和数据总线,可独立编址和独立访问,可对程序和数据进行独立传输,使取指令操作、指令执行操作、数据吞吐并行完成,大提高了数据处理能力和指令的执行速度,非常适合于实时的数字信号处理。

改进型的哈佛结构是采用双存储空间和数条总线,即一条程序总线和多条数据总线。

允许在程序空间和数据空间之间相互传送数据,使这些数据可以由算术运算指令直接调用,增强芯片的灵活性;提供了存储指令的高速缓冲器(cache)和相应的指令,当重复执行这些指令时,只需读入一次就可连续使用,不需要再次从程序存储器中读出,从而减少了指令执行作需要的时间。

4.答:定时器主要由定时寄存器TIM、定时周期寄存器PRD、定时控制寄存器TCR及相应的逻辑控制电路组成。

定时周期寄存器PRD用来存放定时时间,定时寄存器TIM为16位减1计数器,定时控制寄存器TCR存放定时器的控制位和状态位,逻辑控制电路用来控制定时器协调工作。

5. 答:DSP上电复位后,程序PC指针跳转到0xff80位置,在芯片的0xff80这个单元中存储着跳转指令、程序自动跳转到0xF800,开始执行自举装载程序,自举装载程序将片外存储器的程序搬运到DSP程序存储空间的某个地方,自举装载程序的最后一条指令是跳转指令,程序接着跳转到刚才搬运在程序存储空间的某个地址,从而开始程序的自动运行。

6.答:C54x的中断向量地址是由PMST寄存器中的IPTR(9位中断向量指针)和左移2位后的中断向量序号所组成。

中断向量地址=IPTR+(左移2位的中断向量序号)DSP试卷2一.填空题(本题总分12分,每空1分)1.累加器A分为三个部分,分别为;;。

2.TI公司的DSP处理器TMS320VC5402PGE100有___________个定时器。

3.TMS329VC5402型DSP的ST1寄存器中,INTM位的功能是。

4.在器命令文件中,PAGE 0通常指________存储空间。

5.DSP处理器按数据格式分为两类,分别是_______ __;_____ ___。

6.DSP处理器TMS320VC5402的IO管脚供电电压________伏。

7.TMS320VC5402型DSP的累加器是位。

8.TMS320C54X具有两个通用I/O口,________用于输入外设的状态;________用于输出外设的控制信号。

二.判断题(本题总分10分,每小题1分)1.DSP的工作频率只能是外部晶体振荡器的频率。

()2.TMS320C54X DSP的汇编语言中有除法指令。

()3.哈佛结构的特点是数据总线和程序总线分开。

()4.在C54x系列DSP中断向量表中,每个中断向量的入口地址间隔4个字。

()5.在DSP处理器汇编程序中,标号区分大小写。

()6. TMS320VC5402型DSP汇编语言的伪指令也是一种指令,同样占用存储空间。

()7. DSP 处理器TMS320VC5402的软件中断是不可屏蔽的中断。

()8.DSP 处理器TMS320VC5402有不止一种串行口。

()9.DSP处理器TMS320VC5402在微型计算机工作模式时,上电复位后程序从片外存储器的FF80h单元开始执行。

()10. TMS320VC5402型DSP汇编语言的寻址方式可以实现FFT算法中的位倒序寻址方式。

()三.程序阅读题(本题总分30分,每小题10分)1.阅读下面的程序:.mmregsDAT0 .SET 60HDAT1 .SET 61HDAT2 .SET 62HDAT3 .SET 63Hadd3 .macro P1,P2,P3,ADDRPLD P1,AADD P2,AADD P3,ASTL A,ADDRP.endmST #0034h,DA T0ST #0243h,DA T1ST #1230h,DA T2ADD3 DA T0,DA T1,DAT2,DA T3问题:(1)语句“.mmregs”的含义。

(2)语句“ADD3 DAT0,DAT1,DAT2,DAT3”是一条什么类型的语句?作用是什么?(3)执行此段程序后,存储单元(DAT3)的运行结果多少?2.阅读下面的程序,回答问题。