串口JTAG使用说明

AVR单片机JTAG接口的使用方法

AVR单片机JTAG接口的使用方法AVR单片机JTAG(Joint Test Action Group)接口是一种用于单片机的调试和编程工具。

它提供了一种高效的方式来进行硬件调试、固件编程和软件调试。

在本文中,我将详细介绍AVR单片机JTAG接口的使用方法。

1.JTAG接口简介JTAG接口由四条线组成,分别是TCK(时钟线)、TMS(状态线)、TDI(数据输入线)和TDO(数据输出线)。

它是一种串行接口,用于与其他外设进行通信。

JTAG接口能够通过硬件调试、固件编程和软件调试来提高系统调试的效率。

2.JTAG接口的初始化在使用JTAG接口之前,需要对其进行初始化。

首先,需要确定使用的JTAG接口类型,然后根据类型选择与之匹配的调试工具和软件。

接下来,需要连接JTAG接口的四个引脚到单片机的相应引脚上。

通常,这些引脚在单片机的数据手册中有详细的说明。

3.JTAG接口的连接连接JTAG接口的四个引脚到单片机的相应引脚上,确保连接正确无误。

通常,TCK(时钟线)和TMS(状态线)引脚是共享的,它们分别连接到单片机的相应引脚上。

TDI(数据输入线)和TDO(数据输出线)引脚则是分别连接到单片机的相应引脚上。

请务必根据单片机的数据手册正确连接JTAG接口引脚。

4.JTAG接口的编程在使用JTAG接口进行编程之前,需要确保已经安装了合适的调试工具和软件。

这些工具和软件可以帮助我们完成对单片机的编程操作。

通常,这些工具和软件提供了一些简单的命令和接口,用于与单片机进行通信。

通过这些命令和接口,我们可以读取和写入单片机的内部寄存器,从而实现对单片机的编程操作。

5.JTAG接口的调试使用JTAG接口进行调试可以帮助我们找到系统中的错误和问题。

通过读取和写入单片机的内部寄存器,我们可以查看程序的执行状态、输入和输出数据、栈的使用情况等信息。

通过这些信息,我们可以判断程序中的错误和问题,并进行调试操作。

6.JTAG接口的注意事项在使用JTAG接口之前-确保JTAG接口的引脚连接正确无误,避免引脚连接错误导致的通信问题。

JTAG仿真器使用方法图文教程

JTAG仿真器使⽤⽅法图⽂教程本⽂主要介绍USBJTAG的使⽤⽅法,该仿真器既可以⽤做JTAG放着器给AVR芯⽚下载程序以及仿真,也可以⽤来给STC89C系列的芯⽚下载程序。

本⽂主要分为以下⼏个部分:JTAG简介、AVRJTAG仿真器⼯作原理、JTAG仿真器上的跳线设置、JTAG驱动安装、JTAG仿真器的验证。

1、什么是JTAG仿真器JTAG仿真器,也叫JTAG调试器,即⼀种采⽤JTAG协议进⾏调试和下载的器件。

JTAG也是⼀种国际标准测试协议(IEEE 1149.1兼容),主要⽤于芯⽚内部测试。

现在多数的⾼级器件都⽀持JTAG协议,如DSP、FPGA器件等。

标准的JTAG接⼝是4线:TMS(模式选择)、TCK(时钟)、TDI(数据输⼊)、TDO(数据输出)。

相关JTAG引脚的定义为:TCK为测试时钟输⼊;TDI为测试数据输⼊,数据通过TDI引脚输⼊JTAG接⼝;TDO为测试数据输出,数据通过TDO引脚从JTAG 接⼝输出;TMS为测试模式选择,TMS⽤来设置JTAG接⼝处于某种特定的测试模式;TRST为测试复位,输⼊引脚,低电平有效。

这⾥主要介绍的是AVR的JTAG仿真器,由于每个器件对应的上位机软件(PC上运⾏的软件)实现⽅式不同,所以不同器件的JTAG仿真器是不能够通⽤的。

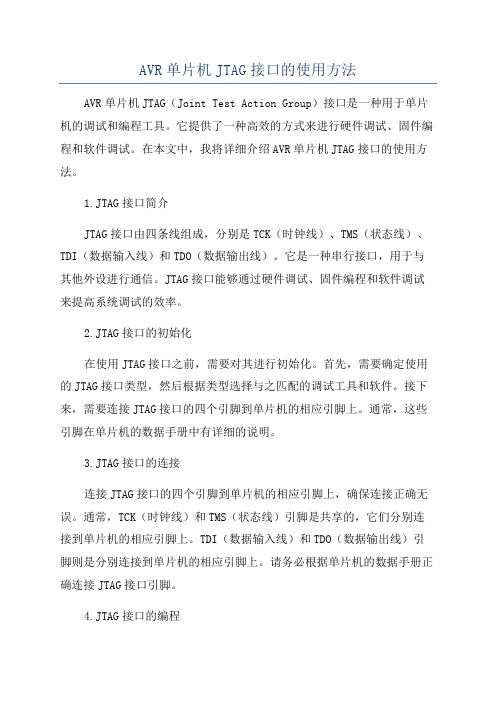

AVR使⽤的JTAG接⼝是4线接⼝,但是现在⽹上普遍流⾏的做法是,在JTAG接⼝中加⼊AVR器件的复位(RST)引脚,2个电源引脚(VCC)、2个地引脚(GND)、⼀个空引脚(NC)⼀共是10个引脚,并且这10个引脚有固定的引脚排序。

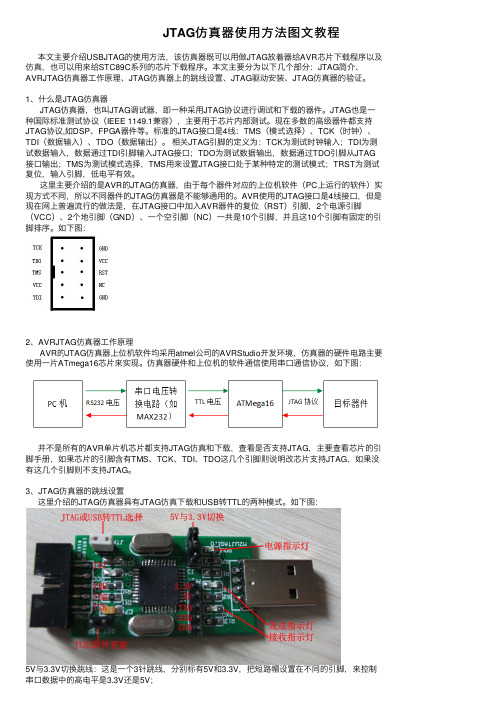

如下图:2、AVRJTAG仿真器⼯作原理AVR的JTAG仿真器上位机软件均采⽤atmel公司的AVRStudio开发环境,仿真器的硬件电路主要使⽤⼀⽚ATmega16芯⽚来实现。

仿真器硬件和上位机的软件通信使⽤串⼝通信协议,如下图:并不是所有的AVR单⽚机芯⽚都⽀持JTAG仿真和下载,查看是否⽀持JTAG,主要查看芯⽚的引脚⼿册,如果芯⽚的引脚含有TMS、TCK、TDI、TDO这⼏个引脚则说明改芯⽚⽀持JTAG,如果没有这⼏个引脚则不⽀持JTAG。

jtag工作原理详解

jtag工作原理详解JTAG(Joint Test Action Group)是一种用于测试和调试集成电路的标准接口。

它提供了一种通用的、标准化的方法来访问集成电路内部的信号和寄存器,以便进行测试、调试和编程操作。

本文将详细介绍JTAG工作原理,包括JTAG的基本原理、信号传输方式、测试模式和操作流程等。

一、JTAG的基本原理JTAG是一种串行接口,它使用了四根信号线(TCK、TMS、TDI、TDO)来实现与目标芯片的通信。

其中,TCK(Test Clock)是测试时钟信号,用于同步数据传输;TMS(Test Mode Select)是测试模式选择信号,用于控制JTAG状态机的状态转换;TDI(Test Data Input)是测试数据输入信号,用于向目标芯片发送测试数据;TDO(Test Data Output)是测试数据输出信号,用于从目标芯片读取测试结果。

二、信号传输方式JTAG使用的是一种称为“链式扫描”(Scan Chain)的方式来传输数据。

在链式扫描中,所有的目标芯片连接成一个长链,每个芯片都有一个扫描链(Scan Chain)用于传输数据。

通过控制TMS信号,可以选择要操作的芯片,并将数据从一个芯片传递到下一个芯片。

三、测试模式JTAG定义了多种测试模式,包括测试、调试和编程模式等。

其中,测试模式用于对芯片进行功能测试和故障诊断;调试模式用于对芯片进行调试和性能分析;编程模式用于对芯片进行编程操作。

在测试模式下,可以通过JTAG接口对芯片内部的寄存器进行读写操作,以验证芯片的功能是否正常。

通过设置不同的测试模式,可以选择要测试的功能模块,并将测试数据传递到目标芯片进行测试。

四、操作流程JTAG的操作流程通常包括以下几个步骤:1. 初始化:将JTAG状态机设置为测试模式,并将目标芯片复位到初始状态。

2. 选择目标芯片:通过控制TMS信号,选择要操作的目标芯片。

3. 设置测试模式:通过控制TMS和TDI信号,设置目标芯片的测试模式。

什么是JTAG及其使用方法

什么是JTAG及其使用方法JTAG(Joint Test Action Group)是一种用于测试和调试电子设备的接口和协议标准。

它最初是由一组芯片制造商于1985年共同开发的,并被广泛应用于各种数字电路和嵌入式系统中。

JTAG可以通过一组标准的测试和调试功能,提供对目标设备内部电路的控制和观察。

JTAG的使用方法包括以下几个方面:1.设备连接:使用JTAG接口连接目标设备和测试设备。

JTAG接口通常由四个线路组成,即TCK(时钟)、TMS(状态机控制)、TDI(数据输入)和TDO(数据输出)。

这些线路通过专门的JTAG连接器或引脚与目标设备连接。

2.设备识别:测试设备通过JTAG接口与目标设备通信,并识别目标设备的类型和功能。

这通常是通过发送一系列特定的指令和信号来实现的。

目标设备需要支持JTAG协议,并在芯片内部集成了JTAG控制逻辑。

3.测试模式:JTAG可以让我们在目标设备的测试模式下运行和测试其内部电路。

在测试模式下,我们可以检查和修改目标设备内部各个电路的状态和数据。

测试模式通常使用状态机来控制目标设备的测试流程。

4.调试功能:JTAG还提供了强大的调试功能,允许工程师监视和控制目标设备的执行过程。

通过JTAG接口,我们可以在目标设备运行的任何时候停止执行,并检查寄存器、内存和其他关键数据。

同时,我们还可以通过JTAG接口修改寄存器和内存中的数据,以调试软件和硬件问题。

5.效能测试:除了测试和调试功能之外,JTAG还可以用于测试目标设备的性能和效能。

通过发送特定的信号和指令,我们可以控制目标设备的工作频率、电压和其他工作参数,以评估其在不同工作条件下的性能。

需要注意的是,JTAG只是一个接口标准和协议,而实现JTAG功能的具体硬件和软件可能因厂商和设备类型而有所差异。

因此,在实际使用JTAG之前,我们需要了解目标设备的JTAG接口规格和支持的JTAG功能。

总之,JTAG是一种强大而灵活的测试和调试接口,它能够帮助我们识别和解决各种硬件和软件问题。

jtagapb用法

jtagapb用法摘要:1.JTAG简介2.APB简介3.JTAG与APB的结合:JTAG-APB4.JTAG-APB的使用方法5.实例演示6.注意事项正文:JTAG(Joint Test Action Group,联合测试行动组)和APB(Advanced Peripheral Bus,高级外围总线)是两种硬件调试和编程接口,它们在嵌入式系统开发中广泛应用。

JTAG主要用于芯片内部测试,而APB则用于芯片内部各个模块之间的通信。

当这两者结合时,它们为开发者提供了一种强大的硬件调试和编程解决方案。

本文将详细介绍JTAG-APB的使用方法。

1.JTAG简介JTAG是一种用于测试和调试硬件的标准接口,它最初由英国公司Philips Semiconductors于1990年代研发。

JTAG接口主要有四根线:TMS(Test Mode Select,测试模式选择)、TDI(Test Data In,测试数据输入)、TDO (Test Data Out,测试数据输出)和TCK(Test Clock,测试时钟)。

通过这些线路,JTAG提供了一种可靠的方法来访问和控制芯片内部的各种寄存器和逻辑。

2.APB简介APB是一种高性能、低延迟的总线接口,用于芯片内部各个模块之间的通信。

它由两根数据线(A和B)和一根时钟线(CLK)组成。

APB支持同步和异步传输,数据传输速率较高,可满足大多数嵌入式系统的需求。

3.JTAG与APB的结合:JTAG-APB当JTAG和APB结合时,开发者可以利用JTAG接口进行硬件调试,同时通过APB接口实现芯片内部模块之间的通信。

这为开发者提供了一种便捷的方式,可以在调试过程中实时观察和控制芯片的运行状态。

4.JTAG-APB的使用方法要使用JTAG-APB,首先需要配置相应的硬件和软件环境。

这包括:- 硬件:具有JTAG和APB接口的芯片- 软件:支持JTAG-APB的调试工具和驱动程序使用JTAG-APB时,可分为以下几个步骤:1)连接硬件:将JTAG和APB接口连接到开发板上。

串口JTAG使用说明

AVR JTAG下载HEX文件使用说明本文只介绍AVR JTAG下载HEX文件在AVR Studio环境下的下载方法,推荐使用。

并口下载线主要优点是电路简单,缺点主要有下载速度慢、不能在AVR Studio环境下使用。

具体差别在用了AVR JTAG 之后就知道了,现在一个标准的下载线也只要几十块钱和并口下载线没什么差别了。

此处所说的STK500下载线和AVR ISP下载线同属一类,它们使用相同的通信协议,STK500确切的说是一个学习板,AVR JTAG才是真正意义上的下载线。

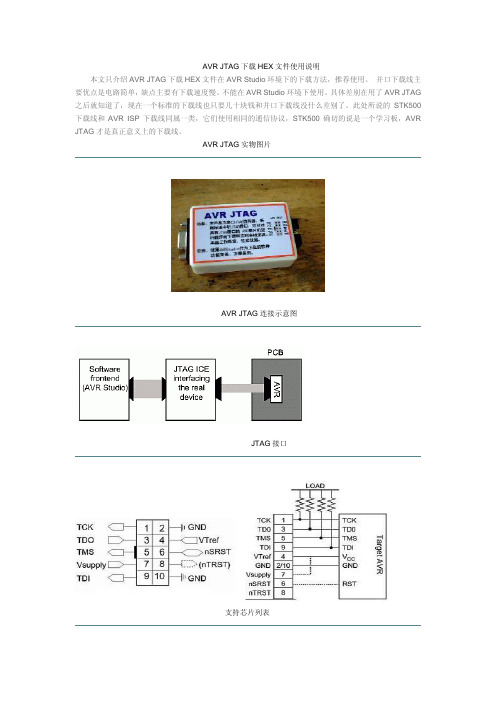

AVR JTAG实物图片AVR JTAG连接示意图JTAG接口支持芯片列表AVR JTAG下载线支持芯片型号非常多,这里就不一一列出了,只要AVR芯片支持ISP下载的都可以。

AVR JTAG下载HEX文件-操作方法:1、打开AVR Studio 软件,按下图操作。

2、在这里选择所用器件及连接端口,选择JTAG ICE,自动检测端口,点击Connect进入下一步。

3、下面窗口提示所用AVR ISP下载线固件版本与当前所用软件不同,提示要求升级AVR ISP下载线固件,如版本相同就不会出现下面的提示。

如你所用的AVR ISP下载线不支持在线升级功能的话,不要点确定要不AVR ISP下载线会死在那里不动了,直接点击取消跳过此步既可。

4、正常会进入下面编程(Program)界面。

主要包括有器件(Device)、编程模式(Programming mode)、Flash下载、EEPROM下载几个部分,最下面部分是信息窗口。

器件:用于选择器件和手工擦除器件。

编程模式:用于选择ISP和并口下载模式,由于此处用的是AVR JTAG下载线只支持ISP方式下载。

Erase Device Before擦除器件,选中此项在每次下载前会对将器件擦除。

需要同时烧写用户程序和引导程序时需要注意此处,正常情况下需选中此项。

Verify Devic写入校验,默认为选中。

fpga jtag手册

fpga jtag手册

FPGA JTAG接口是一种串行接口,用于对FPGA内部逻辑进行调试、配置和测试等功能。

以下是FPGA JTAG接口的基本使用手册:

连接方式:将JTAG电缆的一端连接到FPGA开发板上的JTAG接口,另一端连接到PC上的JTAG调试器。

确保连接稳定,避免在调试过程中出现断线或接触不良的情况。

配置JTAG接口:在开始调试之前,需要配置JTAG接口的参数,例如波特率、数据位、停止位等。

这些参数需要根据目标FPGA设备和JTAG调试器的要求进行设置。

启动调试:打开JTAG调试器软件,选择正确的设备型号和连接方式,然后点击“开始调试”按钮。

此时,调试器将与目标FPGA建立通信连接,并进入调试状态。

加载配置文件:在调试过程中,可能需要将配置文件加载到目标FPGA中。

可以通过JTAG接口将配置文件传输到目标FPGA中,或者在调试器软件中选择相应的配置文件进行加载。

运行和停止调试:在调试过程中,可以通过调试器软件控制目标FPGA的运行和停止。

可以单步执行、步进执行或全速运行目标FPGA的程序。

同时,还可以在调试过程中设置断点、观察寄存器和内存等操作。

结束调试:当调试完成后,可以通过调试器软件结束调试会话,并关闭JTAG接口的连接。

需要注意的是,使用FPGA JTAG接口进行调试需要一定的技术背景和经验。

在调试过程中,需要仔细检查连接线和设备参数设置,避免出现通信错误或配置错误等问题。

同时,也需要遵守相关的安全操作规程,确保不会损坏目标FPGA 或造成其他安全问题。

详细解读Zynq的三种启动方式(JTAG,SD,QSPI)

详细解读Zynq的三种启动方式(JTAG,SD,QSPI)本文介绍zynq上三种方式启动文件的生成和注意事项,包括只用片上RAM (OCM)和使用DDR3两种情况。

JTAG方式JTAG方式是调试中最常用的方式,在SDK中在Project Explorer窗口工程上右键-Debug As-Debug ConfiguraTIons可以看到以下窗口首次打开左边窗口中Xilinx C/C++ applicaTIon(GDB)下没有子项,这时双击Xilinx C/C++ applicaTIon(GDB)即可新建一个调试;这时右边窗口会自动填充如上图,若没有则手动填入;在右边ApplicaTIon窗口指定要下载调试的.elf文件;在右边STDIO Connection可以指定标准输入输出串口,即printf打印串口,若这里选择开发板上uart的com口,则调试时printf的信息打印到调试时Console窗口,同时也可从Console窗口输入数据,以此将数据通过串口发送到开发板上以上设置完成后点击Debug即可开始调试;若以上在Project Explorer窗口工程上右键-Run As-Run Configurations;配置与此类似,最后点击run即可开始运行,只是不是调试而是直接上板运行。

只用OCM只用OCM指不使用DDR3的方式,与使用DDR3的方式略有不同。

这里不用FSBL来加载PL部分的.bit文件和第二阶段启动程序(裸机程序),而直接用BootROM加载裸机程序到OCM,即将裸机程序当做FSBL来运行,当然还要以下处理才可以:包含进头文件:#include ps7_init.h在裸机程序main函数开始处调用:ps7_init()从design_1_wrapper_hw_platform_1目录复制ps7_init.c和ps7_init.h文件到裸机程序所在的src目录中注意:这里样调用ps7_init()只适用于只用OCM的情况,经测试打开DDR3后再这样调用会在ps7_init()中初始化失败,调试发现在初始化PLL时失败(原因未知)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

AVR JTAG下载HEX文件使用说明

本文只介绍AVR JTAG下载HEX文件在AVR Studio环境下的下载方法,推荐使用。

并口下载线主要优点是电路简单,缺点主要有下载速度慢、不能在AVR Studio环境下使用。

具体差别在用了AVR JTAG 之后就知道了,现在一个标准的下载线也只要几十块钱和并口下载线没什么差别了。

此处所说的STK500下载线和AVR ISP下载线同属一类,它们使用相同的通信协议,STK500确切的说是一个学习板,AVR JTAG才是真正意义上的下载线。

AVR JTAG实物图片

AVR JTAG连接示意图

JTAG接口

支持芯片列表

AVR JTAG下载线支持芯片型号非常多,这里就不一一列出了,只要AVR芯片支持ISP下载的都可以。

AVR JTAG下载HEX文件-操作方法:

1、打开AVR Studio 软件,按下图操作。

2、在这里选择所用器件及连接端口,选择JTAG ICE,自动检测端口,点击Connect进入下一步。

3、下面窗口提示所用AVR ISP下载线固件版本与当前所用软件不同,提示要求升级AVR ISP下载线固件,如版本相同就不会出现下面的提示。

如你所用的AVR ISP下载线不支持在线升级功能的话,不要点确定要不AVR ISP下载线会死在那里不动了,直接点击取消跳过此步既可。

4、正常会进入下面编程(Program)界面。

主要包括有器件(Device)、编程模式(Programming mode)、Flash下载、EEPROM下载几个部分,最下面部分是信息窗口。

器件:用于选择器件和手工擦除器件。

编程模式:用于选择ISP和并口下载模式,由于此处用的是AVR JTAG下载线只支持ISP方式下载。

Erase Device Before擦除器件,选中此项在每次下载前会对将器件擦除。

需要同时烧写用户程序和引导程序时需要注意此处,正常情况下需选中此项。

Verify Devic写入校验,默认为选中。

Flash:下载Flash文件,有选择文件(Input HEX File)、编程(Program)、校验(Verify)、读取(Read)。

EEPROM:下载EEPROM文件,包含内容与上面相同。

如果你是初学者,并不要求对器件进行熔丝等复杂配置,由此窗口将HEX文件写入器件就可以实验了。

其它系统时钟及看门狗等可先使用器件默认配置。

5、下图为熔丝配置(Fuses)界面,具体配置请参照熔丝配置部分。

6、下图为器件锁定配置(LockBits)界面,主要为设置对用户代码、程序区及引导区的保护等级。

7、下图为高级配置(Advanced)界面。

8、下图为AVR ISP下载线配置(Board)界面,主要对下载线进行相关设置。

由于工作在AVRISP模式,只ISP下载波特率可以使用,通常情况下设置为230.4kHz均可使用,如目标板装有晶振主频较高时可以提高此处下波特率,可以提高下载速度。

注:更改后需要点后面的写入(Write)才有效。

9、下图为自动编程(Auto)界面,可以在这里选择要操作的项目,然后按启动(Start)既可一次完成。

AVR ISP下载线-连接错误:

1、AVR ISP下载线,重复出现下面窗口。

问题原因:PC机与AVR ISP下载线连接不成功。

问题出在PC与AVR下载线之间,查看串口连接是否正确、AVR下载线是否上电。

3、AVR ISP下载线窗口弱出如下窗口。

问题原因:AVR ISP下载线与目标芯片连接不成功。

问题出在AVR ISP下载线与目标芯片之间,查看ISP接口是否正确、是不是芯片时钟被锁住了。

AVR JTAG仿真器-仿真模式:

1、打开AVR Studio 软件,按下图操作。

2、在打开图口中选择需要仿真程序的.cof仿真文件,注意编译环境也需要设置生成目标文件为cof文件。

这

个文件包含调试信息,可以在C源程序的环境下调试,如果打开的是hex,则只能在编译器生成的汇编语言下调试了。

点击“打开”进入下一步。

3、下面窗口提示工程文件保存位置,使用默认位置就行了,点击“保存”进入下一步。

4、软件弹出设置器件及仿真模式窗口,此处是AVR JTAG硬件仿真所以下面分别选择:调试模式为JTAG ICE、芯片型号为mega16、端口用自动就可以了。

点击“完成”进入下一步。

5、经过上面步骤如硬件连接没有问题,那么会进入正式仿真界面,界面如下图。

6、到这一步就可以进行程序调试了,再后面的详细操作方法可以参照书本或者查看AVR STUDIO技术手册:AVR Studio 中文使用说明。

AVR JTAG仿真器-连接错误:

1、AVR JTAG仿真器工作在下载模式,重复出现下面窗口。

问题原因:PC机与AVR JTAG仿真器连接不成功。

问题出在PC与AVR仿真器之间,查看串口连接是否正确、AVR仿真器是否上电。

2、AVR JTAG仿真器工作在仿真模式,重复出现下面窗口。

PC机与AVR JTAG仿真器连接不成功。

问题原因:PC机与AVR JTAG仿真器连接不成功。

问题出在PC与AVR仿真器之间,查看串口连接是否正确、AVR仿真器是否上电。

3、AVR JTAG仿真器工作在仿真模式,重复出现下面窗口。

问题原因:AVR JTAG仿真器与目标芯片连接不成功。

问题出在AVR JTAG仿真器与目标芯片之间,查看JTAG接口是否正确、AVR芯片是否打开JTAGEN熔丝位。