八位序列检测器设计

8位SARADC设计说明书

8位SAR ADC1关键名词解释文档中描述了12位ADC。

2功能概述图二。

1系统结构ADC子系统2包括一个8通道可配置模拟多路复用器(AMUX2)、一个可编程增益放大器(PGA2)和一个500ksps、8位分辨率逐次逼近型寄存器ADC,其中集成了一个跟踪保持电路。

AMUX2、PGA2和数据转换模式可由软件通过特殊功能寄存器进行配置。

仅当ADC2控制寄存器(ADC2_CN)的AD2EN位设为“1”时,ADC2子系统(8位ADC、采样保持和PGA)才使能。

当AD2EN位为“0”时,ADC2子系统处于低功耗关断模式。

ADC2有8个测量通道,由寄存器MUX_2SL选择通道。

PGA AMUX输出信号的放大系数由ADC2配置寄存器adc2 _ cf中的AMP2GN2-0决定,PGA可以通过软件编程为0.5、1、2、4,复位时的默认增益为0.5。

界面描述●3工作原理及电路性能分析3.1数字部分控制逻辑比较简单,主要总结控制逻辑的主要特点。

1)注意移位寄存器的第一位逻辑。

比较开始时,SAR的第一位设置为1,然后设置为0。

移位寄存器工作时只有一位是1,这就需要移位寄存器第一个触发器的输出Q端和输入D端有反馈逻辑。

2)当移位寄存器移位完成比较时,移位寄存器的下一位会发出完成信号通知数据寄存器,这样之前已经完成比较的位会一起输出。

同时,第一次转换后会通知采样信号,可以进行下一次采样。

3)双端差分输入和单端输入决定解码的最高位,通道配置寄存器提供通道配置信号,与ADC最高位形成决策逻辑。

4)移位寄存器和数据存储寄存器的复位信号也很重要,关系到ADC的启动。

3.2模拟部分3.2.1关于采样精度和采样时间SAR时钟频率为6MHz,所以比较器的延迟应为170ns,参考电压为 2.4v,比较器的分辨率为1/2 LSB = 4.6875mv,因此每级比较器的输出都有一个有限摆幅的反馈电路。

采样建立时间要求由下式给出:SA是建立精度,用LSB的分数表示(例如,0.25的建立精度相当于1/4 LSB)。

带有密码锁的八路信号电压自动巡测仪(江西省第24界大学电子设计大赛题目)

江西省大学生电子设计制作赛参赛规则与赛场纪律1、参赛选手抽签对号入座,在参赛证上填好所在学校和本人姓名,同时把学生证摆放在座位的右上角,供监考人员核对检查。

2、必须自带制作和检测工具,可带《电工电子实践指导》和《电子设计制作基础》参考书进场。

3、开赛时选手在前一小时内仔细看清楚赛题内容和要求,构思并设计电路原理图,器件连接图;按元器件清单核对品种、型号、数量(万能板与电源线在开赛一小时后发),如发现缺少,可先自行记录,因所发放的元器件多于作品的实需器件,待设计原理图、器件连接图后,若确实缺少器材,可在发万能板后的半小时内传字条给监考人员,经监考人员核对后可予以补发,此后不再无偿补发器件。

4、在参赛作品上不得使用自带导线和器件,要求采用裸线连接,杜绝锡拖焊的方法焊接器件,否则扣分。

5、每位选手必须独立设计、制作完成作品,不准互相讨论,不准互相帮助。

不许将场外制品带入赛场,否则予以没收,情节严重者取消参赛资格。

6、竞赛时间为连续7.5小时,中途不得随意离开赛场,需要临时离开考场时,必须经监考人员同意。

揭开题卷后的三小时内不得以任何方式结束竞赛、走出赛场大楼。

7、竞赛过程中应爱护公物,电烙铁一律用烙铁架,同时不要因短路引起赛场断电,否则,由此影响赛场竞赛时,取消该选手参赛资格。

在制作过程中,若有器件或工具损坏,可到元件服务处购买。

8、参赛选手应自备干粮和饮用水,场外人员不得以任何方式进场送物,杜绝借送饭、送工具等机会从中作弊。

9、参赛选手进赛场后手机、小灵通一律关机,在赛场内不得开机,违者取消参赛资格。

10、在竞赛过程中,监考人员每隔2小时向大家报时1次,竞赛结束时间一到,参赛选手必须立即停止作业。

把作品和参赛证一并装入塑料袋封好,参赛证不要折叠,应放在最外层,使监考人员验收时不开袋就能方便查看。

请注意,作品上不得蓄意留有记号,否则扣5芬直至参赛作品判为0分江西省第24届大学电子设计大赛题目带有密码锁的八路信号电压自动巡测仪一、题意参赛者在赛场提供的元器件中选用元器件,设计、制作一个自带密码锁的8路信号电压自动巡测仪。

8位数码扫描显示电路设计实验

实验一基本组合电路设计(1)实验目的:熟悉 Quartus U的文本输入设计法和原理图输入设计法,学习简单组合电路以及多层次电路的设计、仿真和硬件测试。

(2)实验内容:I.利用Quartus U完成2选1多路选择器的文本编辑输入。

【参考程序】:ENTITY mux21a ISPORT ( a, b, s: IN BIT;y : OUT BIT );END ENTITY mux21a;ARCHITECTURE one OF mux21a ISBEGINPROCESS (a,b,s)BEGINIF s = ' O' THEN y <= a ;ELSE y<= b ;END IF;END PROCESS;END ARCHITECTURE one ;n .将实验I中的2选1多路选择器生成一个元件 mux21a利用原理图输入设计方法实现图1-1的双2选1多路选择器,并将此文件放在同一目录中。

最后进行编译、仿真,并对其仿真波形作出分析说明。

川.对U进行引脚锁定及硬件下载测试。

建议选择实验电路模式5,用键1(PIOO, 引脚号为1)控制sO;用键2(PIO1,引脚号为2)控制s1; a3、a2和a1分别接clock5(引脚号为16)、clockO (引脚号为93)和clock2 (引脚号为17);输出信号outy接扬声器spker (引脚号为129)。

通过短路帽选择clock5接1024Hz 信号,clock0接256Hz信号,clock2接8Hz信号。

最后进行编译、下载和硬件测试实验(通过选择键1、键2、控制s0、s1,可使扬声器输出不同音调)。

(3)实验报告:1.实验U的原理图。

2•实验U的仿真波形报告分析说明。

3.实验川硬件测试的详细实验说明。

图1-1 双2选1多路选择器实验_二基本时序电路设计(1)实验目的:熟悉Quartus U的VHDL文本设计过程,学习简单时序电路的设计、仿真和硬件测试。

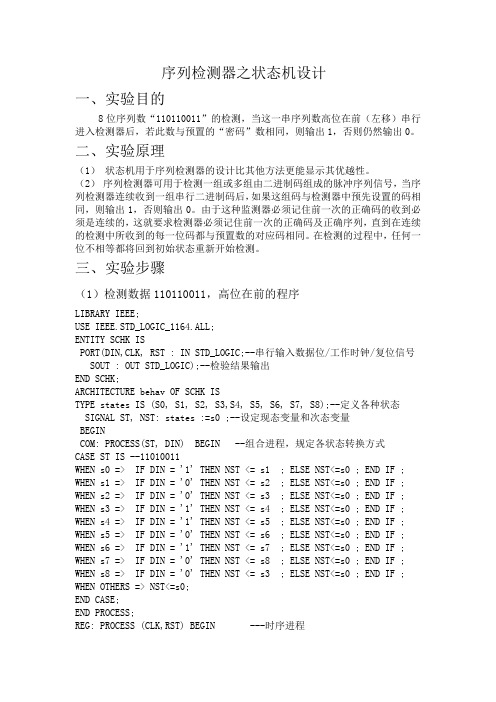

序列检测器之状态机设计

序列检测器之状态机设计一、实验目的8位序列数“110110011”的检测,当这一串序列数高位在前(左移)串行进入检测器后,若此数与预置的“密码”数相同,则输出1,否则仍然输出0。

二、实验原理(1)状态机用于序列检测器的设计比其他方法更能显示其优越性。

(2)序列检测器可用于检测一组或多组由二进制码组成的脉冲序列信号,当序列检测器连续收到一组串行二进制码后,如果这组码与检测器中预先设置的码相同,则输出1,否则输出0。

由于这种监测器必须记住前一次的正确码的收到必须是连续的,这就要求检测器必须记住前一次的正确码及正确序列,直到在连续的检测中所收到的每一位码都与预置数的对应码相同。

在检测的过程中,任何一位不相等都将回到初始状态重新开始检测。

三、实验步骤(1)检测数据110110011,高位在前的程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY SCHK ISPORT(DIN,CLK, RST : IN STD_LOGIC;--串行输入数据位/工作时钟/复位信号 SOUT : OUT STD_LOGIC);--检验结果输出END SCHK;ARCHITECTURE behav OF SCHK ISTYPE states IS (S0, S1, S2, S3,S4, S5, S6, S7, S8);--定义各种状态SIGNAL ST, NST: states :=s0 ;--设定现态变量和次态变量BEGINCOM: PROCESS(ST, DIN) BEGIN --组合进程,规定各状态转换方式CASE ST IS --11010011WHEN s0 => IF DIN = '1' THEN NST <= s1 ; ELSE NST<=s0 ; END IF ; WHEN s1 => IF DIN = '0' THEN NST <= s2 ; ELSE NST<=s0 ; END IF ; WHEN s2 => IF DIN = '0' THEN NST <= s3 ; ELSE NST<=s0 ; END IF ; WHEN s3 => IF DIN = '1' THEN NST <= s4 ; ELSE NST<=s0 ; END IF ; WHEN s4 => IF DIN = '1' THEN NST <= s5 ; ELSE NST<=s0 ; END IF ; WHEN s5 => IF DIN = '0' THEN NST <= s6 ; ELSE NST<=s0 ; END IF ; WHEN s6 => IF DIN = '1' THEN NST <= s7 ; ELSE NST<=s0 ; END IF ; WHEN s7 => IF DIN = '0' THEN NST <= s8 ; ELSE NST<=s0 ; END IF ; WHEN s8 => IF DIN = '0' THEN NST <= s3 ; ELSE NST<=s0 ; END IF ; WHEN OTHERS => NST<=s0;END CASE;END PROCESS;REG: PROCESS (CLK,RST) BEGIN ---时序进程IF RST='1' THEN ST <= s0;ELSIF CLK'EVENT AND CLK='1' THEN ST <= NST; END IF;END PROCESS REG;SOUT <= '1' WHEN ST=s8 ELSE '0' ;END behav ;(2)生成的RTL电路图如下所示:图(1)(3)生成symbol如图所示:图(2)(4)对其进行波形仿真得到波形如下所示:图(3)四、结果分析图(3)的波形显示,当有正确序列进入时,到了状态S8时,输出正确标志SOUT=1。

11100111的序列检测器

《电子设计基础》课程报告设计题目:序列检测器学生班级:电气1101学生学号:20115122学生姓名:代涛指导教师:刘春梅时间:2013/6/28一、 设计任务用D 触发器设计一个11100111的序列检测器。

二、设计要求用D 触发器设计序列检测器。

三、 设计内容1、设计思想由课程设计的题目可知,该电路输入为序列号,所以还需一个序列发生器,输出为脉冲信号,最后安一个LED 灯来检测脉冲。

由于输入序列号为8位的,所以需要3个D 触发器。

2、设计说明该电路的元器件主要由D 触发器,与、非、或门,电源,LED 灯组成。

输入的序列号经D 触发器和门电路组成的电路输出为脉冲信号,当输入的序列号为11100111就会产生高电平,使LED 灯亮。

3、系统方案由于方便,我令A=000,B=001,C=010,D=011,E=100,F=101,G=110,H=111。

X 为输入信号,Y 为输出信号。

0/01/1状态转换图从表上可以看出状态D和I是等价状态,可以合并。

所以可以将I一行去n+1根据真值表得到输入的表达式,下面用卡诺图进行化简。

D 2 Q 1 XQ 0 Q 200 01 11 10 00011110D 2=X —Q 2Q —1Q —0+X —Q —2Q 1Q 0+XQ 2Q —1Q 0+XQ 2Q 1Q —D 1 Q 1 XQ 0 Q 2 00 01 11 100001 1110D 1=X(Q 1+Q 0)D 0Q 1 X Q 0 Q 2D0=X(Q1+Q—0)+Q2Q—1Q—0Y=XQ1Q2Q34、设计方案(1)、序列发生器为了仿真能成功,我设计了一个序列发生器。

序列信号是把一组0、1数码按一定规则顺序排列的串行信号,该序列发生器能发出11100111的序列号,为了测试我连了个LED灯,当出现高电平时灯亮。

序列发生器发出的序列波形仿真(2)、序列检测器序列检测器是一种能够检测输入的一串二进制编码,当该二进制码与事先设定的码一致时,检测电路输出高电平,否则输出低电平。

数字逻辑实验 8_序列检测器

实验八序列检测器的设计与仿真一、实验要求1.用VHDL语言设计一个Mealy机以检测“1101001”序列;2.用VHDL语言设计一个Moore机以检测“1101001”序列;3.在文本编辑区使用VHDL硬件描述语言设计逻辑电路,再利用波形编辑区进行逻辑功能仿真,以此验证电路的逻辑功能是否正确。

二、实验内容用VHDL语言设计各一个mealy和moore状态机测试“1101001”位串的序列检测器,并通过仿真波形验证设计的功能是否正确。

三、实验过程由于在报告1中已经详尽描述了如何使用Quartus 2建立逻辑原理图和使用VHDL语言实现元件功能,所以本次的实验报告中便不再赘述上述内容,报告将主要就VHDL 语言描述实现元件的功能的过程进行阐述。

1.Mealy机选择File→New,弹出新建文本对话框,在该对话框中选择VHDL File并单击OK按钮,进入文本编辑窗口,输入VHDL代码。

library ieee;use ieee.std_logic_1164.all;entity melay isport(clk,rst,d: in std_logic;z: out std_logic);end melay;architecture arc of melay istype state_type is(s0,s1,s2,s3,s4,s5,s6);signal state: state_type;beginprocess(clk,rst)beginif rst= '1' thenstate<=s0;elsif (clk'event and clk ='1') thencase state is --1101001when s0 =>if d='1' thenstate<=s1;elsestate<=s0;end if;when s1=>if d='1' thenstate<=s2;elsestate<=s0;end if;when s2=>if d='0' thenstate<=s3;elsestate<=s2;end if;when s3=>if d='1' thenstate<=s4;elsestate<=s0;end if;when s4=>if d='0' thenstate<=s5;elsestate<=s1;end if;when s5=> --1101001if d='0' thenstate<=s6;elsestate<=s1;end if;when s6=>if d='1' thenstate<=s0;elsestate<=s0;end if;end case;end if;end process;process(state,d)begincase state iswhen s6=>if d='1' thenz<='1';elsez<='0';end if;when others=>z<='0';end case;end process;end arc;保存文件并编译,选择菜单File→New,选择Vector Waveform File新建波形图,添加节点,参数设置为:End Time=2us, Grip size=50ns。

基于VHDL语言的八位时序奇偶校验器的设计

eg (o k t n de l )h c c e

p e e t sa e = n x — t t ; rs n_ tt< e t sa e

e di n £ e d p o e sfrt n rc s is ; sc n :rc s pe e ts a e e o dpo e s r sn t t ,

_

es le

ne t x

—

sae = 3 tt< s ; b 8 <= : e di n

as ) i bg en i

wa n n <= 0 ; rig

c s r s n sa e i a e p e e t tt s

( 3 4s , , , , ,l , s, , s B s s sO s 56789

n x t t < s ; e t sa e = 4 b a <= :

种 检 s ; rs n ~ t t < O e sfrsn li ii g

_

奇 偶校 验 码 是 一 种 通 过 增 加 冗余 位 使 得 码 字 中 ” ” 个 数 恒 为 奇 1的 数 或偶 数 的编 码 方 法 。其 局 限性 是 只 能 检 测 出 奇 数 个 错 误 . 由 于 其 但 简 单 方便 。 数 据 传 输 的 差 错 控 制 上 仍 然 得 到 广 泛 的 使 用 。 以 前 的 奇 在 偶校 验 器 太 多 采 用 通 用 逻 辑 元 器 件 进 行 设 计 。 致 了 设 计 和 调 试 过 程 导 冗 长 、 统稳 定 性 不 高 , 常 不 便 。如 今 , 着 以 F G 和 C L 为 代 系 非 随 PA PD 表 的可 编 程 A I SC技术 的 日趋 成 熟 和完 善 。用 户 可 以完 全 根 据 自 己 的 需 要 . E A 技 术 作 为 开 发 手 段 。 一 块 F GA或 C L 以 D 用 P P D设 计 出 符 合 自已需 要 的 芯 片 。

8通道位移检测仪的设计

8通道位移检测仪的设计1、引言在机械系统中,往往需要对各种机械量进行测量,由于许多机械量能够变换成位移,故选用适当的位移传感器就能测量出许多机械量。

差动变压器将机械位移转换成与它成比例的电压或电流信号,是一种非常便利的位移检测器。

差动变压器式(LVDT)位移传感器广泛应用于工业现场和测试领域, 如过程检测和自动控制形变测量等, 适用于油污、光照等恶劣环境。

这种传感器可靠而耐用, 但选用它监控机械位移量, 还需设计与传感器配套的测量装置。

差动变压器的结构形式较多,但其工作原理却基本一样,都是将被测量的变化转换成变压器的互感变化,变压器初级线圈输入交流电压,次级线圈则感应出电动势。

通过结构优化,差动变压器可以测量0.01μm~500mm的机械位移,并具有测量精度高、灵敏度高、结构简单、性能可靠等优点。

2、差动变压器的基本结构以螺管形差动变压器为例,介绍差动变压器的基本工作原理。

螺管形差动变压器的结构如图1所示。

它由初级线圈p,两个次级线圈S1、S2和插入线圈中央的圆柱形铁芯b组成,其结构形式又有三段式和两段式之分。

图1螺管形差动变压器结构原理(a)三段式(b)二段式(c)电量原理图差动变压器的线圈连接如图1c所示。

次级线圈S1和S2反极性连接。

当初级线圈p加上某一频率的正弦交流电压Ui后,次级线圈产生感应电压为U1和U2,它们的大小与铁芯在线圈内的位置有关。

U1和U2反极性连接便得到输出电压U0。

当铁芯位于线圈中心位置时,U1=U2,U0=0;当铁芯向上移动时(见图1c),U1>U2,U0>0,则M1大,M2小(M1、M2为互感系数);当铁芯向下移动时(见图1c),U1<U2,U0<0,则M1小,M2大。

铁芯偏离中心位置时,输出电压U0随着铁心偏离中心位置的大小,U1或U2逐渐增大,移动方向不同,相位相差180°,如图2所示。

因此,测量出输出电压的大小和相位就能知道铁芯移动的距离和方向。

图2差动变压器输出电压的特性曲线由上图可知,当x=0时,其输出电压ΔU≠0,而是Uδ,此值约为1mV~几十mV,并称为零位电压。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

八位序列检测器设计

班级:1302012

学号:

姓名:郭春晖

一、设计说明

使用quartus软件进行仿真和验证,并且还可以检测其他的序列,只需要修改一部分代码就可以实现。

二、方案

工作原理:基于FPGA的多路脉冲序列检测器的设计方案,使用VHDL语言设计时序逻辑电路,先设计序列发生器产生序列:01010;再设计序列检测器,检测序列发生器产生序列,若检测到信号与预置待测信号相同,则输出“1”,否则输出“0”,并且将检测到的信号的显示出来。

三、单元模块设计

1、序列信号发生器

序列信号是指在同步脉冲作用下循环地产生一串周期性的二进制信号。

利用状态机设计,首先定义一个数据类型FSM_ST它的取值为st0到st15的16个状态。

序列信号发生器的代码如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY SHK IS

PORT (CLK,RST :IN STD_LOGIC; CO :OUT STD_LOGIC );

END SHK;

ARCHITECTURE behav OF SHK IS

TYPE FSM_ST IS (s0,s1,s2,s3,s4,s5,s6,s7,s8,s9,s10,s11,s12,s13,s14,s15); SIGNAL REG:FSM_ST;

SIGNAL Q:STD_LOGIC;

BEGIN

PROCESS(CLK,RST)

BEGIN

IF RST ='1' THEN REG<=s0;Q<='0';

ELSIF CLK'EVENT AND CLK='1' THEN

CASE REG IS

WHEN s0=> Q<='1'; REG<=s1; WHEN s1=> Q<='0';REG<=s2; WHEN s2=> Q<='1';REG<=s3; WHEN s3=> Q<='1';REG<=s4; WHEN s4=> Q<='0';REG<=s5; WHEN s5=> Q<='1';REG<=s6; WHEN s6=> Q<='0';REG<=s7; WHEN s7=> Q<='0';REG<=s8; WHEN s8=> Q<='0';REG<=s9; WHEN s9=> Q<='1';REG<=s10; WHEN s10=> Q<='1';REG<=s11; WHEN s11=> Q<='0';REG<=s12; WHEN s12=> Q<='1';REG<=s13; WHEN s13=> Q<='0';REG<=s14;

WHEN s14=> Q<='1';REG<=s15; WHEN s15=> Q<='0';REG<=s0;

WHEN OTHERS=>REG<=s0;Q<='0';

END CASE;

END IF;

END PROCESS; CO<=Q;

END behav;

转化成可调用的元件:

波形仿真如下:

2、序列检测器

脉冲序列检测起可用于检测一组或多组二进制码组成的脉冲序列信号,当序列检测器连续接收到一组穿行二进制码后,如果这组码与检测器中预先设置的码相同,则输出1,否则输出0。

由于这种检测的关键在于正确码的收到必须是连续的,这就要求检测器必须记住前一次的正确码及正确的序列,直到连续的检测中所收到的每一位码都与预置数的对应码相同。

在检测过程中,任何一位不相等将回到初始状态重新开始检测。

序列检测器的代码如下:

library ieee;

use ieee.std_logic_1164.all;

entity SCHK1 is

port(datain,clk:in std_logic;

t: in std_logic_vector (4 downto 0);

q:out std_logic;

cq: out std_logic_vector (4 downto 0));

end SCHK1;

architecture rt1 of SCHK1 is

signal reg:std_logic_vector(4 downto 0);

begin

process(clk)

variable t1:std_logic_vector (4 downto 0);

begin

if clk'event and clk='1' then

reg(0)<=datain;

reg(4 downto 1)<=reg(3 downto 0) ;

end if;

t1:=t;

if reg=t1 then q<='1' ; else q<='0';

cq<=reg;

end if;

end process;

end rt1;

可调用的元件:

图3.3

波形仿真如下:

3、计数器

利用序列检测器产生的信号(1和0)作为计数器模块的时钟信号,产生的信号0、1变化,形成类似的CLK信号,实现计数器计数。

计数器的代码如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY COUNT IS

PORT (CLK, EN,RST :IN STD_LOGIC; Q1:OUT

STD_LOGIC_VECTOR(3 DOWNTO 0);

Q2:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); COUT: OUT STD_LOGIC );

END ENTITY COUNT;

ARCHITECTURE ONE OF COUNT IS BEGIN

PROCESS(CLK,EN,RST)

VARIABLE CQI:STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

IF RST='1' THEN CQI:= (OTHERS=>'0');

ELSIF CLK'EVENT AND CLK='1' THEN

IF EN='1' THEN

IF CQI<153 THEN

IF CQI(3 DOWNTO 0)=9 THEN CQI:=CQI +7; --高位进位

ELSE CQI := CQI+1;

END IF;

ELSE CQI:= (OTHERS=>'0');

END IF;

END IF;

END IF;

IF CQI=153 THEN COUT<='1';

ELSE COUT<='0';

END IF;

Q1<=CQI(3 DOWNTO 0); Q2<=CQI(7 DOWNTO 4);

END PROCESS COUNT; END ARCHITECTURE ONE;

可调用的元件:

波形仿真如下:

4、顶层文件设计

通过前面的准备,我们得到了3个模块,即序列信号发生器、序列检测器、计数器。

在此,我们运用原理图法来生成顶层实体。

即将上述3个模块,通过我们的设计软件,生成可以移植,调用的原理图文件,在将其在顶层设计中直接调用即可。

本次设计生成的顶层实体如下图所示:

四波形仿真与验证1、时序仿真

置入待检测序列:

仿真结果:

2、管脚连接

Node Name Location

1 count[3] PIN_J2

2 count[2] PIN_J3

3 count[1] PIN_H1

4 count[0] PIN_F2

5 date[7] PIN_J6

6 date[6] PIN_H5

7 date[5] PIN_H6

8 date[4] PIN_G4

9 date[3] PIN_G5

10 date[2] PIN_J7

11 date[1] PIN_H7

12 date[0] PIN_E3

13 error PIN_J1 3、结果分析:

输入待测序列若有检测的序列则会加一,之后继续检测。