数字电子技术基础试题及答案(1)

数字电子技术基础习题及答案

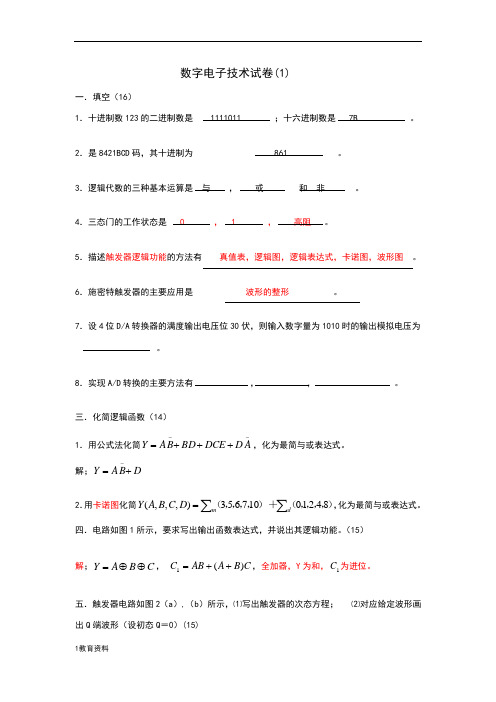

数字电子技术试卷(1)一.填空(16)1.十进制数123的二进制数是 1111011 ;十六进制数是 7B 。

2.是8421BCD 码,其十进制为 861 。

3.逻辑代数的三种基本运算是 与 , 或 和 非 。

4.三态门的工作状态是 0 , 1 , 高阻 。

5.描述触发器逻辑功能的方法有 真值表,逻辑图,逻辑表达式,卡诺图,波形图 。

6.施密特触发器的主要应用是 波形的整形 。

7.设4位D/A 转换器的满度输出电压位30伏,则输入数字量为1010时的输出模拟电压为 。

8.实现A/D 转换的主要方法有 , , 。

三.化简逻辑函数(14)1.用公式法化简--+++=A D DCE BD B A Y ,化为最简与或表达式。

解;D B A Y +=-2.用卡诺图化简∑∑=mdD C B A Y ),,,,()+,,,,(84210107653),,,(,化为最简与或表达式。

四.电路如图1所示,要求写出输出函数表达式,并说出其逻辑功能。

(15)解;C B A Y ⊕⊕=, C B A AB C )(1++=,全加器,Y 为和,1C 为进位。

五.触发器电路如图2(a ),(b )所示,⑴写出触发器的次态方程; ⑵对应给定波形画出Q 端波形(设初态Q =0)(15)解;(1)AQ Q Q n +=-+1,(2)、A Q n =+1六.试用触发器和门电路设计一个同步的五进制计数器。

(15)七.用集成电路定时器555所构成的自激多谐振荡器电路如图3所示,试画出V O ,V C 的工作波形,并求出振荡频率。

(15)数字电子技术试卷(2)二.填空(16)1.十进制数的二进制数是;十六进制数是。

2.逻辑代数中逻辑变量得取值为 0、1 。

3.组合逻辑电路的输出状态只与当前输入有关而与电路原状态无关。

4.三态门的输出有0、1、高阻,三种状态,当多个三态门的输出端连在一根总线上使用时,应注意只能有1个三态门被选通。

5.触发器的基本性质有有两个稳态,在触发信号作用下状态可相互转变,有记忆功能6.单稳态触发器的主要应用是延时。

数字电子技术基础试卷及答案套

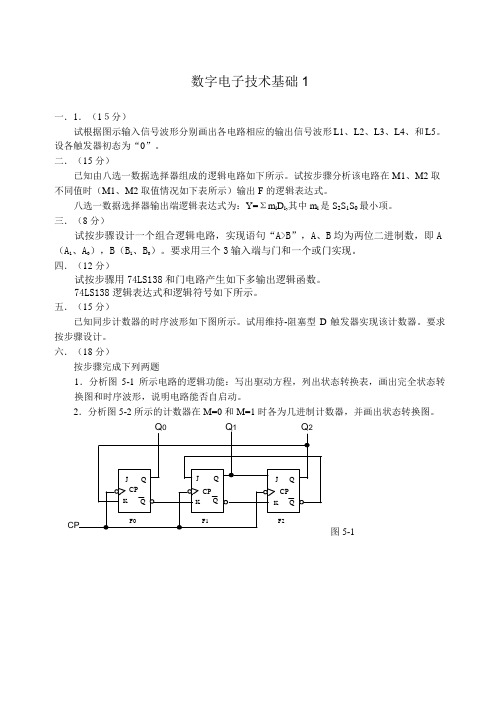

数字电子技术基础1一.1.(15分)试根据图示输入信号波形分别画出各电路相应的输出信号波形L1、L2、L3、L4、和L5。

设各触发器初态为“0”。

二.(15分)已知由八选一数据选择器组成的逻辑电路如下所示。

试按步骤分析该电路在M1、M2取不同值时(M1、M2取值情况如下表所示)输出F的逻辑表达式。

八选一数据选择器输出端逻辑表达式为:Y=Σm i D i,其中m i是S2S1S0最小项。

三.(8分)试按步骤设计一个组合逻辑电路,实现语句“A>B”,A、B均为两位二进制数,即A (A1、A0),B(B1、B0)。

要求用三个3输入端与门和一个或门实现。

四.(12分)试按步骤用74LS138和门电路产生如下多输出逻辑函数。

74LS138逻辑表达式和逻辑符号如下所示。

五.(15分)已知同步计数器的时序波形如下图所示。

试用维持-阻塞型D触发器实现该计数器。

要求按步骤设计。

六.(18分)按步骤完成下列两题1.分析图5-1所示电路的逻辑功能:写出驱动方程,列出状态转换表,画出完全状态转换图和时序波形,说明电路能否自启动。

2.分析图5-2所示的计数器在M=0和M=1时各为几进制计数器,并画出状态转换图。

图5-1图5-2七.八.(10分) 电路下如图所示,按要求完成下列问题。

1.指出虚线框T1中所示电路名称.2.对应画出V C 、V 01、A 、B 、C 的波形。

并计算出V 01波形的周期T=?。

数字电子技术基础2一.(20分)电路如图所示,晶体管的β=100,Vbe=0.7v 。

(1)求电路的静态工作点;(2) 画出微变等效电路图, 求Au 、r i 和r o ;(3)若电容Ce 开路,则将引起电路的哪些动态参数发生变化?并定性说明变化趋势. 二.(15分)求图示电路中a U 、bU 、b U 、c U 及L I 。

三.(8分)逻辑单元电路符号和具有“0”、“1”逻辑电平输入信号X 1如下图所示,试分别画出各单元电路相应的电压输出信号波形Y 1、Y 2、Y 3。

数字电子技术基础试题及答案一

数字电子技术基础试题及答案一TTA standardization office【TTA 5AB- TTAK 08- TTA 2C】数字电子技术基础期末考试试卷1. 时序逻辑电路一般由 和 两分组成。

2. 十进制数(56)10转换为二进制数为 和十六进制数为 。

3. 串行进位加法器的缺点是 ,想速度高时应采用 加法器。

4. 多谐振荡器是一种波形 电路,它没有稳态,只有两个 。

5. 用6个D 触发器设计一个计数器,则该计数器的最大模值M= 。

1.写出函数F (A,B,C,D) =A B C D E ++++的反函数。

2.证明逻辑函数式相等:()()BC D D B C AD B B D ++++=+ 3.已知逻辑函数F= ∑(3,5,8,9,10,12)+∑d(0,1,2) (1)化简该函数为最简与或式:(2)画出用两级与非门实现的最简与或式电路图: 4.555定时器构成的多谐振动器图1所示,已知R1=1KΩ,R2=Ω,C=μF 。

试求脉冲宽度T ,振荡频率f 和占空比q 。

图15.某地址译码电路如图2所示,当输入地址变量A7-A0的状态分别为什么状态 时,1Y 、6Y 分别才为低电平(被译中)。

………………………密……………………封…………………………装…………………订………………………线……………………… 学院 专业(班级) 姓名 学号……………………6.触发器电路就输入信号的波形如图3所示,试分别写出D触发器的Q和Q1的表达式,并画出其波形。

图D= Q n+1=Q1=7. 已知电路如图4所示,试写出:①驱动方程;②状态方程;③输出方程;④状态表;⑤电路功能。

图41.设计一个三变量偶检验逻辑电路。

当三变量A、B、C输入组合中的“1”的个数为偶数时F=1,否则F=0。

选用8选1数选器或门电路实现该逻辑电路。

要求:(1)列出该电路F(A,B,C)的真值表和表达式;(2)画出逻辑电路图。

A B C F2.试用74161、3-8译码器和少量门电路,实现图5所示波形VO1、VO2,其中CP为输入波形。

数字电子技术试题及答案(题库)

数字电子技术基础试题(一)一、填空题 : (每空1分,共10分)1. (30.25) 10 = ( ) 2 = ( ) 16 。

2 . 逻辑函数L = + A+ B+ C +D = 。

3 . 三态门输出的三种状态分别为:、和。

4 . 主从型JK触发器的特性方程= 。

5 . 用4个触发器可以存储位二进制数。

6 . 存储容量为4K×8位的RAM存储器,其地址线为条、数据线为条。

二、选择题: (选择一个正确的答案填入括号内,每题3分,共30分 )1.设图1中所有触发器的初始状态皆为0,找出图中触发器在时钟信号作用下,输出电压波形恒为0的是:()图。

图 12.下列几种TTL电路中,输出端可实现线与功能的电路是()。

A、或非门B、与非门C、异或门D、OC门3.对CMOS与非门电路,其多余输入端正确的处理方法是()。

A、通过大电阻接地(>1.5KΩ)B、悬空C、通过小电阻接地(<1KΩ)D、通过电阻接V CC4.图2所示电路为由555定时器构成的()。

A、施密特触发器B、多谐振荡器C、单稳态触发器D、T触发器5.请判断以下哪个电路不是时序逻辑电路()。

图2A、计数器B、寄存器C、译码器D、触发器6.下列几种A/D转换器中,转换速度最快的是()。

图2A、并行A/D转换器B、计数型A/D转换器C、逐次渐进型A/D转换器D、双积分A/D转换器7.某电路的输入波形 u I 和输出波形 u O 如图 3所示,则该电路为()。

图3A、施密特触发器B、反相器C、单稳态触发器D、JK触发器8.要将方波脉冲的周期扩展10倍,可采用()。

A、10级施密特触发器B、10位二进制计数器C、十进制计数器D、10位D/A转换器9、已知逻辑函数与其相等的函数为()。

A、B、C、D、10、一个数据选择器的地址输入端有3个时,最多可以有()个数据信号输出。

A、4B、6C、8D、16三、逻辑函数化简(每题5分,共10分)1、用代数法化简为最简与或式Y= A +2、用卡诺图法化简为最简或与式Y= + C +A D,约束条件:A C + A CD+AB=0四、分析下列电路。

数字电子技术试卷及答案(1)

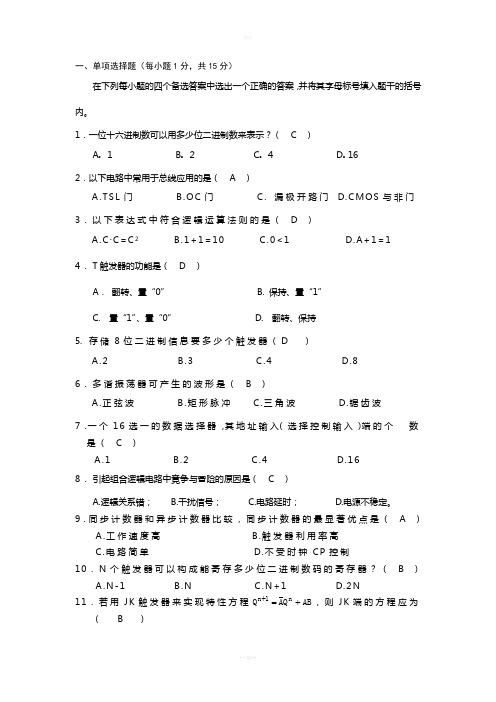

一、单项选择题(每小题1分,共15分)在下列每小题的四个备选答案中选出一个正确的答案,并将其字母标号填入题干的括号内。

1.一位十六进制数可以用多少位二进制数来表示?( C )A . 1B . 2C . 4D . 16 2.以下电路中常用于总线应用的是( A )A.T S L 门B.O C 门C. 漏极开路门D.C M O S 与非门 3.以下表达式中符合逻辑运算法则的是( D )A.C ·C =C 2B.1+1=10C.0<1D.A +1=1 4.T 触发器的功能是( D )A . 翻转、置“0” B. 保持、置“1” C. 置“1”、置“0” D. 翻转、保持 5. 存储8位二进制信息要多少个触发器(D )A.2B.3C.4D.8 6.多谐振荡器可产生的波形是( B )A.正弦波B.矩形脉冲C.三角波D.锯齿波 7.一个16选一的数据选择器,其地址输入(选择控制输入)端的个 数是( C )A.1B.2C.4D.16 8.引起组合逻辑电路中竟争与冒险的原因是( C )A.逻辑关系错;B.干扰信号;C.电路延时;D.电源不稳定。

9.同步计数器和异步计数器比较,同步计数器的最显著优点是( A ) A.工作速度高 B.触发器利用率高C.电路简单D.不受时钟C P 控制10.N 个触发器可以构成能寄存多少位二进制数码的寄存器?( B ) A.N -1 B.N C.N +1 D.2N11.若用J K 触发器来实现特性方程AB Q A Q n 1n +=+,则J K 端的方程应为( B )A.J =A B ,K =B AB.J =A B ,K =B AC.J =B A +,K =A BD.J =B A ,K =A B12.一个无符号10位数字输入的DA C ,其输出电平的级数是( C )A.4B.10C.1024D.10013.要构成容量为4K ×8的RAM ,需要多少片容量为256×4的RAM ?( D )A.2B.4C.8D.3214.随机存取存储器R A M 中的内容,当电源断掉后又接通,则存储器中的内容将如何变换?( C )A.全部改变B.全部为1C.不确定D.保持不变 15.用555定时器构成单稳态触发器,其输出的脉宽为( B )A.0.7RC ;B.1.1RC ;C.1.4RC ;D.1.8RC ;二、多项选择题(每小题1分,共5分)在下列每小题的四个备选答案中有二至四个正确答案,请将正确答案全部选出并将其字母标号填入题干的括号内;少选错选都不得分。

《数字电子技术基础》试题及参考答案_shijuan1

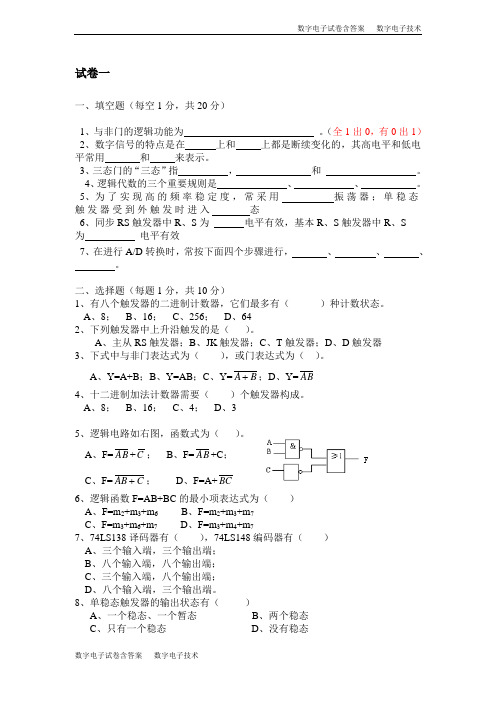

试卷一一、填空题(每空1分,共20分)1、与非门的逻辑功能为。

(全1出0,有0出1)2、数字信号的特点是在上和上都是断续变化的,其高电平和低电平常用和来表示。

3、三态门的“三态”指,和。

4、逻辑代数的三个重要规则是、、。

5、为了实现高的频率稳定度,常采用振荡器;单稳态触发器受到外触发时进入态6、同步RS触发器中R、S为电平有效,基本R、S触发器中R、S为电平有效7、在进行A/D转换时,常按下面四个步骤进行,、、、。

二、选择题(每题1分,共10分)1、有八个触发器的二进制计数器,它们最多有()种计数状态。

A、8;B、16;C、256;D、642、下列触发器中上升沿触发的是()。

A、主从RS触发器;B、JK触发器;C、T触发器;D、D触发器3、下式中与非门表达式为(),或门表达式为()。

A、Y=A+B;B、Y=AB;C、Y=BA+;D、Y=AB4、十二进制加法计数器需要()个触发器构成。

A、8;B、16;C、4;D、35、逻辑电路如右图,函数式为()。

A、F=AB+C;B、F=AB+C;AB+;D、F=A+BCC、F=C6、逻辑函数F=AB+BC的最小项表达式为()A、F=m2+m3+m6B、F=m2+m3+m7C、F=m3+m6+m7D、F=m3+m4+m77、74LS138译码器有(),74LS148编码器有()A、三个输入端,三个输出端;B、八个输入端,八个输出端;C、三个输入端,八个输出端;D、八个输入端,三个输出端。

8、单稳态触发器的输出状态有()A、一个稳态、一个暂态B、两个稳态C、只有一个稳态D、没有稳态三、判断(每题1分,共10分):1、逻辑变量的取值,1比0大。

(×)2、对于MOS门电路多余端可以悬空。

(×)3、计数器的模是指对输入的计数脉冲的个数。

(×)4、JK触发器的输入端J 悬空,则相当于J = 0。

(×)5、时序电路的输出状态仅与此刻输入变量有关。

数字电子技术基础--第一章练习题及参考答案

第一章数字电路基础第一部分基础知识一、选择题1.以下代码中为无权码的为。

A. 8421BCD码B. 5421BCD码C.余三码D.格雷码2.以下代码中为恒权码的为。

A.8421BCD码B. 5421BCD码C.余三码D.格雷码3.一位十六进制数可以用位二进制数来表示。

A.1B.2C.4D. 164.十进制数25用8421BCD码表示为。

A.10 101B.0010 0101C.100101D.101015.在一个8位的存储单元中,能够存储的最大无符号整数是。

A.(256)10B.(127)10C.(FF)16D.(255)106.与十进制数(53.5)10等值的数或代码为。

A.(0101 0011.0101)8421BCDB.(35.8)16C.(110101.1)2D.(65.4)87.矩形脉冲信号的参数有。

A.周期B.占空比C.脉宽D.扫描期8.与八进制数(47.3)8等值的数为:A. (100111.011)2B.(27.6)16C.(27.3 )16D. (100111.11)29.常用的B C D码有。

A.奇偶校验码B.格雷码C.8421码D.余三码10.与模拟电路相比,数字电路主要的优点有。

A.容易设计B.通用性强C.保密性好D.抗干扰能力强二、判断题(正确打√,错误的打×)1. 方波的占空比为0.5。

()2. 8421码1001比0001大。

()3. 数字电路中用“1”和“0”分别表示两种状态,二者无大小之分。

()4.格雷码具有任何相邻码只有一位码元不同的特性。

()5.八进制数(18)8比十进制数(18)10小。

()6.当传送十进制数5时,在8421奇校验码的校验位上值应为1。

()7.在时间和幅度上都断续变化的信号是数字信号,语音信号不是数字信号。

()8.占空比的公式为:q = t w / T,则周期T越大占空比q越小。

()9.十进制数(9)10比十六进制数(9)16小。

数字电子技术试题及答案试题库

数字电子技术根底试题〔一〕一、填空题 : 〔每空1分,共10分〕1. (30.25) 10 = ( ) 2 = ( ) 16 。

2 . 逻辑函数L = + A+ B+ C +D = 。

3 . 三态门输出的三种状态分别为:、和。

4 . 主从型JK触发器的特性方程= 。

5 . 用4个触发器可以存储位二进制数。

6 . 存储容量为4K×8位的RAM存储器,其地址线为条、数据线为条。

二、选择题: (选择一个正确的答案填入括号,每题3分,共30分 )1.设图1中所有触发器的初始状态皆为0,找出图中触发器在时钟信号作用下,输出电压波形恒为0的是:〔〕图。

图 12.以下几种TTL电路中,输出端可实现线与功能的电路是〔〕。

A、或非门B、与非门C、异或门D、OC门3.对CMOS与非门电路,其多余输入端正确的处理方法是〔〕。

A、通过大电阻接地〔>1.5KΩ〕B、悬空C、通过小电阻接地〔<1KΩ〕D、通过电阻接V CC4.图2所示电路为由555定时器构成的〔〕。

A、施密特触发器B、多谐振荡器C、单稳态触发器D、T触发器5.请判断以下哪个电路不是时序逻辑电路〔〕。

图2A、计数器B、存放器C、译码器D、触发器6.以下几种A/D转换器中,转换速度最快的是〔〕。

图2A、并行A/D转换器B、计数型A/D转换器C、逐次渐进型A/D转换器D、双积分A/D转换器7.*电路的输入波形 u I 和输出波形 u O 如图 3所示,则该电路为〔〕。

图3A、施密特触发器B、反相器C、单稳态触发器D、JK触发器8.要将方波脉冲的周期扩展10倍,可采用〔〕。

A、10级施密特触发器B、10位二进制计数器C、十进制计数器D、10位D/A转换器9、逻辑函数与其相等的函数为〔〕。

A、B、C、D、10、一个数据选择器的地址输入端有3个时,最多可以有〔〕个数据信号输出。

A、4B、6C、8D、16三、逻辑函数化简〔每题5分,共10分〕1、用代数法化简为最简与或式Y= A +2、用卡诺图法化简为最简或与式Y= + C +A D,约束条件:A C + A CD+AB=0四、分析以下电路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

5.某地址译码电路如图2所示,当输入地址变量 A7-A0的状态分别为什么状态时,丫1、丫6分别才为低电平(被译中)数字电子技术基础期末考试试卷一、填空题1. 时序逻辑电路一般由 ________________ 和 _______________ 两分组成。

2. 十进制数(56) 10转换为二进制数为 ____________ 和十六进制数为 __________3. 串行进位加法器的缺点是 _________ ,想速度高时应采用 ____________ 加法器<4. 多谐振荡器是一种波形 _________ 电路,它没有稳态,只有两个 ______________5. 用6个D 触发器设计一个计数器,则该计数器的最大模值M ________________二、化简、证明、分析综合题:1. 写出函数F (A,B,C,D) = A B C D E 的反函数2.证明逻辑函数式相等: BC D D(B C)(AD B) B D3. 已知逻辑函数 F= E( 3,5,8,9 , 10, 12) +E d(0,1,2) (1) 化简该函数为最简与或式:(2) 画出用两级与非门实现的最简与或式电路图:4. 555定时器构成的多谐振动器图1所示,已知R 1=1K Q , R 2=8.2K Q , C=0.1卩F 试求脉冲宽度T ,振荡频率f 和占空比q 。

)级 班 ( 业 专M As As 扣 As6•触发器电路就输入信号的波形如图 3所示,试分别写出D 触发器的Q 和Q1 的表达式,并画出其波形。

Q n+1=7.已知电路如图4所示,试写出: ① 驱动方程; ② 状态方程; ③ 输出方程; ④ 状态表; ⑤ 电路功能。

二、设计题:(每10分,共20分)1 •设计一个三变量偶检验逻辑电路。

当三变量 A B C 输入组合中的“ T 的 个数为偶数时F=1,否则F=0。

选用8选1数选器或门电路实现该逻辑电路。

要求:(1)列出该电路F(A,B,C)的真值表和表达式; (2)画出逻辑电路图2 .试用74161、3-8译码器和少量门电路,实现图 5所示波形V01 VO2 其中CP 为输入波形。

要求:1 ARd O E營_TLnJTTLTLD= J -Q i =(1) 列出计数器状态与V01、V02的真值表;(2) 画出逻辑电路图。

,1 ,2 3 4 5 5 7 8 5 10 11畀nrurLTLn^n-ru^urLTLn m i i I ______________ ___________________________________________________________________________________________________ _______ » I图5数字电路期末考试试卷评分标准一、填空题:(每题2分,共10 分)1. 存储电路,组合电路。

2. 111000 ,383. 速度慢,超前进位4. 产生,暂稳态5. 32二、化简、证明、分析综合题:(每小题10分,共70分)1.解: F A B C D E 3分A?(B C D E) 4分A B A C AgDgE 3分2.证明:左边BC D (B C)(AD B) 3分BC D BAD CAD BC 3分(BC BC) D(1 BA CA) 2分B D第3页共6页2分原式成立第3页共6页2分3•解:(1)化简该函数为最简与或式:解:---------- 2分---------- 2分由卡诺图可得:F AgB AgCgD AgCcP BgD BgD ---------------------------- 2 分(2)画出用两级与非门实现的最简与或式电路图:F AgB AgCgp AgCgP BgC BgPF AgB AgCgp AgCgp BgC BgP 1分F AgB? AgCgp ?AgCgP?BgC ?BgP 1分则可得电路图如下:----- ----------- 2-------------------------------------------------------------------- F4.解:3 6T i=0.7 ( R i R2 ) • C=0.7 ( 1+8.2) 10 0.1 10-=0.644ms ---2 分36T=0.7 ( R 1 2R 2) • C=0.7 (1+2 8.2) 100.1 10-=1.218ms---3 分q=T1TR 1 R 2 0.644 52 %---------------- 2R 1 2R 21.2185 .解:Y i S 1S 2gS 3gmiqm 为A 2,A,A o 的最小项) 2分图中 SA 7, S 2 A 6A 5 , S 3A ^A 31 分当 S 1,S 2 S 3 0时: Y i m ii 0~72 分当A , , A 1 , A J 001和110时Y 1和Y e 分别被选中 ---------- -----1 分 既:A 7 1; A 1, A 1,A 4 0, A 0时,且A 2, A 1, A 0 001和110时Y 1和丫6分别被选中; -------------- 2 当"As A 5A 4A 3A 2A 1A 011100001 和 11100110 时 Y 1 和 Y 6 分别被选中——26.---------------------------------------------------------------------------------------- 解:D=A 1 分Q n+1=D=A ----------------------------------------------------------------- 2 分Q 1 QOE QOE ---------------------------------------------------------------- 2 分设触发器初始状态为0态,波形如图3所示。

CP JLTLTLFURd 讪1' ' hi JdI I ■ i7.解:①驱动方程: J 0 K 0 1J 1 K 1 X Q o(2 分)f=1T 1.218 103821HZ 0.821KHZ ---------------------- 3分E②状态方程:n 1 n n n n n nQ i J1Q1 K1Q1 (Q o X)Q (Q o X)Q i (2分)③输出方程:Y Q;Q0 ----------------------------------- (1分)3分)0Y0j01001110010100011D□Q10011010101011000111110:⑤从状态表可得:为受控制的可逆进制值计数器。

---------------------------- (2分)三、设计题:(每10分,共20分)1.------------------------------------------------------------------------ 解:(1)依题意得真值表如下: ---------------------------------------------- 3NO A B C F0 000 11 001 02 010 03 011 14 100 05 101 16 110 17 111 0(2)由真值表可得:F m o m 3 m )5 m )6F AgBgC AgBgc AgBgC AgBgC(3) ----------------------------------------------------------------------------- 选用8选1数选器实现该逻辑电路如下: ------------------------------- 4 分2. 解:(1)从波形图上可得:该电路有5个状态,且电路为上升沿触发,电路为穆尔型 时序电路。

任取74161累加计数中的5个状态,这里取0000至0100共5个 状态,任取一种映射得计数器状态与 V01、V02的真值表如下:分(2)从真值表得:a1 1 □ 1 □ □ 1»T0|74LSI51TH 丸Be3 IAAA -用138实现该函数,当使能端失效时:V01 mV02mmi j Y1Y0 ?Y2------- 1 分m2m0?m2保持权位一致性:得Q 3 S2, Q 0,S1 1Q A2,Q1 A1,Q0 A0其中74161构成5进制加法计数器, 得逻辑电路图如下:vccV ol ----------------------------------------- 1 分702mom2m0?m2----------------------- 1 分4 分A QAB QBC QCI-gHJT43*CLP广LJUnCP74LS151174LS13SN沁•LrSJl -CZ、填空题:(每小题2分,共10分)1. _________________________________________________ 二进制数(1011.1001 2转换为八进制数为__________________________ ,转换为十六进为 _______________ 。

2. 数字电路按照是否具有记忆功能通常可分为两类:____________ 、___________ 。

3. _______________________________________________________________ 已知逻辑函数F = A © B ,它的与非-与非表达式为___________________________ ,或与非表达式为 _______________________ 。

4. _________________________ 5个变量可构成______________________________ 个最小项,变量的每一种取值可使 ___________ 个最小项的值为1。

5.555定时器构成的施密特触发器,若电源电压V cc = 12V,电压控制端经0.01 F 电容接地,则上触发电平U T+ = _______________ V,下触发电平U T = ___________ V。

二、化简题:(每小题10分,共20分)1 .用代数法将下面的函数化为最简与或式:F=C- [ ABD BC ABD+(B+C)D]2. 用卡诺图法将下列函数化简为最简与或式:F(A、B C D)=E m( 0,2,4,5,7,13 )+E d(8,9,10,11,14,15)三、分析题:(每小题10分,共40分)1. 试分析题1图所示逻辑电路,写出逻辑表达式和真值表,表达式化简后再画出新的逻辑图。