verilog--4路抢答器设计-带30s倒计时

数字四路抢答器设计方案

数字四路抢答器设计方案介绍数字四路抢答器是一种常用于教育培训、比赛答题等场合的设备,其作用是指示哪个参赛者按下按钮抢答、以及谁率先抢答成功。

本文档将介绍数字四路抢答器的设计方案。

设计背景基于教育和比赛的需要,越来越多的场合需要使用抢答器来提高效率和公正性。

而数字化的抢答器相比于传统的机械式抢答器具有更高的精度和易用性,因此在市场上越来越受欢迎。

数字四路抢答器是一种常见的数字化抢答器,其能够为教师、裁判提供一种简单、准确、实用的抢答解决方案。

设计思路数字四路抢答器主要由以下部分组成:按钮、指示器、控制器。

具体的设计思路如下:按钮数字四路抢答器需要配备四个按钮,分别对应四个参赛者。

当任意一个参赛者按下按钮后,系统会进行响应,并指示哪个参赛者按下了按钮。

指示器数字四路抢答器需要配备一个指示器,用于指示哪个参赛者率先抢答成功。

指示器可以是LED灯、端口提示音等。

控制器数字四路抢答器需要配备一个控制器,用于控制按钮、指示器等功能的运行。

控制器可以使用单片机、传感器等元件来实现。

通过单片机的编程,可以实现响应按键事件、控制指示灯等功能。

设计要点设计数字四路抢答器的过程中,需注意以下关键点:稳定性抢答系统的稳定性是其最基本的设计要求之一。

在使用过程中,系统必须极具稳定性、可靠性,确保不会出现不必要的故障和错误。

在设计过程中,需要对抢答系统进行充分测试和优化,以保证其高效运行。

实用性数字四路抢答器的实用性是设计的另一项重要目标。

系统需要具备直观、简单、易操作等特点,确保教师、裁判能够方便地使用抢答器。

此外,系统还需要具有较高的适应性,可以扩展适应不同场合。

硬件选型在设计数字四路抢答器时,硬件选型将起到决定性作用。

对于不同的应用场合,不同的硬件选型将产生不同的效果。

因此,在进行硬件选型时,需要充分考虑到项目的实际需求和预算等因素。

设计实现数字四路抢答器的设计实现可以采用以下步骤:1.选用合适的硬件元件,如单片机、开发板、LED灯、按键、电源等。

毕业设计——四路智力竞赛智能抢答器【范本模板】

摘要和关键词本文主要围绕四路选手抢答电路的设计和制作而展开叙述的,叙述了电路设计的过程。

该电路主要包括电源电路、抢答显示电路、倒计时电路和脉冲电路构成。

电源电路提供稳定的5V电源,抢答显示电路能够锁存抢先获得抢答权的选手编号,倒计时电路能够对选手答题时间进行控制,脉冲电路为电路提供秒脉冲信号。

关键词:抢答电路仿真电路板倒计时目录一.绪论..。

.。

.。

.。

.。

..。

.。

..。

.。

.。

..。

11.1 设计任务与要求.。

....。

..。

.。

.....。

..。

....。

.。

.。

..。

.。

..。

11.2 设计方案.。

..。

..。

....。

....。

.....。

.。

.。

.。

..。

.。

.。

..。

1二。

模块设计及仿真..。

.。

.。

.。

...。

.....。

..。

.。

.。

.。

22。

1 仿真软件介绍。

.。

.。

.。

....。

.。

..。

.。

...。

..。

....。

..。

.。

22.2 电源电路的设计和仿真...。

.。

...。

.。

.。

..。

.。

...。

...。

......。

.。

32.3 抢答显示电路。

...。

.。

..。

..。

...。

.。

..。

.。

.。

.。

...。

..........。

.。

42.4 定时电路.....。

..。

.。

..。

.。

.。

..。

.。

.。

...。

.。

....。

...。

...。

.。

52。

5 脉冲电路..。

..。

.。

..。

..。

.。

.。

.。

.。

...。

.。

.。

..。

..。

.。

.。

(5)三. 元件及封装选择。

..。

.。

.。

..。

...。

.。

.。

..。

.。

63.1 74LS279锁存器。

.。

.。

.。

...。

.。

.....。

....。

.。

..。

..。

..。

..。

.。

.。

63.2 优先编码器 74LS148。

.。

.。

.。

......。

..。

.。

.。

...。

......。

..。

.。

.7 3.3 555定时器。

..。

.。

..。

..。

..。

..。

......。

...。

..。

.......。

...。

..9 3.4 译码器及应用.。

EDA课程设计 VHDL四路智力抢答器

EDA课程设计 VHDL四路智力抢答器eda课程设计--vhdl四路智力抢答器vhdl四路智力抢答器eda课程设计一、任务与目的1.1熟练掌握eda工具软件quartus的使用1.2熟识采用vhdl硬件描述语言叙述数字电路1.3学会采用vhdl展开大规模集成电路设计1.4学习使用cpld/fpga实验系统硬件验证电路设计的正确性1.5初步掌握eda技术并具备一定的可编程逻辑芯片的开发能力二、设计题目与建议2.1设计题目四路智力竞赛抢答器2.2设计建议1.按所布置的题目要求,每一位学生独立完成全过程2.分模块层次化的设计;3.各功能模块的底层文件必须用vhdl语言设计,顶层文件可以用vhdl语言设计,也可以用原理图设计。

2.3设计内容设计一个可容纳四组参赛者同时抢答的数字抢答器。

主持人可控制系统发的清零和抢答的开始,控制电路可实现最快抢答选手按键抢答的判别和锁定功能,并禁止后续其他选手抢答。

抢答选手确定后给出选手编号的显示,抢答选手的编号显示保持到系统被清零为止,若提前抢答则对相应的抢答组发出警告。

*拓展内容:减少答题限时的功能,在确认了答对顺利有效率后,存有主持人按下答题限时功能键,开始9s的倒计时。

在计时结束后,超时提示led闪烁。

在主持人按下clear 开关时限时复位。

三、功能分析四路智力竞赛抢答器按功能设计分为三个模块1.答对锁存模块,在主持人收到答对指令后(start=’1’),若存有参赛者按下答对按钮,则显示器显示抢答组别,同时电路处于自锁状态,使其它组的抢答器不起作用。

主持人可以用清零按钮进行清零(clr=’0’).若抢答指令未发出(start=’0’),而有参赛者按下抢答按钮,则发出警告信号(alm=1).2.表明功能模块,在参赛者答对信号(界别)收到后,对参赛者信号展开译码,然后用7段数码管显示出来。

3.计时模块,在确认了答对顺利有效率后,存有主持人按下答题限时功能键,已经开始9s的好像计时。

基于FPGA平台的四位抢答器设计

现代电子系统设计综合题目——抢答器班级:电子信息工程(4)班姓名:尹燕宁学号:07090403日期:2011-12-14合作者:王启俊按照抢答器的设计要求,本设计主要实现以下基本功能:(1) 抢答器可以容纳四组参赛队进行抢答。

(2)系统复位后进入抢答状态,抢答开始后20秒倒计时,20秒倒计时后无人抢答显示超时,并报警。

(3)能显示抢答台号,且一组抢答后,则不接纳其他组抢答。

根据其设计要求,经过仔细试验和比较开始时所设想的两种方案,采用了以下方案以满足要求:倒计时模块应用动态显示方法显示两位变化的数字,倒计时过程中无人抢答则在计时结束后触发bell 信号发出报警声表示超时,有人抢答时则首先按下按钮的人通过一个stop信号屏蔽掉其他人的抢答信号,且不再计时。

在具体实现方案时,根据给定的电子综合设计实验箱的模块和已有元件的限制,对方案进行了如下调整和补充:首先是进行时钟信号分频,由给定的50MHz的时钟分成1Hz,以实现按秒倒计时;其次是倒计时显示的两位数字,由于只有一个静态显示数码管且被用于显示抢答台号,所以必须运用动态显示来进行两位数字的显示和控制;最后是复位后的初值设定,以使上一次抢答的结果不会影响下一次的抢答过程,增加电路的稳定性。

经过仿真以及实验,本设计能够圆满完成设计要求,且具有电路简洁、方案易懂、操作方便、抗干扰性强等特点,经过适当的轻微改造即可作为实际比赛时的四组抢答器,效果良好。

第一章方案的论证与设计第二章理论计算第三章电路图及相关设计文件第四章仿真与测试分析第五章设计总结第六章参考文献第七章附件(含完整电路图、VHDL设计文件)第一章方案的论证与设计为便于进行电路的方案设计和模块化设计,首先根据要求画出实现抢答器功能的系统框图如下所示:根据其设计要求,按照现有的知识水平和实验设备,提出了以下两种实现抢答器的方案:(一)倒计时部分采用静态显示,方便简单。

四人抢答部分根据抢答信号的高低来判断是否继续倒计时并且屏蔽掉其他后来的抢答信号。

verilog--4路抢答器设计-带30s倒计时

四路抢答器一、程序module qiangda4(clr,clk,input1,input2,input3,input4,seg,clockin,scan,LED);input clr,clk,input1,input2,input3,input4;output [7:0] seg; //7段数码管数据output [7:0] scan; //数码管位选output [3:0] LED; //输出LED灯指示output clockin; //蜂鸣器reg [7:0] seg;reg [7:0] scan;reg [3:0] LED;reg clockin;reg [3:0] data;reg input_flag,count_flag;reg [14:0] count1;reg [8:0] count2;reg [3:0] LED_N;//reg clock_flag;reg div1khz,div1hz;reg [2:0] cnt;reg [3:0] dat;//reg [7:0] data_count;reg [3:0] count_one,count_ten;initial count_one='d0; //初始化initial count_ten='d3;initial data=4'b0000;initial LED_N=4'b1111;//-------------fenping分频1khz-----------------------------------always @(posedge clk )beginif(count1=='d25000)begin div1khz<=~div1khz;count1<=0;endelsebegin count1<=count1+1'b1;endend//-------------fenping--1hz-------------------------------always @(posedge div1khz)beginif(count2=='d500)begin div1hz<=~div1hz;count2<=0;endelsebegin count2<=count2+1'b1;endend//----------------------------------------------------------always @(posedge div1hz or negedge clr)beginif(!clr)begincount_one<='d0;count_ten<='d3;count_flag<=1'b0;endelse if((!input_flag)&(!count_flag))begin if(count_one=='d0&&count_ten=='d0)begin count_flag<=1'b1;endelse if(count_one=='d0)begin count_one<=4'b1001;count_ten<=count_ten-1'b1;endelsebegin count_one<=count_one-1'b1;endendelsebegin count_one<=count_one;count_ten<=count_ten;endend//-----------------------------------------------------------always @(posedge clk ) //or input1 or input2 or input3 or input4 beginif(!clr)beginLED_N<=4'b1111;//clock_flag<=1'b0;input_flag<=1'b0;data<=4'b0000;endelse if((!input_flag)&(!count_flag))beginif(input1==0)begindata<=4'b0001;LED_N<=4'b0111;input_flag<=1'b1;endelse if(input2==0)begindata<=4'b0010;LED_N<=4'b1011;input_flag<=1'b1;endelse if(input3==0)begindata<=4'b0011;LED_N<=4'b1101;input_flag<=1'b1;endelse if(input4==0)begindata<=4'b0100;LED_N<=4'b1110;input_flag<=1'b1;endelsebegindata<=data;LED_N<=LED_N;input_flag<=input_flag;endendend//-------------led灯及蜂鸣器--------------------------------------------------- always @(posedge clk)beginLED<=LED_N;clockin<=div1khz&(input_flag|count_flag);//dat<=data;end//--------------shu ma guan sao miao数码管扫描--------------------------------- always @(posedge div1khz)beginif(cnt=='d3)begin cnt<=0;endelsebegin cnt<=cnt+1'b1;endend//-----------------------------------------------------always @(cnt,data,count_one,count_ten)begincase(cnt)//3'b000 : begin scan<=8'b01111111;end3'b001 : begin scan<=8'b10111111;dat<=data;end //选手编号3'b010 : begin scan<=8'b11011111;dat<=count_one;end //倒计时3'b011 : begin scan<=8'b11101111;dat<=count_ten;enddefault : begin scan<=8'bx;dat<=4'bx;endendcaseend//--------------------------------------------------------always @(dat)begincase(dat)4'b0000 : seg[7:0]<=8'b11000000;4'b0001 : seg[7:0]<=8'b11111001;4'b0010 : seg[7:0]<=8'b10100100;4'b0011 : seg[7:0]<=8'b10110000;4'b0100 : seg[7:0]<=8'b10011001;4'b0101 : seg[7:0]<=8'b10010010;4'b0110 : seg[7:0]<=8'b10000010;4'b0111 : seg[7:0]<=8'b11111000;4'b1000 : seg[7:0]<=8'b10000000;4'b1001 : seg[7:0]<=8'b10010000;4'b1010 : seg[7:0]<=8'b10001000;4'b1011 : seg[7:0]<=8'b10000011;4'b1100 : seg[7:0]<=8'b11000110;4'b1101 : seg[7:0]<=8'b10100001;4'b1110 : seg[7:0]<=8'b10000110;4'b1111 : seg[7:0]<=8'b10001110;default : seg[7:0]<=8'bx;endcaseendendmodule二、框图三、设计思路四路抢答,有30s倒计时,当有人抢答时,数码管显示对应选手编号,同时对应LED灯亮,蜂鸣器响起,此时其他选手抢答无效。

VHDL四路抢答器的设计

VHDL四路抢答器的设计设计要求:1.抢答器同时供N名选手,(此处假设4个)分别用4个按钮S0~ S3表示。

2.设置一个系统“开始复位”开关S,该开关由主持人控制(当主持人按下该开关后以前的状态复位并且开始计时抢答)。

3.抢答器具有锁存与显示功能。

即选手按动按钮,锁存相应的编号,并在LED数码管上显示,同时扬声器发出报警声响提示。

选手抢答实行优先锁存,优先抢答选手的编号一直保持到主持人将系统清除为止。

4. 抢答器具有定时抢答功能,且一次抢答的时间(0-99S)。

当主持人启动“开始复位”键后,定时器进行减计时。

5. 如果定时时间已到,无人抢答,本次抢答无效,系统报警并禁止抢答,定时显示器上显示00。

一、概述抢答器的逻辑结构主要由抢答鉴别lock模块、定时模块、译码模块和报警器模块组成。

在整个抢答器中最关键的是如何实现抢答封锁,在控制键按下的同时计数器倒计时显示有效剩余时间。

除此之外,整个抢答器还需有一个“复位开始”信号,以便抢答器能实现清零和开始。

抢答器共有3个输出显示,选手代号、计数器的个位和十位,他们输出全都为BCD码输出,这样便于和显示译码器连接。

当主持人按下控制键、选手按下抢答键蜂鸣器短暂响起。

•方案设计与论证嘿嘿!将该任务分成N个模块进行设计,分别为:抢答器鉴别模块、抢答器计时模块、译码模块、报警模块,最后是综合。

1. 抢答器鉴别模块:在这个模块中主要实现抢答过程中的抢答功能,并且能实现当有一路抢答按键按下时,该路抢答信号将其余个绿抢答封锁的功能。

在这个模块输入端有WARN输入(以时间控制系统的WARN输出信号为信号源)、一个和“时间控制系统”公用的CLEAR端、4人抢答输入信号端S0,S1,S2,S3和有一个时钟信号端CLK,这个时钟信号是个高频信号,用以扫描S0,S1,S2,S3是否有信号输入。

输出端有对应于S0,S1,S2,S3编号的4个指示灯LED 和4线2进制输出端STATES(用于锁存当前的状态),还有一个STOP 端用于指示S0,S1,S2,S3按钮状态(控制计时器停止)。

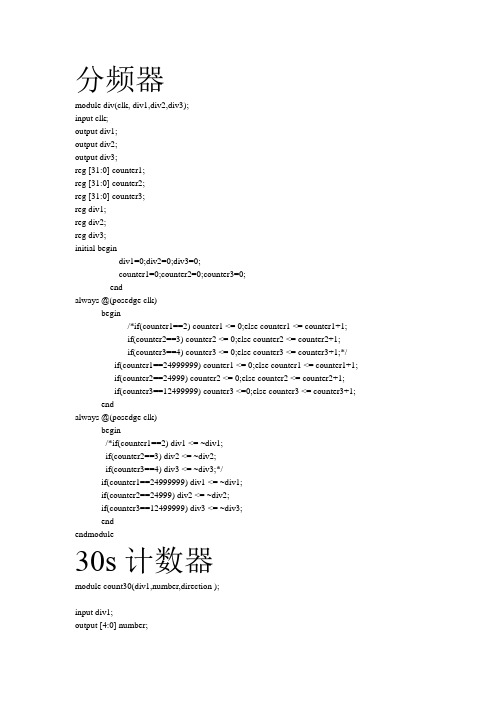

verilog 分频器,30s计数器及交通灯控制器设计

分频器module div(clk, div1,div2,div3);input clk;output div1;output div2;output div3;reg [31:0] counter1;reg [31:0] counter2;reg [31:0] counter3;reg div1;reg div2;reg div3;initial begindiv1=0;div2=0;div3=0;counter1=0;counter2=0;counter3=0;endalways @(posedge clk)begin/*if(counter1==2) counter1 <= 0;else counter1 <= counter1+1;if(counter2==3) counter2 <= 0;else counter2 <= counter2+1;if(counter3==4) counter3 <= 0;else counter3 <= counter3+1;*/ if(counter1==24999999) counter1 <= 0;else counter1 <= counter1+1;if(counter2==24999) counter2 <= 0;else counter2 <= counter2+1;if(counter3==12499999) counter3 <=0;else counter3 <= counter3+1;endalways @(posedge clk)begin/*if(counter1==2) div1 <= ~div1;if(counter2==3) div2 <= ~div2;if(counter3==4) div3 <= ~div3;*/if(counter1==24999999) div1 <= ~div1;if(counter2==24999) div2 <= ~div2;if(counter3==12499999) div3 <= ~div3;endendmodule30s计数器module count30(div1,number,direction );input div1;output [4:0] number;reg [4:0] number;reg direction;initialbegindirection=0;number=30;endalways@(posedge div1)beginif(number==0)begindirection<=~direction;number<=30;endelse number<=number-1;endendmodule控制器module moniter( div3,number,direction,eastred,eastyellow,eastgreen,northred,northyellow,northgreen );input div3;input direction;input [4:0]number;output eastred;output eastyellow;output eastgreen;output northred;output northyellow;output northgreen ;//wire [4:0] number;reg eastred;reg eastyellow;reg eastgreen;reg northred;reg northyellow;reg northgreen ;initial begineastred<=1;eastgreen<=0;northred<=1;northgreen<=0;northyellow<=eastyellow<=0;endalways @(posedge div3)beginif(number<=3)beginif (direction==0) eastyellow<=~eastyellow;else northyellow<=~northyellow;endelse begin eastyellow<=0;northyellow<=0;end endalways @(number )/*beginif(number==30&&direction==0)begin eastred<=1;eastgreen<=0;northred<=1;northgreen<=0;end*/if (number>2'b00010&&direction==0)begineastred<=0;eastgreen<=1;northred<=1;northgreen<=0;endelse if(number<3&&direction==0)begineastred<=0;eastgreen<=0;northred<=1;northgreen<=0;endelse if(number>2&&direction==1)begineastred<=1;eastgreen<=0;northred<=0;northgreen<=1;endelse if(number<3&&direction==1)begineastred<=1;eastgreen<=0;northred<=0;northgreen<=0;endendmodule译码器module yimaqi( clk,number,led1,led2);input clk;input [4:0] number;output [6:0] led1;output [6:0] led2;reg [6:0] led1;reg [6:0] led2;always @( number )begincase (number)5'b00000: begin led1 <= 7'b0000001; led2 <= 7'b0000001;end5'b00001: begin led1 <= 7'b0000001; led2 <= 7'b1001111;end5'b00010: begin led1 <= 7'b0000001; led2 <= 7'b0010010;end7'b0000110;end5'b00100: begin led1 <= 7'b0000001; led2 <= 7'b1001100;end5'b00101: begin led1 <= 7'b0000001; led2 <= 7'b0100100;end5'b00110: begin led1 <= 7'b0000001; led2 <= 7'b1100000;end5'b00111: begin led1 <= 7'b0000001; led2 <= 7'b0001111;end5'b01000: begin led1 <= 7'b0000001; led2 <= 7'b0000000;end5'b01001: begin led1 <= 7'b0000001; led2 <= 7'b0001100; end5'b01010: begin led1 <= 7'b1001111; led2 <= 7'b0000001;end5'b01011: begin led1 <= 7'b1001111; led2 <= 7'b1001111; end5'b01100: begin led1 <= 7'b1001111; led2 <= 7'b0010010;end5'b01101: begin led1 <= 7'b1001111; led2 <= 7'b0000110; end5'b01110: begin led1 <= 7'b1001111; led2 <= 7'b1001100;end5'b01111: begin led1 <= 7'b1001111; led2 <= 7'b0100100;end5'b10000: begin led1 <= 7'b1001111; led2 <= 7'b1100000;end5'b10001: begin led1 <= 7'b1001111; led2 <= 7'b0001111;end5'b10010: begin led1 <= 7'b1001111; led2 <= 7'b0000000;end5'b10011: begin led1 <= 7'b1001111; led2 <= 7'b0001100;end5'b10100: begin led1 <= 7'b0010010; led2 <= 7'b0000001;end5'b10101: begin led1 <= 7'b0010010; led2 <= 7'b1001111;end5'b10110: begin led1 <= 7'b0010010; led2 <= 7'b0010010;end5'b10111: begin led1 <= 7'b0010010; led2 <= 7'b0000110;end5'b11000: begin led1 <= 7'b0010010; led2 <= 7'b1001100;end7'b0100100;end5'b11010: begin led1 <= 7'b0010010; led2 <= 7'b1100000;end5'b11011: begin led1 <= 7'b0010010; led2 <= 7'b0001111;end5'b11100: begin led1 <= 7'b0010010; led2 <= 7'b0000000;end5'b11101: begin led1 <= 7'b0010010; led2 <= 7'b0001100;end5'b11110: begin led1 <= 7'b0000110; led2 <= 7'b0000001;enddefault: begin led1 <= 7'b0000000; led2 <= 7'b0000000;endendcaseendendmodulemodule dianzhen(direction,clk,div2,row,con);input div2;input clk;input direction;output[15:0] row;output[15:0] con;reg[15:0] row;reg[15:0] con;integer cnt,b;reg[15:0] r[48:0];initialbeginif (direction==0)begin// 丁r[0] <=16'b1111111111111111;r[1] <=16'b1011111111111111;r[2] <=16'b1011111111111111;r[3] <=16'b1011111111111111;r[4] <=16'b1011111111111111;r[5] <=16'b1011111111111011;r[6] <=16'b1011111111111101;r[7] <=16'b1000000000000011;r[8] <=16'b1011111111111111;r[9] <=16'b1011111111111111;r[10]<=16'b1011111111111111;r[11] <=16'b1011111111111111;r[12]<=16'b1011111111111111;r[13]<=16'b1011111111111111;r[14]<=16'b1011111111111111;r[15]<=16'b1111111111111111;// 乾r[16]<=16'b1101111111101111 ;r[17]<=16'b1101000000101111 ;r[18]<=16'b1101010101101111 ;r[19]<=16'b0000010101101111 ;r[20]<=16'b1101010100000000 ;r[21]<=16'b1101010101101111 ;r[22]<=16'b1101000000101111 ;r[23]<=16'b1101110111101111 ;r[24]<=16'b1111001111110011 ;r[25]<=16'b0000110111001101 ;r[26]<=16'b1010110110111101 ;r[27]<=16'b1110110101111101 ;r[28]<=16'b1110110011111101 ;r[29]<=16'b1110110111100001 ;r[30]<=16'b1110111111111011 ;r[31]<=16'b1111111111111111 ;// 全灭r[32]<=16'b1111111111111111;r[33]<=16'b1111111111111111;r[34]<=16'b1111111111111111;r[35]<=16'b1111111111111111;r[36]<=16'b1111111111111111;r[37]<=16'b1111111111111111;r[38]<=16'b1111111111111111;r[39]<=16'b1111111111111111;r[40]<=16'b1111111111111111;r[41]<=16'b1111111111111111;r[42]<=16'b1111111111111111;r[43]<=16'b1111111111111111;r[44]<=16'b1111111111111111;r[45]<=16'b1111111111111111;r[46]<=16'b1111111111111111;r[47]<=16'b1111111111111111;endelse if(direction==1)begin//1r[0] <=16'b 1111111111111111;r[1] <=16'b 1111111111111111;r[2] <=16'b 1111111111111111;r[3] <=16'b 1111111111111111;r[4] <=16'b 1111111111111111;r[5] <=16'b 1111011111111011;r[6] <=16'b 1111011111111011;r[7] <=16'b 1110000000000011;r[8] <=16'b 1111111111111011;r[9] <=16'b 1111111111111011;r[10]<=16'b 1111111111111111;r[11] <=16'b 1111111111111111;r[12]<=16'b 1111111111111111;r[13]<=16'b 1111111111111111;r[14]<=16'b 1111111111111111;r[15]<=16'b 1111111111111111;// 0r[16]<=16'b 1111111111111111;r[17]<=16'b 1111111111111111;r[18]<=16'b 1111111111111111;r[19]<=16'b 1111111111111111;r[20]<=16'b 1111111111111111;r[21]<=16'b 1111100000001111;r[22]<=16'b 1111011111110111;r[23]<=16'b 1110111111111011;r[24]<=16'b 1110111111111011;r[25]<=16'b 1111011111110111;r[26]<=16'b 1111100000001111;r[27]<=16'b 1111111111111111;r[28]<=16'b 1111111111111111;r[29]<=16'b 1111111111111111;r[30]<=16'b 1111111111111111;r[31]<=16'b 1111111111111111;// 9r[32]<=16'b 1111111111111111;r[33]<=16'b 1111111111111111;r[34]<=16'b 1111111111111111;r[35]<=16'b 1111111111111111;r[36]<=16'b 1111111111111111;r[37]<=16'b 1111100011111111;r[38]<=16'b 1111011101110011;r[39]<=16'b 1110111110111011;r[40]<=16'b 1110111110111011;r[41]<=16'b 1111011101110111;r[42]<=16'b 1111100000001111;r[43]<=16'b 1111111111111111;r[44]<=16'b 1111111111111111;r[45]<=16'b 1111111111111111;r[46]<=16'b 1111111111111111;r[47]<=16'b 1111111111111111;endendalways@(posedge clk )beginif (b==47)b<=0;else b<=b+1;endalways@(posedge div2)beginif(cnt==15)begincnt<=0;endelsecnt<=cnt+1;case(cnt)15: con<=16'b0000_0000_0000_0001; 14: con<=16'b0000_0000_0000_0010; 13: con<=16'b0000_0000_0000_0100; 12: con<=16'b0000_0000_0000_1000; 11: con<=16'b0000_0000_0001_0000; 10: con<=16'b0000_0000_0010_0000; 9: con<=16'b0000_0000_0100_0000; 8: con<=16'b0000_0000_1000_0000; 7: con<=16'b0000_0001_0000_0000; 6: con<=16'b0000_0010_0000_0000; 5: con<=16'b0000_0100_0000_0000; 4: con<=16'b0000_1000_0000_0000; 3: con<=16'b0001_0000_0000_0000; 2: con<=16'b0010_0000_0000_0000; 1: con<=16'b0100_0000_0000_0000; 0: con<=16'b1000_0000_0000_0000;endcasecase(cnt)0: row<=r[b+0];1: row<=r[b+1];2: row<=r[b+2];3: row<=r[b+3];4: row<=r[b+4];5: row<=r[b+5];6: row<=r[b+6];7: row<=r[b+7];8: row<=r[b+8];9: row<=r[b+9];10: row<=r[b+10];11: row<=r[b+11];12: row<=r[b+12];13: row<=r[b+13];14: row<=r[b+14];15: row<=r[b+15];endcaseendendmodule。

抢答器verilog版

抢答器-verilog一.实验要求设计一个可容纳四组参赛的数字式抢答器,每组设一个按钮供抢答使用。

抢答器具有第一信号鉴别和锁存功能,使除第一抢答者外的按钮不起作用;设置一个主持人“复位”按钮,主持人复位后,开始抢答,第一信号鉴别锁存电路得到信号后,用指示灯显示抢答组别,扬声器发出2—3s的音响。

设置犯规电路,对提前抢答和超时答题(例如3min)的组别鸣笛示警,并由组别显示电路显示出犯规组别。

设置一个计分电路,每组开始预置10分,由主持人记分,答对一次加1分,答错一次减1分。

二.实验方框图三.答题规则(本实验均采用脉冲按键模式)四.本次实验的verilog源程序module answer(clk,k1,k2,k3,k4,o1,o2,o3,o4,out1,out2,start,reset1, save); //抢答信号鉴别,保持模块input clk,k1,k2,k3,k4,start,reset1;//k1~k2是选手按键output o1,o2,o3,o4,out1,out2;//o1~o2是抢答信号显示灯output[2:0] save; //用于保存选手的抢答信号reg o1,o2,o3,o4,out1,out2,ok;reg[7:0] counter;reg[2:0] save;integer i;always@(posedge clk)if(reset1)//当reset1为1时复位清零begin{o1,o2,o3,o4,out1,out2,ok}<=7'b0000000;counter<=0;i=0;endelsebegin////if(start)beginok<=1;save<=0;endif(!ok)//reset1和ok为0时,有人按键表示犯规begin //一旦有人按键,他的输出信号将屏蔽其他人的按键if(k1&&!o2&&!o3&&!o4)begino1<=1;save<=1;endif(k2&&!o1&&!o3&&!o4)begino2<=1;save<=2;endif(k3&&!o1&&!o2&&!o4)begino3<=1;save<=3;endif(k4&&!o1&&!o2&&!o3)begino4<=1;save<=4;endif(o1 || o2 || o3 || o4)//提前按键扬声器响out1<=1;endelse//reset1为0,ok为1时,有人按键为正常抢答begin//if(k1 || k2 || k3 || k4)begin //一旦有人按键,他的输出信号将屏蔽其他人的按键if(k1&&!o2&&!o3&&!o4)begino1<=1;save<=1;endif(k2&&!o1&&!o3&&!o4)begino2<=1;save<=2;endif(k3&&!o1&&!o2&&!o4)begino3<=1;save<=3;endif(k4&&!o1&&!o2&&!o3)begino4<=1;save<=4;endendif(o1 || o2 || o3 || o4)begini=i+1;if(i<2)out2<=1;//有人抢到题,响几下铃。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

四路抢答器一、程序module qiangda4(clr,clk,input1,input2,input3,input4,seg,clockin,scan,LED);input clr,clk,input1,input2,input3,input4;output [7:0] seg; //7段数码管数据output [7:0] scan; //数码管位选output [3:0] LED; //输出LED灯指示output clockin; //蜂鸣器reg [7:0] seg;reg [7:0] scan;reg [3:0] LED;reg clockin;reg [3:0] data;reg input_flag,count_flag;reg [14:0] count1;reg [8:0] count2;reg [3:0] LED_N;//reg clock_flag;reg div1khz,div1hz;reg [2:0] cnt;reg [3:0] dat;//reg [7:0] data_count;reg [3:0] count_one,count_ten;initial count_one='d0; //初始化initial count_ten='d3;initial data=4'b0000;initial LED_N=4'b1111;//-------------fenping分频1khz-----------------------------------always @(posedge clk )beginif(count1=='d25000)begin div1khz<=~div1khz;count1<=0;endelsebegin count1<=count1+1'b1;endend//-------------fenping--1hz-------------------------------always @(posedge div1khz)beginif(count2=='d500)begin div1hz<=~div1hz;count2<=0;endelsebegin count2<=count2+1'b1;endend//----------------------------------------------------------always @(posedge div1hz or negedge clr)beginif(!clr)begincount_one<='d0;count_ten<='d3;count_flag<=1'b0;endelse if((!input_flag)&(!count_flag))begin if(count_one=='d0&&count_ten=='d0)begin count_flag<=1'b1;endelse if(count_one=='d0)begin count_one<=4'b1001;count_ten<=count_ten-1'b1;endelsebegin count_one<=count_one-1'b1;endendelsebegin count_one<=count_one;count_ten<=count_ten;endend//-----------------------------------------------------------always @(posedge clk ) //or input1 or input2 or input3 or input4 beginif(!clr)beginLED_N<=4'b1111;//clock_flag<=1'b0;input_flag<=1'b0;data<=4'b0000;endelse if((!input_flag)&(!count_flag))beginif(input1==0)begindata<=4'b0001;LED_N<=4'b0111;input_flag<=1'b1;endelse if(input2==0)begindata<=4'b0010;LED_N<=4'b1011;input_flag<=1'b1;endelse if(input3==0)begindata<=4'b0011;LED_N<=4'b1101;input_flag<=1'b1;endelse if(input4==0)begindata<=4'b0100;LED_N<=4'b1110;input_flag<=1'b1;endelsebegindata<=data;LED_N<=LED_N;input_flag<=input_flag;endendend//-------------led灯及蜂鸣器--------------------------------------------------- always @(posedge clk)beginLED<=LED_N;clockin<=div1khz&(input_flag|count_flag);//dat<=data;end//--------------shu ma guan sao miao数码管扫描--------------------------------- always @(posedge div1khz)beginif(cnt=='d3)begin cnt<=0;endelsebegin cnt<=cnt+1'b1;endend//-----------------------------------------------------always @(cnt,data,count_one,count_ten)begincase(cnt)//3'b000 : begin scan<=8'b01111111;end3'b001 : begin scan<=8'b10111111;dat<=data;end //选手编号3'b010 : begin scan<=8'b11011111;dat<=count_one;end //倒计时3'b011 : begin scan<=8'b11101111;dat<=count_ten;enddefault : begin scan<=8'bx;dat<=4'bx;endendcaseend//--------------------------------------------------------always @(dat)begincase(dat)4'b0000 : seg[7:0]<=8'b11000000;4'b0001 : seg[7:0]<=8'b11111001;4'b0010 : seg[7:0]<=8'b10100100;4'b0011 : seg[7:0]<=8'b10110000;4'b0100 : seg[7:0]<=8'b10011001;4'b0101 : seg[7:0]<=8'b10010010;4'b0110 : seg[7:0]<=8'b10000010;4'b0111 : seg[7:0]<=8'b11111000;4'b1000 : seg[7:0]<=8'b10000000;4'b1001 : seg[7:0]<=8'b10010000;4'b1010 : seg[7:0]<=8'b10001000;4'b1011 : seg[7:0]<=8'b10000011;4'b1100 : seg[7:0]<=8'b11000110;4'b1101 : seg[7:0]<=8'b10100001;4'b1110 : seg[7:0]<=8'b10000110;4'b1111 : seg[7:0]<=8'b10001110;default : seg[7:0]<=8'bx;endcaseendendmodule二、框图三、设计思路四路抢答,有30s倒计时,当有人抢答时,数码管显示对应选手编号,同时对应LED灯亮,蜂鸣器响起,此时其他选手抢答无效。

当倒计时到达0时,蜂鸣器响,此时不能够抢答,清零后重新计时。

程序有个小问题,数码管显示选手编号时,存在干扰,能够勉强辨认出选手编号,但不够清晰,找了好久都没查出。