vhdl基础及经典实例开发pdf

第三章VHDL程序设计案例

第三章VHDL程序设计案例

37

带允许端的十二进制计数器

第三章VHDL程序设计案例

38

可逆计数器(加减计数器)

第三章VHDL程序设计案例

39

可逆计数器仿真结果:

第三章VHDL程序设计案例

40

例:六十进制(分、秒)计数器

第三章VHDL程序设计案例

end decoder;

architecture rtl of decoder is

begin

process(inp)

begin

outp<=(others=>’0’);

outp(conv_integer(inp))<=‘1’;

end process;

end rtl;

第三章VHDL程序设计案例

sel=000 sel =001 sel =010 sel =011 sel =100 sel =101 sel =110 sel =111

第三章VHDL程序设计案例

25

clock sig_in reset 同步复位 sig_out1 异步复位 sig_out2

第三章VHDL程序设计案例

26

二) 常用时序电路设计

1、触发器(Flip_Flop) 1)D触发器

第三章VHDL程序设计案例

27

异步置位/复位D触发器

第三章VHDL程序设计案例

1)“”序列发生器

第三章VHDL程序设计案例

49

第三章VHDL程序设计案例

50

第三章VHDL程序设计案例

51

仿真结果:

第三章VHDL程序设计案例

52

2)序列信号检测器的状态机设计与实现, 检测“”

第1章VHDL语言基础

位矢量(BIT_VECTOR)。若端口定义为BIT,则其信号值 是一个1位的二进制数,取值只能是0或1;若端口定义为 BIT_VECTOR,则其信号值是一组二进制数。

➢ 在电路中,如果实体代表一个器件符号,则结构体描述了 这个符号的内部行为。当把这个符号例化成一个实际的器 件安装到电路上时,则需用配置语句为这个例化的器件指 定一个结构体(即指定一种实现方案),或由编译器自动选一 个结构体。

1. 结构体的一般语句格式 ARCHITECTURE 结构体名 OF 实体名 IS [说明语句;] BEGIN [功能描述语句;] END [ARCHITECTURE] [结构体名];

1.1 VHDL程序基本结构

一、VHDL程序设计约定 ➢ 语句结构描述中方括号“[ ]”内的内容为可选内容。 ➢ 对于VHDL的编译器和综合器来说,程序文字的大小写是不

加区分的。 ➢ 程序中的注释使用双横线“- -”。 ➢ 源程序命名与实体同名(MAX+plus Ⅱ要求)。

二、VHDL程序设计引例( 74LS00的设计 )

③ 信号赋值语句将设计实体内的处理结果向定义的信号或界面 端口进行赋值。

④ 子程序调用语句用于调用一个已设计好的子程序。

⑤ 元件例化语句对其他的设计实体作元件调用说明,并将此元 件的端口与其他的元件、信号或高层次实体的界面端口进行 连接。

A

A NAND2

Y

Y

B

B

(a)

A1

A NAND2

U1 Y

Y1

B1

B

A2

A NAND2

VHDL语言编写经典常用实例

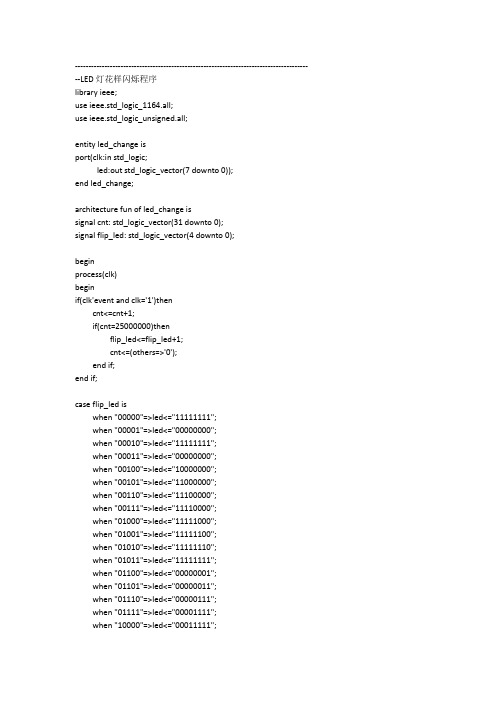

--------------------------------------------------------------------------------------- --LED灯花样闪烁程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity led_change isport(clk:in std_logic;led:out std_logic_vector(7 downto 0));end led_change;architecture fun of led_change issignal cnt: std_logic_vector(31 downto 0);signal flip_led: std_logic_vector(4 downto 0);beginprocess(clk)beginif(clk'event and clk='1')thencnt<=cnt+1;if(cnt=25000000)thenflip_led<=flip_led+1;cnt<=(others=>'0');end if;end if;case flip_led iswhen "00000"=>led<="11111111";when "00001"=>led<="00000000";when "00010"=>led<="11111111";when "00011"=>led<="00000000";when "00100"=>led<="10000000";when "00101"=>led<="11000000";when "00110"=>led<="11100000";when "00111"=>led<="11110000";when "01000"=>led<="11111000";when "01001"=>led<="11111100";when "01010"=>led<="11111110";when "01011"=>led<="11111111";when "01100"=>led<="00000001";when "01101"=>led<="00000011";when "01110"=>led<="00000111";when "01111"=>led<="00001111";when "10000"=>led<="00011111";when "10001"=>led<="00111111";when "10010"=>led<="01111111";when "10011"=>led<="11111111";when "10100"=>led<="00000000";when others =>led<="ZZZZZZZZ";end case;if(flip_led>"10100")thenflip_led<="00000";end if;end process;end fun;--拨码开关控制LED程序library ieee;use ieee.std_logic_1164.all;entity switch_led isport(key : in std_logic_vector(1 downto 0);led : out std_logic_vector(7 downto 0)); --八个led灯end switch_led;architecture fun of switch_led isbeginprocess(key)begincase key iswhen "00" => led <="00000000"; -- // "0"when "01" => led <="00001111"; -- // "1"when "10" => led <="11110000"; -- // "2"when "11" => led <="11111111"; -- // "3"when others => led <="ZZZZZZZZ";end case;end process;end;--按键消抖控制LED程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity stable_key isport(clk :in std_logic;key_in:in std_logic;key_out: out std_logic);end ;architecture fun of stable_key issignal cnt : integer range 0 to 1999999;signal key ,key_d : std_logic;beginprocess(clk)beginif clk'event and clk='1' thenif key /= key_in then -----键值变化开始计时10ms key_d <= key_in;cnt <= 0;elsif cnt=1999999 then ---10mskey_out <= not key_d;cnt <= 0;elsecnt <= cnt + 1 ;end if ;key<= key_in;end if ;end process;end ;--蜂鸣器电子琴程序library ieee;use ieee.std_logic_1164.all;entity digital_piano isport(key : in std_logic_vector(7 downto 0); --定义8个按键key1~key8clk : in std_logic; --时钟输入端50Mhzbeep: out std_logic); --蜂鸣器输出端end digital_piano;architecture fun of digital_piano issignal freq : integer range 0 to 50000;signal beep_reg: std_logic;beginbeep_process: process(clk,freq) --分频进程--本工程内核心进程,计数器的大小由counter决定variable cnt : integer range 0 to 50000;beginif clk'event and clk='1' thenif cnt < freq thencnt := cnt + 1;elsecnt := 0 ;beep_reg <=not beep_reg;end if;end if;end process beep_process;freq_process: process(key)begincase key iswhen "11111110" => freq <= 47774; ---------------------------------counter 计算公式:中音do的频率为523.3hz,为了在上个beep_pro进程中得到523的频率counter= 50*1000000/(523*2)when "11111101" => freq <= 42568; --中音re的频率为587.3hzwhen "11111011" => freq <= 37919; --中音mi的频率为659.3hzwhen "11110111" => freq <= 35791; --中音fa的频率为698.5hzwhen "11101111" => freq <= 31888; --中音sol的频率为784hzwhen "11011111" => freq <= 28409; --中音la的频率为880hzwhen "10111111" => freq <= 25309; --中音si的频率为987.8hzwhen "01111111" => freq <= 23912; --高音do的频率为1045.5hzwhen "01111101" => freq <= 21282; --高音re的频率为1174.7hzwhen "01111011" => freq <= 18961; --高音mi的频率为1318.5hzwhen "01110111" => freq <= 17897; --高音fa的频率为1396.9hzwhen "01101111" => freq <= 15944; --高音sol的频率为1568hzwhen "01011111" => freq <= 14205; --高音la的频率为1760hzwhen "00111111" => freq <= 12605; --高音si的频率为1975.5hzwhen others => freq <= 0;end case;end process freq_process;beep <= beep_reg;end;--数码管静态扫描library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity static_segled isport(clk : in std_logic;data:out std_logic_vector(7 downto 0);sel:out std_logic_vector(7 downto 0));end ;architecture fun of static_segled issignal num : std_logic_vector(3 downto 0);signal cnt : integer range 0 to 12499999 ;beginsel <= "00000000"; --静态显示,全部位选中process(clk)beginif clk'event and clk='1' then --每四秒改变一次数字if cnt=12499999 thencnt<=0;num<= num + 1;elsecnt<= cnt + 1 ;end if ;end if ;end process;process(num)begincase num iswhen "0000" => data<=x"c0"; -- // "0"when "0001" => data<=x"f9"; -- // "1"when "0010" => data<=x"a4"; -- // "2"when "0011" => data<=x"b0"; -- // "3"when "0100" => data<=x"99"; -- // "4"when "0101" => data<=x"92"; -- // "5"when "0110" => data<=x"82"; -- // "6"when "0111" => data<=x"f8"; -- // "7"when "1000" => data<=x"80"; -- // "8"when "1001" => data<=x"90"; -- // "9"when "1010" => data<=x"88"; -- // "a"when "1011" => data<=x"83"; -- // "b"when "1100" => data<=x"c6"; -- // "c"when "1101" => data<=x"a1"; -- // "d"when "1110" => data<=x"86"; -- // "e"when "1111" => data<=x"8e"; -- // "f"when others => data<=x"ff";end case;end process;end ;--数码管动态扫描library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity dynamic_segled isport(clk : in std_logic;data: out std_logic_vector(7 downto 0);sel:out std_logic_vector(7 downto 0) );end ;architecture fun of dynamic_segled issignal cnt: integer range 0 to 62449;signal flip_led: integer range 0 to 7;beginprocess(clk)beginif clk'event and clk='1' then ----- 动态扫描if cnt=62499 thencnt<=0;flip_led<=flip_led+1; -- 数据改变elsecnt<=cnt + 1;end if ;end if ;end process;process(flip_led)begincase flip_led is ---译码显示when 0 =>sel<="01111111";data<=x"c0";when 1 =>sel<="10111111";data<=x"f9";when 2 =>sel<="11011111";data<=x"a4";when 3 =>sel<="11101111";data<=x"b0";when 4 =>sel<="11110111";data<=x"99";when 5 =>sel<="11111011";data<=x"92";when 6 =>sel<="11111101";data<=x"82";when 7 =>sel<="11111110";data<=x"f8";when others=>sel<="11111111";data<=x"ff"; end case;end process;end ;。

VHDL简单实例

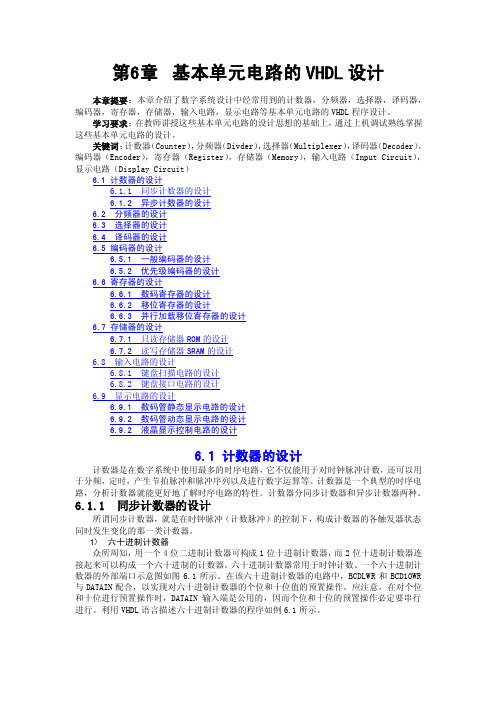

第6章基本单元电路的VHDL设计本章提要:本章介绍了数字系统设计中经常用到的计数器,分频器,选择器,译码器,编码器,寄存器,存储器,输入电路,显示电路等基本单元电路的VHDL程序设计。

学习要求:在教师讲授这些基本单元电路的设计思想的基础上,通过上机调试熟练掌握这些基本单元电路的设计。

关键词:计数器(Counter),分频器(Divder),选择器(Multiplexer),译码器(Decoder),编码器(Encoder),寄存器(Register),存储器(Memory),输入电路(Input Circuit),显示电路(Display Circuit)6.1 计数器的设计6.1.1 同步计数器的设计6.1.2 异步计数器的设计6.2 分频器的设计6.3 选择器的设计6.4 译码器的设计6.5 编码器的设计6.5.1 一般编码器的设计6.5.2 优先级编码器的设计6.6 寄存器的设计6.6.1 数码寄存器的设计6.6.2 移位寄存器的设计6.6.3 并行加载移位寄存器的设计6.7 存储器的设计6.7.1 只读存储器ROM的设计6.7.2 读写存储器SRAM的设计6.8 输入电路的设计6.8.1 键盘扫描电路的设计6.8.2 键盘接口电路的设计6.9 显示电路的设计6.9.1 数码管静态显示电路的设计6.9.2 数码管动态显示电路的设计6.9.2 液晶显示控制电路的设计6.1 计数器的设计计数器是在数字系统中使用最多的时序电路,它不仅能用于对时钟脉冲计数,还可以用于分频,定时,产生节拍脉冲和脉冲序列以及进行数字运算等。

计数器是一个典型的时序电路,分析计数器就能更好地了解时序电路的特性。

计数器分同步计数器和异步计数器两种。

6.1.1 同步计数器的设计所谓同步计数器,就是在时钟脉冲(计数脉冲)的控制下,构成计数器的各触发器状态同时发生变化的那一类计数器。

1) 六十进制计数器众所周知,用一个4位二进制计数器可构成1位十进制计数器,而2位十进制计数器连接起来可以构成一个六十进制的计数器。

VHDL语言编程.pdf

由于VHDL已经成为IEEE标准所规范的硬件描述语言言,大大多数EDA工工具几几乎都支支持VHDL,这 为VHDL的进一一步推广广和广广泛应用用奠定了了基础。在硬件电路路设计过程中,主要的设计文文件是用用 VHDL编写的源代码,因为VHDL易易读和结构化,所以易易于修改设计。

易易于共享和复用用

VHDL采用用基于库(Library)的设计方方法,可以建立立各种可再次利利用用的模 块。这些模块可以预先设计或使用用以前设计中的存档模块,将这些模块存放 到库中,就可以在以后的设计中进行行行复用用,可以使设计成果在设计人人员之间 进行行行交流和共享,减少硬件电路路设计。

VHDL程序的结构

VHDL语言编程

VHDL语言言是什什么?

VHDL全名Very-High-Speed Integrated Circuit Hardware Description Language,诞生生于1982年年。 是一一种用用于电路路设计的高高级语言言。它在80年年代的 后期出现。最初是由美国国防部开发出来供美军用用 来提高高设计的可靠性和缩减开发周期的一一种使用用范 围较小小的设计语言言 。用用在FPGA/CPLD/EPLD的 设计中。当然在一一些实力力力较为雄厚的单位,它也被 用用来设计ASIC。

END CASE; END invert; END logic;

各部分详细说明-Entity(实体)

entity 实体名is [generic (参数名表:类型;…);] [port (端口口表:方方式类型;…);] [声明] [begin

被动并行行行语句句] end [entity] [实体名];

√

×

Out

输出

×

√

vhdl编程实例

vhdl编程实例VHDL编程实例- 设计与实现一个4位的全加器在本篇文章中,我们将一步一步地回答如何设计和实现一个4位的全加器。

VHDL编程语言将是我们用于描述和模拟这个电路的工具。

第一步:理解全加器的原理在编写代码之前,我们首先需要理解全加器的原理。

全加器是一种用于对两个二进制数字进行相加的电路。

它接收三个输入信号:两个位的输入(A 和B)以及一个进位输入(C_in)。

全加器的输出结果为一个位的和(S)和一个进位输出(C_out)。

我们可以使用如下的真值表来描述全加器的输出结果:输入信号输出结果A B C_in S C_out0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1了解了全加器的工作原理后,我们可以开始编写代码了。

第二步:编写全加器的VHDL代码我们将使用VHDL语言来描述和模拟全加器。

下面是一个简单的4位全加器的VHDL代码实现:vhdlEntity声明entity full_adder isport (A, B : in std_logic_vector(3 downto 0);C_in : in std_logic;S : out std_logic_vector(3 downto 0);C_out : out std_logic);end full_adder;Architecture声明architecture Behavioral of full_adder isbeginprocess(A, B, C_in)variable carry : std_logic;begincarry := C_in;for i in 0 to 3 loopS(i) <= A(i) xor B(i) xor carry;carry := (A(i) and B(i)) or (carry and (A(i) xor B(i)));end loop;C_out <= carry;end process;end Behavioral;在此代码中,我们首先声明了一个实体(entity)和一个架构(architecture)。

第3部分VHDL基本知识共152页文档

数字逻辑

3.2 VHDL程序的基本结构

3.2.1 实体说明 实体说明部分的一般结构: ENTITY 实体名 IS [GENERIC (类属表);] [PORT (端口表);] END [ENTITY] 实体名;

18

数字逻辑

3.2 VHDL程序的基本结构

1. 实体名 实体说明部分以“ENTITY 实体名 IS”开始,以 “END [ENTITY] 实体名”结束。其中实体名由 设计者自定义,一般根据所设计实体的功能来取 名,“ENTITY”是VHDL语法规定中的保留关键 字。大多数EDA软件中的编译器和适配器是不区 分VHDL语言大小写的,但为了保持良好的设计 风格和便于阅读,通常将VHDL语言的标识符和 保留关键字以大写表示,设计者自定义符号小写 表示,如实体名、结构体名、变量名等。

5

数字逻辑

3.1 硬件描述语言VHDL介绍

2019年,我国国家技术监督局制定的《CAD通用技术规 范》推荐VHDL作为我国电子设计自动化硬件描述语言 国家标准。从此,VHDL语言在我国迅速普及,成为广 大硬件工程师必须掌握的一项技术。

VHDL语言能够成为标准化的硬件描述语言并获得广泛 应用,是因为有其它硬件描述语言不具备的有点:

13

数字逻ary)、 程序包(package)、实体 (entity declaration)、结构 体(architecture body)、配 置(configuration)五部分组 成。设计实体结构结构图如 图3-2所示,其中设计实体 必须有实体和结构体,其它 部分根据设计需要来添加。

端口名2 :通信模式 数据类型;

……

端口名n :通信模式 数据类型;

);

《VHDL程序设计基础》课件

语法格式

library library_name; use library_name.packag e_name.item;

库的使用

在程序中引用库中的函 数、过程、数据类型等 。

示例

library IEEE; use IEEE.STD_LOGIC_116 4.ALL;

程序包(Package)

01 程序包描述

并行赋值语句

同时对多个信号进行赋值操作。

生成语句

用于生成多个相似的电路结构, 如多路选择器、译码器等。

04 VHDL设计方法

自顶向下设计方法

总词

从整体到局部的设计方法

详细描述

自顶向下设计方法是一种从整体到局部的设计方法,首先确定系统的整体结构 和功能,然后逐步细化各个模块的设计,最终完成整个系统的设计。这种方法 有助于提高设计的层次性和模块化,便于设计和调试。

状态机设计

总结词

通过实例演示如何使用VHDL设计状态机。

详细描述

介绍状态机的基本概念和设计方法,包括状态图的绘制、状 态转移的实现等。通过具体的VHDL代码实现一个有限状态机 ,并解释代码中的各个部分。

06 VHDL仿真与验证

仿真工具与流程

仿真工具

ModelSim、Vivado Simulation等常用的 VHDL仿真工具,支持多种仿真算法和精度 。

02 语法格式

03 包的内容

04 包的使用

05 示例

程序包是库的子集,用于 组织相关的函数、过程、 数据类型等。

package package_name is

在包中声明函数、过程、 数据类型等。

在其他程序中引用包中的 内容。

package logic_operators is function AND (A, B: in std_logic) return std_logic; function OR (A, B: in std_logic) return std_logic; end logic_operators;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

vhdl基础及经典实例开发pdf VHDL是一种硬件描述语言,它用于描述和设计数字电路。

VHDL的全称是Very High Speed Integrated Circuit Hardware Description Language,它源于20世纪80年代的美国国防部,是一种为了描述硬

件而设计的开发语言。

VHDL的基础知识包括语法、数据类型和结构体。

语法方面,VHDL 有自己的语法规则和词法规则,要正确地描述一个硬件电路,我们需

要熟悉这些规则。

数据类型方面,VHDL内置了基本的数据类型,如bit、bit vector、integer等,这些数据类型可以用来描述电路的输入输出和中间信号。

结构体方面,VHDL支持设计者自定义类型,比如用record来描述一个复杂的数据结构。

在VHDL开发中,经典实例是不可或缺的。

经典实例可以帮助我们更好地理解VHDL的使用方法和特点,也可以让我们更好地掌握VHDL

的编程技巧。

下面是一些经典实例的介绍。

1.二进制加法器(Binary Adder):二进制加法器可以实现两个

二进制数的加法运算。

它是数字电路中常用的基本模块,很多其他的

电路都需要用到它。

通过构建一个二进制加法器的实例,我们可以学习到VHDL的语法规则、数据类型的使用以及模块化设计的思想。

2.时钟分频器(Clock Divider):时钟分频器可以将输入的时钟信号分频为较低频率的信号。

在数字电路中,时钟分频器是非常常见的一个模块,它可以用于控制其他电路的时序。

通过构建一个时钟分频器的实例,我们可以学习到VHDL的状态机设计、时序逻辑的实现以及对时钟信号的处理。

3.多路选择器(Multiplexer):多路选择器可以根据选择信号选择其中的一个输入信号输出。

在数字电路中,多路选择器可以用于实现多个输入的选择和切换。

通过构建一个多路选择器的实例,我们可以学习到VHDL的条件语句的使用、信号赋值的方法以及对多个输入信号的处理。

除了以上这些经典实例,VHDL的应用还非常广泛。

它可以用于设计CPU、FPGA、ASIC等各种数字电路,也可以用于设计计算机芯片、通信芯片等各种集成电路。

在数字系统的设计和开发中,VHDL是一种非常重要的工具和技术。

总结来说,VHDL是一种硬件描述语言,用于描述和设计数字电路。

掌握VHDL的基础知识是学习和使用VHDL的前提,经典实例的开发可

以帮助我们更好地理解VHDL的使用方法和特点。

VHDL在数字系统的设计和开发中有着广泛应用,是一种非常重要的工具和技术。