数字电路与逻辑设计 第6章计数器11

第六章时序逻辑电路-丽水学院

第六章 时序逻辑电路(14课时)本章教学目的、要求:1.掌握时序逻辑电路的分析方法。

2.掌握常用时序逻辑部件:寄存器、移位寄存器、由触发器构成的同步二进制递 增计数器和异步十进制递减计数器,及由集成计数器构成任意进制计数器。

3.熟悉常用中规模集成时序逻辑电路的逻辑功能及使用方法。

4.掌握同步时序逻辑电路的设计方法。

重点:时序逻辑电路在电路结构和逻辑功能上的特点;同步时序逻辑电路的分析方法;常用中规模集成时序逻辑电路的逻辑功能及使用方法;由集成计数器构成任意进制计数器。

难点:同步时序逻辑电路的设计方法第一节 概述(0.5课时)一、定义:1.定义:任一时刻电路的稳定输出不仅取决于当时的输入信号,而且还取决于电路原来的状态。

2.例:串行加法器:指将两个多位数相加时,采取从低位到高位逐位相加的方式完成相加运算。

需具备两个功能:将两个加数和来自低位的进位相加, 记忆本位相加后的进位结果。

全加器执行三个数的相加运算, 存储电路记下每次相加后的运算结果。

CP a i b i c i-1(Q ) s i c i (D )0 a 0 b 0 0 s 0 c 0 1 a 1 b 1 c 0 s 1 c 1 2 a 2 b 2 c 1 s 2 c2 3.结构上的特点:①时序逻辑电路通常包含组合电路和存储电路两部分,存储电路(触发器)是必不可少的;②存储器的输出状态必须反馈到组合电路的输入端,与外部输入信号共同决定组合逻辑电路的输出。

∑CI COCLKC1<1DQ 'Qia ic i-1c ib is 串行加法器电路二、时序电路的功能描述原状态:q1, q2, …, q l新状态:q1*,q2 *,…,q l*1.逻辑表达式。

Y = F [X,Q] 输出方程。

Z = G [X,Q] 驱动方程(或激励方程)。

Q* = H [Z,Q] 状态方程。

2.状态表、状态图和时序图。

三、时序电路的分类1. 按逻辑功能划分有:计数器、寄存器、移位寄存器、读/写存储器、顺序脉冲发生器等。

北京邮电大学数字电路与逻辑设计本科课件 第六章

Q0

1

C1

R

(1)74161:4位同 D0

& G9

& 1K

步二进制计数器。 功能:二进制加法

G5

& G10G17

FF1 & 1J

Q1

&

1

C1

R

计数、预置数、保持、D1

异步清零等。

CP

1 G2

计数脉冲

G6

& G11

& G12G18

& 1K

FF2 & 1J

Q2

&

1

C1

R

LOAD 为预置数控 D2

制端;

RD

(3)复位功能 复位也称为“清零”,将计数器的状态恢复到0状

态。复位是由复位控制端来控制。复位也分异步复

位和同步复位,异步复位不受时钟的控制,同步复

位除需要复位信号有效外,还必须在时钟的有效边 沿到来才能实现复位。

(4)进位(借位)功能 同步计数器可以有进位(借位)输出信号功能。当计

数器进入最大状态(例如输出全1),会产生进位输 出;或者当减法计数进入最小状态(输出全0),会 产生借位输出。进位/借位输出一般都是宽度等于 一个周期的脉冲,但是,脉冲的极性(正脉冲或负脉 冲)则要取决于具体的芯片,可从手册中的描述或功 能表中获得。

CKB的时钟),实现8421码十进制异步计数;

4.从CKB输入外部时钟,且 QD接到CKA,实现5421

码十进制异步计数。QA

QB

QC

QD

1J SD

C1

1KRD

1J C1

1KRD

1J C1

1KRD

& SD

数字电子技术基础-第六章_时序逻辑电路(完整版)

T0 1

行修改,在0000 时减“1”后跳变 T1 Q0 Q0(Q3Q2Q1)

为1001,然后按

二进制减法计数

就行了。T2 Q1Q0 Q1Q0 (Q1Q2Q3 )

T3 Q2Q1Q0

50

能自启动

47

•时序图 5

分 频

10 分 频c

0

t

48

器件实例:74 160

CLK RD LD EP ET 工作状态 X 0 X X X 置 0(异步) 1 0 X X 预置数(同步) X 1 1 0 1 保持(包括C) X 1 1 X 0 保持(C=0) 1 1 1 1 计数

49

②减法计数器

基本原理:对二进 制减法计数器进

——74LS193

异步置数 异步清零

44

(采用T’触发器,即T=1)

CLKi

CLKU

i 1

Qj

j0

CLKD

i 1

Qj

j0

CLK0 CLKU CLKD

CLK 2 CLKU Q1Q0 CLK DQ1Q0

45

2. 同步十进制计数器 ①加法计数器

基本原理:在四位二进制 计数器基础上修改,当计 到1001时,则下一个CLK 电路状态回到0000。

EP ET 工作状态

X 0 X X X 置 0(异步)

1 0 X X 预置数(同步)

X 1 1 0 1 保持(包括C)

X 1 1 X 0 保持(C=0)

1 1 1 1 计数

39

同步二进制减法计数器 原理:根据二进制减法运算 规则可知:在多位二进制数 末位减1,若第i位以下皆为 0时,则第i位应翻转。

Y Q2Q3

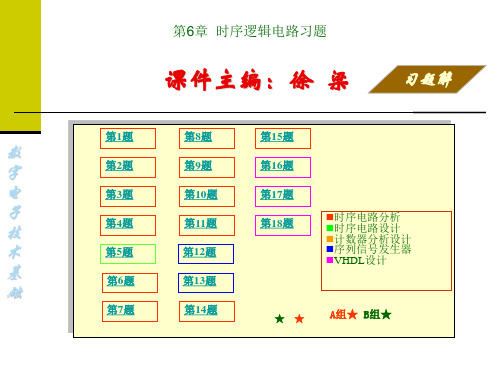

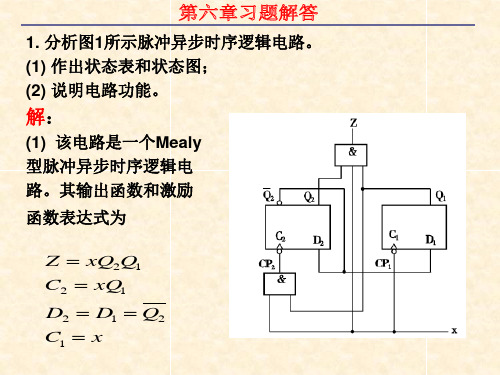

第06章时序逻辑电路习题解

[题6.20]分析图P 6.20给出的电路,说明这是多少进制的计数器,两片之间是多少进制。 74LSl61的功能表见表6.3.4。

解:这是采用整体置数法接成的计数器。 在出现LD'=0信号以前,两片74LSl61均按十六进制计数。即第(1)片到第(2) 片为十六进制。当第(1)片计为2,第(2)片计为5时产生LD'=0信号,待下一个 CLK信号到达后两片74LSl61同时被置零,总的进制为 5 X 16+2+1=83 故为八十三进制计数器。

图A 6.12

[题6.13]试分析图P 6.13的计数器在M=1和M=0时各为几进制。

解:图P6.13电路是采用同步置数法用74160接成的可变进制计数器。在M=1的 状态下,当电路进入Q3Q2Q1Q0=1001(九)以后,LD'=0。下一个CLK到达时将 D3D2D1D0=0100(四)置入电路中,使Q3Q2Q1Q0=0100,再从0100继续作加 法计数。因此,电路在0100到1001这六个状态间循环,构成六进制计数器。同 理,在M=0的情况下,电路计到1001后置入0010(二),故形成八进制计数器。

[题6.6]分析图P 6.6给出的时序电路,画出电路的状态转换图,检查电路能否自启动,说 明电路实现的功能。A为输入变量。

解:由电路图写出驱动方程为 J1=K1=1 J2=K2=A Q1 将上述驱动方程代入JK触发器的特性方程,得到状态方程 Q1*=Q1' Q2*=A Q1 Q2 输出方程为 Y=AQ1Q2+A'Q1'Q2' 根据状态方程和输出方程画出的状态转换图如图A 6.6所示。因为不存在无效 状态,所以电路不存在自启动与否的问题。 当A=0时电路对CLK脉冲作二进制加法计数,A=1时作二进制减法计数。

数字电路与逻辑设计 第6章计数器11

74190: 4位十进制同步加/减计数器。 74191: 4位二进制同步加/减计数器。

1.

Q0 QA IJA &

集成同步计数器74161

Q1 Q2 Q3 CO QB R IKA & ≥1 IJB & ≥1 & & & & R IKB & QC IJC & ≥1 & & R IKC & QD IJD & ≥1 & R IKD & &

∧

CR LD D3 D2 D1 D 0 1

CR LD D3 D2 D1 D 0 1

∧

CTT CTP CP

1 计数脉冲

由前面例题分析中可以发现,用反馈置零法设计 计数器存在一个普遍规律:

例3:用74161计数器实现模12计数。 Q3Q 2 CR

1 CP

CTP D3D2D1D0 CO CTT

1 CP

例2:分析图示电路的功能

1

CTP CTT D3 D2 D1 D0 CO

74161

Q3 Q2 Q1 Q0

LD

CP

CR

&

2、采用清零法设计任意模值计数器设计步骤

☆

确定有效状态

☆ 找出反馈清零状态 产生反馈清零信号 ☆ 画出计数器的逻辑电路

反馈清0法的基本思想是: 计数器从全0状态S0开始计数,计满 M个状态产生清0信号,使计数器恢复 到初态S0,然后再重复前面过程。

&

&

&

&

1

1

1

&

LD

D0

CR

D1

CP

D2

数字逻辑 第六章习题答案

根据真值表画出激励函数和输出函数卡诺图(略),化简后可 得:

(5) 画出逻辑电路图 根据激励函数和输出函数表达式,可画出实现给定功能的逻 辑电路如图11所示。该电路存在无效状态10,但不会产生挂 起现象,即具有自启动功能。

7 试用与非门构成的基本R-S触发器设计一个 脉冲异步模4加1计数器。 解(1) 设电路输入脉冲为x,状态变量为 y1y0,其状态表如表9所示。

(2)该电路的状态图、状态表

(3)该电路是一个“x1—x2—x3”序列检测器。

4 分析图7所示脉冲异步时序电路,作出时间 图并说明该电路逻辑功能。

解:(1) 该电路是一个 Moore型脉冲异步时序逻辑 电路,其输出即电路状态。激 励函数表达式为

(2)电路次态真值表

(3)时间图

(4)该电路是一个模4计数器。

(4) 确定激励函数和输出函数 确定激励函数和输出函数时注意: ● 对于多余状态y2y1=10和不允许输入x2x1=11,可作为无关条 件处理; ● 当输入x2x1=00时,电路状态保持不变; ● 由于触发器时钟信号作为激励函数处理,所以,可假定次态 与现态相同时,触发器时钟信号为0,T端为d。 据此,可列出激励函数和输出函数真值表如表8所示。

(2) 根据状态表和RS触发器的功能表,可列出激 励函数真值表如表10所示。

Байду номын сангаас

(3)化简后,可得激 励函数最简表达式为:

(4)根据激励函数表达式,可画出逻辑电路 图如图12所示。

5 用D触发器作为存储元件,设计一个脉冲异 步时序电路。该电路在输入端x的脉冲作用 下,实现3位二进制减1计数的功能,当电 路状态为“000”时,在输入脉冲作用下输 出端Z产生一个借位脉冲,平时Z输出0。

《数字电路与系统设计》第6章习题答案

l ee t h e \1210101…X/Z0/01/0X/Z11…100…6.3对下列原始状态表进行化简: (a)解:1)列隐含表: 2)进行关联比较3)列最小化状态表为:a/1b/0b b/0a/0aX=1X=0N(t)/Z(t)S(t)解:1)画隐含表: 2)进行关联比较: 6.4 试画出用MSI 移存器74194构成8位串行 并行码的转换电路(用3片74194或2片74194和一个D 触发器)。

l ee t-h e \r 91行''' 试分析题图6.6电路,画出状态转移图并说明有无自启动性。

解:激励方程:略 状态方程:略状态转移图 该电路具有自启动性。

6.7 图P6.7为同步加/减可逆二进制计数器,试分析该电路,作出X=0和X=1时的状态转移表。

解:题6.7的状态转移表X Q 4nQ 3nQ 2nQ 1nQ 4n +1Q 3n +1Q 2n +1Q 1n +1Z 0 0 0 0 0 1 1 1 1 1 0 1 1 1 1 1 1 1 0 0 0 1 1 1 0 1 1 0 1 0 0 1 1 0 1 1 1 0 0 0 0 1 1 0 0 1 0 1 1 0 0 1 0 1 1 1 0 1 0 0 0 1 0 1 0 1 0 0 1 0 0 1 0 0 1 1 0 0 0 0 0 1 0 0 0 0 1 1 1 0 0 0 1 1 1 0 1 1 0 0 0 0 1 1 0 0 1 0 1 0 0 0 1 0 1 0 1 0 0 0 0 0 1 0 0 0 0 1 1 0 0 0 0 1 1 0 0 1 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 1 1 0 0 0 0 0 0 0 1 0 1 0 0 0 1 0 0 1 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 0 0 0 1 0 1 0 0 0 1 0 1 0 1 0 1 0 1 0 1 1 0 0 1 0 1 1 0 0 1 1 1 0 1 0 1 1 1 1 0 0 0 0 1 1 0 0 0 1 0 0 1 0 1 1 0 0 1 1 0 1 0 0 1 1 0 1 0 1 0 1 1 0 1 1 0 1 1 1 1 0 0 0 1 1 1 0 0 1 1 0 1 0 1 1 1 0 1 1 1 1 0 0 1 1 1 1 0 1 1 1 1 1 11 1116.8分析图6.8电路,画出其全状态转移图并说明能否自启动。

《数字电路与逻辑设计》实验考核抽测,2011年11月

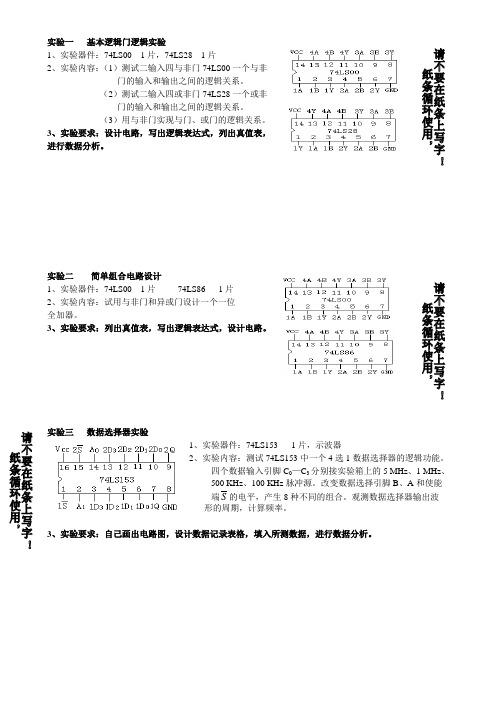

实验一基本逻辑门逻辑实验1、实验器件:74LS00 1片,74LS28 1片2、实验内容:(1)测试二输入四与非门74LS00一个与非门的输入和输出之间的逻辑关系。

(2)测试二输入四或非门74LS28一个或非门的输入和输出之间的逻辑关系。

(3)用与非门实现与门、或门的逻辑关系。

3、实验要求:设计电路,写出逻辑表达式,列出真值表,进行数据分析。

实验二简单组合电路设计1、实验器件:74LS00 1片74LS86 1片2、实验内容:试用与非门和异或门设计一个一位全加器。

3、实验要求:列出真值表,写出逻辑表达式,设计电路。

实验三数据选择器实验1、实验器件:74LS153 1片,示波器2、实验内容:测试74LS153中一个4选1数据选择器的逻辑功能。

四个数据输入引脚C0—C3分别接实验箱上的5 MHz、1 MHz、500 KHz、100 KHz脉冲源。

改变数据选择引脚B、A和使能端S的电平,产生8种不同的组合。

观测数据选择器输出波形的周期,计算频率。

3、实验要求:自己画出电路图,设计数据记录表格,填入所测数据,进行数据分析。

实验四 译码器实验(1)1、实验器件:74LS139 1片2、实验内容:测试74LS139中一个2—4译码器的逻辑功能。

四个译码输出引脚0Y —3Y 接电平指示灯。

改变 引脚S 、A 1、A 0的电平。

观测并记录指示灯的显示状态。

3、实验要求:画出电路图,自己设计数据记录表格,填入所测数据,进行数据分析。

实验五 译码器实验(2)1、实验器件:74LS139 1片2、实验内容:试用74LS139 2—4译码器扩展成3—8译码器。

输出引脚07Y Y 接电平指示灯。

改变引脚S 、A 1、A 0的电平。

观测并记录指示灯的显示状态。

3、实验要求:列出真值表,写出逻辑表达式,设计电路。

实验六 一位全加器的设计1、实验器件:74LS86 1片,74LS08 1片,74LS32 1片2、实验内容:试用与非门、与门、或门设计一个一位全加器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

计数器的模 计数器所能计算的脉冲数目的最大值

(即电路所能表示状态数目的最大值)

二、计数器的分类

按触发器的翻转次序,分为同步和异步计数器 按进位制,分为模二、模十和任意模计数器 按逻辑功能,分为加法、减法和可逆计数器 按集成度,分为小规模与中规模集成计数器

三、集成同步计数器 介绍:

异步清除:当CR=0时,Q均为0

74161 4位二进制加法计数(异步清除)

74160 十进制同步计数器(异步清除)

同步清除: 是当CR=0时,在时钟信号作用下, 实现清除。 74163 4位二进制加法计数(同步清除) 74162 十进制同步计数器(同步清除)

集成同步计数器

74192:双时钟触发的4位十进制同步加/减计数器. 74193: 双时钟触发的4位二进制同步加/减计数器.

74161 CR

CP

1 0

1 01 0 0 0

&

1 0

G2

G1 G3 &

1 2

3

&

1 0

当第十个CP↑到来: 基本触发器Q=0,/CR=0, 使Q3Q2Q1Q0=0000。 当第十个CP↓到来: 1Q 0 基本触发器Q=1, /CR=1。 10 在第十个CP的↑或↓沿的 作用下,Q端输出的清0信号 宽度和计数脉冲CP=1的持续 时间相同。足以保证各级触 发器能正常工作。

∧

CR LD D3 D2 D1 D 0 1

CR LD D3 D2 D1 D 0 1

∧

CTT CTP CP

1 计数脉冲

由前面例题分析中可以发现,用反馈置零法设计 计数器存在一个普遍规律:

例3:用74161计数器实现模12计数。 Q3Q 2 CR

1 CP

CTP D3D2D1D0 CO CTT

1 CP

例1、用74161组成十进制(N=10)计数器

解:

用CR 0实现反馈置0 。

选择初态为0,0~9为有效状态,10~15为 无效状态。 CR=Q3Q1 ☆ 当输入十个CP脉冲,Q3Q2Q1Q0=1010时, 强制计数器置0。强制置0信号是异步置0,与 CR Q3Q1 0 计数器其它状态无关。因而1010这个状态不 计算在主循环内。

74161

Q3 Q2 Q1 Q0

CR

LD

CP

&

0 1 2 3 4 5 6 7 8 9 10

CR=Q3Q1

功能:M=10同步计数器

1

☆ 为什么1010状态不算在主循 环内,用波形图说明

CP

Q0 Q1 Q2 Q3 CR

CTP D3D2D1D0CO CTT 74161 CR

LD Q3Q2 Q1Q0

1

2

3

CP

LD: 同步预置,低电平有效

Q3 ~ Q0:数据输出端 CTP、CTT:使能端,多片级联

2)74161逻辑功能描述

CTP CTT D3 D2 D1 D0 CO CR 0

74161逻辑功能表

清零 预置 使能 LD CTT CTP × × × 时钟 预置数据 输入 输 出

CP D3D2D1D0

× ××××

假设:Q1比Q3速度快,低位先翻。

CP Q0 Q1 Q2 Q3

CR

1

2

3

4

5

6

7

8

9 10

当Q1由1→0,Q3没来的及翻,/CR早已变为1 ,造成Q3Q2Q1Q0=1000 。发生错误计数

1

CTP D3D2D1D0 CO CTT

加基本RS触发器,使 /CR 脉冲宽度变宽

LD Q Q Q Q 3 2 1 0

G2

基本触发器Q=0,/CR=0,使 Q3Q2Q1Q0=0000。

CP

1 0

1 01 0 0 0

&

G1 G3 &

1 2

3

&

1 0

Q

1Q 0

当第十个CP↓到来:

基本触发器Q=1,/CR=1。

在第十个CP的↑或↓沿的作用 下,Q端输出的清0信号宽度和计 数脉冲CP=1的持续时间相同。足 以保证各级触发器能正常工作。

1

CTP CTT D3 D2 D1 D0 CO

采用CT74161

态序表 Q3 Q2 Q1 Q0 CR 0 0 0 0 0 0 0 0 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 0 1 1 0 0 1 1 0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 1 1 1 1 1 1 1 1 1 0

&

&

&

&

1

1

1

&

LD

D0

CR

D1

CP

D2

D3

CTP CT T

1、集成同步计数器—74161

1). 逻辑符号

四个J-K触发器构成 D3 ~ D0:数据输入端 CP: 时钟输入, 上升沿有效 CR: 异步清零, 低电平有效

CTP

CTT D3 D2 D1 D0 CO

74161

Q3 Q2 Q1 Q0

CR

LD

CP Q0 Q1 Q2 Q3

CR

1

2

3

4

5

6

7

8

9 10

当Q1由1→0,Q3没来的及翻,/CR早已变为1 ,造成Q3Q2Q1Q0=1000 。发生错误计数

1

CTP D3D2D1D0 CO CTT

加基本RS触发器,使 /CR 脉冲宽度变宽

LD Q Q Q Q 3 2 1 0

74161 CR

当第十个CP↑到来: 1 0

2 、四位二进制同步计数器——CT74163

CT74163功能表 CT74161功能表

输 CP Ф ↑ ↑ Ф Ф ↑ CR 0 1 1 1 1 LD Ф 0 1 1 1 Ф Ф 0 Ф 1 入 CTT CT P Ф Ф Ф 0 1 输 A B C D ФФФФ 0 AB C D ФФФФ 保 ФФФФ 保 ФФФФ 计 0 出 Q A QB QC QD 0 持 持 数 0 C D A B

例2:分析图示电路的功能

1

CTP CTT D3 D2 D1 D0 CO

74161

Q3 Q2 Q1 Q0

LD

CP

CR

&

2、采用清零法设计任意模值计数器设计步骤

☆

确定有效状态

☆ 找出反馈清零状态 产生反馈清零信号 ☆ 画出计数器的逻辑电路

反馈清0法的基本思想是: 计数器从全0状态S0开始计数,计满 M个状态产生清0信号,使计数器恢复 到初态S0,然后再重复前面过程。

☆

Q3Q2Q1Q0 0 0 0 0 0 0 0 1 0 0 1 0 1 0 0 1 (1 0 1 0) 1 0 1 1

1 1 1 1

反馈电路是一个二输入与非门

最后画出原理电路图:

1

CTP

CTT

D3 D2 D1 D0

CO

74161

Q3 Q2 Q1 Q0

CR

LD

CP

&

假设:Q1比Q3速度快,低位先翻

常用时序逻辑电路:计数器

1. 掌握计数器的基本概念及分类; 2. 学会通过功能表了解计数器的逻辑功能; 3. 灵活运用中规模计数器模块分析设计任 意模计数电路。

一、计数器的概念

计数器

用来计算输入脉冲数目的时序逻辑电路。它是用 电路的不同状态来表示输入脉冲的个数。

电路作用:分频、定时、产生脉冲序列、数字运算等;

1

1

1

1

+ 0

0

0

1

1 × × × × CR A B C D CTT CO CTP 74161(A) >CP Q Q Q Q LD

A B C D

1 × × × ×

1

1

1

CR A B C D CTT CO 1 CTP 74161(B) LD >CP Q A QB Q CQ D

1

串行进位 异步级联

计数状态 : 0000 0000 ~1111 1111

Q

4

5

6

7

8

9

CP Q0 Q1 Q2 Q3 G1 CR

利用异步清零法实现模10计数的波形图: 1 2 3 4 5 6 7 8 9 10

(一)反馈清零法

采用CT74161 态序表 N Q3 Q 2 Q 1 Q 0 0 1 2 3 4 5 6 7 8 9 10 11 12 0 0 0 0 0 0 0 0 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 0 1 0 1 0 1 0 1 0 1 0

4

5

6

7

8

9

10

CP

&

同步计数器最低位Q0在CP↑ 翻转。先画最低位Q0

Q1在Q0↓翻 Q2在Q1↓翻 Q3在Q2↓翻 当第十个脉冲上升沿到达后Q3Q2Q1Q0=1010,/CR=0。只要 /CR=0,计数器强制置0。1010只能使Q3Q1出现一个很窄的小毛刺。 缺点:Q1输出波形上有毛刺。造成/CR脉冲宽度太窄,清0不可靠。

时钟 CP 预置数据输入 D3 D2 D1 D0 输出 Q3 Q2 Q1 Q0 工作模式

0

1 1 1 1

×

0 1 1 1

×

× 0 1 1

×

× × 0 1

×

↑ × × ↑

×

× × ×

×

× × ×

×

× × ×

×

× × ×

0

0

0

0

异步清零

同步置数 数据保持 数据保持 加法计数