VerilogHDL经典程序非常适合新手

数字电路应用之Verilog HDL语言常用经典程序例题(Quartus II软件)

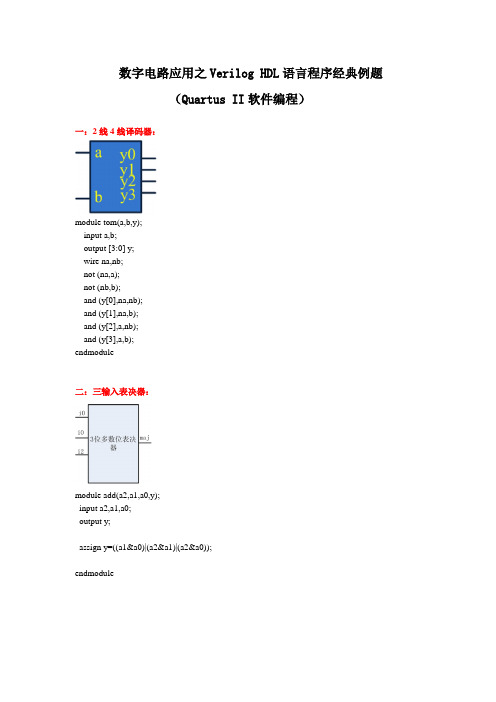

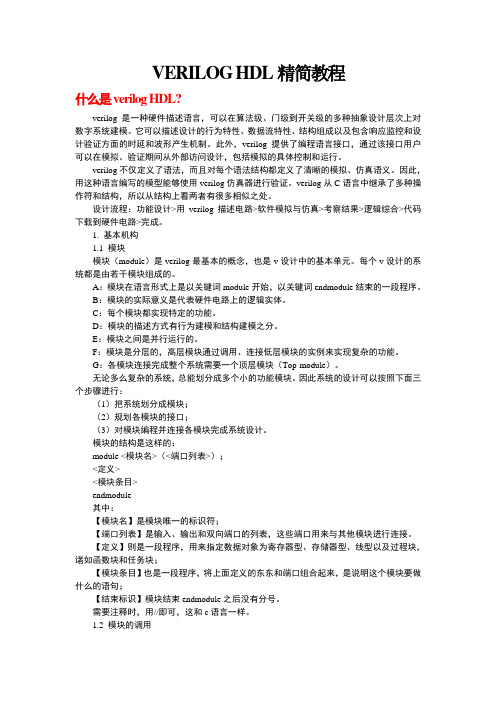

数字电路应用之Verilog HDL语言程序经典例题(Quartus II软件编程)一:2线4线译码器:module tom(a,b,y);input a,b;output [3:0] y;wire na,nb;not (na,a);not (nb,b);and (y[0],na,nb);and (y[1],na,b);and (y[2],a,nb);and (y[3],a,b);endmodule二:三输入表决器:module add(a2,a1,a0,y);input a2,a1,a0;output y;assign y=((a1&a0)|(a2&a1)|(a2&a0));endmodule三:3线8线译码器:module fulladd(a2,a1,a0,y);input a2,a1,a0;output [7:0] y;assign y[0]= ~( ~a2 & ~a1 & ~a0); assign y[1]= ~( ~a2 & ~a1 & a0); assign y[2]= ~( ~a2 & a1 & ~a0); assign y[3]= ~( ~a2 & a1 & a0); assign y[4]= ~( a2 & ~a1 & ~a0); assign y[5]= ~( a2 & ~a1 & a0); assign y[6]= ~( a2 & a1 & ~a0); assign y[7]= ~( a2 & a1 & a0);endmodule四:BIN2BCD码制转换:module fulladd(y,d,e);input [6:0] y;output [3:0] d,e;assign d=y/10;assign e=y%10;endmodule五:4位比较器:module tom(y,x,d);input [3:0] y,x;output [2:0] d;assign d[2]=(x>y)?1:0;assign d[1]=(x==y)?1:0;assign d[0]=(x<y)?1:0;endmodule六:四位全加器:法一:(调用程序法)module fulladd4(sum,c_in,c_out,a,b); output [3:0] sum;output c_out;input [3:0] a,b;input c_in;wire c1,c2,c3;fulladd fa0(sum[0],c1,a[0],b[0],c_in); fulladd fa1(sum[1],c2,a[1],b[1],c1); fulladd fa2(sum[2],c3,a[2],b[2],c2); fulladd fa3(sum[3],c_out,a[3],b[3],c3); endmodule//程序调用module fulladd(sum, c_out, a, b, c_in); output sum, c_out;input a, b, c_in;wire s1, c1, c2;xor (s1, a, b);and (c1, a, b);xor (sum, s1, c_in);and (c2, s1, c_in);xor (c_out, c2, c1);endmodule法二:(通用法)module fulladd4(A,B,Cin,SUM,Cout); input [3:0] A,B;input Cin;output [3:0] SUM;output Cout;assign {Cout,SUM}=A+B+Cin; endmodule七:七段显示译码器:法一:module bbc(a,d,g);input [3:0] a;output [6:0] d;output [3:0] g;reg [6:0] d;assign g=4'b0001;always @(a)begincase(a)4'b0000 :d=7'b100_0000;4'b0001 :d=7'b111_1001;4'b0010 :d=7'b010_0100;4'b0011 :d=7'b011_0000;4'b0100 :d=7'b001_1001;4'b0101 :d=7'b001_0010;4'b0110 :d=7'b000_0010;4'b0111 :d=7'b111_1000;4'b1000 :d=7'b000_0000;4'b1001 :d=7'b001_0000;default :d=7'b000_0000;endcaseendendmodule法二:module bbc(a,d,g);input [3:0] a;output [6:0] d;output [3:0] g;reg [6:0] d;assign g=4'b0001;always @(a)beginif (a==4'b0000) d=7'b100_0000;else if (a==4'b0001) d=7'b111_1001;else if (a==4'b0010) d=7'b010_0100;else if (a==4'b0011) d=7'b011_0000;else if (a==4'b0100) d=7'b001_1001;else if (a==4'b0101) d=7'b001_0010;else if (a==4'b0110) d=7'b000_0010;else if (a==4'b0111) d=7'b111_1000;else if (a==4'b1000) d=7'b000_0000;else if (a==4'b1001) d=7'b001_0000;else d=7'b000_0000; endendmodule八:8—3优先编码器:法一:module qq (y,d,g);input [7:0] y;output [2:0] d;output [3:0] g;reg [2:0] d;assign g=4'b0001;always @ ybeginif (y[7]==1) d=3'b111;else if (y[6]==1) d=3'b110;else if (y[5]==1) d=3'b101;else if (y[4]==1) d=3'b100;else if (y[3]==1) d=3'b011;else if (y[2]==1) d=3'b010;else if (y[1]==1) d=3'b001;else if (y[0]==1) d=3'b000;endendmodule法二:module encoder(none_on,outcode,a, b, c, d, e, f, g, h); output[2:0] outcode;output none_on;input a, b, c, d, e, f, g, h;reg[3:0] outtemp;assign {none_on, outcode} = outtemp;always @(a or b or c or d or e or f or g or h)begincasex ({a, b, c, d, e, f, g, h})8'B????_???1 : outtemp=4'b0_111;8'B????_??10 : outtemp=4'b0_110;8'B????_?100 : outtemp=4'b0_101;8'B????_1000 : outtemp=4'b0_100;8'B???1_0000 : outtemp=4'b0_011;8'B??10_0000 : outtemp=4'b0_010;8'B?100_0000 : outtemp=4'b0_001;8'B1000_0000 : outtemp=4'b0_000;8'B0000_0000 : outtemp=4'b1_000;endcaseendendmodule九:计数器:module bbc(clk,set,reset,d,y);input set,reset,clk;input [3:0] d;output [7:0] y;reg [7:0] y;always@(posedge clk or negedge reset or posedge set) if(~reset) y<=8'b0;else if (set) y[3:0]<=d[3:0];else y<=y+1'b1;endmodule十:移位寄存器:module asd (clk,set,reset,d,y,cin);input clk,set,reset,cin;input [3:0] d;output [7:0] y;reg [7:0] y;always@(posedge clk)beginif(~reset) y=0;else if(set)beginy[7:4]=y[3:0] ;y[3:0]=d[3:0];endelsebeginy=y<<1;y[0]=cin;endendendmodule十一:4位乘法:法一:module bbc(y,a,b);input [3:0] a;input [3:0] b;output [7:0] y;reg [7:0] y;reg[7:0] temp_a;reg[3:0] temp_b;integer i;always @(a or b)beginy=0;temp_a=a;temp_b=b;beginfor(i=0;i<=3;i=i+1)beginif(temp_b[0]) y=y+temp_a;temp_a=temp_a<<1;temp_b=temp_b>>1;endendendendmodule法二:module qq(outcome,a,b);output [8:1] outcome;input [4:1] a,b;reg [8:1] outcome;integer i;always@(a or b)beginoutcome=0;for(i=1;i<=4;i=i+1)if (b[1]) outcome=outcome + (a<<(i-1)); endendmodule十二:数码管跑马灯:module asd(cr,clk,a,b,c,d,e,f,g);input cr,clk;output a,b,c,d,e,f,g;reg a,b,c,d,e,f,g;integer i=0;always @ (posedge clk or negedge cr)beginif(~cr)begin{a,b,c,d,e,f,g}=7'b111_1111;i=0;endelse if(clk)begini=i+1;if(i==1) {a,b,c,d,e,f,g}=7'b011_1111;if(i==2) {a,b,c,d,e,f,g}=7'b101_1111;if(i==3) {a,b,c,d,e,f,g}=7'b110_1111;if(i==4) {a,b,c,d,e,f,g}=7'b111_0111;if(i==5) {a,b,c,d,e,f,g}=7'b111_1011;if(i==6) {a,b,c,d,e,f,g}=7'b111_1101;if(i==7) {a,b,c,d,e,f,g}=7'b111_1110;if(i==8) {a,b,c,d,e,f,g}=7'b000_0000;if(i==9)begin{a,b,c,d,e,f,g}=7'b111_1111;i=0;endendendendmodule十三:LED跑马灯:module add(cr,clk,y);input cr,clk;output [7:0] y;reg [7:0] y;integer i;always@(posedge clk or negedge cr) beginif(~cr)beginy=0;i=-1;endelse if (clk)begini=i+1;y=0;y[i]=1;beginif(i==7)i=-1;endendendendmodule。

Verilog语法入门,初学者必看

Verilog的词法约定1Verilog是大小写相关的,其中的关键字全部为小写。

2空白符由空格、制表符、和换行符组成。

3单行注释以“//”开始,verilog将忽略此处到行尾的内容。

多行注释以“/*”开始,以“*/”结束。

多行注释不允许嵌套4操作符有三种:单目操作符、双目操作符和三目操作符。

5数字声明Verilog中有两种数字生命:指明位数的数字和不指明位数的数字指明位数的数字表示形式:<size>’<base format><number>Size用来指明数字位宽度,只能用十进制整数表示Base format包括十进制(’d或’D),二进制(’b或’B),八进制(‘o或’O),十六进制(‘h或’H)例如4’b1111 //4位2进制数12’h3ac //12位16进制数不指明位数的数字:如果数字说明中没有指定基数,那么默认表示为十进制数。

如果没有指定位宽,则默认的位宽度与仿真器和使用的计算机有关(最小为32位)。

‘o21 //32位八进制数X值和Z值:不确定值用X表示,高阻用Z值表示。

在八进制数中代表3位,十六进制中代表4位。

12’h12X //这是一个12位16进制数,其中低四位不确定负数:在表示位宽的数字前面增加一个减号来表示它是一个负数。

-6’d3 //一个6位的用二进制补码形式存储的十进制数3,表示负数-6’sd3 //一个6位的带符号算数运算的负数下划线符号和问号:除了第一个字符,下划线“_”可以出现在数字中的任何位置,它的作用只是提高可读性,在编译阶段会被忽略掉问号“?”是z的另一种表示,使用问号的目的在于增强casex和casez语句的可读性。

在这两条语句中,“?”表示不必关心的情况。

12’B1111_0011_1110 // 增强可读性4’b10?? //相当于4’b10zz6字符串是双引号括起来的一个字符队列。

对于字符串的限制是,它必须在一行中书写完,不可书写在多行中,也不能包含回车符。

verilog HDL精简教程

VERILOG HDL精简教程什么是verilog HDL?verilog是一种硬件描述语言,可以在算法级、门级到开关级的多种抽象设计层次上对数字系统建模。

它可以描述设计的行为特性、数据流特性、结构组成以及包含响应监控和设计验证方面的时延和波形产生机制。

此外,verilog提供了编程语言接口,通过该接口用户可以在模拟、验证期间从外部访问设计,包括模拟的具体控制和运行。

verilog不仅定义了语法,而且对每个语法结构都定义了清晰的模拟、仿真语义。

因此,用这种语言编写的模型能够使用verilog仿真器进行验证。

verilog从C语言中继承了多种操作符和结构,所以从结构上看两者有很多相似之处。

设计流程:功能设计>用verilog描述电路>软件模拟与仿真>考察结果>逻辑综合>代码下载到硬件电路>完成。

1. 基本机构1.1 模块模块(module)是verilog最基本的概念,也是v设计中的基本单元。

每个v设计的系统都是由若干模块组成的。

A:模块在语言形式上是以关键词module开始,以关键词endmodule结束的一段程序。

B:模块的实际意义是代表硬件电路上的逻辑实体。

C:每个模块都实现特定的功能。

D:模块的描述方式有行为建模和结构建模之分。

E:模块之间是并行运行的。

F:模块是分层的,高层模块通过调用、连接低层模块的实例来实现复杂的功能。

G:各模块连接完成整个系统需要一个顶层模块(Top-module)。

无论多么复杂的系统,总能划分成多个小的功能模块。

因此系统的设计可以按照下面三个步骤进行:(1)把系统划分成模块;(2)规划各模块的接口;(3)对模块编程并连接各模块完成系统设计。

模块的结构是这样的:module <模块名>(<端口列表>);<定义><模块条目>endmodule其中:【模块名】是模块唯一的标识符;【端口列表】是输入、输出和双向端口的列表,这些端口用来与其他模块进行连接。

Verilog HDL入门教程

文档编号 资源类别: HDL语言

版本 1.0

密级

内部公开

共41页

Verilog HDL入门教程

(仅供内部使用)

拟制: 批准: 批准:

中研基础 中研基础

日期: 日期: 日期:

2004.8.3 yyyy/mm/dd

版权所有 不得复制

Verilog HDL 入门教程

日期 2004.8.3

修订记录

2.4.1 历史 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 2.4.2 能力 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 3 Verilog HDL 建模概述 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 3.1 模块 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 3.1.1 简单事例 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Verilog+HDL+入门教程华为

文档中心文档编号资源类别:HDL语言版本1.0密级内部公开共41页Verilog HDL入门教程(仅供内部使用)拟制:批准:批准:中研基础中研基础日期:日期:日期:2004.8.3yyyy/mm/dd版权所有不得复制日期2004.8.3 修订版本1.00描述初稿完成修订记录作者目录1 前言. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52 HDL设计方法学简介. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52.1 数字电路设计方法. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52.2 硬件描述语言. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62.3 设计方法学. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62.4 Verilog HDL简介. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72.4.1 历史. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72.4.2 能力. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73 Verilog HDL 建模概述. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93.1 模块. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93.1.1 简单事例. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93.1.2 模块的结构. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .103.1.3 模块语法. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113.2 时延. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113.3 三种建模方式. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123.3.1 结构化描述方式. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123.3.2 数据流描述方式. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143.3.3 行为描述方式. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153.3.4 混合设计描述. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .164 Verilog HDL 基本语法. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174.1 标识符. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174.1.1 定义. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .174.1.2 关键词. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174.1.3 书写规范建议. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .174.2 注释. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174.3 格式. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184.4 数字值集合. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .184.4.1 值集合. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184.4.2 常量. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .184.5 数据类型. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .205.1 模块定义结构. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .285.2 模块端口. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .285.3 实例化语句. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .295.4 结构化建模具体实例. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .316 数据流建模. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 346.1 连续赋值语句. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 346.2 阻塞赋值语句. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 346.3 数据流建模具体实例. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .347 行为建模. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 357.1 简介. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .357.2 顺序语句块. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Verilog HDL 入门教程关键词:摘要:本文主要介绍了Verilog HDL 语言的一些基本知识,目的是使初学者能够迅速掌握HDL 设计方法,初步了解并掌握Verilog HDL语言的基本要素,能够读懂简单的设计代码并能够进行一些简单设计的Verilog HDL建模。

VerilogHDL基础语法入门

1) $dumpfile(“file.dump”); //打开记录数据变化的数据文件

2) $dumpvars();

//选择需要记录的变量

3) $dumpflush; //把记录在数据文件中的资料转送到硬盘保存

4) $dumpoff;

//停止记录数据变化

5) $dumpon;

//重新开始记录数据变化

模块的抽象

技术指标:

用文字表示 用算法表示 用高级行为的Verilog模块表示

RTL/功能级:

用可综合的Verilog模块表示

门级/结构级:

用实例引用的Verilog模块表示

版图布局/物理级:

用几何形状来表示

行为综合 综合前仿真

逻辑综合

综合后仿真 布局布线

第三部分.简单的 Verilog HDL 模块

转换为门级电路互连的电路结构(综合)。 ▪ 需要对已经转换为门级电路结构的逻辑

进行测试(门级电路仿真)。 ▪ 需要对布局布线后的电路结构进行测试。

(布局布线后仿真)。

模块的测试

激励和控 制信号

被测模块

输出响应 和验证

模块的测试

测试模块常见的形式:

module t; reg …; //被测模块输入/输出变量类型定义 wire…; //被测模块输入/输出变量类型定义 initial begin …; …; …; end … …//产生测试信号 always #delay begin …; end … …//产生测试信号

▪ Verilog HDL的构造性语句可以精确地建立信号的 模型。这是因为在Verilog HDL中,提供了延迟和输出 强度的原语来建立精确程度很高的信号模型。信号值 可以有不同的的强度,可以通过设定宽范围的模糊值 来降低不确定条件的影响。

VerilogHDL的入门学习(可编辑修改word版)

先记下来:1、不使用初始化语句;2、不使用延时语句;3、不使用循环次数不确定的语句,如:forever,while 等;4、尽量采用同步方式设计电路;5、尽量采用行为语句完成设计;6、always 过程块描述组合逻辑,应在敏感信号表中列出所有的输入信号;7、所有的内部寄存器都应该可以被复位;8、用户自定义原件(UDP 元件)是不能被综合的。

一:基本Verilog 中的变量有线网类型和寄存器类型。

线网型变量综合成wire,而寄存器可能综合成WIRE,锁存器和触发器,还有可能被优化掉。

二:verilog 语句结构到门级的映射1、连续性赋值:assign连续性赋值语句逻辑结构上就是将等式右边的驱动左边的结点。

因此连续性赋值的目标结点总是综合成由组合逻辑驱动的结点。

Assign 语句中的延时综合时都将忽视。

2、过程性赋值:过程性赋值只出现在always 语句中。

阻塞赋值和非阻塞赋值就该赋值本身是没有区别的,只是对后面的语句有不同的影响。

建议设计组合逻辑电路时用阻塞赋值,设计时序电路时用非阻塞赋值。

过程性赋值的赋值对象有可能综合成wire, latch,和flip-flop,取决于具体状况。

如,时钟控制下的非阻塞赋值综合成flip-flop。

过程性赋值语句中的任何延时在综合时都将忽略。

建议同一个变量单一地使用阻塞或者非阻塞赋值。

3、逻辑操作符:逻辑操作符对应于硬件中已有的逻辑门,一些操作符不能被综合:===、!==。

4、算术操作符:Verilog 中将reg 视为无符号数,而integer 视为有符号数。

因此,进行有符号操作时使用integer,使用无符号操作时使用reg。

5、进位:通常会将进行运算操作的结果比原操作数扩展一位,用来存放进位或者借位。

如:Wire [3:0] A,B;Wire [4:0] C;Assign C=A+B;C 的最高位用来存放进位。

6、关系运算符:关系运算符:<,>,<=,>=和算术操作符一样,可以进行有符号和无符号运算,取决于数据类型是reg,net 还是integer。

VerilogHDL入门教程

VerilogHDL入门教程第一部分:Verilog HDL概述(约200字)Verilog HDL是一种硬件描述语言,用于描述和建模数字电路和系统。

它是一种被广泛使用的硬件设计语言,特别适合用于逻辑设计和验证。

Verilog HDL提供了一种形式化的方式来表示数字电路和系统的行为和结构,使得工程师可以更轻松地进行硬件设计和验证。

第二部分:Verilog HDL基础(约400字)在Verilog HDL中,最基本的组成单元是模块。

模块是Verilog HDL中的一个独立的、可重用的单元,可以由其他模块实例化和连接。

每个模块由端口(输入和输出)和内部功能(如逻辑代码和信号声明)组成。

module and_gate(input a, input b, output y);assign y = a & b;endmodule这个模块表示一个与门,它有两个输入a和b,一个输出y。

使用assign语句,我们将输出y连接到输入a和b的逻辑与操作。

第三部分:Verilog HDL高级特性(约400字)除了基本的模块和连接之外,Verilog HDL还提供了一些高级特性,用于更复杂的电路建模和验证。

一种特殊的构造是always块。

always块用于描述模块内的行为,基于一个条件或时钟信号的变化。

例如,下面是一个使用always块的模块示例:module counter(input clk, input enable, output reg count);if (enable)count = count + 1;endendmodule这个模块表示一个简单的计数器,在时钟上升沿时根据enable信号增加计数器的值。

Verilog HDL还支持层次化的建模,允许将模块层次化地组织起来,以便更好地管理和复用代码。

层次化建模通过使用模块的层次命名和连接来实现。

例如,我们可以将上面的计数器模块实例化为另一个模块,如下所示:module top_module(input clk, input enable, output reg count);countercounter_inst(.clk(clk), .enable(enable), .count(count));endmodule这个模块实例化了上面定义的计数器模块,并将其内部信号和端口连接到外部接口。

中文版Verilog_HDL简明教程

中文版Verilog HDL简明教程:第1章简介Verilog HDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。

被建模的数字系统对象的复杂性可以介于简单的门和完整的电子数字系统之间。

数字系统能够按层次描述,并可在相同描述中显式地进行时序建模。

Verilog HDL 语言具有下述描述能力:设计的行为特性、设计的数据流特性、设计的结构组成以及包含响应监控和设计验证方面的时延和波形产生机制。

所有这些都使用同一种建模语言。

此外,Verilog HDL语言提供了编程语言接口,通过该接口可以在模拟、验证期间从设计外部访问设计,包括模拟的具体控制和运行。

Verilog HDL语言不仅定义了语法,而且对每个语法结构都定义了清晰的模拟、仿真语义。

因此,用这种语言编写的模型能够使用Verilog仿真器进行验证。

语言从C编程语言中继承了多种操作符和结构。

Verilog HDL提供了扩展的建模能力,其中许多扩展最初很难理解。

但是,Verilog HDL语言的核心子集非常易于学习和使用,这对大多数建模应用来说已经足够。

当然,完整的硬件描述语言足以对从最复杂的芯片到完整的电子系统进行描述。

历史Verilog HDL语言最初是于1983年由Gateway Design Automation公司为其模拟器产品开发的硬件建模语言。

那时它只是一种专用语言。

由于他们的模拟、仿真器产品的广泛使用,Verilog HDL 作为一种便于使用且实用的语言逐渐为众多设计者所接受。

在一次努力增加语言普及性的活动中,Verilog HDL语言于1990年被推向公众领域。

Open Verilog International (OVI)是促进Verilog 发展的国际性组织。

1992年, OVI决定致力于推广Verilog OVI标准成为IEEE标准。

这一努力最后获得成功,Verilog 语言于1995年成为IEEE标准,称为IEEE Std 1364-1995。

Verilog HDL入门

线网型:wire,tri

wor,trior,wand,triand,trireg,tri1,tri0 supply0,supply1

寄存器型:

reg integer,time real,realtime

wire和tri

用于连接单元的连线是最常见的线网类型。 默认值为z。 wire与tri语法和语义一致; 三态线可以用于描述多个驱动源驱动同一根线 的线网类型;并且没有其他特殊的意义。 通常都用wire。 其他线网型用于底层设计与仿真,FPGA设计通 常不会涉及。

简单的Verilog程序

该程序例子通过另一种方法描述了一个三态 门。 在这个例子中存在着两个模块:模块trist1 在这个例子中存在着两个模块:模块trist1 tri_inst。 调用模块 mytri 的实例元件 tri_inst。 是上层模块。 模块 trist1 是上层模块。模块 mytri 则被 称为子模块。 称为子模块。 通过这种结构性模块构造可构成特大型模块 。

例:always @(b or c) always a=b&c;

元件(实)例化

例:and and1(a,b,c); BUFG BUFG_inst ( .O(out), // Clock buffer output .I(in) // Clock buffer input );

注意

三种方式可以在同一个模块之内混合使用 ; 同一个模块内可以有多个always块,多个 assign和多个元件例化。 所有这些单元是并行执行的。 这些单元的书写顺序不影响逻辑功能;

128状态值集合:包含强度信息

其他值集合

整数(32bits) 实数 字符串 时间(64bits) 布尔值(0,1) ……

提纲

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、2线-4线译码器module counter4(q1,q0,ncr,cp);input cp,ncr;output q1,q0;reg q1,q0;always@(posedge cp or negedge ncr) beginif(~ncr){q1,q0}<=2'b00;else{q1,q0}<={q1,q0}+1'b1;endendmodule二、4选1数据选择器module selector4_1(i0,i1,i2,i3,a1,a0,y); input i0,i1,i2,i3,a1,a0;output y;reg y;always@(a1or a0)begincase({a1,a0})2'b00:y=i0;2'b01:y=i1;2'b10:y=i2;2'b11:y=i3;default:y=0;一、2线-4线译码器module counter4(q1,q0,ncr,cp);input cp,ncr;output q1,q0;reg q1,q0;always@(posedge cp or negedge ncr) beginif(~ncr){q1,q0}<=2'b00;else{q1,q0}<={q1,q0}+1'b1;endendmodule二、4选1数据选择器module selector4_1(i0,i1,i2,i3,a1,a0,y); input i0,i1,i2,i3,a1,a0;output y;reg y;always@(a1or a0)begincase({a1,a0})2'b00:y=i0;2'b01:y=i1;2'b10:y=i2;2'b11:y=i3;default:y=0;endcaseendendmodule三、8线-3线优先编码器module encoder8_3(i,y,ei,eo,gs); input[7:0]i;input ei;output[2:0]y;output eo;output gs;reg[2:0]y;reg eo,gs;always@(ei or i)beginif(ei==1'b1)begin{y,eo,gs}=5'b111_11;endelse if(i[7:0]==8'b1111_1111) begin{y,eo,gs}=5'b111_01;endelse if(i[7]==1'b0)begin{y,eo,gs}=5'b000_10;endelse if(i[6]==1'b0)begin{y,eo,gs}=5'b001_10;endelse if(i[5]==1'b0)begin{y,eo,gs}=5'b010_10;endelse if(i[4]==1'b0)begin{y,eo,gs}=5'b011_10;endelse if(i[3]==1'b0)begin{y,eo,gs}=5'b100_10;endelse if(i[2]==1'b0)begin{y,eo,gs}=5'b101_10;endelse if(i[1]==1'b0)begin{y,eo,gs}=5'b110_10;endelse if(i[0]==1'b0)begin{y,eo,gs}=5'b111_10;endendendmodule四、模10加法计数器和一个时钟10分频电路1、模10加法计数器cnt_10的Verilog代码module count_10(clk,reset,dout);input clk;input reset;output[3:0]dout;reg[3:0]dout;always@(posedge clk or negedge reset)beginif(~reset)dout<=4'b0000;elseif(dout<4'b1001)dout<=dout+1;elseif(dout==4'b1001)dout<=4'b0000;endendmodule2、10分频模块fenpin_10的Verilog代码module fenpin_10(clk_in,reset,clk_out); input clk_in;input reset;output[0:0]clk_out;reg[0:0]clk_out;reg[3:0]count;always@(posedge clk_in or negedge reset) beginif(~reset)count<=4'b0000;elseif(count<4'b1001)count<=count+1;elseif(count==4'b1001)begincount<=4'b0000;clk_out<=~clk_out;endendendmodule五、10110101序列发生器module generator(clk,endcaseendendmodule三、8线-3线优先编码器module encoder8_3(i,y,ei,eo,gs); input[7:0]i;input ei;output[2:0]y;output eo;output gs;reg[2:0]y;reg eo,gs;always@(ei or i)beginif(ei==1'b1)begin{y,eo,gs}=5'b111_11;endelse if(i[7:0]==8'b1111_1111) begin{y,eo,gs}=5'b111_01;endelse if(i[7]==1'b0)begin{y,eo,gs}=5'b000_10;endelse if(i[6]==1'b0)begin{y,eo,gs}=5'b001_10;else if(i[5]==1'b0)begin{y,eo,gs}=5'b010_10;endelse if(i[4]==1'b0)begin{y,eo,gs}=5'b011_10;endelse if(i[3]==1'b0)begin{y,eo,gs}=5'b100_10;endelse if(i[2]==1'b0)begin{y,eo,gs}=5'b101_10;endelse if(i[1]==1'b0)begin{y,eo,gs}=5'b110_10;endelse if(i[0]==1'b0)begin{y,eo,gs}=5'b111_10;endendendmodule四、模10加法计数器和一个时钟10分频电路1、模10加法计数器cnt_10的Verilog代码module count_10(clk,reset,dout);input clk;input reset;output[3:0]dout;reg[3:0]dout;always@(posedge clk or negedge reset)beginif(~reset)dout<=4'b0000;elseif(dout<4'b1001)dout<=dout+1;elseif(dout==4'b1001)dout<=4'b0000;endmodule2、10分频模块fenpin_10的Verilog代码module fenpin_10(clk_in,reset,clk_out); input clk_in;input reset;output[0:0]clk_out;reg[0:0]clk_out;reg[3:0]count;always@(posedge clk_in or negedge reset) beginif(~reset)count<=4'b0000;elseif(count<4'b1001)count<=count+1;elseif(count==4'b1001)begincount<=4'b0000;clk_out<=~clk_out;endendendmodule五、10110101序列发生器module generator(clk,clr,dout);input clk;input clr;output dout;reg dout;reg[7:0]temp;always@(posedge clk or negedge clr) beginif(~clr)begindout<=1'b0;temp<=8'b10110101;endelsebegintemp<=temp<<1;temp[0]<=temp[7];dout<=temp[7];endendendmodule六、利用状态机设计一个1011序列检测器module detec1101(clk,reset,din,get1101); input clk;input reset;input din;output get1101;reg get1101;reg[2:0]current_state;reg[2:0]next_state;parameter IDLE=3'b000,S1=3'b001,S2=3'b010,S3=3'b100,s4=3'b100;always@(posedge clk or negedge reset)beginif(~reset)current_state<=IDLE;elsecurrent_state<=next_state;endalways@(din or current_state or next_state)beginnext_state=3'b111;case(current_state)IDLE:next_state=(din==1'b1)?S1:IDLE;S1:next_state=(din==1'b1)?S2:IDLE;S2:next_state=(din==1'b1)?S2:S3;S3:next_state=(din==1'b1)?s4:IDLE;s4:next_state=(din==1'b1)?S1:IDLE;default:next_state=IDLE;endcaseendalways@(posedge clk)begincase(next_state)s4:get1101<=1'b1;IDLE,S1,S2,S3:get1101<=1'b0;default:get1101<=1'b0;endcaseend endmodule。