乒乓球游戏机--EDA课程设计--完整版本

EDA课程设计之乒乓球游戏机

分,该方就算胜了此局。

记分牌清零后,又可开始新的一局比赛2.2.2乒乓游戏机设计思路根据乒乓游戏机功能要求,可以分成四个模块来实现,其中corna模块为整个程序的核心,它实现了整个系统的全部逻辑功能;模块CH41A在数码的片选信号时,送出相应的数据;模块sel产生数码管的片选信号;模块disp是7段译码器。

2.3乒乓球各模块的设计2.3.1 控制模块的设计模块CORNA 分两个进程,第一个进程实现逻辑功能,第二个进程将整数的记分转换为十进制数,便于译码显示。

AF,AJ,BF,BJ分别为a方发球键和接球键,b方发球键和接球键,shift表示球所在的位置。

其vhdl程序描述如下:图1 模块CORNA1LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CORNAL ISawIN<=t1;bwIN<=t2;END PROCESS;END behav;2.3.2 送数据模块的设计送数据模块CH41A的vhdl程序描述如下:图2 模块CH41ALIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY CH41A ISPORT(sel:IN STD_LOGIC_VECTOR(2 DOWNTO 0);D0,d1,d2,d3:IN STD_LOGIC_VECTOR(3 DOWNTO 0);Q:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END CH41A;ARCHITECTURE behave OF CH41A ISBEGINPROCESS(sel)BEGINCASE sel ISWHEN”100”=>q<=d0;WHEN”101”=>q<=d1;WHEN”000”=>q<=d2;WHEN others=>q<=d3;END CASE;END PROCESS;END behav;2.3.3 产生数码管片选信号模块的设计产生数码管片选信号模块sel的vhdl程序描述如下:图3数码管片选信号模块sel LIBRARY IEEE;USE IEEE.S TD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY sel ISPORT(clk:IN STD_LOGIC;sell:OUT STD_LOGIC_VECTOR(2 DOWNTO 0)); END sel;ARCHITECTURE behav OF sel ISBEGINPROCESS(clk)VARIABLE tmp:STD_LOGIC_VECTOR(2 DOWNTO 0);BEGINIF clk’event and clk=’1’ THENIF tmp=”000” THENt mp:=”001”;ELSIF tmp=”001” THENt mp:=”100”;ELSIF t mp=”100” THENt mp:=”101”;ELSIF tmp=”101” THENt mp:=”000”;END IF;END IF;sell<=tmp;END PROCESS;END behav;2.3.4 7段译码器模块的设计7段译码器模块disp的vhdl的程序描述如下:图4 7段译码器模块disp LIBRARY IEEE;USE IEEE.S TD_LOGIC_1164.ALL;ENTITY disp ISPORT(d:IN STD_LOGIC_VECTOR(3 DOWNTO 0);Q:OUT STD_LOGIC_VECTOR(6 DOWNTO 0)); END disp;ARCHITECTURE behav OF disp ISBEGINPROCESS(d)BEGINCASE d ISWHEN”0000”=>q<=”0111111”;WHEN”0001”=>q<=”0000110”;WHEN”0010”=>q<=”1011011”;WHEN”0011”=>q<=”1001111”;WHEN”0100”=>q<=”1100110”;WHEN”0101”=>q<=”1101101”;WHEN”0110”=>q<=”1111101”;WHEN”0111”=>q<=”0100111”;WHEN”1000”=>q<=”1111111”;WHEN others=>q<=”1101111”;END CASE;END PROCESS;END behav;3.设计结果与分析3.1系统的波形仿真图5所示为A方发球,在恰当的时候B方接到球,当球回到A方时,A方又接到球,但B方再也没有接到球的仿真波形。

乒乓球游戏机EDA课程设计完整版本

乒乓球游戏机EDA课程设计完整版本

本文主要介绍了一款基于FPGA可编程硬件的乒乓球游戏机的设计。

本文将重点介绍

如何利用FPGA技术来搭建可编程硬件电路,如何使用Verilog HDL语言来设计数字电路,如何使用Quartus II环境来实现复杂任务,以及如何利用FPGA来完成乒乓球游戏机的EDA课程设计。

首先,在设计乒乓球游戏机的FPGA可编程硬件系统时,最重要的是硬件架构设计,

选择固定板来作为FPGA控制器,能够有效地根据游戏需求控制其各个功能,保证游戏机

运行稳定性和可靠性。

为了满足乒乓球游戏机的需求,FPGA控制器引入Verilog HDL语言,用数字电路的方式进行设计,从而构建出模拟端口,使用I/O 端口对乒乓球系统进行控制,其内部控制器模块实现了所有的乒乓球游戏逻辑功能。

在设计主板的时候,FPGA

中实现的硬件电路会结合安装在主板上的器件,比如七段LED显示器、微型键盘、LED灯等,从而使乒乓球游戏机更加复杂,实现更多的功能。

接下来,使用Quartus II环境,实现乒乓球游戏机的EDA课程设计。

首先,在Quartus II中编写Verilog HDL语言编程,利用FPGA可编程硬件系统设计乒乓球游戏逻辑,构建出特定的模块,实现系统的功能。

其次,编写控制逻辑,运用Verilog HDL语言

编程,在FPGA硬件中得到设计的图像图案,以及搭建复杂的乒乓球游戏的系统结构,实

现乒乓球游戏的控制逻辑功能。

最后,完成了乒乓球游戏机的EDA课程设计。

乒乓球游戏机课程设计

乒乓球游戏机课程设计一、课程目标知识目标:1. 学生理解乒乓球游戏机的基本结构和工作原理,掌握相关电子元件的功能和连接方式。

2. 学生掌握编程控制乒乓球游戏机的技能,能够运用所学知识编写程序,实现乒乓球游戏机的运行和交互。

3. 学生了解乒乓球游戏机在现实生活中的应用,认识到科技与日常生活的紧密联系。

技能目标:1. 学生能够运用所学的电子知识和编程技能,独立完成乒乓球游戏机的搭建和编程。

2. 学生能够在团队协作中发挥自己的专长,共同解决制作过程中遇到的问题,提高团队协作能力。

3. 学生通过动手实践,培养创新思维和问题解决能力。

情感态度价值观目标:1. 学生培养对科学技术的兴趣和好奇心,激发学习电子和编程的热情。

2. 学生在学习过程中,培养坚持不懈、勇于挑战的精神,增强自信心。

3. 学生通过团队协作,学会尊重他人、沟通合作,培养良好的团队精神和人际交往能力。

4. 学生认识到科技发展对生活的影响,激发为我国科技创新贡献力量的责任感。

课程性质:本课程为实践性较强的综合课程,结合电子、编程和团队合作等元素,旨在培养学生的动手能力、创新思维和团队协作能力。

学生特点:六年级学生对电子和编程有一定的基础,好奇心强,喜欢动手操作,具备一定的团队合作能力。

教学要求:注重理论与实践相结合,关注学生的个体差异,提高学生的动手实践能力和创新精神,培养团队协作能力。

在教学过程中,将目标分解为具体的学习成果,便于教学设计和评估。

二、教学内容1. 电子元件知识:介绍乒乓球游戏机中涉及的电子元件,如电源、微控制器、传感器等,结合课本相关知识,让学生了解各元件的作用和连接方式。

2. 编程技能:教授学生使用编程软件,如Arduino或Scratch,编写控制乒乓球游戏机的程序。

内容包括基本语法、逻辑控制、传感器数据读取等。

3. 乒乓球游戏机结构:讲解乒乓球游戏机的整体结构,分析各部分的功能和相互关系,指导学生进行实际搭建。

4. 团队合作:组织学生分组,进行团队协作,共同完成乒乓球游戏机的制作,培养学生团队协作能力。

EDA课程设计_7

乒乓球游戏电路设计一、乒乓球设计方案(1)我们设计的乒乓球游戏是以一排发光二极管交替发光指示乒乓球的行进路径, 其行进的速度可由输入的时钟信号控制。

乒乓球比赛是甲乙双方的比赛, 所以用两个按键模拟左右两个球拍;我们还要设计一个乒乓球控制模块, 即当发光二极管到最后一个的瞬间, 若检测到对应的表示球拍的键的信号, 立即使“球”反向运行, 如果此瞬间没有接到按键信号, 将给出失败鸣叫, 同时为对方记1分, 并将记分显示出来, 然后由对方重新发球以此类推;还要设计失球计数器的高低位计数模块;乒乓球行进方向控制模块, 主要由发球键控制;还要有一个失球提示发生模块。

(2)要知道乒乓球的游戏规则, 以多少分为一局, 谁先得到一定的分数谁就赢一局, 以此来判断输赢。

(3)用数码管显示双方的得分, 还要设计一个十进制计数器, 来显示分数。

(4)在乒乓球设计方案时还要考虑球速的问题。

二、乒乓球游戏电路的设计程序1.LIBRARY IEEE;--乒乓球游戏顶层文件use ieee.std_logic_1164.all;entity TENNIS isport(bain,bbin,clr,clk,souclk:in std_logic;ballout:out std_logic_vector(7 downto 0);countah,countal,countbh,countbl:out std_logic_vector(3 downto 0);lamp,speaker:out std_logic);end entity TENNIS;architecture ful of TENNIS iscomponent soundport(clk,sig,en:in std_logic;sout:out std_logic);end component;component ballctrlport(clr,bain,bbin,serclka,serclkb,clk:in std_logic; bdout,serve,serclk,ballclr,ballen:out std_logic);end component;component ballport(clk,clr,way,en:in std_logic;ballout:out std_logic_vector(7 downto 0));end component;component boardport(ball,net,bclk,serve:in std_logic;couclk,serclk:out std_logic);end component;component cou10port(clk,clr:in std_logic;cout:out std_logic;qout:out std_logic_vector(3 downto 0));end component;component cou4port(clk,clr:in std_logic;cout:out std_logic;qout:out std_logic_vector(3 downto 0));end component;component mwayport(servea,serveb:in std_logic;way:out std_logic);end component;signalnet,couclkah,couclkal,couclkbh,couclkbl,cah,cbh:std_logic; signalserve,serclka,serclkb,serclk,ballclr,bdout,way,ballen:std_lo gic;signal bbll:std_logic_vector(7 downto 0);beginnet<=bbll(4);ballout<=bbll;lamp<=clk;uah:cou4 port map(couclkah,clr,cah,countah);ual:cou10 port map(couclkal,clr,couclkah,countal);ubh:cou4 port map(couclkbh,clr,cbh,countbh);ubl:cou10 port map(couclkbl,clr,couclkbh,countbl); ubda:board port map(bbll(0),net,bain,serve,couclkal,serclka);ubdb:board port map(bbll(7),net,bbin,serve,couclkbl,serclkb);ucpu:ballctrlportmap(clr,bain,bbin,serclka,serclkb,clk,bdout,serve,serclk, ballclr,ballen);uway:mway port map(serclka,serclkb,way);uball:ball port map(clk,ballclr,way,ballen,bbll);usound:sound port map(souclk,ballen,bdout,speaker);end ful;2.library ieee;use ieee.std_logic_1164.all;entity sound isport(clk:in std_logic; --发声时钟sig:in std_logic; --正确接球信号en:in std_logic; --球拍接球脉冲sout:out std_logic); --提示声输出, 接小喇叭end entity sound;architecture ful of sound isbeginsout<=clk and (not sig) and en;--球拍接球, 没接到时, 发提示声end ful;3.library ieee; --总控制模块use ieee.std_logic_1164.all;entity ballctrlisport(clr:in std_logic; --系统复位bain:in std_logic; --左球拍bbin:in std_logic; --右球拍seclka:in std_logic; --左拍准确接球或发球serclkb:in std_logic; --右拍准确接球或发球clk:in std_logic; --乒乓球灯移动时钟bdout:out std_logic; --球拍接球脉冲serve:out std_logic; --发球状态信号serclk:out std_logic; --球拍正确接球信号ballclr:out std_logic; --乒乓球灯清零信号ballen:out std_logic); --乒乓球灯使能end entity ballctrl;architecture ful of ballctrl issignal bd:std_logic;signal ser:std_logic;beginbd<=bain or bbin;ser<=serclka or serclkb;serclk<=ser;--球拍正确接球信号bdout<=bd; --球拍接球脉冲process(clr,clk,bd)beginif(clr='1')then --系统复位serve<='1'; --系统处在职发球状态ballclr<='1'; --乒乓球灯清零elseif(bd='1')then --系统正常--球拍发球或接球时ballclr<='1'; --乒乓球灯清零if(ser='1')then --球拍发球或准确接球ballen<='1'; --乒乓球灯使能允许serve<='0'; --系统处在接球状态else ballen<='0';serve<='1'; --系统处在发球状态end if;else ballclr<='0';--没发球或接球时乒乓球灯不清零end if;end if;end process;end ful;4.--乒乓球灯模块library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity ball isport(clk:in std_logic; --乒乓球灯前进时钟clr:in std_logic; --乒乓球灯清零way:in std_logic; --乒乓球灯前进方向en:in std_logic; --乒乓球灯使能ballout:out std_logic_vector(7 downto 0));--乒乓球灯end entity ball;architecture ful of ball issignal lamp:std_logic_vector(9 downto 0);beginprocess(clk,clr,en)beginif(clr='1') then lamp<="1000000001";--清零elsif en='0' thenelsif (clk'event and clk='1')then--使能允许, 乒乓球灯前进时钟上升沿if(way='1') then lamp(9 downto 1)<=lamp(8 downto 0);lamp(0)<='0';--乒乓球灯右移else lamp(8 downto 0)<=lamp(9 downto 1); lamp(9)<='0';--乒乓球灯左移end if;end if;ballout<=lamp(8 downto 1);end process;end ful;5.--乒乓拍模块library ieee;use ieee.std_logic_1164.all;entity board isport(ball:in std_logic; --接球点, 也就是乒乓球灯的末端net:in std_logic; --乒乓球灯的中点, 乒乓球过中点时, counclk、serclk复位bclk:in std_logic; --球拍接球信号serve:in std_logic; --发球信号couclk:out std_logic;serclk:out std_logic);end entity board;architecture ful of board isbeginprocess(bclk,net)beginif(net='1')then serclk<='0';couclk<='0';--乒乓球过中点时, counclk、serclk复位elsif(bclk'event and bclk='1')then—球拍接球时if(serve='1')then serclk<='1';--系统处于发球状态时—发球成功else—系统处于接球状态if(ball='1')then serclk<='1';--乒乓球刚落在接球点上, 接球成功else serclk<='0';couclk<='1';end if;end if;end if;end process;end ful;6.--十进制计数器用来做失球低位计数library ieee;use ieee.std_logic_1164.all;entity mway isport(servea:in std_logic;serveb:in std_logic;way:out std_logic);end entity mway;architecture ful of mway isbeginprocess(servea,serveb)beginif(servea='1')then way<='1';elsif(serveb='1')then way<='0';end if;end process;end ful;7、--四进制计数器用来做失球高位计数library ieee;use ieee.std_logic_1164.all;entity mway isport(servea:in std_logic;serveb:in std_logic;way:out std_logic);end entity mway;architecture ful of mway isbeginprocess(servea,serveb)beginif(servea='1')then way<='1';elsif(serveb='1')then way<='0';end if;end process;end ful;8、--乒乓球前进方向产生模块library ieee;use ieee.std_logic_1164.all;entity mway isport(servea:in std_logic;--左选手发球信号serveb:in std_logic;--右选手发球信号way:out std_logic);--乒乓球灯前进方向信号end entity mway;architecture ful of mway isbeginprocess(servea,serveb)beginif(servea='1')then way<='1';--左选手发球方向向右elsif(serveb='1')then way<='0';--右选手发球方向向左end if;end process;end ful;三、乒乓球游戏程序的仿真波形仿真波形图四、硬件测试方法然后我们就要测试硬件, 下载文件。

EDA课程设计之乒乓球游戏机

EDA课程设计之乒乓球游戏机乒乓球是我国非常流行的一项体育运动,它既可以作为一项竞技运动,也可以作为一项休闲娱乐活动。

乒乓球游戏机是一种将乒乓球运动与电子游戏相结合的娱乐设备,通过电子屏幕和操纵杆模拟真实的乒乓球比赛,使玩家能够在室内环境中享受乒乓球运动的乐趣。

本文将从乒乓球游戏机的设计思路、功能和优势等方面进行详细介绍。

首先,乒乓球游戏机的设计思路是将真实的乒乓球比赛场景还原到电子游戏中。

通过操纵杆控制游戏中的球拍移动,并通过电子屏幕实时显示球的运动轨迹和计分情况,使玩家能够真实地感受到乒乓球比赛的紧张和刺激。

同时,乒乓球游戏机还可以根据玩家的操作水平设置不同的难度,提供多种游戏模式和关卡,使游戏更具娱乐性和挑战性。

其次,乒乓球游戏机的主要功能包括游戏模式选择、角色扮演、多人对战、即时对战等。

玩家可以根据自己的喜好选择不同的游戏模式进行游戏,例如单人模式、双人模式、联网对战模式等。

在游戏过程中,玩家可以选择不同的角色扮演,并通过不断挑战更高难度的关卡来提高自己的技术水平。

同时,乒乓球游戏机还支持多人对战和即时对战功能,玩家可以与朋友或其他玩家进行真人对战,增加游戏的互动性和竞技性。

乒乓球游戏机的优势主要体现在以下几个方面。

首先,乒乓球游戏机可以在室内环境中提供真实的乒乓球比赛体验,避免了受天气、场地等外界因素的影响。

其次,乒乓球游戏机采用电子屏幕显示球的运动轨迹和计分情况,可以实时调整比赛难度和计分规则,方便了玩家的操作和记录。

再次,乒乓球游戏机支持多种游戏模式和关卡,玩家可以根据自己的喜好选择不同的游戏方式,增加了游戏的可玩性和趣味性。

最后,乒乓球游戏机还可以通过联网对战功能,与其他玩家进行真人对战,增加了游戏的竞技性和社交性。

总之,乒乓球游戏机是一种将乒乓球运动和电子游戏相结合的娱乐设备,通过电子屏幕和操纵杆模拟真实的乒乓球比赛,使玩家能够在室内环境中享受乒乓球运动的乐趣。

它的设计思路是将真实的乒乓球比赛场景还原到电子游戏中,主要功能包括游戏模式选择、角色扮演、多人对战、即时对战等。

乒乓球游戏电路课程设计最终完成版

乒乓球游戏电路课程设计最终完成版第一篇:乒乓球游戏电路课程设计最终完成版电子课程设计——基于Verilog的乒乓游戏设计电路学院:专业、班级:姓名:学号:指导教师:2014年12月引言可编程器件的广泛应用,为数字系统的设计带来了极大的灵活性。

可编程器件可以通过软件编程对硬件的结构和工作方式进行重构,使得硬件的设计可以如同软件设计那样快捷方便。

高速发展的FPGA、CPLD兼有串、并行工作方式和高速、高可靠性的特点,在电子系统设计中得到了广泛应用。

通常使用硬件描述语言(Hardware Description Language,HDL)进行数字电子系统设计。

目前应用广泛的硬件描述语言有:VHDL语言,Verilog HDL语言,AHDL语言。

Verilog语言由于具有强大的行为描述能力和丰富的仿真语句从而成为系统设计领域最佳的硬件描述语言。

鉴于如上所述,本系统使用Verilog语言进行设计,采用自上向下的设计方法。

利用Quartus II 9.1 进行Verilog程序的编译与综合,然后用Modelism SE 6.0进行功能仿真和时序仿真,并使用EDA实验箱进行下载验证。

基于Verilog的乒乓游戏设计电路一、设计任务与要求任务:设计一个乒乓球游戏机,模拟乒乓球比赛的基本过程和规则,并能裁判和自动计分。

要求如下:1.使用乒乓球游戏机的甲乙双方在不同的位置罚球或击球。

2.乒乓球的位置和移动方向可由发光二极管和依次点亮的方向决定,为球的移动速度为一定值(我们设计中设为0.5秒移动一位)。

使用者可按乒乓球的位置发出相应的动作,在其他时候击球视为犯规,给对方加一分;都犯规双方各加一分。

二、总体框图设计思路根据乒乓球比赛的过程和规则,首先游戏开始,如果一方非正确击球则另一方加分,当分数大于11时获胜,游戏结束,系统设计流程图如图1所示。

图2给出了乒乓球游戏机的原理图。

用5个发光二极管代表乒乓球,在游戏机两侧各设置二个开关,一个是发球开关,一个是击球开关。

EDA课程设计——乒乓球比赛游戏机

《电子设计自动化(EDA)技术》课程设计报告题目: 乒乓球比赛游戏机姓名:院系:专业:学号:指导教师:完成时间: 年月日目录1 课程设计题目、内容与要求………………………………1.1 设计内容………………………………………………1.2 具体要求………………………………………………2 系统设计……………………………………………………2.1 设计思路………………………………………………2.2 系统原理(包含:框图等阐述)与设计说明等内容3 系统实现……………………………………………………注:此部分阐述具体实现,包含主要逻辑单元、模块、源代码等内容4 系统仿真……………………………………………………5 硬件验证(操作)说明……………………………………6 总结………………………………………………………7 参考书目…………………………………………………1课程设计题目、内容与要求1.1课程设计的题目乒乓球比赛游戏机1.2课程设计目的随着科学技术日益迅速的发展,数字系统已经深入到生活的各个方面。

它具有技术效果好,经济效益高,技术先进,造价较低,可靠性高,维修方便等许多优点。

使我们更加熟练掌握数字系统的设计。

对所学的专业知识有能力更好的应用在实践方面。

1.3课程设计要求(1)使用乒乓球游戏机的双方在不同位置发球或击球。

(2)乒乓球的位置和移动方向由灯亮和依次亮的方向决定。

使用者根据球的位置发出相应的动作(3)比赛用21分为一局来进行,双方设置各自的记分牌,任意一方先记满21分就获胜此局。

当记分牌清零后,开始新的一局比赛。

1.4课程设计内容设计一个由甲乙双方参赛,有裁判的三人乒乓球游戏机。

用8个(或更多个)LED排成一条直线,以中点为界,两边各代表参赛双方的位置,其中一只点亮的LED指示球的当前位置,点亮的LED依次从左到右,或从右到左,其移动的速度应能调节。

当“球”(点亮的那只LED)运动到某方的最后一位时,参赛者应能果断地按下位于自己一方的按纽开关,即表示启动球拍击球,若击中,则球向相反方向运动;若未中,球掉出桌外,则对方得一分。

乒乓球游戏机--EDA课程设计--完整版本

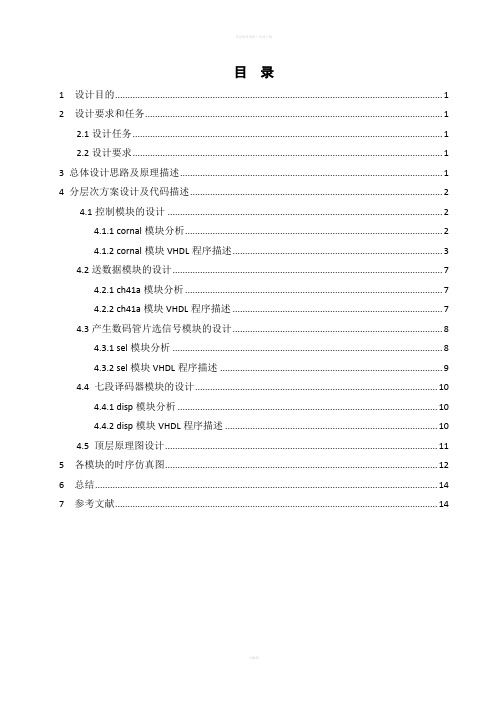

目录1 设计目的 (1)2 设计要求和任务 (1)2.1设计任务 (1)2.2设计要求 (1)3 总体设计思路及原理描述 (1)4 分层次方案设计及代码描述 (2)4.1控制模块的设计 (2)4.1.1 cornal模块分析 (2)4.1.2 cornal模块VHDL程序描述 (3)4.2送数据模块的设计 (7)4.2.1 ch41a模块分析 (7)4.2.2 ch41a模块VHDL程序描述 (7)4.3产生数码管片选信号模块的设计 (8)4.3.1 sel模块分析 (8)4.3.2 sel模块VHDL程序描述 (9)4.4 七段译码器模块的设计 (10)4.4.1 disp模块分析 (10)4.4.2 disp模块VHDL程序描述 (10)4.5 顶层原理图设计 (11)5 各模块的时序仿真图 (12)6 总结 (14)7 参考文献 (14)乒乓游戏机1 设计目的掌握熟悉的使用Quartus II 9.1软件的原理图绘制,程序的编写,编译以及仿真。

体会使用EDA综合过程中电路设计方法和设计思路的不同。

掌握使用EDA工具设计乒乓游戏机的的设计思路和设计方法。

2 设计要求和任务2.1设计任务设计一个乒乓球游戏机,该机模拟乒乓球比赛的基本过程和规则,并能自动裁判和几分。

2.2设计要求(1)甲乙双方各在不同的位置发球或击球。

(2)乒乓球的位置和移动方向由灯亮及依次点亮的方向决定,球移动的速度为0.1-0.5秒移动一位。

(3)11分为一局,甲乙双方都应设置各自的几分牌,任何一方先记满11分,该方胜出。

当记分牌清零后,重新开始。

3 总体设计思路及原理描述由乒乓游戏机功能,用原理图作为顶层模块,再将底层划分成四个小模块来实现:(1)cornal模块:整个程序的核心,它实现了整个系统的全部逻辑功能;(2)ch41a模块:在数码的片选信号时,送出相应的数据;(3)sel模块:产生数码管的片选信号;(4)disp模块:7段译码器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

目录1 设计目的 (1)2 设计要求和任务 (1)2.1设计任务 (1)2.2设计要求 (1)3 总体设计思路及原理描述 (1)4 分层次方案设计及代码描述 (2)4.1控制模块的设计 (2)4.1.1 cornal模块分析 (2)4.1.2 cornal模块VHDL程序描述 (3)4.2送数据模块的设计 (7)4.2.1 ch41a模块分析 (7)4.2.2 ch41a模块VHDL程序描述 (7)4.3产生数码管片选信号模块的设计 (8)4.3.1 sel模块分析 (8)4.3.2 sel模块VHDL程序描述 (9)4.4 七段译码器模块的设计 (10)4.4.1 disp模块分析 (10)4.4.2 disp模块VHDL程序描述 (10)4.5 顶层原理图设计 (11)5 各模块的时序仿真图 (12)6 总结 (14)7 参考文献 (14)乒乓游戏机1 设计目的掌握熟悉的使用Quartus II 9.1软件的原理图绘制,程序的编写,编译以及仿真。

体会使用EDA综合过程中电路设计方法和设计思路的不同。

掌握使用EDA工具设计乒乓游戏机的的设计思路和设计方法。

2 设计要求和任务2.1设计任务设计一个乒乓球游戏机,该机模拟乒乓球比赛的基本过程和规则,并能自动裁判和几分。

2.2设计要求(1)甲乙双方各在不同的位置发球或击球。

(2)乒乓球的位置和移动方向由灯亮及依次点亮的方向决定,球移动的速度为0.1-0.5秒移动一位。

(3)11分为一局,甲乙双方都应设置各自的几分牌,任何一方先记满11分,该方胜出。

当记分牌清零后,重新开始。

3 总体设计思路及原理描述由乒乓游戏机功能,用原理图作为顶层模块,再将底层划分成四个小模块来实现:(1)cornal模块:整个程序的核心,它实现了整个系统的全部逻辑功能;(2)ch41a模块:在数码的片选信号时,送出相应的数据;(3)sel模块:产生数码管的片选信号;(4)disp模块:7段译码器。

图3.1 结构层次图4 分层次方案设计及代码描述4.1控制模块的设计4.1.1 cornal模块分析a发球一、在范围内1、b没有接到球,a加1分,将灯光清零000 00 0002、b接到了球,则灯光为0 &【7位】二、在b方出界了1、如果b没有接到球,则a加分2、如果b接到了球,则灯光为0 &【7位】b发球一、在范围内1、a没有接到球,b加1分,并将灯光清零000 00 0002、a接到了球,则灯光计分为【7位】& 0二、在a方出界了1、a没有接到球,则b加分2、a接到了球,则灯光计分为【7位】& 0af,aj,bf,bj分别为a方发球键和接球键,b方发球键和接球键,shift表示球所在的位置。

图4.1 conal模块原理图4.1.2 cornal模块VHDL程序描述Library ieee;Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Entity cornal isPort(clr,af,aj,bf,bj,clk:in std_logic;Shift:out std_logic_vector(7 downto 0);Ah,al,bh,bl:out std_logic_vector(3 downto 0);Awin,bwin:out std_logic);End cornal;Architecture bahave of cornal isSignal amark,bmark:integer;BeginProcess(clr,clk)Variable a,b:std_logic;Variable she:std_logic_vector(7 downto 0);BeginIf clr=’0’ t hena:=’0’;b:=’0’;she:=”00000000”amark<=0;bmark<=0;elsif clk’event and clk=’1’ thenif a=’0’ and b=’0’ and af=’0’ then --a方发球 a:=’1’;she;=”10000000”;elsif a=’0’ and b=’0’ then bf=’0’ then --b方发球 b:=’1’;she:=”00000001”;elsif a=’1’ and b=’0’ then --a方发球后if she>8 thenif bj=’0’ then --b方过网击球amark<=amark+1; --a方加一分a:=’0’;b:=’0’;she:=”00000000”;elseshe:=’0’&she(7 downto 1); --b方没有击球end if;elsif she=0 then --球从b方出界amark<=amark+1; --a方加一分a:=’0’;b:=’0’;elseif bj=’0’ then --b方正常击球a:=’0’;b:=’1’;elseshe:=’0’&she(7 downto 1); --b方没有击球end if;end if;elsif a=’0’ and b=’1’then --b方发球if she<16 and she/=0 thenif aj=’0’ thenbmark<=bmark+1;a:=’0’;b:=’0’;she:=”00000000”;elseshe:=she(6 downto 0)&’0’;end if;elsif she=0 thenbmark<=bmark+1;a:=’0’;b:=’0’;elseif aj=’0’thena:=’1’;b:=’0’;elseshe:=she(6 downto 0)&’0’;end if;end if;end if;end if;shift<=she;end process;process(clk,clr,amark,bmark)variable aha,ala,bha,bla:std_logic_vector(3 downto 0); variable tmp1,tmp2:integer;variable t1,t2:std_logic;beginif clr=’0’then --清零aha:=”0000”;ala:=”0000”;bha:=”0000”;bla:=”0000”;tmp1:=0;tmp2:=0;t1:=’0’;t2:=’0’;elsif clk’event and clk=’1’ thenif aha=”0001” and ala=”0001” then --a方得分达到11分,则保持 aha:=”0001”;ala:=”0001”;t1:=’1’;elsif bha=”0001”and bla=”0001” then --b方得分达到11分,则保持 bha:=”0001”;bla:=”0001”;t2:=’1’;elsif amark>tmp1 thenif ala=”1001” thenala:=”0000”;aha:=aha+1;tmp1:=tmp1+1;elseala:=ala+1;tmp1:=tmp1+1;end if;elsif bmark>tmp2 thenif bla=”1001” thenbla:=”0000”;bha:=bha+1;tmp2:=tmp2+1;elsebla:=bla+1;tmp2:=tmp2+1;end if;end if;end if;al<=ala;bl<=bla;ah<=aha;bh<=bha;awin<=t1;bwin<=t2;end process;end behave;4.2送数据模块的设计4.2.1 ch41a模块分析图4.2 ch41a模块分析及原理图4.2.2 ch41a模块VHDL程序描述Library IEEE;Use IEEE.std_logic_1164.all;Entity ch41a isPort(sel:in std_logic_vector(2 downto 0);D0,d1,d2,d3:in std_logic_vector(3 downto 0);Q:out std_logic_vector(3 downto 0));End ch41a;Architecture behave of ch41a isBeginProcess(sel)BeginCase sel isWhen”100”=>q<=d0;When”101”=>q<=d1;When”000”=>q<=d2;When others=>q<=d3;End case;End process;End behave;4.3产生数码管片选信号模块的设计4.3.1 sel模块分析图4.3 sel模块分析及原理图4.3.2 sel模块VHDL程序描述Library ieee;Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Entity sel isPort(clk:in std_logic;Sell:out std_logic_vector(2 downto 0)); End sel;Architecture behave of sel isBeginProcess(clk)Variable tmp:std_logic_vector(2 downto 0); BeginIf clk’event and clk=’1’ thenIf tmp=”000” thenTmp:=”001”;Elsif tmp=”001” thenTmp:=”100”;Elsif Tmp=”100” thenTmp:=”101”;Elsif tmp=”101” thenTmp:=”000”;End if;End if;Sell<=tmp;End process;End behave;4.4 七段译码器模块的设计4.4.1 disp模块分析图4.4 disp模块分析及原理4.4.2 disp模块VHDL程序描述Library ieee;Use ieee.std_logic_1164.all;Entity disp isPort(d:in std_logic_vector(3 downto 0);Q:out std_logic_vector(6 downto 0));End disp;Architecture behave of disp isBeginProcess(d)BeginCase d isWhen”0000”=>q<=”0111111”;When”0001”=>q<=”0000110”;When”0010”=>q<=”1011011”;When”0011”=>q<=”1001111”;When”0100”=>q<=”1100110”;When”0101”=>q<=”1101101”;When”0110”=>q<=”1111101”;When”0111”=>q<=”0100111”;When”1000”=>q<=”1111111”;When others=>q<=”1101111”;End case;End process;End behave;4.5顶层原理图设计图4.5 顶层模块原理图5 各模块的时序仿真图图5.1为A方两次发球,B方没有接到球,A方得到2分的仿真波形图图5.1 仿真波形图图5.2所示为A方发球,B方提前击球的情况,此时,A方得一分。