杭州矽力杰笔试

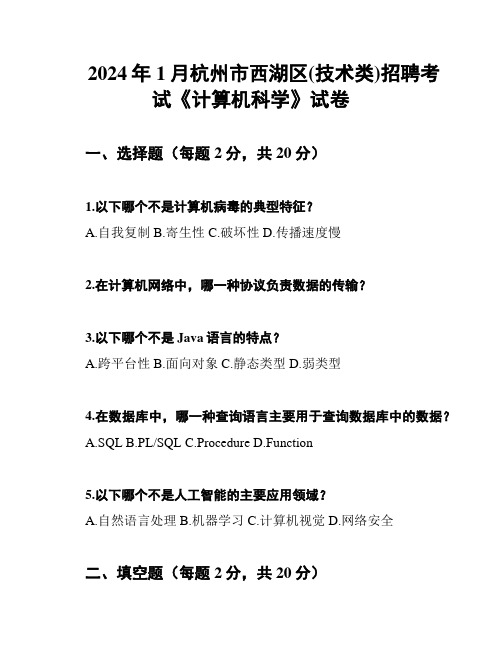

2024年1月杭州市西湖区(技术类)招聘考试《计算机科学》试卷

2024年1月杭州市西湖区(技术类)招聘考试《计算机科学》试卷一、选择题(每题2分,共20分)1.以下哪个不是计算机病毒的典型特征?A.自我复制B.寄生性C.破坏性D.传播速度慢2.在计算机网络中,哪一种协议负责数据的传输?3.以下哪个不是Java语言的特点?A.跨平台性B.面向对象C.静态类型D.弱类型4.在数据库中,哪一种查询语言主要用于查询数据库中的数据?A.SQLB.PL/SQLC.ProcedureD.Function5.以下哪个不是人工智能的主要应用领域?A.自然语言处理B.机器学习C.计算机视觉D.网络安全二、填空题(每题2分,共20分)6._____是一种用于描述计算过程的形式化语言。

7._____是一种用于管理和组织计算机硬件和软件资源的操作系统。

9._____是一种用于加密和解密数据的算法。

10._____是一种用于在计算机网络中传输文件的协议。

三、简答题(每题10分,共30分)11.请简述TCP/IP协议的作用和组成。

12.请简述面向对象编程的主要特点。

13.请简述人工智能的发展历程和主要应用领域。

四、案例分析题(共30分)14.某公司采用了一种基于Java语言开发的企业级应用,运行在Linux操作系统上,使用MySQL数据库存储数据。

请回答以下问题:1. 请简述Java语言在企业级应用开发中的优势。

2. 请简述Linux操作系统在企业级应用中的优势。

3. 请简述MySQL数据库在企业级应用中的优势。

五、编程题(共30分)15.请编写一个Java程序,实现以下功能:1. 输入一个字符串,输出字符串中字母和数字的个数。

2. 输入一个整数,输出它的阶乘。

半导体或芯片岗位招聘笔试题与参考答案2025年

2025年招聘半导体或芯片岗位笔试题与参考答案(答案在后面)一、单项选择题(本大题有10小题,每小题2分,共20分)1、在半导体工艺中,使用多种类型的光刻胶,其中最常用于大规模集成电路生产的是()。

A. GRI-45B. GRI-25C. GRI-46D. GRI-422、MOS(金属-氧化物-半导体)制作技术中,晶体管结构所采用的材料中不包括()。

A. 金属B. 绝缘体C. 导电材料D. 电阻体3.在半导体制造工艺中,以下哪个步骤不属于典型的半导体制造流程?A. 氧化B.光刻C. 薄膜沉积D. 清洗4.下列哪种材料是用于制作半导体器件的理想材料?A. 铜B. 锌C. 石墨D. 硅5、以下哪个半导体工艺技术能够实现更小的晶体管尺寸?A、传统CMOS工艺B、FinFET工艺C、GAAFET工艺D、平面晶体管工艺6、在半导体制造过程中,以下哪个步骤是为了提高硅片的纯度?A、扩散B、蚀刻C、清洗D、热处理7、半导体材料中最常用的材料是什么?()A. 硅(Si)B. 铜(Cu)C. 金(Au)D. 镁(Mg)8、在芯片制造过程中,光刻技术的主要作用是什么?()A. 去除不需要的材料B. 增加材料的功能性C. 将电路设计图案转移到硅片上D. 加热固化硅片结构9.在半导体制造工艺中,以下哪个步骤不属于典型的CMOS工艺流程?A. 氧化硅膜沉积B. 光刻C. 切割D. 离子注入 10.在半导体器件中,MOSFET(金属氧化物半导体场效应晶体管)的主要组成部分包括:A. 沟道区B. 源极C. 栅极D. 上述全部二、多项选择题(本大题有10小题,每小题4分,共40分)1、以下哪个物理现象通常用于提高晶体管开关速度?()A、短沟道效应B、量子隧道效应C、沟道极化D、多晶硅栅极2、在数字电路中,一种常见的数字缓冲器是 _ 。

()A、反馈触发器B、D触发器C、三态缓冲器D、差分放大器3.以下关于半导体材料的说法正确的是():A. SiC的禁带宽度比 Si 更宽B. GaN的发光效率比 Si 更高C. InGaAs 的电子迁移率比 Si 更快D. ZnSe可以用于制造红光 LED4.在半导体器件制造中,对于离子注入工艺,正确的工作原则包括():A. 离子注入可以形成三维空间中的杂质分布B. 注入离子可以改变晶格特性,增强材料强度C. 注入离子能量过高,可能导致晶体缺陷D. 离子注入温度应当尽可能高,以提高注入效率5.半导体芯片制造过程中,哪些步骤通常需要使用光刻技术?A. 芯片设计B. 光刻C. 薄膜沉积D. 金属化6.在半导体器件中,MOSFET(金属氧化物半导体场效应晶体管)的主要组成部分包括:A. 沟道区B. 源极C. 次沟道区D. 栅极7、在半导体的制造过程中,以下哪个工艺步骤不用于清洗晶圆?A. 刻蚀B. 化学机械抛光C. 清洁去毛刺D.湿法沉积8、在半导体制造过程中,以下哪种类型的晶圆对齐是用来确保图案精确地转移到光罩上的?A. 接触式对准B. 深亚微米对准C. 缩放对准D. 光学对准9.在半导体行业中,晶体管通常分为两种类型:双极型晶体管(BJTs)和场效应晶体管(FETs)。

微电子笔试(笔试和面试题)有答案

微电子笔试(笔试和面试题)有答案第一部分:基础篇(该部分共有试题8题,为必答题,每位应聘者按自己对问题的理解去回答,尽可能多回答你所知道的内容。

若不清楚就写不清楚)。

1、我们公司的产品是集成电路,请描述一下你对集成电路的认识,列举一些与集成电路相关的内容(如讲清楚模拟、数字、双极型、CMOS、MCU、RISC、CISC、DSP、ASIC、FPGA等的概念)。

数字集成电路是将元器件和连线集成于同一半导体芯片上而制成的数字逻辑电路或系统。

模拟信号,是指幅度随时间连续变化的信号。

例如,人对着话筒讲话,话筒输出的音频电信号就是模拟信号,收音机、收录机、音响设备及电视机中接收、放大的音频信号、电视信号,也是模拟信号。

数字信号,是指在时间上和幅度上离散取值的信号,例如,电报电码信号,按一下电键,产生一个电信号,而产生的电信号是不连续的。

这种不连续的电信号,一般叫做电脉冲或脉冲信号,计算机中运行的信号是脉冲信号,但这些脉冲信号均代表着确切的数字,因而又叫做数字信号。

在电子技术中,通常又把模拟信号以外的非连续变化的信号,统称为数字信号。

FPGA是英文Field-Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL、GAL、EPLD 等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

2、你认为你从事研发工作有哪些特点?3、基尔霍夫定理的内容是什么?基尔霍夫电流定律:流入一个节点的电流总和等于流出节点的电流总和。

基尔霍夫电压定律:环路电压的总和为零。

欧姆定律: 电阻两端的电压等于电阻阻值和流过电阻的电流的乘积。

4、描述你对集成电路设计流程的认识。

模拟集成电路设计的一般过程:1.电路设计依据电路功能完成电路的设计。

2.前仿真电路功能的仿真,包括功耗,电流,电压,温度,压摆幅,输入输出特性等参数的仿真。

杭州矽力杰笔试教案资料

杭州矽力杰笔试IC Design Engineer Test SheetAnalog DesignDevice Knowledge1. p+/n- junction and p-/n+ junction, which has a higher breakdown voltage? Why? For a p+/n- junction having N A and N D, what is the approximate function of junction capacitance (C j) vs. reverse biased voltage (V R)?2. Draw the cross-section of a CMOS inverter. Draw the parasitic structure on the cross-section. Describe ways to prevent “latch-up”?Circuit Analysis3. See the figure below.a. Draw the bode plot for this circuit.b. Estimate the systematic offset in this amplifier.c. Which is the positive input?4. See the figure below.a. What is this circuit?b. Which input is the positive input?c. How much current flows in P2?d. If I=10uA, what is a good selection for the value of R?e. What is the Common Mode Input Range for this circuit?f. What is the Common Mode Output Range for this circuit?g. Assume the only capacitance is from OUT to GND. Draw a Bode Plot.h. Assume no load. What is the maximum positive slew rate if C OUT=C? What is the maximum negative slew rate?5. See the figure below.Assume at time=0 inductor current is 0A. Draw inductor current, V X and V OUT vs. time.I6. See the figure below.a. What is this circuit?b. What is the desired ratio R2/R1?c. How many stable points does this circuit have?d. Assume R1 and R2 have no Temperature Coefficient. Draw a graph of I in R2 vs. Temperature.e. What is the minimum supply voltage necessary for this circuit to work properly?OUT7. See the figure below.a. Write the gain equation of each circuit.b. Assuming V O=0 at time 0. Sketch V O(t) for the given input signal.ABC8. Draw Buck Converter Circuit and key waveform, explain the basic operations at steady state.OtherMust Answer (Question 1-3)Question 1:Write the V/I relationship equations for resistor (R), capacitor (C), and inductor (L).Question 2:Given V B in Table 1, please calculate V C and V E. Assumptions: beta of NPN is infinity, P-N junction forward voltage drop is 0.7V.Question 3:假设图中理想放大器工作在深度负反馈状态,请计算下图输出端电压(V OUT)。

IC笔试题大全(部分含答案)

EE笔试/面试题目集合分类--IC设计基础1、我们公司的产品是集成电路,请描述一下你对集成电路的认识,列举一些与集成电路相关的内容(如讲清楚模拟、数字、双极型、CMOS、MCU、RISC、CISC、DSP、ASIC、FPGA等的概念)。

(仕兰微面试题目)2、FPGA和ASIC的概念,他们的区别。

(未知)答案:FPGA是可编程ASIC。

ASIC:专用集成电路,它是面向专门用途的电路,专门为一个用户设计和制造的。

根据一个用户的特定要求,能以低研制成本,短、交货周期供货的全定制,半定制集成电路。

与门阵列等其它ASIC(Application Specific IC)相比,它们又具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及可实时在线检验等优点模拟电路1、基尔霍夫定理的内容是什么?(仕兰微电子)2、平板电容公式(C=εS/4πkd)。

(未知)3、最基本的如三极管曲线特性。

(未知)4、描述反馈电路的概念,列举他们的应用。

(仕兰微电子)5、负反馈种类(电压并联反馈,电流串联反馈,电压串联反馈和电流并联反馈);负反馈馈的优点(降低放大器的增益灵敏度,改变输入电阻和输出电阻,改善放大器的线性和非线性失真,有效地扩展放大器的通频带,自动调节作用)(未知)6、放大电路的频率补偿的目的是什么,有哪些方法?(仕兰微电子)7、频率响应,如:怎么才算是稳定的,如何改变频响曲线的几个方法。

(未知)8、给出一个查分运放,如何相位补偿,并画补偿后的波特图。

(凹凸)9、基本放大电路种类(电压放大器,电流放大器,互导放大器和互阻放大器),优缺点,特别是广泛采用差分结构的原因。

(未知)10、给出一差分电路,告诉其输出电压Y+和Y-,求共模分量和差模分量。

(未知)11、画差放的两个输入管。

(凹凸)12、画出由运放构成加法、减法、微分、积分运算的电路原理图。

并画出一个晶体管级的运放电路。

(仕兰微电子)13、用运算放大器组成一个10倍的放大器。

半导体或芯片岗位招聘笔试题与参考答案(某大型国企)

招聘半导体或芯片岗位笔试题与参考答案(某大型国企)(答案在后面)一、单项选择题(本大题有10小题,每小题2分,共20分)1、以下哪个选项不属于半导体制造过程中的关键步骤?A、光刻B、蚀刻C、离子注入D、组装2、在半导体行业中,以下哪个术语用来描述晶体管中用于控制电流流动的导电区域?A、源极B、栅极C、漏极D、基区3、题干:以下关于半导体制造工艺的描述,正确的是:A、光刻工艺是将光刻胶图案转移到硅片上的过程。

B、蚀刻工艺是利用光刻胶保护硅片,通过化学或物理方法去除硅片表面不需要的层。

C、离子注入是将离子直接注入硅片表面,用于掺杂的过程。

D、扩散工艺是通过在硅片表面形成一层光刻胶,然后利用高温使杂质原子扩散到硅片中。

4、题干:在半导体制造过程中,以下哪种缺陷类型对芯片性能影响最为严重?A、表面缺陷B、体缺陷C、界面缺陷D、晶格缺陷5、在半导体制造过程中,以下哪种材料通常用于制造晶圆的基板?A. 石英玻璃B. 单晶硅C. 聚酰亚胺D. 氧化铝6、以下哪种技术用于在半导体器件中实现三维结构,从而提高器件的集成度和性能?A. 厚膜技术B. 硅片减薄技术C. 三维封装技术D. 双极型晶体管技术7、在半导体制造过程中,下列哪种缺陷类型是指由于光刻胶在曝光和显影过程中产生的缺陷?A. 逻辑缺陷B. 光刻缺陷C. 杂质缺陷D. 损伤缺陷8、下列哪种技术用于在硅片上形成纳米级结构的半导体器件?A. 溶胶-凝胶法B. 化学气相沉积法(CVD)C. 离子束刻蚀D. 电子束刻蚀9、以下哪项不属于半导体制造过程中的关键步骤?()A、光刻B、蚀刻C、离子注入D、焊接二、多项选择题(本大题有10小题,每小题4分,共40分)1、以下哪些是半导体制造过程中常见的工艺步骤?()A、光刻B、蚀刻C、离子注入D、化学气相沉积E、掺杂2、以下哪些是影响芯片性能的关键因素?()A、晶体管结构B、工艺节点C、材料选择D、功耗控制E、封装设计3、以下哪些技术是现代半导体制造中常用的光刻技术?A. 干法光刻B. 湿法光刻C. 电子束光刻D. 紫外光刻E. 激光直接成像4、下列关于半导体材料掺杂的描述,正确的是:A. N型半导体通过加入五价元素如磷(P)或砷(As)来制造B. P型半导体通过加入三价元素如硼(B)或铟(In)来制造C. 掺杂的目的是增加半导体的导电性D. 杂质原子在半导体中的浓度被称为掺杂浓度E. 掺杂过程会改变半导体的电学性质5、以下哪些技术属于半导体制造过程中常用的光刻技术?()A. 光刻胶技术B. 具有纳米级分辨率的电子束光刻C. 紫外光光刻D. 平板印刷技术E. 双光束干涉光刻6、以下哪些因素会影响半导体器件的可靠性?()A. 热稳定性B. 电压应力C. 材料纯度D. 封装设计E. 环境因素7、以下哪些是半导体制造过程中常见的缺陷类型?()A. 晶圆划痕B. 氧化层破裂C. 线路短路D. 热应力裂纹E. 杂质沾污8、在半导体器件的测试与表征中,以下哪些方法用于评估器件的电气特性?()A. 频域分析B. 温度特性测试C. 噪声分析D. 瞬态响应测试E. 微观结构分析9、以下哪些是半导体制造过程中常用的物理或化学方法?()A. 光刻B. 化学气相沉积(CVD)C. 离子注入D. 磨光E. 蚀刻三、判断题(本大题有10小题,每小题2分,共20分)1、半导体制造过程中,光刻是直接将电路图案转移到硅片上的关键步骤。

集成电路设计岗位招聘笔试题及解答(某世界500强集团)2024年

2024年招聘集成电路设计岗位笔试题及解答(某世界500强集团)(答案在后面)一、单项选择题(本大题有10小题,每小题2分,共20分)1、下列晶体管类型的半导体材料中,通常用于集成电路制造中的集电极,其来源最为广泛且成本较低的是?A. 氮化镓 (GaN)B. 硅 (Si)C. 锗 (Ge)D. 金刚石2、在集成电路设计行业中,总线宽度是指一次可以传输的信号数量。

下列总线的有效性排列中,哪一组是可以用在8位处理器的?A. 1位或4位总线B. 4位或8位总线C. 8位或16位总线D. 4位或16位总线3、下列哪种电路拓扑结构通常用于实现高增益放大器?A.மமமமமமமமமமB. 喜欢的肯定是什么?4、CMOS工艺中,为降低漏电流和提高开关速度,通常采用什么措施?A. 增加阈值电压B. 减少阈值电压C. 降低工作电压D. 提高工作电压5.在集成电路设计中,以下哪个因素对芯片的性能有最大影响?A. 电流大小B. 电压水平C. 晶体管尺寸D. 电阻值6.在设计集成电路时,以下哪种布局方法可以最小化信号传输延迟?A. 混合布局B. 紧凑布局C. 顺序布局D. 扇形布局7、数字选数字。

在模拟到数字转换电路中,使用最多的技术是()。

A、反相放大器B、运算放大器C、二极管放大器D、集成运放放大器8、数字选数字。

双极型晶体管在半导体工艺中,通常使用()掺杂技术。

A、P区掺杂B、N区掺杂C、平面掺杂D、表面掺杂9、设一款MMIC Amplifier电路的截止频率为10GHz,其放大倍数为20dB,则该放大器在1kHz处的增益 (以分贝为单位)A.约为20dBB.约为1.2dBC.约为0dBD.约为200dB 10、下列哪种晶体管的工作原理是基于电流的控制效果?A.MOSFETB.BJTTFETD.FinFET二、多项选择题(本大题有10小题,每小题4分,共40分)1.集成电路设计中,以下哪个因素对芯片性能影响最大?A. 电流大小B. 电压频率C. 电磁干扰D. 噪声大小2.在CMOS工艺中,以下哪种器件主要用于实现逻辑非功能?A. 二极管B. 晶体管C. 互连D. 电容3、集成电路设计中,每种不同类型的门电路都有其组成形式和特性方程,其中三态门(Out,tree)电路的特性方程,下述的英文表达准确的为:() A) Out = (A!) B) Out = ( *mc*ai) C) Out = ( ) is not the right choice D)Out = 0并且向上false4、某一电路的表达式为 Out = ( * ),( ) 表示废物符号,关于此电路的描述正确的是哪些?( ) A)只要有一个输入为1,则 Out=1,其 Low电平比单输出 t 高B)当 A,B,C 三个输入都为 0 时, Out=0 C)若 C=0,无论输入为0,1均不产生 anything D)三种输入相等时,三种条件下的结果一样5、下列关于 CMOS 集成电路的描述,哪些是正确的?( )A. CMOS 电路采用互补型 MOSFET 作为开关元件B. CMOS 电路在高速工作时功耗较低C. CMOS 电路主要用于模拟信号处理D. CMOS 电路在静态功耗方面较低6、下列关于设计流程中布局規劃的描述,哪些是正确的?( )A. 布局规划直接影响到芯片的性能B. 布局规划需要考虑每一级线路的容量C. 布局规划主要关心电路的功能实现D. 布局规划阶段可以随意修改电路结构7、在数字电路设计中,以下哪些电压类型是常见的逻辑门电压()。

半导体或芯片岗位招聘笔试题与参考答案

招聘半导体或芯片岗位笔试题与参考答案(答案在后面)一、单项选择题(本大题有10小题,每小题2分,共20分)1、半导体器件中,以下哪个材料是制作晶体管的最佳选择?A、硅(Si)B、锗(Ge)C、砷化镓(GaAs)D、碳化硅(SiC)2、在半导体工艺中,以下哪个步骤用于形成晶体管的有源区?A、光刻B、扩散C、蚀刻D、离子注入3、题干:在半导体制造过程中,下列哪种设备用于在硅片上形成绝缘层?A. 溶胶-凝胶法B. 气相沉积法C. 化学气相沉积法D. 离子注入法4、题干:下列哪种材料在制造芯片时用作硅片的基板?B. 蓝宝石C. 硅D. 玻璃5、题干:在半导体制造过程中,以下哪个步骤是用于形成晶体管的沟道区域?A. 源极/栅极/漏极扩散B. 化学气相沉积(CVD)C. 光刻D. 离子注入6、题干:以下哪个选项不是半导体器件性能退化的主要因素?A. 氧化B. 金属污染C. 温度D. 磁场7、以下哪种技术不属于半导体制造中的光刻技术?A. 具有曝光光源的接触式光刻B. 具有投影光源的接触式光刻C. 具有曝光光源的投影式光刻D. 具有投影光源的扫描式光刻8、在半导体制造过程中,以下哪种工艺是用来形成半导体器件中的掺杂层的?A. 离子注入B. 化学气相沉积D. 硅烷刻蚀9、在半导体制造过程中,下列哪一种工艺主要用于晶体管的掺杂?A. 离子注入B. 化学气相沉积C. 蚀刻D. 光刻 10、以下哪一项不是半导体芯片制造过程中的关键环节?A. 材料制备B. 设备测试C. 晶圆加工D. 封装测试二、多项选择题(本大题有10小题,每小题4分,共40分)1、以下哪些是半导体制造过程中的关键工艺步骤?()A. 光刻B. 沉积C. 刻蚀D. 化学气相沉积E. 离子注入2、以下哪些是影响芯片性能的关键因素?()A. 电路设计B. 材料选择C. 制造工艺D. 封装技术E. 电源电压3、以下哪些是半导体制造过程中的关键工艺步骤?A. 光刻B. 溅射C. 化学气相沉积D. 离子注入E. 硅片切割4、以下哪些是影响半导体器件性能的主要因素?A. 杂质浓度B. 静电放电C. 温度D. 电压E. 射线辐照5、以下哪些是半导体制造过程中常见的工艺步骤?A. 光刻B. 化学气相沉积(CVD)C. 离子注入D. 硅片切割E. 激光打标6、在芯片设计过程中,以下哪些工具或方法有助于提高设计效率?A. 逻辑综合B. 硅基模拟C. 动态仿真D. FPGA原型E. 硅验证7、以下哪些是半导体制造过程中常见的工艺步骤?()A. 光刻B. 刻蚀C. 化学气相沉积D. 离子注入E. 线宽控制8、以下哪些因素会影响芯片的性能?()A. 集成度B. 电压C. 温度D. 材料E. 制造工艺9、以下哪些是半导体制造过程中的关键工艺步骤?()A. 光刻B. 化学气相沉积C. 离子注入D. 晶圆切割E. 热处理 10、以下哪些是影响半导体器件性能的关键参数?()A. 集电极电压B. 跨导C. 开关速度D. 噪声电压E. 耗散功率三、判断题(本大题有10小题,每小题2分,共20分)1、半导体制造过程中,光刻是直接在硅片上形成电路图案的关键步骤。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Analog Design

Device Knowledge

1. p+/n- junction and p-/n+ junction, which has a higher breakdown voltage? Why? For

a p+/n- junction having N

A and N

D

, what is the approximate function of junction

capacitance (C

j ) vs. reverse biased voltage (V

R

)?

2. Draw the cross-section of a CMOS inverter. Draw the parasitic structure on the cross-section. Describe ways to prevent “latch-up”?

Circuit Analysis

3. See the figure below.

a. Draw the bode plot for this circuit.

b. Estimate the systematic offset in this amplifier.

c. Which is the positive input?

4. See the figure below.

a. What is this circuit?

b. Which input is the positive input?

c. How much current flows in P

?

2

d. If I=10uA, what is a good selection for the value of R?

e. What is the Common Mode Input Range for this circuit?

f. What is the Common Mode Output Range for this circuit?

g. Assume the only capacitance is from OUT to GND. Draw a Bode Plot.

=C? What is the

h. Assume no load. What is the maximum positive slew rate if C

OUT

maximum negative slew rate?

5. See the figure below.

Assume at time=0 inductor current is 0A. Draw inductor current, V

X and V

OUT

vs. time.

I

6. See the figure below.

a. What is this circuit?

b. What is the desired ratio R

2/R

1

?

c. How many stable points does this circuit have?

d. Assume R

1 and R

2

have no Temperature Coefficient. Draw a graph of I in R

2

vs.

Temperature.

e. What is the minimum supply voltage necessary for this circuit to work properly?

OUT

7. See the figure below.

a. Write the gain equation of each circuit.

b. Assuming V O =0 at time 0. Sketch V O (t) for the given input signal.

A

B

C

8. Draw Buck Converter Circuit and key waveform, explain the basic operations at steady state.

Other

Must Answer (Question 1-3)

Question 1:

Write the V/I relationship equations for resistor (R), capacitor (C), and inductor (L).

Question 2:

Given V

B in Table 1, please calculate V

C

and V

E

. Assumptions: beta of NPN is infinity,

P-N junction forward voltage drop is .

Question 3:

假设图中理想放大器工作在深度负反馈状态,请计算下图输出端电压(V

)。

OUT

For Test Engineer (Question 4-5)

Question 4:

用C语言写一个递归算法求N!

Question 5:

C语言题目

a. 在编译环境下,下列类型变量需要占几个字节内存:

int

float

double

long

char

unsigned char

b. 以下程序的输出结果:

#define ADD(x) (x)+(x)

main()

{

int a=4, b=6, c=7, d=ADD(a+b)*c;

printf(“d=%d\n”,d);

}

c. 设int a=7,b=9,t;执行完表达式t=(a>b)?a:b;后,t的值是?

d. 设计一个排序函数,并同时获得最大值,最小值,均方根。

函数名、排序数列等自行定义。

For AE Engineer (Question 6-8)

Question 6:

a. What is this circuit shown in the Figure?

C1

b. Please draw the waveforms for V

2

for three cases (use the same scale):

C 1=open, R

3

=1k;

R 3=open, C

1

=1uF;

R 3=1k, C

1

=1uF.

0V

0V Question 7:

Draw bode plots of V

O /V

I

(gain and phase) for the circuit shown below. Please label

the proper pole/zero location.

V I

O

Case 1: R3=open

Case 2: R3=1K

Question 8:

Figure below shows a simple buck converter. The switching frequency of the converter is 1MHz.

L 1

I OUT

a. V IN =10V, V OUT =4V, I OUT =5A, what is the ON time of Q 2?

b. Draw waveforms of V SW and I L1 below (under the same time scale of V G -V SW ). Assumption: I OUT =5A.

For Layout Engineer (Question 9-12)

Question 9: 简述CMOS 工艺流程。

Question 10:

Draw the layout of a two-input NAND gate.

Z

A

B

Question 11:

下面电路图中有两个MOSFET(M

A and M

B

)。

假设每个MOSFET有两个gate figure,右下版图应

该如何连接,才能使M

A

和M

B

匹配。

Question 12:

画出不同的电流镜图,并简述各自特点。