锁相环及载波同步

同步原理(载波同步与位同步)

载波同步的基本原理,实现方法和性能指标

实际中,伴随信号一起进入接收机的还有加性高斯白噪声,为了改善平方变换法的性能,使恢复的相干载波更为纯净,常用锁相环代替窄带滤波器。如下图: 平方环法提取载波框图 锁相环具有良好的跟踪,窄带滤波和记忆功能。

等价于:中心频率可调的窄带滤波器

载波同步的基本原理,实现方法和性能指标

载波同步:是指在相干解调时,接收端需要提供一个与接收信号中的调制载波同频同相的相干载波。 载波同步是实现相干解调的先决条件。 提取相干载波的方法:直接法(自同步法)

插入导频法

载波同步的基本原理,实现方法和性能指标

载波同步的基本原理,实现方法和性能指标

直接法:有些信号(DSB-SC,PSK),虽然本身不含有载波分量,但经过某种非线性变化后,将具有载波的谐波分量,因此可以从中提取。下面介绍几种常用的方法:

载波同步的基本原理,实现方法和性能指标

一:在抑制载波的双边带信号中插入导频法 导频的插入方法: 在抑制载波双边带信号的已调信号的载频出插入一个与该信号频谱正交的载波信号。 插入导频系统的发端框图: 输出信号为:

载波同步的基本原理,实现方法和性能指标

1

插入导频系统的接收端框图:

平方变换法和平方环法 设调制信号 ,则抑制载波的双边带信号为: 平方变换法提取载波框图: 窄带滤波器输出为:

载波同步的基本原理,实现方法和性能指标

二分频器输出,可得载波信号: 注意:载波提取的方框图中用了一个二分频电路,由于分频起点的不确定性,使输出的载波相对于接收信号的相位有180度的相位模糊。 相位模糊对模拟通信关系不大(人耳听不出相位变化) 对数字通信影响很大,有可能使2PSK相干解调后出 现“反向工作”的问题。 解决办法:对调制器输入的信息序列进行差分编码。(2DPSK)

同步技术

同步技术一、同步技术的定义:同步技术即调整通信网中的各种信号使之协同工作的技术。

诸信号协同工作是通信网正常传输信息的基础。

二、同步技术的分类:按照同步的功能来分,同步可以分为载波同步、位同步(码元同步)、群同步(帧同步)和网同步(通信网中用)等四种。

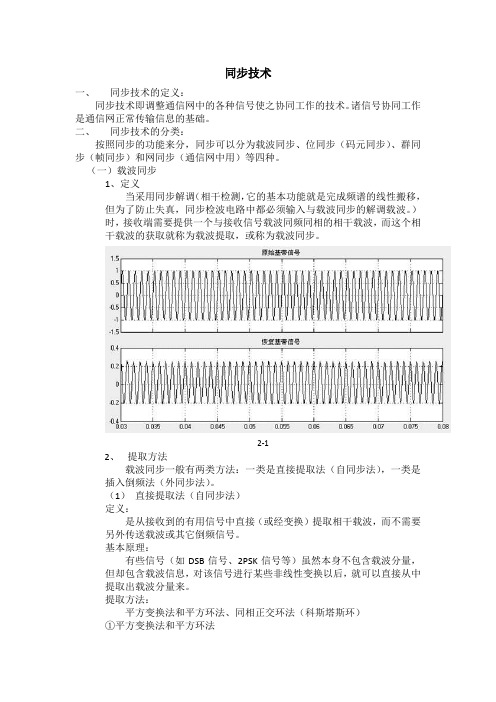

(一)载波同步1、定义当采用同步解调(相干检测,它的基本功能就是完成频谱的线性搬移,但为了防止失真,同步检波电路中都必须输入与载波同步的解调载波。

)时,接收端需要提供一个与接收信号载波同频同相的相干载波,而这个相干载波的获取就称为载波提取,或称为载波同步。

2-12、提取方法载波同步一般有两类方法:一类是直接提取法(自同步法),一类是插入倒频法(外同步法)。

(1)直接提取法(自同步法)定义:是从接收到的有用信号中直接(或经变换)提取相干载波,而不需要另外传送载波或其它倒频信号。

基本原理:有些信号(如DSB信号、2PSK信号等)虽然本身不包含载波分量,但却包含载波信息,对该信号进行某些非线性变换以后,就可以直接从中提取出载波分量来。

提取方法:平方变换法和平方环法、同相正交环法(科斯塔斯环)①平方变换法和平方环法图2-2平方变换法提取载波图2-2即为平方变换法提取载波,为了改善性能,可以在平方变换法大的基础上,把窄带滤波器用锁相环替代,构成如图2-3所示的方框图,这就是平方环法提取载波。

图2-3平方环法提取载波由于锁相环具有良好的跟踪、窄带滤波性能,因此平方环法比一般的平方变换法具有更好的性能,因而得到广泛的应用。

②同相正交环法(科斯塔斯环)图2-4同相正交环法提取载波同相正交环法(科斯塔斯环)是利用锁相环提取载波的另一种常用方法,由于加到上下两个相乘器的本地信号分别为压控振荡器的输出信号和它的正交信号,因此常称这种环路为同相正交环,有时也被称为科斯塔斯环(Costas)环。

如图2-4所示。

(2)插入倒频法(外同步法)定义:是在发端发送信息码元的同时,再发送一个(或多个)包含载波信息的倒频信号,并且要求这个倒频信号不随传播的信息变换,在接收端根据倒频信号提取载波。

第4章 锁相与同步

网同步

整个数字通信网内有一个统一的时间节拍标准

2013-7-24 2

4.2 锁相环

锁相环具有:

跟踪特性 窄带滤波特性 记忆特性

可用来提取载波和位定时信号 有模拟和数字锁相环之分。

2013-7-24

3

1 锁相环路的组成和工作原理

锁相环路是一种关于时间的伺服系统,它是最重要的一种同步技术。

s(t)

/2 VCO v2 环路滤波 vd

v4

低通滤波

Costas 环的原理框图

v6

输入信号:

正交本地 载频信号: 2013-7-24

s t Acm t cos 2 fct

ˆ v1 t cos 2 fct ,

ˆ v2 t sin 2 fct

ˆ (t ) K v(t )dt

t

+ -

ˆ

1 ˆ sin( ) 2

vd

G ( s)

ˆ

K /s

锁相环的等效闭环系统方框图

2013-7-24

6

鉴相特性为:

ˆ Vd Kd sin( ) Kd sin

从鉴相特性可见当相位误差 0 时,产生正的误差电压 vd 去控制

ˆ VCO,使 得增加,从而减小相位误差。当 0 时,产生负的误

平衡点是

2013-7-24

ˆ 差电压 vd 去控制VCO,使 减小,从而使相位误差向正的方向增大。

0 ,这是一个稳定的平衡点。

7

当环路工作在跟踪模式时,这时相位误差很小,可以采用近似

ˆ ˆ sin( )

t s 越短越好

同步保持时间

锁相环的基本原理锁相环基本原理及其应用

锁相环的基本原理锁相环基本原理及其应用锁相环的基本原理锁相环基本原理及其应用锁相环及其应用所谓锁相环路,实际是指自动相位控制电路(APC),它是利用两个电信号的相位误差,通过环路自身调整作用,实现频率准确跟踪的系统,称该系统为锁相环路,简称环路,通常用PLL表示。

锁相环路是由鉴相器(简称PD)、环路滤波器(简称LPF或LF)和压控振荡器(简称VCO)三个部件组成闭合系统。

这是一个基本环路,其各种形式均由它变化而来PLL概念设环路输入信号v= Viomimsin(ωit+φi)环路输出信号v= Vosin(ωot+φo)——其中ωo=ωr+△ωo通过相位反馈控制,最终使相位保持同步,实现了受控频率准确跟踪基准信号频率的自动控制系统称为锁相环路。

PLL构成由鉴相器(PD)环路滤波器(LPF)压控振荡器(VCO)组成的环路。

PLL原理从捕捉过程→锁定A.捕捉过程(是失锁的)a. b.φi┈φi均是随时间变化的,经相位比较产生误差相位φe=φi-φo,也是变化的。

φe(t)由鉴相器产生误差电压v(t)=f(φde)完成相位误差—电压的变换作用。

v(t)为交流电压。

dc.v(t)经环路滤波,滤除高频分量和干扰噪声得到纯净控制电压,由VCO产生d控制角频差△ω0,使ω0随ωi变化。

B.锁定(即相位稳定)a. b.一旦锁定φe(t)=φe∞(很小常数)v(t)= V(直流电压)ddω0≡ωi输出频率恒等于输入频率(无角频差,同时控制角频差为最大△ω0max, 即ω0=ωr+△ω0max。

ωr为VCO固有振荡角频率。

)锁相基本组成和基本方程(时域)各基本组成部件鉴相器(PD)数学模式v(t)=AsinφdDe(t)相位模式环路滤波器(LPF) 数学模式v(t)=A(P) v(t)cFd相位模式压控振荡器(VCO)数学模式相位模式环路模型相位模式:指锁相环(PLL)输入相位和输出相位的反馈调节关系。

相位模型:把鉴相器,环路滤波器和压控振荡器三个部件的相位模型依次级联起来就构成锁相相位模型。

实验5 数字锁相环与位同步

一、 实验目的

1. 掌握数字锁相环工作原理。 2. 掌握用数字环提取位同步信号的原理及对信息代码的要求。 3. 掌握位同步器的同步建立时间、同步保持时间、位同步信 号同步抖动等概念。

二、

实验内容

1. 观察数字环的失锁状态、锁定状态。 2. 观察数字环锁定状态下位同步信号的相位抖动现象 及相位抖动大小与固有频差、信息代码的关系。 3. 观察数字环位同步器的同步保持时间与固有频差之 间的关系。

四、Βιβλιοθήκη 实验步骤本实验使用数字信源单元和位同步单元。 1、熟悉位同步单元工作原理。将数字信源单元的NRZ-OUT用信 号连线连接到位同步单元的S-IN点,接通实验箱电源。调整信源 模块的K1、K2、K3开关,使NRZ-OUT的连“0”和连“1”个数较少。 2、观察数字环的锁定状态和失锁状态。 将示波器的两个探头分别接数字信源单元的NRZ-OUT和位同步单 元的BS-OUT,调节位同步单元上的可变电容C2,观察数字环的锁 定状态和失锁状态。锁定时BS-OUT信号上升沿位于NRZ-OUT信号 的码元中间且在很小范围内抖动;失锁时,BS-OUT的相位抖动很 大,可能超出一个码元宽度范围,变得模糊混乱。

五、

实验报告要求

数字环位同步器输入NRZ码连“1”或连“0”个数增加时, 提取的位同步信号相位抖动增大,试解释此现象。

据通信双方的计算机在时钟频率上存在差异,而这种 差异将导致不同的计算机的时钟周期的微小误差。尽管这 种差异是微小的,但在大量的数据传输过程中,这种微小 误差的积累足以造成传输的错误。因此,在数据通信中, 首先要解决的是收发双方计算机的时钟频率的一致性问题。 一般方法是,要求接收端根据发送端发送数据的起止时间 和时钟频率,来校正自己的时间基准和时钟频率,这个过 程叫位同步。可见,位同步的目的是使接收端接收的每一 位信息都与发送端保持同步。目前实现位同步的方法主要 有外同步法和自同步法两种: 1、外同步法。外同步的方法是,发送端发送数据之前 先发送同步时钟信号,接收方用这一同步信号来锁定自己 的时钟脉冲频率,以此来达到收发双方位同步的目的; 2、自同步法。接收方利用包含有同步信号的特殊编码 (如曼彻斯特编码)从信号自身提取同步信号来锁定自己 的时钟脉冲频率,达到同步目的。

锁相环工作原理

锁相环工作原理锁相环路是一种反馈电路,锁相环的英文全称是Phase-Locked Loop,简称PLL。

其作用是使得电路上的时钟和某一外部时钟的相位同步。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

在数据采集系统中,锁相环是一种非常有用的同步技术,因为通过锁相环,可以使得不同的数据采集板卡共享同一个采样时钟。

因此,所有板卡上各自的本地80MHz和20MHz时基的相位都是同步的,从而采样时钟也是同步的。

因为每块板卡的采样时钟都是同步的,所以都能严格地在同一时刻进行数据采集。

锁相环路是一个相位反馈自动控制系统。

它由以下三个基本部件组成:鉴相器(PD)、环路滤波器(LPF)和压控振荡器(VCO)。

锁相环的工作原理:1. 压控振荡器的输出经过采集并分频;2. 和基准信号同时输入鉴相器;3. 鉴相器通过比较上述两个信号的频率差,然后输出一个直流脉冲电压;4. 控制VCO,使它的频率改变;5. 这样经过一个很短的时间,VCO 的输出就会稳定于某一期望值。

锁相环可用来实现输出和输入两个信号之间的相位同步。

当没有基准(参考)输入信号时,环路滤波器的输出为零(或为某一固定值)。

这时,压控振荡器按其固有频率fv进行自由振荡。

当有频率为fR的参考信号输入时,uR 和uv同时加到鉴相器进行鉴相。

如果fR和fv相差不大,鉴相器对uR和uv进行鉴相的结果,输出一个与uR和uv的相位差成正比的误差电压ud,再经过环路滤波器滤去ud中的高频成分,输出一个控制电压uc,uc将使压控振荡器的频率fv(和相位)发生变化,朝着参考输入信号的频率靠拢,最后使fv= fR,环路锁定。

环路一旦进入锁定状态后,压控振荡器的输出信号与环路的输入信号(参考信号)之间只有一个固定的稳态相位差,而没有频差存在。

实验八 基于通信原理的数字锁相环与位同步

实验八数字锁相环与位同步一、实验目的掌握数字锁相环工作原理以及触发式数字锁相环的快速捕获原理。

掌握用数字环提取位同步信号的原理及对信息代码的要求。

掌握位同步器的同步建立时间、同步保持时间、位同步信号同步抖动等概念。

二、实验原理可用窄带带通滤波器,锁相环来提取位同步信号。

实验一中用模数混合锁相环(电荷泵锁相环)提取位同步信号,它要求输入信号是一个准周期数字信号。

实验三中的模拟环也可以提取位同步信号,它要求输入准周期正弦信号。

本实验使用数字锁相环提取位同步信号,它不要求输入信号一定是周期信号或准周期信号,其工作频率低于模数环和模拟环。

用于提取位同步信号的数字环有超前滞后型数字环和触发器型数字环,此实验系统中的位同步提取模块用的是触发器型数字环,它具有捕捉时间短、抗噪能力强等特点。

位同步模块原理框图如图8-1所示。

其内部仅使用+5V电压。

图8-1 位同步器方框图位同步模块有以下测试点及输入输出点:∙ S-IN 基带信号输入点/测试点(2个)∙ BS-OUT 位同步信号输出点/测试点(3个)图8-1中各单元与电路板上元器件的对应关系如下:∙晶振CRY3:晶体;U39:7404∙控制器U48:或门7432;U41:计数器74190∙鉴相器U40:D触发器7474∙量化器U45:可编程计数器8254∙数字环路滤波器由软件完成∙数控振荡U46、U45:8254∙脉冲展宽器U47:单稳态触发器74123位同步器由控制器、数字锁相环及脉冲展宽器组成,数字锁相环包括数字鉴相器、量化器、数字环路滤波器、数控振荡器等单元。

下面介绍位同步器的工作原理。

数字锁相环是一个单片机系统,主要器件是单片机89C51及可编程计数器8254。

环路中使用了两片8254,共六个计数器,分别表示为8254A 0、8254A 1、8254A 2、8254B 0、8254B 1、8254B 2。

它们分别工作在M 0、M 1、M 2三种工作模式。

实验三:模拟锁相环与载波同步.

实验三:模拟锁相环与载波同步一、实验目的1.模拟锁相环工作原理以及环路锁定状态、失锁状态、同步带、捕捉带等基本概念。

2.掌握用平方法从2DPSK信号中提取相干载波的原理及模拟锁相环的设计方法。

3.了解相干载波相位模糊现象产生的原因。

二、实验内容1. 观察模拟锁相环的锁定状态、失锁状态及捕捉过程。

2. 观察环路的捕捉带和同步带。

3. 用平方环法从2DPSK信号中提取载波同步信号,观察相位模糊现象。

三、实验步骤本实验使用数字信源单元、数字调制单元和载波同步单元。

1.熟悉载波同步单元的工作原理。

接好电源线,打开实验箱电源开关。

2.检查要用到的数字信源单元和数字调制单元是否工作正常(用示波器观察信源NRZ-OUT(AK)和调制2DPSK信号有无,两者逻辑关系正确与否)。

3. 用示波器观察载波同步模块锁相环的锁定状态、失锁状态,测量环路的同步带、捕捉带。

环路锁定时ud为直流、环路输入信号频率等于反馈信号频率(此锁相环中即等于VCO信号频率)。

环路失锁时ud为差拍电压,环路输入信号频率与反馈信号频率不相等。

本环路输入信号频率等于2DPSK载频的两倍,即等于调制单元CAR信号频率的两倍。

环路锁定时VCO信号频率等于CAR-OUT信号频率的两倍。

所以环路锁定时调制单元的CAR和载波同步单元的CAR-OUT频率完全相等。

根据上述特点可判断环路的工作状态,具体实验步骤如下:(1)观察锁定状态与失锁状态打开电源后用示波器观察ud ,若ud为直流,则调节载波同步模块上的可变电容C34,ud随C34减小而减小,随C34增大而增大(为什么?请思考),这说明环路处于锁定状态。

用示波器同时观察调制单元的CAR和载波同步单元的CAR-OUT,可以看到两个信号频率相等。

若有频率计则可分别测量CAR和CAR-OUT频率。

在锁定状态下,向某一方向变化C34,可使ud由直流变为交流,CAR和CAR-OUT频率不再相等,环路由锁定状态变为失锁。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

fc

f2

f1 fC f m f1 f 2 fC f r f 2

VSB 插入导频的方案之一

接收端:

目标:利用f1、 f2的和、差、 倍关系得到fc

f 1 fC f m f 1 f 2 fC f r f 2

接收信号

f1窄带滤 波/PLL

f2窄带滤 波/PLL

– 条件1:低通滤波器LF的带宽大于信号带宽 KP 截止角频率为Kp的 VP ( s ) K FM M ( s ) s KP 低通滤波器 – 条件2: K P / 2 B B为信号带宽

VP ( s ) K FM M ( s )

锁相环在通信系统中的应用

• 锁相环在通信系统中有很多应用,包括:高稳定FM 信号产生、FM鉴频、调幅信号的相干解调、倍频、 频率合成以及数字系统中的比特同步等等 • NFM信号的相干解调

vi(t)

鉴相器 PD

vD(t)

压控振荡 器VCO

环路低通 滤波器LF

vP(t)

vo(t)

PLL的主要性能指标, 主要取决于环路滤波 器的设计

压控振荡器

• 压控振荡器

自由振荡频率或 中心(角)频率 电压控制部分

(t ) 0 gv P (t )

(t)

(t ) 0 KV v P (t )

锁相环PLL由鉴相器、环路(低通滤波器)和 压控振荡器三个基本部件组成相位反馈控制系统 锁定、跟踪(同步带)、捕捉

锁相环基本原理

锁定、失锁、跟踪(同步带)、捕捉

v P (t )

f0

同步带 捕捉带

f

鉴相器

鉴相器完成输入信 号与压控振荡器之间 相位差到电压的转换

vo(t) -

e(t)

vi(t) vo(t)

载波同步---插入导频法

抑制载波的双边带信号(如 DSB 、等概的 2PSK ) 本身不含有载波, 残留边带( VSB )信号虽含有载 波分量,但很难从已调信号的频谱中把它分离出来。 对这些信号的载波提取, 可以用插入导频法(外同 步法)。尤其是单边带(SSB)信号, 它既没有载波 分量又不能用直接法提取载波,只能用插入导频法 所谓插入导频,就是在已调信号频谱中额外插入一 (多)个低功率的线谱,以便接收端作为载波同步信 号加以恢复,此线谱对应的正弦波称为导频信号

H ( s) 1

e ( s )( t ) o s0 ) i( ) s t(

i ( ss ) / s

i ( s) s s K P H ( s) e ( s) i ( s) ( t) t t 0 s KP i ( s ) / s 2 s e ( s ) lims i ( s) s 0 s K P

DSB 插入导频的方案讨论

讨论:

– 能否在插入同相导频 相干解调后 有直流分量

f 0 fC-fm fC fC+fm

DSB信号的导频插入

– 能否在带外插入导频

– SSB怎么插入导频

f 0 fC-fm fC fC+fm

DSB信号的导频插入

பைடு நூலகம்

VSB 插入导频的方案之一

发送端:

H(f)

f

1

fr

f

2

f1 fc-fm

i(s) o(s)

KP

H(S)

1/S

锁相环应用分析例

• 分析锁相环成为FM鉴频器的条件

VP ( s ) s o ( s ) sT ( s ) i ( s ) K P H ( s) K FM M ( s ) s K P H ( s)

i(s) o(s)

KP

H(S)

1/S

发送端:

m(t) 相乘 调制 带通 滤波

/ 2

相 输出 加 s(t)

f 0 fC-fm fC fC+fm

aC cos C t

~

DSBÐ Å º Å µ Ä µ ¼ Æ µ ² å È ë

s(t ) ac m(t ) cosc t ac sinc t

已调信号 插入导频

DSB 插入导频的方案之一

i(s) o(s)

KP

H(S)

1/S

锁相环的复频域模型

两种锁相环分析示例

( s) K P H ( s) T ( s) o i ( s) s K P H ( s)

e ( s) i ( s) o ( s)

s s K P H ( s)

i ( s)

vP(t)

0 (t ) 0 t KV v P ( )d 0 ( t ) KV v P ( )d

锁相环的环路方程

i (t ) o (t ) v D K D sin

i (t )

vi(t) vD(t)

VCO

v P (t ) v D (t ) h(t )

s o ( s ) K P o ( s ) i ( s )H ( s ) T ( s)

o ( s) K P H ( s) i ( s) s K P H ( s)

K P KV K D

不同的环路滤波器,可以求 出相位不同的传输函数,进 行分析,得到稳态相差、稳 定度等指标

接收端:

r(t)

带通 滤波

fc窄带滤 波/PLL

相乘 v(t) 低通 m(t) 器 滤波

/ 2

相干载波恢 复

v ( t ) r ( t ) cos c t s( t ) cos c t ac m( t ) cos2 c t ac cos c t si n c t ac ac ac m( t ) cos 2 c t si n2 c t 2 2 2

e ( s) 0

e ( s ) KP

只有相差 有频率差

两种锁相环分析示例

K H ( s) s K

e ( s)

s s K P H ( s)

s 0

( t) t 0 i ( s ) / s

i ( s)

( t) t

f2-f1

低通

fc窄带 /PLL

载波 输出

移相

1

q次 分频

3

4

2

VSB 插入导频的方案之一

f 1 fC f m f 1

接收端:

1

f 2 fC f r f 2

– f1、f2相乘滤波取差频 cos(2f1t 1 ) cos(2f 2 t 2 )

1 cos2 ( f r f 2 f m f 1 )t 2 1 2 f f 1 1 cos 2 ( f r f 2 )(1 m )t 2 1 2 f r f 2

鉴相器 PD

vD(t) vD(t)

vo(t) -

e(t)

v D f i (t ) 0 (t )

i ( t ) o ( t ) K D si n2 0 t i ( t ) o ( t ) K D si n

环路低通滤波器

• 环路滤波器的主要功能: – 滤除误差信号中的高频分量 – 为锁相环提供一个短时记忆,如果系统由于瞬时 噪声而失锁,可确保锁相环路迅速重新捕获信号。 • 环路滤波器的设计对环路的各项性能都有重要影响 – 稳态相差、跟踪时间、捕捉带宽、稳定性等。

t0

e ( s) lims

s

s K P H ( s)

i ( s)

i ( s ) / s 2

e ( s) 0 e ( s) 0

只有相差 有频率差

锁相环应用分析例

• 分析锁相环成为FM鉴频器的条件

v i ( t ) A cos c t K FM

插入的导频:位置、强度、 与传输信号关系?

载波同步---插入导频法

导频与信号 同时(频带)传输 互不干扰

导频插入 在任意位置 (一般在 通带内)

导频插在信号谱 的零点或与信号 正交传输,以保 证不干扰信号

导频线谱的强度 远大于信号谱, 以便于接收端滤波 或锁相跟踪

在信号频 带外,单 独传输?

DSB 插入导频的方案之一

m ( )d

vi(t)

i ( t ) K FM m ( )d i ( s ) K FM

1 M ( s) s

vD(t)

VCO

H(f) LF

vP(t) vo(t)

VP ( s ) s o ( s ) sT ( s ) i ( s ) K P H ( s) K FM M ( s ) s K P H ( s)

已调信号含 有同步信息

信道

载波恢复

相干解调

AM

载波同步

已调信号

插入 载波/导频

信道

载波恢复

相干解调

同步本身虽然不包含所要传送的信息,但只有 收发设备之间建立了同步后才能开始传送信息, 所以同步是进行信息传输的必要和前提。同步性 能的好坏又将直接影响着通信系统的性能。如果 出现同步误差或失去同步就会导致通信系统性能 下降或通信中断。因此,同步系统应具有比信息 传输系统更高的可靠性和更好的质量指标,如同 步误差小、相位抖动小以及同步建立时间短,保 持时间长等。

R

1 Cs

1 Cs 1 RC s 1 RC

H ( s) 1

1 H ( s ) Cs K s K

R

两种锁相环分析示例

(t) t 0 i ( s ) / s (t) t t 0 i ( s ) / s

2

只有相差

有频率差

两种锁相环分析示例