SO、SOP、SOIC封装详解(关于宽体、中体、窄体)

什么是SOT和SOD封装

什么是SOT和SOD封装上次说到了SOP的封装,唯独没有说SOT和SOD封装,其实SOT和SOD作为晶体管封装,小编单拉出来以便大家更好的理解。

什么是SOT和SOD封装?SOT的英文全名是:Small Outline Transistor(小外形晶体管),SOT是一种表面贴装的封装形式,一般引脚小于等于5个的小外形晶体管。

根据表面宽度的不同分为两种,一种宽度为1.3mm,一种宽度为1.6mm。

SOD的英文全名是:Small Outline Diode(小外形二级管),SOD 后面常会是跟一串数字,表示封装的标准序号,如:SOD-23,SOD-523,SOD323等等。

其实SOD指贴片二极管的封装,而SOT是一般指贴片三极管的封装。

常见SOT封装:常见SOD封装上篇讲到上世纪七十年代的DIP封装,而到八十年代初,SMT(Surface Mount Technology表面贴片技术)开始流行,封装的管脚上开始变化,从DIP直插方式慢慢衍生出SOP封装形式。

什么是SOP封装?SOP的英文全名:Small Outlinepackage(小外形封装),引脚从的两个较长的边引出,引脚的末端向外伸展呈鸥翼形的一种表面贴装型的封装。

SOP的命名规则SOP的封装命名与DIP的一样,其后面的数字表示着该封装的引脚数,如SOP8,8表示引脚数(两侧引脚各4个)。

SOP的常见类型SOP的“另类”封装1、SOJ封装SOJ的英文全名:Small Outline J-Lead (小尺寸J 形引脚封装),引脚从封装两侧引出向下呈J 字形。

主要应用于储存器。

2、SOIC封装SOIC的英文全名: Small Outline Integrated Circuit(小外型芯片),从字面上理解SOIC=SOP,但小编看各大厂资料发现其尺寸有宽体(wide)和窄体(narrow)之分,以TI的SN74hc595为例。

在其pdf资料中显示SOIC16的封装尺寸有宽和窄体两种。

封装标准介绍(简化版)

芯片的封装技术已经历了好几代的变迁,从DIP、QFP、PGA、BGA到CSP再到MCM,技术指标一代比一代先进,包括芯片面积与封装面积之比越来越接近于1,适用频率越来越高,耐温性能越来越好,引脚数增多,引脚间距减小,重量减小,可靠性提高,使用更加方便等等。

下面将对具体的封装形式作详细说明。

封装形式塑封体尺寸mm*mm*mm引线间距mm/mil跨度mm/milDIP8L9.25*6.35*3.32.54/1007.62/300DIP14L19.1*6.35*3.32.54/1007.62/300DIP16L19.1*6.35*3.32.54/1007.62/300DIP18L22.9*6.5*3.32.54/1007.62/300DIP20L26.23*6.55*3.32.54/1007.62/300DIP24L31.76*13.8*3.852.54/10015.24/600DIP28L37.05*13.8*3.8515.24/600DIP40L52.25*13.8*3.85 2.54/10015.24/600DIP42L52.25*13.8*3.85 2.54/10015.24/600HDIP12L19.1*6.35*3.3 2.54/1007.62/300SDIP24L22.9*6.55*3.3 1.778/707.62/300SDIP28L25.6*8.8*3.3 1.778/7010.16/400SIP8L19.2*6.5*2.8 2.54/100___SIP9L22.3*5.6*3.2 2.54/100___SIP10L24.2*6.7*3.25 2.54/100___HSIP12L2.54/100___ZIP16L24.2*6.7*3.25 1.50/59___SOP8L4.9*3.9*1.38 1.27/505.72/225SOP14L8.65*3.9*1.38 1.27/505.72/225SOP16L9.9*3.9*1.38 1.27/505.72/225SOP16L(W) 10.3*7.5*2.3 1.27/509.53/375SOP20L12.8*7.5*2.3 1.27/509.53/375SOP24L15.4*7.5*2.3 1.27/509.53/375SOP28L18.09*7.5*2.3 1.27/509.53/37519*7.6*2.3 1.27/509.53/375HSOP28L 18.9*7.5*2.3 0.8/31.59.53/375SSOP10L(1) 4.9*3.9*1.38 1/39.33.9/153.5SSOP16L6.2*5.3*1.5 0.62/25.65.3/209SSOP20L7.2*5.3*1.5 0.62/25.65.3/209SSOP24L8.2*5.3*1.5 0.62/25.65.3/209SSOP24L(1) 13*6*1.81/39.36/236SSOP28L 10.2*5.3*1.75 0.62/25.65.3/209TSOP44L 18.44*10.16*1 0.8/31.510.16/400TSOP54L22.2*10.16*10.8/31.510.16/400QFP44L10*10*2.10.8/31.5_____LQFP64L14*14*1.40.8/31.5_____TO251(5L)6.5*5.5*2.31.27/50_____TO252(5L)6.5*5.5*2.31.27/50_____SOT89(3L)4.5*2.5*1.51.5/59_____SOT223(3L)6.5*3.5*1.652.3/91_____一、DIP PGA封装DIP,引脚少于等于24,一般主体宽度为300mil(窄体).多于24脚,多为600mil(宽体)。

芯片常见封装缩写解释

常见封装缩写解释bldh888 发表于: 2010-4-23 22:04 来源: 半导体技术天地1. DIP(dual in-line PACkage)双列直插式封装。

插装型封装之一,引脚从封装两侧引出,封装材料有塑料和陶瓷两种。

DIP 是最普及的插装型封装,应用范围包括标准逻辑IC,存贮器LSI,微机电路等。

引脚中心距2.54mm,引脚数从6 到64。

封装宽度通常为15.2mm。

有的把宽度为7.52mm和10.16mm 的封装分别称为skinny DIP 和slim DIP(窄体型DIP)。

但多数情况下并不加区分,只简单地统称为DIP。

另外,用低熔点玻璃密封的陶瓷DIP 也称为Cerdip(见Cerdip)。

BGA是英文Ball Grid Array Package的缩写,即球栅阵列封装。

SOP小型外引脚封装Small Outline Package r¬o0c[hi^M 4srs?}JSSOP收缩型小外形封装Shrink Small Outline Package P pBI%{p)与SOP的区别:近似小外形封装,但宽度要比小外形封装更窄,可节省组装面积的新型封装。

2. DIP(dual tape carrier PACkage)同上。

日本电子机械工业会标准对DTCP 的命名(见DTCP)。

QTCP(quad tape carrier PACkage)四侧引脚带载封装。

TCP 封装之一,在绝缘带上形成引脚并从封装四个侧面引出。

是利用TAB 技术的薄型封装(见TAB、TCP)。

COB(chip on board)板上芯片封装,是裸芯片贴装技术之一,半导体芯片交接贴装在印刷线路板上,芯片与基板的电气连接用引线缝合方法实现,芯片与基板的电气连接用引线缝合方法实现,并用树脂覆盖以确保可靠性。

虽然COB 是最简单的裸芯片贴装技术,但它的封装密度远不如TAB 和倒片焊技术。

JLCC(J-leaded chip carrier)J 形引脚芯片载体。

IC封装术语(中英文对照)

IC封装术语(中英文对照)1、SOW(SmallOutlinePackage(Wide-Jype))宽体SOP。

部分半导体厂家采用的名称。

2、SOF(smallOut-Linepackage)小外形封装。

表面贴装型封装之一,引脚从封装两侧引出呈海鸥翼状(L字形)。

材料有塑料和陶瓷两种。

另外也叫SOL和DFP。

SOP除了用于存储器LSI外,也广泛用于规模不太大的ASSP等电路。

在输入输出端子不超过10~40的领域,SOP是普及最广的表面贴装封装。

引脚中心距1.27mm,引脚数从8~44。

另外,引脚中心距小于1.27mm的SOP也称为SSOP;装配高度不到1.27mm的SOP也称为TSOP(见SSOP、TSOP)。

还有一种带有散热片的SOP。

3、SONF(SmallOut-LineNon-Fin)无散热片的SOP。

与通常的SOP相同。

为了在功率IC封装中表示无散热片的区别,有意增添了NF(non-fin)标记。

部分半导体厂家采用的名称(见SOP)。

4、SQL(SmallOut-LineL-leadedpackage)按照JEDEC(美国联合电子设备工程委员会)标准对SOP所采用的名称(见SOP)。

5、SOJ(SmallOut-LineJ-LeadedPackage)J形引脚小外型封装。

表面贴装型封装之一。

引脚从封装两侧引出向下呈J字形,故此得名。

通常为塑料制品,多数用于DRAM和SRAM等存储器LSI电路,但绝大部分是DRAM。

用SOJ封装的DRAM 器件很多都装配在SIMM上。

引脚中心距1.27mm,引脚数从20至40(见SIMM)。

6、SOIC(smallout-lineintegratedcircuit)SOP的别称(见SOP)。

国外有许多半导体厂家采用此名称。

7、SOI(smallout-lineI-leadedpackage)I形引脚小外型封装。

表面贴装型封装之一。

引脚从封装双侧引出向下呈I字形,中心距1.27mm。

SO、SOP、SOIC封装详解

精心整理SO、SOP、SOIC封装详解2015-12-15一、简介SOP(Small Outline Package)小外形封装,指鸥翼形(L形)引线从封装的两个侧面引出的一种表面贴装型封装。

1968~1969年飞利浦公司就开发出小外形封装(SOP)。

以后逐渐派生出SOJ(J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)及SOT (小外形晶体管)、SOIC(小外形集成电路)等。

在引脚数量不超过40的领域,SOP是普及最广的表面贴装封装,典型引脚中心距 1.27mm(50mil),其它有0.65mm、0.5mm;引脚数多为8~32;装配高度不到1.27mm的SOP也称为TSOP。

表1、常用缩写代码含义代码英文全称中文全称SOP Small Outline Package 小外形封装。

在EIAJ标准中,针脚间距为 1.27mm (50mil)的此类封装被称为“SOP”。

请注意,JEDEC 标准中所称的“SOP”具有不同的宽度。

SOIC Small Outline Integrated Circuit 小外形集成电路。

有时也称为“SO”或“SOL”,在JEDEC标准中,针脚间距为 1.27mm (50mil)的此类封装被称为“SOIC”。

请注意,EIAJ标准中所称的“SOIC”封装具有不同的宽度。

SO Small Outline (SOP的别称)DSO Dual Small Out-lint 双侧引脚小外形封装(SOP 的别称)SOL Small?Out-Line?L-leaded?package 按照JEDEC标准对SOP?所采用的名称SOW Small Outline Package(Wide-Type) 宽体SOP。

部分半导体厂家采用的名称SSOP Shrink Small Outline Package 缩小外形封装VSOP Very Small Outline Package 甚小外形封装VSSOP Very Shrink Small Outline Package 甚缩小外形封装TSOP Small Outline Package 薄小外形封装TSSOP Thin Shrink Small Outline Package 薄的缩小外形封装MSOP Mini Small Outline Package 迷你小外形封装。

SO、SOP、SOIC封装详解

SO、SOP、SOIC封装详解2015-12-15一、简介SOP(Small Outline Package)小外形封装,指鸥翼形(L形)引线从封装的两个侧面引出的TSSOP Thin Shrink Small Outline Package薄的缩小外形封装MSOP Mini Small Outline Package迷你小外形封装。

Analog Devices公司将其称为“micro SOIC”,Maxim公司称其为“SO/uMAX”,而国家半导体(NationalSemiconductor)公司则称之为“Mini SO”SOJ Small Out-Line J-Leaded Package J 形引脚小外型封装SOT Small Outline Transistor小外形晶体管二、宽体、中体、窄体以及SO、SOP、SOIC之争。

在事实上,针对SOIC封装的尺寸标准,不同的厂家分别或同时遵循了两种不同的标准JEDEC (美国联合电子设备工程委员会)和EIAJ(日本电子机械工业协会),结果就导致了“宽体、中体和窄体”三个分支概念的出现,把很多人搞得晕头转向,也激起很多砖家在“宽体、中体、窄体以及SO、SOP、SOIC”几个概念之间争得死去活来。

还有许多来自不同半导体制造商的封装不属于上述标准。

另外,JEDEC和EIAJ这两种标准的名称也并非总是被用于制造商的产品目录和数据表中,除此以外,不同制造商之间的描述系统也不统一。

其实,静下心来,仔细看一下两个封装标准,再对比几种常见的元件尺寸,不难发现,规律其实并不复杂:1、单从字面上理解,其实SO=SOP=SOIC。

2、混乱现象主要出现在管脚间距的封装上,多为74系列的数字逻辑芯片。

3、两个标准对代码缩写各有自己的习惯:EIAJ习惯上使用SOP(体宽);JEDEC习惯上使用SOIC(与两种体宽);也有些公司并不遵守这个习惯,如UTC,使用SOP(与两种体宽);另有很多制造商使用SO、DSO、SOL等。

集成电路封装缩写

BGA(Ball Grid Array):球栅阵列,面阵列封装的一种。

QFP(Quad Flat Package):方形扁平封装。

PLCC(Plastic Leaded Chip Carrier):有引线塑料芯片栽体。

DIP(Dual In-line Package):双列直插封装。

SIP(Single inline Package):单列直插封装SOP(Small Out-Line Package):小外形封装。

SOJ(Small Out-Line J-Leaded Package):J形引线小外形封装。

COB(Chip on Board):板上芯片封装。

Flip-Chip:倒装焊芯片。

片式元件(CHIP):片式元件主要为片式电阻、片式电容、片式电感等无源元件。

根据引脚的不同,有全端子元件(即元件引线端子覆盖整个元件端)和非全端子元件,一般的普通片式电阻、电容为全端子元件,而像钽电容之类则为非全端子元件。

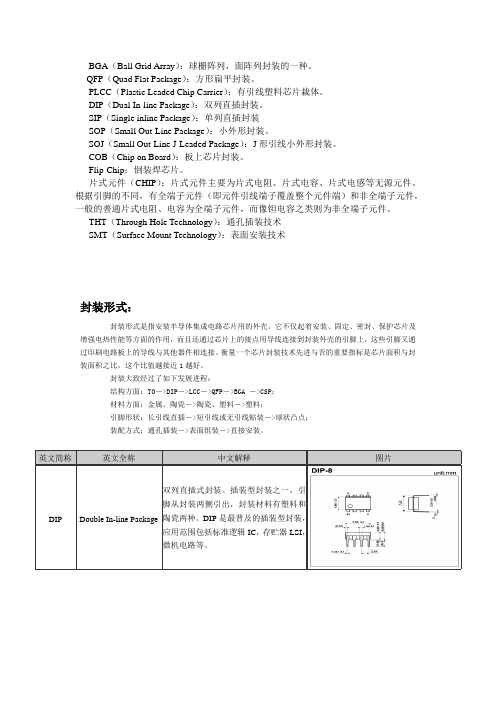

THT(Through Hole Technology):通孔插装技术SMT(Surface Mount Technology):表面安装技术封装形式:封装形式是指安装半导体集成电路芯片用的外壳。

它不仅起着安装、固定、密封、保护芯片及增强电热性能等方面的作用,而且还通过芯片上的接点用导线连接到封装外壳的引脚上,这些引脚又通过印刷电路板上的导线与其他器件相连接。

衡量一个芯片封装技术先进与否的重要指标是芯片面积与封装面积之比,这个比值越接近1越好。

封装大致经过了如下发展进程:结构方面:TO->DIP->LCC->QFP->BGA ->CSP;材料方面:金属、陶瓷->陶瓷、塑料->塑料;引脚形状:长引线直插->短引线或无引线贴装->球状凸点;装配方式:通孔插装->表面组装->直接安装。

双列直插式封装。

插装型封装之一,引脚从封装两侧引出,封装材料有塑料和是最普及的插装型封装,,封装的芯片引脚之间距离很小,管脚很细,一般大规模或超大规模集成电路采用这种封装形式,其引脚数一般年菲为浦公司就开发出小外J (薄小外形SSOP (薄的缩小型SOIC二熟悉公司代理产品线模拟滤波器 光纤通信 高速信号处理和转换 无线/射频 光线通讯,模拟 显示支持电路 高频模拟和混合信号ASIC 数字转换器,接口,电源管理,电池监控 DC/DC 电源 电压基准MAXIM 前缀是“MAX”。

半导体集成电路-常见封装缩写解释

半导体集成电路-常见封装缩写解释半导体集成电路常见封装缩写解释1. DIP(dual in-line PACkage)双列直插式封装。

插装型封装之一,引脚从封装两侧引出,封装材料有塑料和陶瓷两种。

DIP 是最普及的插装型封装,应用范围包括标准逻辑IC,存贮器LSI,微机电路等。

引脚中心距2.54mm,引脚数从6 到64。

封装宽度通常为15.2mm。

有的把宽度为7.52mm 和10.16mm 的封装分别称为skinny DIP 和slim DIP(窄体型DIP)。

但多数情况下并不加区分,只简单地统称为DIP。

另外,用低熔点玻璃密封的陶瓷DIP 也称为Cerdip(见Cerdip)。

BGA是英文Ball Grid Array Package的缩写,即球栅阵列封装。

SOP小型外引脚封装Small Outline Package JSSOP收缩型小外形封装Shrink Small Outline Package P与SOP的区别:近似小外形封装,但宽度要比小外形封装更窄,可节省组装面积的新型封装。

2. DIP(dual tape carrier PACkage)同上。

日本电子机械工业会标准对DTCP 的命名(见DTCP)。

QTCP(quad tape carrier PACkage)四侧引脚带载封装。

TCP 封装之一,在绝缘带上形成引脚并从封装四个侧面引出。

是利用TAB 技术的薄型封装(见TAB、TCP)。

COB(chip on board)板上芯片封装,是裸芯片贴装技术之一,半导体芯片交接贴装在印刷线路板上,芯片与基板的电气连接用引线缝合方法实现,芯片与基板的电气连接用引线缝合方法实现,并用树脂覆盖以确保可靠性。

虽然COB 是最简单的裸芯片贴装技术,但它的封装密度远不如TAB 和倒片焊技术。

JLCC(J-leaded chip carrier)J 形引脚芯片载体。

指带窗口CLCC 和带窗口的陶瓷QFJ 的别称(见CLCC 和QFJ)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SO、SOP、SOIC封装详解

张国营2015-12-15

一、简介

二、宽体、中体、窄体以及SO、SOP、SOIC之争。

在事实上,针对SOIC封装的尺寸标准,不同的厂家分别或同时遵循了两种不同的标准JEDEC(美国联合电子设备工程委员会)和EIAJ(日本电子机械工业协会),结果就导致了“宽体、中体和窄体”三个分支概念的出现,把很多人搞得晕头转向,也激起很多砖家在“宽体、中体、窄体以及SO、SOP、SOIC”几个概念之间争得死去活来。

还有许多来自不同半导体制造商的封装不属于上述标准。

另外,JEDEC和EIAJ这两种标准的名称也并非总是被用于制造商的产品目录和数据表中,除此以外,不同制造商之间的描述系统也不统一。

其实,静下心来,仔细看一下两个封装标准,再对比几种常见的元件尺寸,不难发现,规律其实并不复杂:

1、单从字面上理解,其实SO=SOP=SOIC。

2、混乱现象主要出现在管脚间距1.27mm的封装上,多为74系列的数字逻辑芯片。

3、两个标准对代码缩写各有自己的习惯:

➢EIAJ习惯上使用SOP(5.3mm体宽);

➢JEDEC习惯上使用SOIC(3.9mm与7.5mm两种体宽);

➢也有些公司并不遵守这个习惯,如UTC,使用SOP(3.9mm与7.5mm两种体宽);

➢另有很多制造商使用SO、DSO、SOL等。

4、两个标准规定的尺寸不同,互不兼容,其差异主要体现在宽度WB和WL上,下表给出

了常用SOP封装在两个标准下的WB与WL值:

表2、SOP封装在JEDEC和EIAJ标准下的尺寸差异

引脚数

WB(体宽)WL(总宽)JEDEC EIAJ JEDEC EIAJ

mil mm mil mm mil mm mil mm

8 150 3.8 208 5.3 236 6.0 310 7.9

14 150 3.8 208 5.3236 6.03107.9

16 150/300 3.8/7.5 208 5.3236/400 6.0/10.23107.9

18 300 7.5 208 5.3400 10.2 3107.9

20 300 7.5208 5.340010.23107.9

24 300 7.5208 5.340010.23107.9注:更详细的尺寸信息请参见文件MS-012(JEDEC)、MS-013(JEDEC)和TYPE-II(EIAJ)。

其中WB与WL的含义如下:

三、举例

1、74HC573,仙童公司可同时提供两种封装:

➢SOIC-20---JEDEC MS-013,0.300" =7.5mm Wide

➢SOP-20---EIAJ TYPE II,5.3mm Wide

2、LM2904,TI公司可同时提供两种封装:

➢SOIC-8(D)---JEDEC MS-012 variation AA,0.150"=3.8mm Wide

➢SO-8(PS)---5.3mm Wide

3、74HC595,TI公司可同时提供三种封装:

➢SOIC-16(D)---JEDEC MS-012 variation AC,0.150"=3.8mm Wide

➢SOIC-16(DW)---JEDEC MS-013 variation AA,0.150"=3.8mm Wide

➢SO-16(NS)---5.3mm Wide

四、推荐的标注方法

为避免误解,在设计选型时,尽可能将同一型号的不同制造商的datasheet收集齐全,按制造商的datasheet给出符合通用习惯的代号,对于多种封装尺寸共存的型号(如74HC595),在后面注明尺寸:宽*长,如SOIC-16(3.9*9.9)、SOIC-16(7.5*10.3)、SOP-16(5.3*10.2)。