微机原理期末复习题及答案

微机原理期末试题及答案

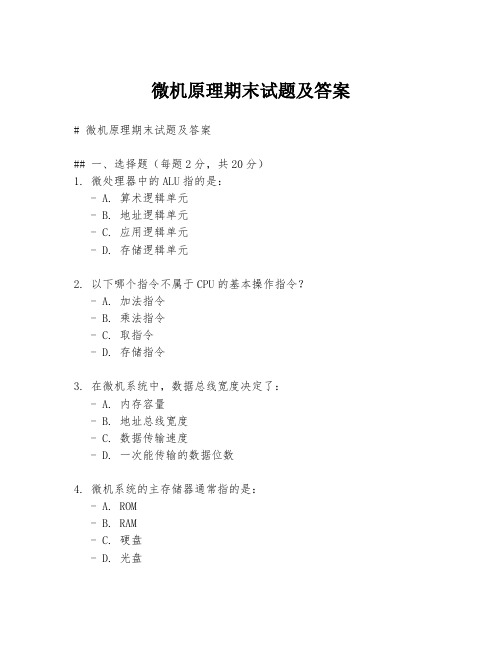

微机原理期末试题及答案# 微机原理期末试题及答案## 一、选择题(每题2分,共20分)1. 微处理器中的ALU指的是:- A. 算术逻辑单元- B. 地址逻辑单元- C. 应用逻辑单元- D. 存储逻辑单元2. 以下哪个指令不属于CPU的基本操作指令?- A. 加法指令- B. 乘法指令- C. 取指令- D. 存储指令3. 在微机系统中,数据总线宽度决定了:- A. 内存容量- B. 地址总线宽度- C. 数据传输速度- D. 一次能传输的数据位数4. 微机系统的主存储器通常指的是:- A. ROM- B. RAM- C. 硬盘- D. 光盘5. 下列哪个不是微机系统的基本组成部分?- A. CPU- B. 主存储器- C. 输入设备- D. 打印机## 二、填空题(每空2分,共20分)6. 在微机系统中,CPU执行指令的过程通常分为四个阶段:取指令、_________、执行指令、_________。

7. 微机系统中的I/O设备通过_________与CPU进行通信。

8. 微机系统中,内存地址从0开始,地址范围通常是_________。

9. 微处理器的指令集是一组_________,定义了CPU可以执行的操作。

10. 微机系统中的中断机制允许_________在某些条件下暂停当前程序的执行,转而执行其他程序。

## 三、简答题(每题15分,共30分)11. 简述微机系统中的总线结构及其作用。

12. 解释微机系统中的DMA(直接存储器访问)机制,并说明其优点。

## 四、计算题(每题15分,共30分)13. 假设有一个8位微处理器,其ALU可以执行加法操作。

如果ALU的输入为01101000B和10101010B,请计算结果,并说明是否有溢出。

14. 给定一个微机系统的时钟频率为2GHz,计算其在一个周期内可以执行的最大指令数,如果每个指令需要4个时钟周期。

## 答案1. A2. D3. D4. B5. D6. 解码指令、写回结果7. I/O控制电路8. 从0到2^n-1(n为地址总线宽度)9. 指令格式和操作码10. 硬件设备或软件中断11. 微机系统的总线结构主要包括数据总线、地址总线和控制总线。

微机原理复习题及答案

微机原理复习题及答案一、单项选择题(每题2分,共20分)1. 微处理器中的ALU负责执行什么操作?A. 算术运算B. 逻辑运算C. 算术和逻辑运算D. 控制运算答案:C2. 在微机中,以下哪个部件负责存储程序和数据?A. 中央处理器(CPU)B. 存储器C. 输入/输出设备D. 总线答案:B3. 8086微处理器的地址总线宽度是多少?A. 8位B. 16位C. 32位D. 64位答案:B4. 微机中的I/O设备通过什么与CPU进行通信?A. 数据总线B. 控制总线C. 地址总线D. 所有总线答案:D5. 微机的存储器分为哪两类?A. 只读存储器和随机访问存储器B. 静态存储器和动态存储器C. 主存储器和辅助存储器D. 内部存储器和外部存储器答案:C6. 微处理器的时钟频率是指什么?A. 处理器的运算速度B. 处理器的时钟周期C. 处理器的时钟脉冲频率D. 处理器的时钟周期数答案:C7. 在微机中,中断服务程序的入口地址通常存放在哪个寄存器中?A. IPB. CSC. DSD. SS答案:B8. 微机的总线通常包括哪几类?A. 数据总线、地址总线和控制总线B. 数据总线、控制总线和电源总线C. 地址总线、控制总线和电源总线D. 数据总线、地址总线和电源总线答案:A9. 微机中的DMA是指什么?A. 直接内存访问B. 动态内存分配C. 数据管理器D. 动态内存访问答案:A10. 微机中,以下哪个部件负责控制数据流向?A. 中央处理器(CPU)B. 存储器C. 输入/输出设备D. 控制器答案:D二、填空题(每空1分,共10分)1. 微处理器中的______(寄存器名)用于存储指令的地址。

答案:IP2. 微机中的______(部件名)用于控制CPU的运行状态。

答案:控制器3. 微机中的______(部件名)用于存储临时数据。

答案:寄存器4. 微机的______(部件名)是CPU与外部设备之间的桥梁。

答案:接口5. 微机中的______(部件名)用于存储程序和数据。

微机原理试题及答案期末

微机原理试题及答案期末

作为微机原理课程的期末考试,试题的出现是为了考查学生在此门课程中所掌握的知识和技能。

本文将为大家提供一套微机原理试题,并附上详细的答案解析。

希望通过本文的解析,能够帮助大家更好地理解微机原理的核心概念与应用。

I. 单选题(每题1分,共20题,共20分)

1. 在8086微处理器中,哪个寄存器用来存储当前指令的操作码?

A. AX

B. IP

C. CS

D. SP

答案:B

解析:IP(Instruction Pointer)是指令指针寄存器,用于存储下一条要执行的指令的内存地址。

2. 内部总线宽度决定了8086微处理器的哪个特性?

A. 寻址能力

B. 计算速度

C. 存储能力

D. 并行传输速度

答案:D

解析:内部总线宽度决定了数据的并行传输速度。

8086微处理器的内部数据总线宽度是16位,可以同时处理16位的数据。

3. DMA是指什么?

A. 直接内存访问

B. 动态内存分配

C. 数据管理程序

D. 目标模块访问

答案:A

解析:DMA(Direct Memory Access)是指计算机直接访问内存的一种技术,通过绕过CPU,将数据直接传输到内存,提高数据传输效率。

...

文中所提供的试题及答案解析仅为示例,真实的微机原理试题可能会更加复杂多样。

在考试前应多做练习,强化对微机原理的理解和应用能力。

通过合理安排学习时间,注重实际操作与理论结合,相信大家一定能够在微机原理这门课程中取得好成绩。

最后,祝愿每一位学生在期末考试中取得优异的成绩!加油!。

微机原理期末考试试题及答案

1.8086的数据线为16 位,地址线为20 位,I/O口使用16 位地址线。

2.在某进制的运算中7×3=33,则7×5=_55。

3.用8位二进制数表示整数时,十进制数(-128)的补码为_10000000_。

原码为无,反码为无。

3.8086内部寄存器长度为16 位,通用寄存器有8 个,段寄存器有4 个。

4.8086偶存储体的选片信号是A0 ,奇存储体的选片信号是BHE 。

5.MOV AX,[BX+SI]的源操作数是基址变址寻址方式,目的操作数是寄存器寻址方式。

6.8086可以指向堆栈的指针寄存器有bp 和sp 。

7.程序中段定义结束的伪指令是ENDS ,子程序定义结束的伪指令是ENDP 。

8.EEPROM的擦除方法为点擦除.9.下列指令段经汇编后,DATA所代表的偏移地址为_100 CH__。

ORG 1000HSTROE DB 12 DUP(?)DATA DB 05H,06H,07H,08H1. 8086/8088在不考虑段跨越情况下,DI寄存器给出的偏移地址位于_C__。

A. 仅DS段B. DS或SS段C. DS或ES段D. DS或CS段2. 下列指令中格式错误的是___A___。

A. SHL AL,CXB. XCHG AL,BLC. MOV BX,[SI]D. AND AX,BX3. 设(20010H)=3FH,(20011H)=B2H,执行下列指令段后,BX=____B__。

MOV AX,2000HMOV DS,AXMOV BX,[0010H]A. B2B2HB. B23FHC. 3F3FHD. 3FB2H4. 若SP=0124H,SS=3300H,在执行INT 60H这条指令后,堆栈栈顶的物理地址为___D___。

A. 3311CHB. 33120HC. 33122HD. 3311EH5. 下列指令中格式错误的是_C__。

A. MOV AX,357AH[BX][DI]B. OUT DX,ALC. LEA AX,50H[BX][BP]D. RCR BX,16. 下列指令中允许寻址范围最大的是_D__。

微机原理_期末考试题库与答案(含3套试卷)

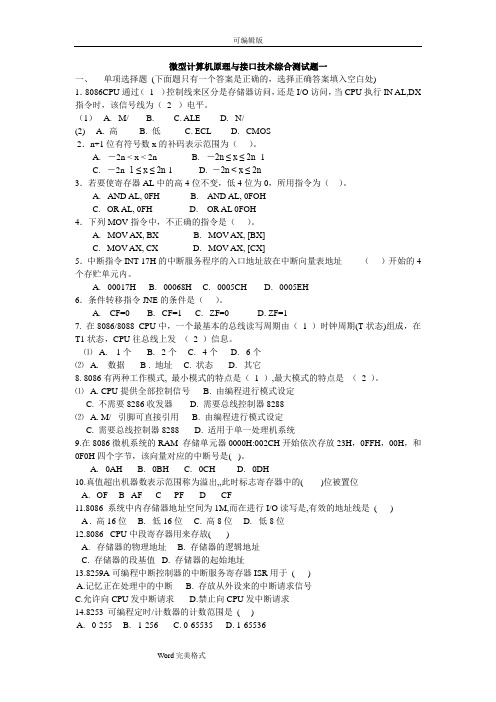

微型计算机原理与接口技术综合测试题一一、单项选择题(下面题只有一个答案是正确的,选择正确答案填入空白处)1.8086CPU通过(1 )控制线来区分是存储器访问,还是I/O访问,当CPU执行IN AL,DX 指令时,该信号线为( 2 )电平。

(1) A. M/ B. C. ALE D. N/(2) A. 高 B. 低 C. ECL D. CMOS2.n+1位有符号数x的补码表示范围为()。

A. -2n < x < 2nB. -2n ≤ x ≤ 2n -1C. -2n -1 ≤ x ≤ 2n-1D. -2n < x ≤ 2n3.若要使寄存器AL中的高4位不变,低4位为0,所用指令为()。

A. AND AL, 0FHB. AND AL, 0FOHC. OR AL, 0FHD. OR AL 0FOH4.下列MOV指令中,不正确的指令是()。

A. MOV AX, BXB. MOV AX, [BX]C. MOV AX, CXD. MOV AX, [CX]5.中断指令INT 17H的中断服务程序的入口地址放在中断向量表地址()开始的4个存贮单元内。

A. 00017HB. 00068HC. 0005CHD. 0005EH6.条件转移指令JNE的条件是()。

A. CF=0B. CF=1C. ZF=0D. ZF=17. 在8086/8088 CPU中,一个最基本的总线读写周期由(1 )时钟周期(T状态)组成,在T1状态,CPU往总线上发(2 )信息。

⑴ A. 1个 B. 2个 C. 4个 D. 6个⑵ A. 数据 B . 地址 C. 状态 D. 其它8. 8086有两种工作模式, 最小模式的特点是(1 ),最大模式的特点是(2 )。

⑴ A. CPU提供全部控制信号 B. 由编程进行模式设定C. 不需要8286收发器D. 需要总线控制器8288⑵ A. M/ 引脚可直接引用 B. 由编程进行模式设定C. 需要总线控制器8288D. 适用于单一处理机系统9.在8086微机系统的RAM 存储单元器0000H:002CH开始依次存放23H,0FFH,00H,和0F0H四个字节,该向量对应的中断号是( )。

微机原理期末考试题库及个别答案

微机原理期末考试题库及个别答案一、填空题1.十进制数11.375转换为二进制数为______;二进制数1101101转换为十进制数为______。

2.二进制数110111100101.1011转换为十六进制数为______。

3.二进制数1001011.1转换为十进制数为______。

4.用MOS器件构成的RAM可分为SRAM_和_DRAM__。

5.A=-113D,则[A]补=__________。

10001111B6.已知BX=1234H,BP=5678H,SI=1357H,DS=0925H,SS=0468H,CS=4B10 H,则指令MOV CL,SS:[SI+50H]中源操作数的寻址方式为_寄存器相对寻址_,存储器操作数的有效地址_13A7H_,实际地址05A27H。

7.对于ADD AL,BL指令,当AX=8573H,BX=8032H时,指令执行后标志位OF=__1___,CF=_0____。

8.变量具有段属性、偏移量属性和类型属性。

9.汇编语言程序的语句可分为两大类:指令性语句和指示性语句。

10.A=-71,则[A]补=______。

11.设一个主存容量为320K,若要访问该主存,其地址码至少__19__位;其最大的主存地址为_4003FH_。

12.8088CPU中指示栈顶的寄存器是_SP_,指示指令执行顺序的寄存器是_IP_。

13.中断处理过程分为中断请求、_中断源识别_(或中断判优)、_中断响应_、中断服务和中断返回。

14.A=+0110101,B=-0110101,[A+B]补=______。

15. 从CPU的NMI引脚产生的中断叫做非屏蔽中断,它的响应不受IF标志___的影响。

16.由INT指令引起的中断称可屏蔽中断,由CPU外部引起的中断称外部中断(或硬件中断)。

17.两片8259级联共可管理_________级中断,若从片连接在主片的IR2上,则从8259A 的ICW3为___________。

微机原理期末试题及答案

微机原理期末试题及答案一、选择题(每题2分,共20分)1. 在计算机系统中,CPU指的是:A. 中央处理器B. 存储器C. 输入设备D. 输出设备答案:A2. 下列哪个不是微机的组成部分?A. 总线B. 内存C. 硬盘D. 打印机答案:D3. 在计算机中,1KB的存储空间等于:A. 1024字节B. 1000字节C. 1024位D. 1000位答案:A4. 8086微处理器的地址总线宽度是:A. 16位B. 32位C. 24位D. 8位答案:A5. 下列哪个指令是用于数据传输的?A. MOVB. ADDC. SUBD. JMP答案:A二、简答题(每题10分,共30分)1. 简述冯·诺依曼计算机体系结构的主要特点。

答案:冯·诺依曼计算机体系结构的主要特点包括:程序存储、程序控制、指令和数据以同等地位存储在同一存储器中、顺序执行指令。

这种结构简化了计算机的设计,使得计算机能够自动、连续地执行程序。

2. 解释什么是指令周期,并简述其主要步骤。

答案:指令周期是CPU执行一条指令所需的全部时间,包括取指令、分析指令、执行指令等步骤。

在每个指令周期中,CPU首先从存储器中取出指令,然后对指令进行译码,最后执行指令所指定的操作。

3. 描述微机总线的基本功能。

答案:微机总线是连接CPU、内存、输入输出设备等组件的通信线路,其基本功能包括数据传输、地址传输和控制信号传输。

数据总线用于在CPU和存储器或输入输出设备之间传输数据;地址总线用于指定数据传输的目标地址;控制总线则用于传输控制信号,如读写信号、中断请求等。

三、计算题(每题15分,共30分)1. 假设一个计算机系统使用16位地址总线,计算该系统的最大内存容量。

答案:使用16位地址总线,意味着可以寻址2^16个不同的内存单元。

如果每个内存单元存储1字节,则最大内存容量为2^16字节,即65536字节,或64KB。

2. 给定一个二进制数10110110,请计算其二进制补码。

微机原理期末考试试题及答案

1.8086的数据线为16 位,地址线为20 位,I/O口使用16 位地址线.2。

在某进制的运算中7×3=33,则7×5=_55。

3。

用8位二进制数表示整数时,十进制数(-128)的补码为_10000000_。

原码为无,反码为无。

3.8086内部寄存器长度为16 位,通用寄存器有8 个,段寄存器有4 个。

4.8086偶存储体的选片信号是A0 ,奇存储体的选片信号是BHE .5.MOV AX,[BX+SI]的源操作数是基址变址寻址方式,目的操作数是寄存器寻址方式。

6.8086可以指向堆栈的指针寄存器有bp 和sp 。

7.程序中段定义结束的伪指令是ENDS ,子程序定义结束的伪指令是ENDP 。

8.EEPROM的擦除方法为点擦除.9.下列指令段经汇编后,DATA所代表的偏移地址为_100 CH__.ORG 1000HSTROE DB 12 DUP(?)DATA DB 05H,06H,07H,08H1. 8086/8088在不考虑段跨越情况下,DI寄存器给出的偏移地址位于_C__。

A. 仅DS段B。

DS或SS段C。

DS或ES段D。

DS或CS段2. 下列指令中格式错误的是___A___。

A。

SHL AL,CX B。

XCHG AL,BLC. MOV BX,[SI]D. AND AX,BX3. 设(20010H)=3FH,(20011H)=B2H,执行下列指令段后,BX=____B__.MOV AX,2000HMOV DS,AXMOV BX,[0010H]A. B2B2HB. B23FH C。

3F3FH D. 3FB2H4。

若SP=0124H,SS=3300H,在执行INT 60H这条指令后,堆栈栈顶的物理地址为___D___。

A. 3311CHB. 33120HC. 33122H D。

3311EH5. 下列指令中格式错误的是_C__。

A。

MOV AX,357AH[BX][DI] B。

OUT DX,ALC。

微机原理复习题(附答案)

微机原理复习题(附答案)一.名词解释1.算术逻辑部件(ALU)(P4)答:cpu内部的算数逻辑部件也叫运算器,是专门用来处理各种数据信息的,它可以进行加、减、乘、除算术运算和与、或、非、异或等逻辑运算。

2.控制器(P5)答:是CPU的控制中心3.字长(P9)答:是cpu同时能处理的数据位数,也称数据宽度。

字长越长,计算能力越高,速度越快。

4.主频(P9)答:Cpu的时钟频率,和cpu的运算速度密切相关,主频越高,运算速度越快。

5.偶校验(P11)答:运算结果的低八位中所含的1的个数为偶数,则PF为1。

6.奇校验(P11)答:运算结果的低八位中所含的1的个数为奇数,则PF为0。

7.总线周期(P12)答:在取指令和传送数据时,CPU总线接口部件占用的时间。

8.最小模式(P13)答:在系统中只有一个微处理器9.中断向量(P27)答:中断处理子程序的入口地址,每个中断类型对应一个中断向量。

10.非屏蔽中断(NMI)(P28)答:从引脚NMI进入的中断,它不受中断允许标志IF的影响。

11.可屏蔽中断(INTR)(P28)答:从引脚INTR进入的中断,它受中断允许标志IF的影响。

12.基址(P77)答:任何通用寄存器都可以作为基址寄存器,即其内容为基址。

注意,这里的基址不是段基址,而只是一个延续下来的习惯叫法,实际上是指有效地址的一个基础量。

13.直接寻址(P77)答:数据在存储器中,有效地址由指令直接给出。

默认段地址寄存器DS。

直接寻址是对存储器访问时可采用的最简单的方式。

14.指令性语句(P127)答:一条指令,在汇编的过程中会产生对应的目标代码。

如:ADD AL,BL和MOV AX,1000都是指令性语句。

15.指示性语句(伪指令)(P127)答:伪指令,为汇编程序提供某些信息,让汇编程序在汇编过程中执行某些特定的功能。

16.接口技术(P177)答:接口按功能分为两类:一类是使CPU正常工作所需要的辅助电路,通过这些辅助电路,使CPU得到时钟信号或接收外部的多个中断请求等;另一类是输入/输出接口,利用这些接口,CPU可接收外部设备送来的信息或发送给外设。

微机原理复习题及答案

微机原理复习题及答案一、选择题1. 微处理器中的寄存器主要用于存储什么?A. 指令B. 数据C. 地址D. 程序答案:B2. 在微机系统中,总线分为哪几种类型?A. 数据总线B. 地址总线C. 控制总线D. 所有以上答案:D3. 微机系统中,CPU的主要功能是什么?A. 存储数据B. 执行程序C. 管理内存D. 显示图像答案:B4. 在微机系统中,RAM和ROM的区别是什么?A. RAM是只读存储器,ROM是随机存取存储器B. RAM是随机存取存储器,ROM是只读存储器C. RAM和ROM都是随机存取存储器D. RAM和ROM都是只读存储器答案:B5. 微机系统中的I/O设备指的是什么?A. 输入/输出设备B. 内部/外部设备C. 集成电路/操作系统设备D. 接口/操作系统设备答案:A二、填空题6. 微机系统中的CPU由______和______组成。

答案:算术逻辑单元(ALU);控制单元(CU)7. 微机系统中的______用于存储正在执行的指令。

答案:指令寄存器(IR)8. 微机系统中的______用于存储当前正在处理的数据。

答案:累加器(ACC)9. 在微机系统中,______是用于存储指令和数据的设备。

答案:内存10. 微机系统中的______是用于输入输出数据的设备。

答案:外部设备三、简答题11. 简述微机系统中的指令周期包括哪些步骤?答案:指令周期通常包括取指令、分析指令、执行指令和写回结果四个步骤。

12. 描述微机系统中的中断系统的作用。

答案:中断系统允许微机在执行程序的过程中,响应并处理外部或内部的突发事件,提高了系统的响应能力和效率。

四、计算题13. 假设一个微机系统有16位地址总线和8位数据总线,请计算该系统的最大内存容量。

答案:最大内存容量 = 2^地址总线位数 * 数据总线位数 = 2^16 * 2^8 = 65536 * 256 = 16777216字节,即16MB。

五、论述题14. 论述微机系统中的流水线技术及其优点。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、选择题:1、(1101001.101)2= DA (69.625)10B (1101001.101) BCDC (69.5)16D (100000101.011000100101)BCD2、若X=-1110110,则[X]原= (1)B ,[X]补= (2)C , [-X/2]补= D (3) 。

(1) A 01110110B 11110110C 10001010D 10001001 (2) A 01110110B 00001010C 10001010D 11110110 (3) A 00010101 B 11111011 C 10001100 D 001110113、已知CS=1000H , DS=4000H ,ES=2000H ,BX=0250H ,SI=0382H ,8086/8088指令 MOV AX , [BX+SI]中源操作数的寻址方式是 D (1) ,目标操作数的寻址方式是 (2)A 。

CPU 执行该指令时,应从内存中物理地址为 B (3) 的字单元中取出数据。

(1) A 寄存器间址方式 B 基址寻址方式 C 变址寻址方式 D 基址加变址寻址方式(2) A 寄存器寻址方式 B 寄存器间址方式 C 基址寻址方式 D 变址寻址方式(3) A 205D2H B 405D2H C 20632H D 40632 H4、若8088 CPU 的寄存器AL 和BL 中分别存放了9AH 和7DH 两个数,当CPU 执行ADD AL, BL 指令操作后,状态寄存器FR 的标志位CF 、OF 、ZF 、SF 分别为 C (1) ,AL 和BL 的内容分别为 (2)D 。

(1)A 0、0、0、0 B 1、0、1、0 C 1、0、0、0 D 0、1、1、0(2)A 117H 和7DH B 117H 和9AH C 17H 和9AH D 17H 和7DH 5、8253外接频率为1MHZ 的时钟信号,若控制字设置为74H ,则8253将工作于 D (1) ,当写入计数器的16位计数初值为7000H 时,可定时的时间为 B (2) 。

(1) A 计数通道0的方式1,按二进制计数 B 计数通道0的方式2,按二进制计数C 计数通道1的方式2,按BCD 码计数 D 计数通道1的方式2,按二进制计数(2) A 7ms B 28.672ms C 70msD 286.72ms 8253 控制字0 0通道0 0 0 计数器锁存 0 0 0 方式0 0 二进制计数0 1 通道1 0 1 读/写低字节 0 0 1方式1 1 BCD 码计数1 0 通道2 1 0 读/写高字节 0 1 0方式21 1 先读/写低字节 0 1 1方式3后读/写高字节 1 0 0方式41 0 1方式56、某80X86微处理器有16条数据线,24条地址线,由该处理器组成的微机系统的最大内存容量为(1)D,该微机被称为(2)B 。

(1) A 216×2 字节 B 216×1字节 C 224×16位 D 224×8位(2) A 8位机 B 16位机 C 24位机 D 32位机7、在8086/8088的中断中,只有(1)B需要外部硬件提供中断类型码,中断类型码是在(2)C通过(3)A 送给CPU的。

(1)A 外部中断 B 可屏蔽中断 C 非屏蔽中断 D 内部中断(2) A 中断请求周期 B 第一个中断响应周期 C 第二个中断响应周期 D存储器读周期(3) A 数据总线 B 地址总线 C 控制总线 D A+B8、下图是一微机系统采用一片8259A构成的中断系统,若8259A设置为全嵌套、非缓冲、非自动中断结束等方式,并ICW2初始化设置为28H,当定时器和串口同时产生中断请求时,则CPU响应中断将从(1)C 存储单元中取得中断服务程序入口地址。

在中断服务结束前(IRET指令前)必须将中断结束命令写入8259A的C(2)。

(1) A B2H-B5H B 112H-115H C A0H-A3H D A0-A7H(2) A ICW1 B OCW1 C OCW2 D OCW3二、填空题:1、8086CPU 有20条地址线,以8086 CPU为核心的微型机的存储器容量最大可达1MB 。

整个存储器可分为奇地址存储体和偶地址存储体,它们的容量均为 512KB 。

2、8086/8088系统的栈区设置在堆栈段中。

一个栈区的最大容量可达64KB,若CS=2000H,DS= 2000H,SS=1500H,SP= 1500H,AX= 0F68H,当执行指令 PUSH AX后,其栈顶的物理地址为164FEH,其单元中内容为68H。

3、8086/8088系统的存储器地址有逻辑地址和物理地址,逻辑地址是指段基地址和偏移地址,物理地址由20 位二进制数组成,它的计算公式为PA= 段基地址*16 + 偏移地址。

4、一般CPU和外设之间传送数据的方式有无条件传送、查询传送、中断传送和直接数据通道传送四种,CPU访问外设接口可有两种编址方式:端口独立编址方式和与存储器统一编址;一般8086/8088 系统采用端口独立编址方式,当将数据写入外设接口时应采用OUT指令。

5、中断是的过程。

8086/8088中断系统最多允许有256个中断源,在内存物理地址为00000H—00FFFH内建立了一个中断向量表,所谓中断向量是指中断服务程序入口地址。

6、若CS=1000H, SS=2000H, DS=ES=3000H, BX=0500H, BP=0200H,IP=1500H ,则CPU要取的当前指令在代码段逻辑段中,其物理地址为11500H ,该逻辑段的长度为64KB 。

7、串行通信接口的作用是实现串行到并行和并行到串行的转换。

若一个串行接口设置为7位数据位、1位终止位和无校验位的异步通信传送方式,当传送7位二进制数5BH时,串口发送的帧格式为011011011 。

三、分析以下以8088为 CPU的最小模式系统,回答以下问题。

1、简要说明系统中各组成部分的作用。

(6分)2、若系统要求配置10KB的存储器,,其中4KB ROM类存储器和6KB RAM 类存储器,ROM 的地址从18000H开始,RAM地址在ROM后连续。

如果采用4KB ROM芯片和 2KB RAM芯片,试写出各芯片的地址范围。

(6分)1、系统由8088CPU、存储器、I/O接口、8282地址锁存器、8284时钟发生器、8286总线驱动器等组成。

8088CPU 是系统控制指挥中心,所有指令的执行、读写存储器和输入输出接口、系统的功能操作都是由CPU完成的;存储器存放CPU执行的指令程序和系统运行过程中的数据;I/O接口连接CPU和外部输入输出设备,保证它们之间数据传送;8282地址锁存器把8088CPU AD0-AD7、AD16/S3-AD19/S6 分时复用线输出的地址信号锁存;8284主要为8088CPU提供工作时钟信号;8286总线驱动器增强cpu数据线的负载能力。

2、采用1片ROM芯片和3片RAM芯片。

ROM芯片地址范围为: 18000H - 18FFFH#1 RAM 芯片地址范围为: 19000H – 197FFH#2 RAM 芯片地址范围为:19800H – 19FFFH#3 RAM 芯片地址范围为:1A000H – 1A7FFH四、以下为8088系统中以8255A 为输入设备和输出设备的查询方式接口电路的部分硬件图。

(18分)1、试述8088CPU和输入设备进行数据传送的工作过程。

(6分)输入设备要将数据传送给CPU时,先将数据输出给8255A的PA0-PA7,然后通过ACK端输出脉冲信号将数据锁存于锁存器,同时将触发器置1。

而CPU要不断查询设备的状态,执行读8255A C口操作,判断从C口读入数据的D1位是1还是0,若为0表示设备未准备好,则等待后再查询;若为1表示设备已将数据送出, CPU 从 8255A的 A口读入数据,然后通过PC 6输出负脉冲将状态触发器清0。

之后重复以上的操作,周而复始。

2、以下是8088CPU将存于以BLOCK为首址的内存单元区域中100个数据依次传送给输出设备的程序段,请在划线处填入内容。

BLOCK DB a1,a2,……a100COUNT EQU $-BLOCKSTART: LEA SI, BLOCK ;置数据单元首址指针MOV CX , COUNTMOV DX, 383H;8255A初始化设置MOV AL, 91HOUT DX, ALMOV DX, 383H;置PC7为低电平MOV AL, 0EHOUT DX, ALAGAIN: MOV DX, 382H ;查询输出设备状态IN AL, DXTEST AL, 04HJNZ AGAINMOV AL, [SI] ;取数据传送给输出设备INC SIMOV DX, 381HOUT DX, ALMOV DX, 383H ;置PC7产生高电平MOV AL, 0FHOUT DX, ALNOPNOPMOV AL, 0EH;置PC7为低电平OUT DX, ALLOOP AGAINRET8255A方式控制字 8255A C口复位/置位控制字1 D6 D5 D4 D3 D2 D1 D0 0 0 0 0 D3 D2 D1 D0A口方式00 方式0 A口C口下半口01 方式1 0 输出0 输出000 PC0 0复位1×方式2 1 输入 1 输入001 PC1 1 置位B口010 PC2C口上半口B口方式0 输出∶∶0 输出0 方式0 1 输入111 PC71 输入 1 方式1五、分析以下汇编语言源程序,根据要求在划线处填上适当内容:DATA SEGMENT AT 2000HORG 0100HTABLE DB 66,76,87,89, 96, 79, 64, 62, 57, 49, 85, 75, 60, 77, 58 COUNT EQU $-TABLENUM1 DB 0NUM2 DB 0NUM3 DB 0DATA ENDSSTACK SEGMENT PARA STACK 'STACK'TOP DB 100 DUP(?)STACK ENDSCODE SEGMENTASSUME CS:CODE,DS:DATA, SS:STACKMAIN : MOV AX,DATAMOV DS,AXMOV SI,OFFSET TABLEMOV CX,COUNTLOP1: MOV AL, [SI]CMP AL, 85JA HIGHCMP AL, 70JBE LOWINC NUM2JMP NEXTHIGH: INC NUM1JMP NEXTLOW: INC NUM3NEXT: INC SILOOP LOP1MOV AH, 4CHINT 21HCODE ENDSEND MAIN(1) 画出数据段中数据定义语句实现的内存分配图。