什么情况下需要做阻抗控制

PCB设计的阻抗控制和阻抗匹配

重要性,电路板出故障或问题的概率, 为一个电容( 图 1 - 1) 。

阻抗控制的精度就越低。

电路中信号的完整性,电路的 E M I 和

(4 )容易造成焊锡短路,可能会增

EMC 特性。但是随着产品的可靠性发展

加产品的成本。

和越来越受到重视,在设计时不再是

PCB 的各层分布一般是对称的。不

简单的导线连接,必须考虑电路中信

Key words: Reliability; Characteristic Impedance; Impedance Controlling; Impedance match

CLC number: TN306

Document code:A

Article ID:1003-0107(2005)04-0029-03

430068)

Huang Shuwei, Zhao Danling1

(Hubei University of Technology,

Wuhan 430068,China)

摘 要: 阻抗设计是 PCB 可靠性设计的一个重要环节。本文从多层 PCB 板叠层的设计原理、特性阻抗的

计算方法、严格的阻抗控制,来保证阻抗匹配,实现 P C B 的可靠性,使产品稳定的工作。

号完全相等。这就是说, 应将信号对称 别是在高频电路中,特性阻抗主要取 特性阻抗是否一致,是否匹配。因此,

地布线在内部地线层的两侧。这样做 决于连线的单位分布电容和单位分布 在 P C B 设计的可靠性设计中有两个概

的优点是容易控制阻抗和环流;缺点 电感带来的分布阻抗。理想传输线的 念是我们必须注意的。

印制电路板上导线的特性阻抗是

传输线的特性阻抗只与信号连线 电路板设计的一个重要指标,特别是

fpc常用阻抗线宽 -回复

fpc常用阻抗线宽-回复什么是fpc常用阻抗线宽?FPC,即柔性印刷电路板(Flexible Printed Circuit Board),是一种由柔性绝缘基材制成的电路板。

它具有弯曲性、折叠性和轻薄性的特点,广泛应用于电子产品中。

FPC的阻抗控制是保证电路性能稳定的重要因素之一,而阻抗线宽是指FPC电路板上信号线的宽度。

不同的阻抗线宽会对信号传输造成影响,因此在设计FPC时,选择适当的阻抗线宽非常关键。

接下来,我们将一步一步回答关于FPC常用阻抗线宽的问题。

1. 为什么要控制阻抗?阻抗是电路中电流和电压之间的相互阻碍程度,它会对信号的传输和电路的性能产生影响。

如果信号传输中的阻抗不匹配,信号会受到反射和衰减,导致信号完整性和电路稳定性的下降。

因此,在设计FPC电路板时,需要控制阻抗,以确保信号的传输稳定和减少信号失真。

2. 如何计算阻抗线宽?阻抗线宽的计算是一个复杂的过程,涉及到电磁场理论和电路设计知识。

一般情况下,可以通过使用电路设计软件或阻抗计算工具进行计算。

这些工具可以根据所选用的绝缘材料、信号层间距、板厚等参数来计算出合适的阻抗线宽。

3. FPC常用的阻抗线宽有哪些?常用的阻抗线宽取决于具体的应用和设计要求。

下面是一些常见的FPC阻抗线宽值:- 50欧姆:常用于高频信号传输,如无线通信设备。

- 75欧姆:广泛应用于电视、无线电和通信设备。

- 90欧姆:常用于高速信号传输,如USB、HDMI和DisplayPort等。

- 100欧姆:用于DDR记忆体和PCIe接口等高速数据传输。

需要注意的是,这些阻抗线宽仅作参考,实际应用时还需要根据具体的设计需求和阻抗控制要求来确定。

4. 如何控制阻抗线宽?控制阻抗线宽的主要方法有两种:板厚和线宽。

通过调整FPC电路板的厚度和信号线的宽度,可以实现所需的阻抗值。

较薄的板和较窄的线宽会增加电流在板上的流动速度,从而增加阻抗。

但是,太薄的板和太窄的线宽可能会导致机械强度下降和加工难度上升,因此在设计时需要进行合理的取舍。

用于测试的控制阻抗设计

用於測詴的控制阻抗設計背景TDR(時域反射計)已經成為測量印刷電路板上的控制阻抗的既定技術。

理想情況下,6英寸的線路長度(IPC2141標準推薦)即可以輕鬆的進行測量,這一長度可以有明顯的平直線路區域,確保精確測量阻抗。

設計時的考慮因素幾個簡單的設計考慮因素將有助於製造商獲取最佳生產效益並降低高性能電路板的成本。

樣板測詴用於PCB工廠的最簡單的方法是使用測詴樣板來驗證控制阻抗PCB。

這些樣板或者是由客戶設計的,或者是由製造商的前端部門添加的。

大型游戏机通常客戶將禁止更改樣板。

這些探針必須頻繁的更換,所以需要PCB製造商在多種測詴系統探針上投資。

這將降低測量系統的R&R。

因此設計廠商和製造商之間需要協調,修改樣板的大小,減少所需的探棒變動的次數。

為何不使用可變間距探棒?儘管這些探棒皆有現成,但它們比較昂貴並且設計用於非連續性操作。

可變間距探棒對於操作者來說使用不是很方便,長期大量使用可變點距探針將導致糟糕的R&R。

電路板測詴大部分測詴是在樣板上進行的。

如果需要在電路板上按照理想情況測詴線路,則電路板樣板線線上應該在邊緣進行終點,並且應該明確標記。

此外,線路穿過貫穿孔應該足夠大,以便於進行手動探棒測詴。

在微條上進行手動TDR測詴幾乎是不可能的!儘管RF觸點可能佈置的非常出色,但是在如此小的接觸區域上使用手動探棒是不切實際的。

如果您需要測詴實際的PCB 線路,需要記住測詴需要從網端開始,而且從該處必須可以存取信號測詴點附近的接地,否則,就不可能在良好的RF條件下連接測詴線路。

測詴線路的長度要在生產中得到可重覆和一致的結果,您需要設計足夠長的測詴線路,避免測詴結果受到探棒到線路的互連的偏差(從線路的起點)和脈衝偏移(導致線路在線路物理中,斷點之前開始上升)的影響。

儘管有些刊物推薦特定的線路測詴區域(例如50% 到70%),但這對於較短的線路而言並非是上佳之選。

樣板的最佳線路長度是 6 英寸(150mm)。

阻抗控制

随着 PCB 信号切换速度不断增长,当今的 PCB 设计厂商需要理解和控制 PCB 迹线的阻抗。

相应于现代数字电路较短的信号传输时间和较高的时钟速率,PCB 迹线不再是简单的连接,而是传输线。

在实际情况中,需要在数字边际速度高于1ns 或模拟频率超过300Mhz时控制迹线阻抗。

PCB 迹线的关键参数之一是其特性阻抗(即波沿信号传输线路传送时电压与电流的比值)。

印制电路板上导线的特性阻抗是电路板设计的一个重要指标,特别是在高频电路的PCB 设计中,必须考虑导线的特性阻抗和器件或信号所要求的特性阻抗是否一致,是否匹配。

这就涉及到两个概念:阻抗控制与阻抗匹配,本文重点讨论阻抗控制和叠层设计的问题。

阻抗控制阻抗控制(eImpedance Controling),线路板中的导体中会有各种信号的传递,为提高其传输速率而必须提高其频率,线路本身若因蚀刻,叠层厚度,导线宽度等不同因素,将会造成阻抗值得变化,使其信号失真。

故在高速线路板上的导体,其阻抗值应控制在某一范围之内,称为“阻抗控制”。

PCB 迹线的阻抗将由其感应和电容性电感、电阻和电导系数确定。

影响PCB走线的阻抗的因素主要有: 铜线的宽度、铜线的厚度、介质的介电常数、介质的厚度、焊盘的厚度、地线的路径、走线周边的走线等。

PCB 阻抗的范围是 25 至120 欧姆。

在实际情况下,PCB 传输线路通常由一个导线迹线、一个或多个参考层和绝缘材质组成。

迹线和板层构成了控制阻抗。

PCB 将常常采用多层结构,并且控制阻抗也可以采用各种方式来构建。

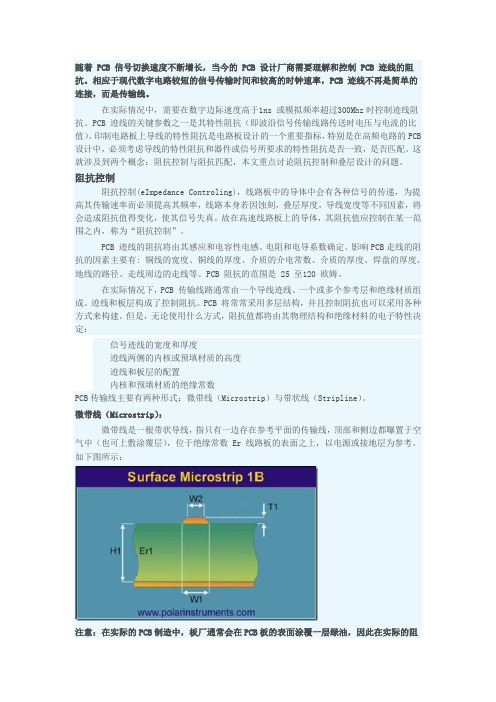

但是,无论使用什么方式,阻抗值都将由其物理结构和绝缘材料的电子特性决定:信号迹线的宽度和厚度迹线两侧的内核或预填材质的高度迹线和板层的配置内核和预填材质的绝缘常数PCB传输线主要有两种形式:微带线(Microstrip)与带状线(Stripline)。

微带线(Microstrip):微带线是一根带状导线,指只有一边存在参考平面的传输线,顶部和侧边都曝置于空气中(也可上敷涂覆层),位于绝缘常数 Er 线路板的表面之上,以电源或接地层为参考。

PCB阻抗控制

PCB阻抗PCB阻抗控制,在PCB设计中经常遇到阻抗计算,但是我不明白阻抗计算是计算整板PCB的阻抗还是几个部分的阻抗PCB阻抗,在PCB设计中经常遇到阻抗计算,但是我不明白阻抗计算是计算整板PCB的阻抗还是几个部分的阻抗:如我有差分阻抗,单线阻抗。

那到底该采用哪些数值呢?可能几个部分的阻抗都不一样在同一PCB板上?这样的话该计算哪个阻抗来作为PCB的阻抗呢!完整性最佳。

是不是每个地方阻抗不一样,我得告诉PCB厂商,这个地方阻抗做多少,哪个地方阻抗做多少啊,比如:USB2.0差分做成90欧姆,DDR与DSP连接线做成多少欧姆,和时钟线做成多少欧姆等等啊?这样的话是不是要详细说明多处的阻抗要求。

关键布线部分是要给出详细的设计要求的,设计时的阻抗大小,是通过仿真软件,使信号完整性达到最好状态下,得到的。

根据仿真结果,可以得到该信号线的线长,线宽,线间距,在那层布线,串接多大的匹配电阻等要求,然后仿真设计人员将此仿真结果交给PCB LAUOUT设计人员,PCB LAUOUT设计人员会根据此要求进行PCB布线设计,设计完毕后的PCB文件生成为GERBER文件,送给PCB制造厂商即可制造出相应的PCB。

1.阻抗控制是控制信号线的阻抗,不是整板PCB的阻抗2.差分阻抗是两条差分信号的阻抗,单线阻抗是单一信号的阻抗。

如USB 2.0要做差分90欧姆,射频信号线一般做单线50欧姆等等。

哪些线要做阻抗控制,控制为多少,一般每个硬件平台都有自己的要求。

3.没有PCB阻抗这种说法,只有信号的阻抗。

电路设计中,差分信号的两条差分线能不能交换顺序?题目说的有些笼统,主要是想知道哪些是可以交换的,为什么,哪些是不可以交换的,又是为什么?还有差分线之间跨加100ohm或12 0ohm的电阻的作用是什么,是阻抗匹配还是将电流转换为电压?各位大牛,ths了会变小。

差分信号实际传输是电压还是电流,什么差分信号,说的通俗一点,差分信号时属于数字信号吗进一步看是以电压为的标准的能量信号,若内阻小,就可以带多个负载(电流大)。

【精品】阻抗控制子宫内膜去除术NovaSure治疗月经过多的临床

【关键字】精品阻抗控制子宫内膜去除术(NovaSure)治疗月经过多的临床观察蒋建发,肖松舒,薛敏中南大学湘雅三医院妇产科,湖南长沙,410013摘要目的:探讨阻抗控制子宫内膜去除术(NovaSure)治疗月经过量的有效性及安全性。

方法:回顾性分析2011年1月~2012年7月在我院行阻抗控制子宫内膜去除术且术后随访3个月的129例月经过量患者的临床资料,其中包括有严重并发症的患者22例。

结果:129例患者均顺利完成手术,术中出血量少,术中术后无严重手术相关并发症发生,术后3个月后随访显示闭经者103例,仍有少量阴道流血者25例,月经无明显改善者1例,闭经率为79.84%,治疗有效率为99.22%,99.22%的患者对治疗效果满意。

结论:阻抗控制子宫内膜去除术是一种治疗月经过量安全有效的治疗方法,对于有严重合并症的月经过量患者可优先考虑此手术。

关键词:月经过量;子宫内膜去除术;诺舒NovaSure impedance controlled endometrial ablation for hypermenorrheaJIANG Jian-fa, XIAO Song-shu, XUE MinDepartment of Gynecology and Obstetrics, , , 410013,Abstract: Objective To investigate the efficacy and safety of NovaSure impedance controlled endometrial ablation treatment of women with hypermenorrhea.Methods From January 2011 to July 2012, 129 women with hypermenorrhea were treated with NovaSure impedance controlled endometrial ablation in our hospital, including 22 patients with severe complication, all of them were successfully followed-up for three months. Their clinical data were retrospectively analyzed. Results The procedure was completed successfully in all the patients. The blood loss was little and there were no severe surgical complications. 103 patients were amenorrhea, 25 patients were low menstrual volume and only one patient remained hypermenorrhea after surgery. The rate of amenorrhea was 79.84%; the rate of efficacy was 99.22%. 99.22% of the patients were satisfied with this treatment. Conclusion NovaSure impedance controlled endometrial ablation was safe and effective, especially for the patients with severe complication.Key Words: hypermenorrhea; endometrial ablation; NovaSure女性正常月经的临床表现为经期2~7天,周期21~35天,经量为30~50 ml。

PCB设计之阻抗控制的走线细节举例

PCB设计之阻抗控制的走线细节举例1.走线的宽度和间距:走线的宽度和间距会直接影响走线的阻抗。

通常情况下,走线的宽度越宽,阻抗越低。

为了控制阻抗,可以在设计软件中使用特定的规则来指定走线的宽度和间距。

例如,对于常见的50欧姆的阻抗控制要求,可以将规则设置为适当的走线宽度和间距。

2.层数的选择:在高速信号传输中,层数的选择也会影响阻抗。

较高的层数可提供更多的走线空间,有助于降低阻抗。

因此,为了阻抗控制,可以选择适当的层数。

在多层PCB设计中,内层走线的间距和宽度也需要综合考虑,以保持阻抗的一致性。

3.地平面的设计:在PCB设计中,地平面的设计是控制阻抗的关键。

地平面应尽可能地平整,并且与走线保持一定的距离。

这样可以减少地平面与走线之间的互电容和互电感,从而提高阻抗的一致性。

为了实现这一点,可以在地平面上设置一些小孔,用于连接不同地层,从而提高地层的连贯性。

4.走线的形状和拐角:走线的形状和拐角也会影响阻抗。

通常情况下,直线和圆弧形的走线对阻抗控制较好,而直角拐弯较差。

在需要进行90度拐角的情况下,可以使用斜角拐弯来减小阻抗的变化。

此外,走线的形状和转角也会对电磁兼容性(EMC)产生影响,在设计时需要综合考虑。

5.信号层和电源/地层的分离:为了阻抗控制,信号层和电源/地层应尽可能地分离。

这样可以减少信号层与电源/地层之间的互电容和互电感,从而提高阻抗的一致性。

在多层PCB设计中,可以选择在信号层之间插入电源/地层,建立一个电源平面或地平面来提供均匀的分布。

6.终端匹配:终端匹配是一种常用的阻抗控制技术。

通过在信号线的起始和终止位置添加合适的电阻、电容等元件,可以达到匹配信号线的阻抗。

例如,可以在信号线的终止位置添加电阻,以匹配信号线和负载之间的阻抗。

终端匹配可以在设计中通过网络分析软件来实现。

综上所述,PCB设计中的走线细节对于阻抗控制至关重要。

通过选择适当的走线宽度和间距、层数、设计合理的地平面、走线的形状和拐角以及合理的终端匹配,可以实现阻抗的一致性,提高信号传输的质量和稳定性。

PCB做板阻抗要求

PCB做板阻抗要求PCB (Printed Circuit Board)是电子产品中常见的元件基板,在现代电子技术中扮演着重要的角色。

在PCB设计和制造过程中,一个关键的要求就是满足特定的板阻抗要求。

本文将详细介绍PCB板阻抗要求的重要性、应用、设计考虑因素和制造过程中的技术。

首先,了解什么是PCB板阻抗要求是很重要的。

在电路板上的信号传输中,阻抗是指信号线上的电阻、电感和电容等的总和。

正确地控制板阻抗对于设计和制造高性能电路板至关重要。

当信号通过PCB时,如果线路上的阻抗不匹配,会引起信号反射、干扰和信号失真等问题,进而影响电路的性能和可靠性。

对于不同的应用场景,PCB板阻抗要求也不同。

例如,在高速数字通信系统、宽频带射频通信系统和高频率电子设备中,要求更严格的板阻抗控制,以确保信号传输的稳定性和准确性。

而在一般的低频电子产品中,对板阻抗的要求相对较低。

因此,设计和制造过程中需要根据不同应用场景来确定PCB板阻抗的要求。

在PCB板阻抗设计方面,需要考虑的因素有很多。

首先是PCB的层堆栈构造。

层堆栈是指PCB板上不同层的结构和排列方式。

通常情况下,高速和高频率应用需要更多的层来实现更好的阻抗控制。

其次是PCB板上线路的布局和走线方式。

规划合理的线路布局和走线方式可以降低信号的干扰和互相影响,提高整体的信号完整性。

此外,还需要考虑信号线的宽度和间距、板材的介电常数等因素。

PCB板阻抗的制造过程中,也有一些关键的技术需要注意。

首先是选用合适的板材。

不同的板材具有不同的介电常数和损耗切角等特性。

正确选择板材可以满足所需的板阻抗要求。

其次是合理的堆叠方式。

通过优化层堆栈结构、调整层间距等方法可以减小信号之间的干扰和影响。

还需要注意制造工艺中的控制参数,例如线路的涂覆厚度、铜层的厚度控制等。

总的来说,PCB板阻抗要求是电子产品成功设计和制造的重要因素之一、合理的板阻抗设计可以保证电路的高性能和可靠性,有效地解决信号传输中的问题。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

什么情况下需要做阻抗控制

什幺情况下需要做阻抗控制?

高速传输、高频讯号传输的传输线,在质量上要比传输导线严格得多。

不再是“开路/短路”测试过关,或者缺口、毛刺未超过线宽的20%,就能接收。

必须要求测定特性阻抗值,这个阻抗也要控制在公差以内,否则,只有报废,不得返工。

特性阻抗值控制缘由:

1、缘由一

电子设备(电脑、通信机)操作时,驱动元件(Driver)所发出的信号,将通过PCB传输线到达接收元件(Receiver)。

信号在印制板的信号线中传输时,其特性阻抗值Z0 必须与头尾元件的“电子阻抗”能够匹配,信号中的“能量”才会得到完整的传输。