利用DSPBuilder设计定点FFT处理器

利用DSPBuilder设计定点FFT处理器

3 [收稿日期]2007-02-29 [作者简介]杨守良(1970-),男,重庆铜梁人,高级实验师,重庆大学在读硕士研究生,主要从事控制理论与控制工程研究. [基金项目]重庆文理学院重点项目资助金资助项目(Z2006WX19). 2007年6月重庆文理学院学报(自然科学版)Jun 1,2007 第26卷 第3期Journal of Chongqing University of A rts and Sciences (Natural Science Editi on )Vol 126 No 13利用DSP Builder 设计定点FFT 处理器杨守良(重庆文理学院 物理与信息工程系,重庆 永川 402160)[摘 要]分析了FFT 算法的原理,并利用DSP Builder 建立了输入为8点基-2FFT 算法的基本模型,在Si m ulink 和Quartus Ⅱ中分别进行了仿真,并将仿真结果与Matlab 仿真值进行了比较,实现了8点实序列FFT 算法.基于DSP Builder 的FFT 算法设计简单,可以重复使用,大大提高了设计效率.[关键词]数字信号处理;DSP Builder;FFT;算法[中图分类号]T N911.7 [文献标识码]A [文章编号]1673-8012(2007)02-0040-03快速傅里叶变换(FFT )算法是数字信号处理中最常用的算法之一.实现FFT 算法的方法有软件法和硬件法.软件法实现比较灵活,但速度受限,因此在实时性要求高的场合多用硬件实现1但由于硬件法实现浮点数的运算要分别对阶和尾数进行运算,所以浮点运算比整数运算复杂,它所需要的硬件设备也更多.随着FPG A 的出现以及EDA 技术的成熟,采用定点运算器以模拟浮点运算来实现数字信号处理的方法已经显示出巨大的潜力[1].1 FFT 算法原理对于一个N 点有限长序列x (n ),其DFT 变换可表示为:X (k )=∑N -1n =0x (n )W nk N .其中,k =0,1,…,N -1;W N =e -j 2πN .假如x (n )、W N 都为复数,计算N 点序列的DFT 共需要N 2次复数乘法和N (N -1)次复数加法1在N 较大时,计算量不可想像.可以利用FFT 本身具有的周期性和对称性,将输入时间序列分解成奇、偶两个子序列1设x N (n )DFT X N (k ),于是有:X N (k )=X e N 2(k )+W kn N X o N 2(k ),(1)X N (k +N 2)=X e N 2(k +N 2)-W kn N X oN 2(k +N 2).(2)(1)式和(2)式中,k =0,1,…,N 2-1;X e N 2(k )和X o N 2(k )分别表示奇数点和偶数点的DFT .图1 D I T 运算信号流图根据(1)式和(2)式,可以用图1来描述其运算的信号流图.由于该运算状似蝶形,故有时也称为蝶形运算.对于N =2M ,可以一直分解到2点DFT .这样,离散傅里叶变换的运算量就大大减少了1这种DFT 的快速算法就是按时间抽取的基-2FFT 1图2给出了N =8时此FFT 算法的信号结构流图[2,3]1图2 N=8时FFT算法的信号流2 利用DSP Builder设计FFT根据图2所示的8点基-2时间抽取的信号流图,首先在Matlab\si m ulink下建立FFT运算模型.由于蝶形运算涉及复数运算,较为复杂,DSP Builder为能实现FFT模型的建构,专门引入了蝶形算子模块Butterfly.但实际使用过程中发现,由于FFT运算常常需要进行小数的运算,在搭建FFT模型时,需将蝶形运算中的蝶形运算系数即FFT运算中的旋转因子转成小数的表示方法.这显然是非常费时费力的,而且很容易出错.而在A lera DSP Builder的算术库中有一个乘加运算模块,它由一个或多个乘法器和一个并行加法器构成,其中所有的乘法器的输出都进入加法器中进行操作,而且输入的数据的数据类型可以是有符号整数、无符号整数、有符号二进制小数等.在调用此模块时,只要选择小数点以左的二进制数位和小数点以右的二进制数位,就可以很容易地构建定点小数的乘加运算.为此,根据FFT算法原理和图2所示的8点FFT算法信号流图,不难在MAT LAB/Si m ulink下建立8点FFT运算模型[4-7],如图3所示.图中wst表示W0,wnt表示W18,wnst表示W28,wncst表示W38,其具体的数值可8以在Matlab下运算后得到.x(0),x(1),x(2),…,x(7)表示输入的实数序列;X(0),X(1),X(2),…, X(7)表示经过FFT运算后的频域序列.在Si m ulink下,在输入端输入一序列x(n)=2,2,4,7,3,5,5,8,图3中从上到下是按倒位序排列输入的数据,因此输出的结果即按正常顺序输出.表1(见下页)所示的是FFT模型输出的数据和利用MAT LAB内部函数fft(x)计算的数据.图3 N=8时的FFT模型表1 FFT模型输出的数据和利用MAT LAB内部函数fft(x)计算的数据输入输出参考值23636.00002-2.412+3.832i-2.41+3.84i4-4+8i-4.0000+8.0000i70.418+1.836i0.4219+1.844i3-8-8.000050.4102-1.836i0.4102-1.84i5-4-8i-4.0000-8.0000i8-2.418-3.836i-2.422-3.844i 由表1中所列数据可以看出,两者数据非常接近,因此模型正确,于是利用DSP Builder本身自带的Signal Comp iler模块将其转换成VHDL语言.再在QuartusⅡ中,对刚才的设计项目进行编译并进行仿真,其仿真波形如图41由图4显示的数据可以看出,QuartusⅡ仿真输出的数据与模型仿真的数据是完全相符的,说明设计无误.最后将其下载到目标器件中,就得到根据用户需要的FFT处理芯片.图4 QuartusⅡ中仿真波形3 结语在MAT LAB/Si m ulink环境下借助A ltera DSP Builder可快速进行定点FFT处理器的设计,避免了利用硬件来表示浮点数的麻烦.另外,借助MAT LAB的仿真功能可方便地查看设计结果,因此它是一种简单有效的设计方法.从图3可以看出,其FFT运算完全是并行的,这样使得采用FPG A来实现数字信号处理可以很好地解决并行性和速度问题,而且其灵活的现场可配置特性使得FPG A构成的数字信号处理系统非常易于修改、测试及硬件升级.[参考文献][1]孙飞,周宁,孙亚楠,等.一种8点fft算法的逻辑电路实现[J].微电子学与计算机,2002,19(11):5-7,10.[2]刘桂华,傅佑麟,严平.FFT实时谱分析系统的FPG A设计和实现[J].电子技术应用,2005,31(4):65-67.[3]程佩青.数字信号处理教程(第2版)[M].北京:清华大学出版社,2001.[4]潘松,黄继业,曾毓.S OPC技术实用教程[M].北京:清华大学出版社,2005.[5]潘松,黄继业,王国栋.现代DSP技术[M].西安:西安电子科技大学出版社,2003.[6]王金明,杨吉斌.数字系统设计与Veril ogHDL[M].北京:电子工业出版社,2002.[7]韩颖,等.FPG A实现高速加窗复数FFT处理器的研究[J].北京理工大学学报,2003,23(3):381-385.(下转第53页)得e1=λ2-λ1λ2,e2=λ3-λ1λ3.所以珒e=1-λ1λ2,1-λ1λ3.由此可知双曲面形状与λ1,λ2,λ3有关,进而由特征方程可知双曲面形状与I1,I2,I3有关,与I4无关.通过对椭圆以及椭球的形状和大小同不变量的关系的讨论,可以得出规律:I1和I2完全刻画椭圆形状,I2和I3完全刻画椭圆面积;不变量I3和I4完全刻画椭球体积大小;不变量I1,I2,I3完全刻画椭球面形状.这对我们提高对二次曲线与二次曲面不变量几何特性的认识很有帮助.致谢:本文得到聂智副教授的悉心指导,在此表示感谢.[参考文献][1]吕林根,许子道.解析几何[M].北京:高等教育出版社,2006:231-240.[2]吕林根,张紫霞,孙存金.解析几何学习指导书[M].北京:高等教育出版社,2001:48-49.[3]陈纪修,於崇华,金路.数学分析(下册)[M].北京:高等教育出版社,1999.On the I nvar i a n ts’Geom etr i c Character isti c of Quadr i c Curve and Quadr i c SurfaceWANG W ei-sheng1,T AO Cheng-hai2(1.D ep t.o fM a th a nd Com p ute r Sc i ence,C hongqi ng U ni ve rs ity o f A rts a nd Sc i e nce s,Yongchuan C ho ngq i ng402160,C h i na;2.C ho ngq i ng No.1H i gh S choo l,Shap i ngba C hongqi ng400030,C h i na)Abstract:The geometric meanings of the invariants I1,I2,I3,I4(quadric curve without I4)composed by equati on coefficients are given though the study of the m.Key words:invariant;eccentricity;area;volu me;peri m eter(上接第42页)D esi gn of F i xed-Po i n t FFT Processor Ba sed on D SP Bu ilderY ANG Shou-liang(D ep t.of Phys i c s&I nfo r m a ti o n Engi nee ri ng,C ho ngqi ng U n i ve rs ity of A rts and Sc i ence s,Yongchuan C ho ngq i ng402160,C h i na) Abstract:The FFT algorith m p rinci p le is analyzed,make use of DSP Builder t o have built8points of the deci m ate in ti m e(D I T)radix-2fast Fourier transfor m(FFT),has separately carried on the si m ulati on in Si m ulink and QuartusⅡ.Then the author i m itated the si m ulati on result and the true value ofMatlab t o carry on the comparis on,realized8points of real nu mber sequence FFT alg orithm,had the design based on the DSP Builder FFT algorithm t o be si m p le,may dup licate uses,greatly enhanced the rated capacity.Key words:D igital Signal Pr ocessing;DSP Builder;FFT;A lgorith m。

实验5基于DSP Builder的8点FFT仿真与硬件环验证

实验5 基于DSP Builder的8点FFT仿真与硬件环验证[实验目的]

1.了解FFT的原理。

2.掌握FFT不同的实现结构。

3.通过DSP Builder实现FFT并进行仿真。

[实验原理]

参考上课内容,书上第8章。

[实验内容]

1.运行Matlab,利用DSP Builder构建8点FFT模型。

2.在输入端接入不同的信号源,在输出端连接示波器和频谱分析仪,对滤波器进行仿真。

3.利用signal complier 对滤波器进行编译综合,得到硬件实现数据。

[实验要求]

1.在DSP Builder构建8点FFT模型的基础上添加Multiplexer将并行输出转换为串行复数序列在示波器上以两路显示,输入不同的序列观测不同的输出。

2.在此基础上构建硬件环(HIL)验证模型,将综合编译生成的配置文件下载到开发板上进行验证。

[扩展部分]

1.将8点FFT扩展为16点FFT

a)可以使用更多的蝶形算子模块。

b)或者采用可变蝶形算子模块实现时分复用结构的FFT。

[实验结果] 1、系数设计

观测结果。

基于DSP Builder数字滤波器的FPGA设计

基于DSP Builder数字滤波器的FPGA设计摘要:现场可编程门阵列( FPGA) 器件广泛应用于数字信号处理领域,而使用VHDL 或VerilogHDL 语言进行设计比较复杂。

提出一种采用DSP Builder 实现IIR数字滤波器的设计方案,按照Matlab/Simulink/DSP Builder/QuartusⅡ的设计流程,设计了一个4阶IIR 低通数字滤波器,并通过QuartusⅡ软件中的嵌入式逻辑分析仪SignalTapⅡ对设计进行了硬件实时测试。

结果表明,所设计的IIR数字滤波器功能正确,性能良好。

Abstract: Field Programmable Gate Array (FPGA) devices is widely used in the field of digital signal processing, but it is complicated to design using VHDL or VerilogHDL. A method of designing IIR digital filter based on DSP Builder are pointed out. Then a 4-order low-pass IIR digital filter was designed according to the process ofMatlab/Simulink/DSP Builder/QuartusⅡ, and the practical test was finished based on Signa1TapⅡof QuartusⅡsoftware. The result shows the designed filter correct in function and good in performance.关键词: FPGA;无限长脉冲响应滤波器;DSP Builder;QuartusⅡKey words: FPGA;IIR filter;DSP Builder;QuartusⅡ中图分类号:TN911.72 文献标识码:A 文章编号:1006-4311(2011)07-0141-020 引言数字滤波器是现代数字信号处理系统的重要组成部分之一,具有模拟滤波器所无法替代的新特性,因此在通信、语音与图像处理、自动控制等领域有着广泛的应用,它对于降低噪声、提高信噪比及信号的频谱纯度等方面有着重要的意义。

基于DSP的FFT实现

基于DSP的FFT实现傅里叶变换(Fourier Transform)是一种将信号在时间和频率域之间进行转换的数学工具。

它可以将信号从时域转换为频域,使我们能够分析信号的频率成分。

离散傅里叶变换(Discrete Fourier Transform,DFT)是一种计算机算法,用于对离散信号进行傅里叶变换。

离散信号是由一系列采样点组成的,并且在实际应用中,离散信号更常见于数字信号处理(Digital Signal Processing,DSP)系统。

FFT(Fast Fourier Transform)是一种高效的算法,用于计算DFT。

它通过利用信号的对称性和周期性,以O(nlogn)的时间复杂度计算DFT,相比于直接计算的O(n^2)时间复杂度更为高效。

因此,FFT在数字信号处理中被广泛使用,并且是很多DSP系统中实现频谱分析的核心算法。

基于DSP的FFT实现通常采用固定点数格式进行计算,以适应数字信号的要求。

固定点数格式将浮点数表示为带有整数和小数部分的定点数,其中小数部分的位数是固定的。

这允许在硬件实现中使用更简单和更高效的运算器,并且减少了计算过程中的存储需求。

在前向变换中,基于DSP的FFT实现通常采用蝶形运算器结构,该结构通过并行计算减少了计算量。

蝶形运算器将复数乘法和加法运算相结合,以高效地计算傅里叶变换的结果。

在反向变换中,基于DSP的FFT实现使用相同的蝶形运算器结构,但需要调整一些参数来恢复时域信号。

这些参数通常是指数项,用于将频域信号的幅度和相位信息与原始时域信号进行组合。

由于DSP系统通常具有固定的计算能力和存储容量,基于DSP的FFT 实现需要考虑对资源的高效利用。

这可能包括通过流水线技术实现并行计算,使用分块技术减少存储需求,并使用低功耗算法来减少计算负载。

总结起来,基于DSP的FFT实现是一种高效的数字信号处理技术,用于将时域信号转换为频域信号。

它通过利用固定点数格式和蝶形运算器结构,以高效和准确的方式计算傅里叶变换。

基于DSP Builder的FIR滤波器设计与实现

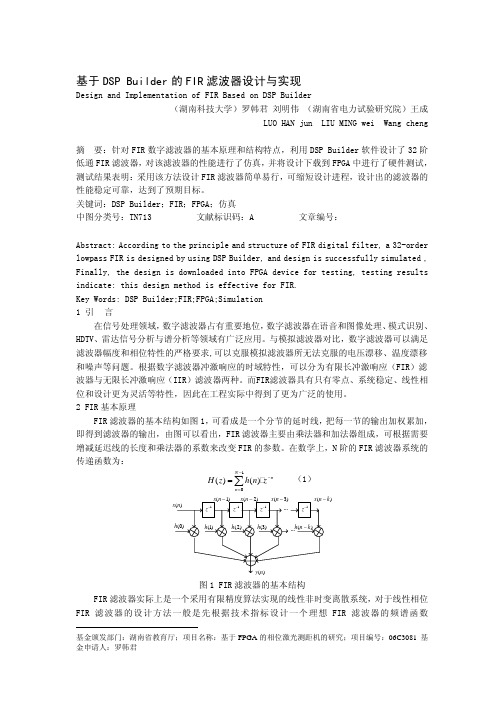

基于DSP Builder 的FIR 滤波器设计与实现Design and Implementation of FIR Based on DSP Builder(湖南科技大学)罗韩君 刘明伟 (湖南省电力试验研究院)王成LUO HAN jun LIU MING wei Wang cheng摘 要:针对FIR 数字滤波器的基本原理和结构特点,利用DSP Builder 软件设计了32阶低通FIR 滤波器,对该滤波器的性能进行了仿真,并将设计下载到FPGA 中进行了硬件测试,测试结果表明:采用该方法设计FIR 滤波器简单易行,可缩短设计进程,设计出的滤波器的性能稳定可靠,达到了预期目标。

关键词:DSP Builder;FIR;FPGA;仿真中图分类号:TN713 文献标识码:A 文章编号:Abstract: According to the principle and structure of FIR digital filter, a 32-order lowpass FIR is designed by using DSP Builder, and design is successfully simulated , Finally, the design is downloaded into FPGA device for testing, testing results indicate: this design method is effective for FIR. Key Words: DSP Builder;FIR;FPGA;Simulation 1 引 言在信号处理领域,数字滤波器占有重要地位,数字滤波器在语音和图像处理、模式识别、HDTV、雷达信号分析与谱分析等领域有广泛应用。

与模拟滤波器对比,数字滤波器可以满足滤波器幅度和相位特性的严格要求,可以克服模拟滤波器所无法克服的电压漂移、温度漂移和噪声等问题。

基于DSPBuilder数字信号处理课程设计

上海电力学院基于DSP Builder数字信号处理课程设计实验名称:AM调制FM调制及DDS信号专业:通信工程姓名:班级:学号:一、设计目的通过本次课程设计,巩固已学数字电路与逻辑设计的理论知识,掌握数字信号处理方法,引导学生从功能设计转向系统设计,掌握由现场可编程逻辑器件实现数字信号处理的方法,掌握现场可编程逻辑器件的应用设计,从而拓宽数字技术及处理的知识和设计能力,提高学生动手能力,培养学生分析问题与解决问题的能力。

二、设计内容本设计利用FPGA开发软件QuartusII,DSP BUILDER,MATLAB,设计实现各类波形信号的发生电路,如AM调制、FM调制、DDS控制等,进行引脚锁定、全编译通过后,完成FPGA器件Cyclone II的配置工作,并在Matlab Simulink中使用Scope显示仿真结果,在DE2开发板上下载并通过七段数码管,显示波形情况。

三、设计要求1.独立完成AM调制、FM调制、DDS控制电路的设计、译码显示电路的设计。

2.熟悉QuartusII,DSP BUILDER,MATLAB环境下系统开发设计流程。

3.在DE2上验证设计结果,并认真写出设计报告。

四、设计原理及步骤(一).AM 调制的设计AM 幅度调制函数信号可以用式)m 1(am dr ⋅+⋅=F F F 来表述,其中,dr F 、am F 、F 分别是被调制的载波信号,需要被调制的信号和调制后AM 的输出信号,它们都是有符号数,m 是调制度,10<<m 。

s (t )=m (t )*sin (t )其中m (t )是1或者是0,sin (t )是载波观察s (t )如果有波形输入的是1没波形是0。

基于DSP Builder 的数字的AM 系统如下图所示元器件的主要参数设定在这里省略介绍仿真如下图所示:通过matlab 转化成VHDL 语言通过Quartus2并下到板上验证,在这里需要添加几个模块一是分频器因为我们晶振频率较高反映在数码管上分辨不出所以叫频率降低,二是把8位的二进制传化成三位的十进制数,三是把十进制的数显示在数码管上;最后通过引脚分配输入端口有时钟clock 、使能端sw ,一个数字输入拨码开光,输出有四个数码管显示。

基于DSP Builder的数字滤波器设计与实现

该模 块可方便 地把 MA L BS ui T A / m l k中的设计 i n 转换为 F G P A可编译的 V D 文件 圈 H L 。

2 I滤波器 的D PB i e设计 1 阶F 6 R S ul r d

21 滤波器参数选取 .

利用 MA L B提供 的滤波器设计 的专门工 TA 具箱 F A o l D T o可以方便地设计滤波器系数 。根

(= -- ) j i1 )

B i e ̄具箱 中的模块进行简单的调用即可。值 ul r d 得注意的是 , S u dr D PB i e 中的 D P l S 模块是以算法

级 的 描 述 出现 的 ,易于用户从 系统 或 者 算 法 级 进

典 型 的直 接 I FR滤 波器 如 图 l 示 ,滤 型 I 所

(l ke 的形式出现 ,可以在 S ui 环境下进 Bo s ) c t i lk m n

1 FR 波 器 原 理 与 D PB i e I滤 S ul r d

11 I滤 波器 原 理 . FR

对于 一 个 FR 滤 波器 系统 ,它 的冲 激响应 总 I 是有 限长 的,FR 滤 波器 的数 学表 达 式可 用差 分 I

A src: il r ga b ta tFe po rmmal gt ary(P A) eie aewie sdi ii linl r csn p l a o s d be a r e a F G dvcs r dl ue dgt g a po e igapi t n y n as s ci

—弛

12 . DSP B i e ul r d

。蕴 : . 源自图 1 直 接 型 FR 滤 波器 结 构 图 I

以往 MA L T AB工 具 的使 用 往往 作为 DS P算

基于dspbuilder的数字滤波器设计方法

基于dspbuilder的数字滤波器设计方法摘要:FPGA正在替代ASIC和PDSP用于前端数字信号处理的运算,采用FPGA进行算法运算比PDSP器件具有更高的效率,更低的成本和功耗。

文章以设计一个32阶fir滤波器为例,验证采用MATlab的DSPbuider工具可大大提高FPGA 编程效率,省去了底层代码编写时间,使设计者更专注于系统级算法的设计。

关键词:dspbuilder;FPGA;数字滤波器数字滤波器应用于修正或改变时域或频域中信号的属性,最普通的数字滤波器就是线性时间不变量(LTI)滤波器,LTI通过与输入信号相互作用经过线性卷积,表示为,其中f是滤波器的脉冲相应,x是输入信号,而y是卷积输出。

线性卷积过程的正式定义为:y[n]=x[n]※f[n]=x[k]f[n-k]=f[k]x[n-k] (1)1模块构建及仿真利用DSPbuilder进行滤波器算法设计,并进行仿真,需设置系统参数,构建信号处理模块、信号源、频谱分析及时波器等外围模块,以及仿真功能。

1.1设置系统参数在MATLAB中新建FIR_32tap_setup.m文件。

在其中设置如下:clock_freq = 100e6;sample_time = 1/clock_freq;clock_period = 1/(clock_freq*1e-9);fir_coeff = firpm(31,[0 0.1 0.2 0.5]*2,[1 1 0 0]);fir_coeff = round(fir_coeff.*(2-1));点击运行按钮,并关闭编辑器。

1.2外围激励的设计在simulink中新建FIR_32tap_ex2.mdl模块。

Sine Wave 0.33及sine wave 0.01分别产生两个正弦波信号,经过ADD模块叠加后输入Fir 32滤波器模块中进行处理,处理前的信号频谱可由input Spectrum观察,处理后的结果由scope模块显示模拟波形,频谱可由output Spectrum观察。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

左的二进制数位和小数点以右的二进制数位 ,就可以很容易地构建定点小数的乘加运算. 为此 ,根据

FFT算法原理和图 2所示的 8点 FFT算法信号流图 ,不难在 MATLAB / Simulink下建立 8点 FFT运算

模型 [ 4 - 7 ] ,如图

3所示. 图中

w st表示

W

0 8

,

wn t表示

W

X

o N 2

(k

+N) 2

.

(2)

(1)式和 (2)式中 , k = 0, 1, …, N

-

1;

X

e N

(k) 和

X

o N

( k) 分别表示奇数点和偶数点的

D FT.

2

2

2

根据 (1)式和 (2)式 ,可以用图 1 来描述其运算的信

号流图. 由于该运算状似蝶形 ,故有时也称为蝶形运算.

对于 N = 2M ,可以一直分解到 2点 DFT. 这样 ,离散

图 3 N = 8时的 FFT模型 41

表 1 FFT模型输出的数据和利用 MATLAB内部函数 fft( x)计算的数据

输入

输出

参考值2ຫໍສະໝຸດ 3636. 0000

2

- 2. 412 + 3. 832 i

- 2. 41 + 3. 84 i

4

- 4 +8i

- 4. 0000 + 8. 0000 i

7

0. 418 + 1. 836 i

杨守良

(重庆文理学院 物理与信息工程系 ,重庆 永川 402160)

[摘 要 ]分析了 FFT算法的原理 ,并利用 DSP B uilder建立了输入为 8点基 - 2 FFT算法的基 本模型 ,在 Simulink和 Quartus Ⅱ中分别进行了仿真 ,并将仿真结果与 M atlab仿真值进行了比 较 ,实现了 8点实序列 FFT算法. 基于 DSP B uilder的 FFT算法设计简单 ,可以重复使用 ,大大 提高了设计效率. [关键词 ]数字信号处理 ; DSP Builder; FFT;算法 [中图分类号 ] TN911. 7 [文献标识码 ]A [文章编号 ]1673 - 8012 (2007) 02 - 0040 - 03

0. 4219 + 1. 844 i

3

-8

- 8. 0000

5

0. 4102 - 1. 836 i

0. 4102 - 1. 84 i

5

- 4 - 8i

- 4. 0000 - 8. 0000 i

8

- 2. 418 - 3. 836 i

- 2. 422 - 3. 844 i

由表 1中所列数据可以看出 ,两者数据非常接近 ,因此模型正确 ,于是利用 DSP Builder本身自带

傅里叶变换的运算量就大大减少了 1这 种 DFT 的 快 速

算 法 就 是 按 时 间 抽 取 的 基 - 2FFT1图 2 给出了 N = 8

图 1 D IT运算信号流图

时此 FFT算法的信号结构流图 [ 2, 3 ] 1

3 [收稿日期 ] 2007 - 02 - 29 [作者简介 ] 杨守良 (1970 - ) , 男 , 重庆铜梁人 , 高级实验师 , 重庆大学在读硕士研究生 , 主要从事控制理论与控制工程

全刻画椭圆面积 ; 不变量 I3 和 I4 完全刻画椭球体积大小 ;不变量 I1 , I2 , I3 完全刻画椭球面形状. 这对我们提高对二次

曲线与二次曲面不变量几何特性的认识很有帮助.

致谢 :本文得到聂智副教授的悉心指导 ,在此表示感谢.

[参考文献 ]

[ 1 ]吕林根 ,许子道. 解析几何 [M ]. 北京 :高等教育出版社 , 2006: 231 - 240. [ 2 ]吕林根 ,张紫霞 ,孙存金. 解析几何学习指导书 [M ]. 北京 :高等教育出版社 , 2001: 48 - 49. [ 3 ]陈纪修 ,於崇华 ,金路. 数学分析 (下册 ) [M ]. 北京 :高等教育出版社 , 1999.

On the Invar ian ts’Geom etr ic Character istic of Quadr ic Curve and Quadr ic Surface WAN G W ei - sheng1 , TAO Cheng - hai2

( 1. D ep t. o f M a th a nd Com p u te r S c ie nce , C ho ngq ing U n ive rs ity o f A rts a nd S c ie nce s, Yo ngchua n C ho ngq ing 402160, C h ina; 2. C ho ngq ing No. 1 H igh S choo l, S hap ingba C ho ngq ing 400030, C h ina )

2007年 6月 第 26卷 第 3期

重庆文理学院学报 (自然科学版 ) Journal of Chongqing University of A rts and Sciences (Natural Science Edition)

Jun1, 2007 Vol126 No13

利用 DSP Builder设计定点 FFT处理器

图 4 QuartusⅡ中仿真波形

3 结语 在 MATLAB / Simulink 环境下借助 A ltera DSP B uilder可快速进行定点 FFT处理器的设计 ,避免了

利用硬件来表示浮点数的麻烦. 另外 ,借助 MATLAB 的仿真功能可方便地查看设计结果 ,因此它是一 种简单有效的设计方法. 从图 3可以看出 ,其 FFT运算完全是并行的 ,这样使得采用 FPGA 来实现数 字信号处理可以很好地解决并行性和速度问题 ,而且其灵活的现场可配置特性使得 FPGA 构成的数 字信号处理系统非常易于修改 、测试及硬件升级.

研究. [基金项目 ] 重庆文理学院重点项目资助金资助项目 ( Z2006WX19).

40

图 2 N = 8时 FFT算法的信号流

2 利用 DSP B uilder设计 FFT

根据图 2所示的 8点基 - 2时间抽取的信号流图 ,首先在 M atlab \ simulink下建立 FFT运算模型.

对于一个 N 点有限长序列 x ( n) ,其 DFT变换可表示为 : X ( k) 其中 , k = 0, 1, …, N - 1; WN = e- .j2Nπ

N-1

∑ =

x

(

n

)

W

nk N

.

n =0

假如 x ( n) 、WN 都为复数 ,计算 N 点序列的 DFT共需要 N2 次复数乘法和 N (N - 1) 次复数加法 1

在 Simulink下 ,在输入端输入一序列 x ( n) = 2, 2, 4, 7, 3, 5, 5, 8 ,图 3中从上到下是按倒位序排

列输入的数据 ,因此输出的结果即按正常顺序输出. 表 1 (见下页 )所示的是 FFT模型输出的数据和利

用 MATLAB 内部函数 fft ( x) 计算的数据.

[参考文献 ]

[ 1 ]孙飞 ,周宁 ,孙亚楠 ,等. 一种 8点 fft算法的逻辑电路实现 [ J ]. 微电子学与计算机 , 2002, 19 (11) : 5 - 7, 10. [ 2 ]刘桂华 ,傅佑麟 ,严平. FFT实时谱分析系统的 FPGA 设计和实现 [ J ] . 电子技术应用 , 2005, 31 (4) : 65 - 67. [ 3 ]程佩青. 数字信号处理教程 (第 2版 ) [M ]. 北京 :清华大学出版社 , 2001. [ 4 ]潘松 ,黄继业 ,曾毓. SOPC技术实用教程 [M ]. 北京 :清华大学出版社 , 2005. [ 5 ]潘松 ,黄继业 ,王国栋. 现代 DSP技术 [M ]. 西安 :西安电子科技大学出版社 , 2003. [ 6 ]王金明 ,杨吉斌. 数字系统设计与 VerilogHDL [M ]. 北京 :电子工业出版社 , 2002. [ 7 ]韩颖 ,等. FPGA 实现高速加窗复数 FFT处理器的研究 [ J ]. 北京理工大学学报 , 2003, 23 (3) : 381 - 385.

在 N 较大时 ,计算量不可想像. 可以利用 FFT本身具有的周期性和对称性 ,将输入时间序列分解成奇 、

偶两个子序列 1设 xN ( n) DFT XN ( k) ,于是有 :

XN ( k)

=

X

e N

( k)

2

+

W

kn N

X

o N 2

( k)

,

(1)

XN

(k

+

N 2

)

=

X

e N

(k

+N

)

2

2

-

W

kn N

1 8

,

w n st表示

W

2 8

,

wnc st表示

W

3 8

,其具体的数值可

以在 M atlab下运算后得到. x ( 0) , x ( 1) , x ( 2) , …, x ( 7) 表示输入的实数序列 ; X ( 0) , X ( 1) , X ( 2) , …,

X ( 7) 表示经过 FFT运算后的频域序列.

的 SignalComp iler模块将其转换成 VHDL 语言. 再在 QuartusⅡ中 ,对刚才的设计项目进行编译并进行 仿真 ,其仿真波形如图 41由图 4显示的数据可以看出 , QuartusⅡ仿真输出的数据与模型仿真的数据 是完全相符的 ,说明设计无误. 最后将其下载到目标器件中 ,就得到根据用户需要的 FFT处理芯片.

快速傅里叶变换 ( FFT)算法是数字信号处理中最常用的算法之一. 实现 FFT算法的方法有软件 法和硬件法. 软件法实现比较灵活 ,但速度受限 ,因此在实时性要求高的场合多用硬件实现 1但由于 硬件法实现浮点数的运算要分别对阶和尾数进行运算 ,所以浮点运算比整数运算复杂 ,它所需要的硬 件设备也更多. 随着 FPGA 的出现以及 EDA 技术的成熟 ,采用定点运算器以模拟浮点运算来实现数字 信号处理的方法已经显示出巨大的潜力 [ 1 ]. 1 FFT算法原理