ModelSim-Altera使用方法.pdf[1]

modelsim_altera破解

做FPGA用到ModelSim仿真,QuartusII 13.0调用发现"unable

to check out a license .run the modelsim licensing

wizard from start.programs menu to dignose problem"

的问题,才发现Quarttus13.0破解后还要再破解Modelsim,方法如下:

1.下载破解文件,自行百度

2.复制破解文件中的MentorKG.exe和patch_dll.bat到Modelsim安

装目录的win32aloem文件夹下

3.运行patch_dll.bat,将生成的LICENSE.TXT文件另存为

LICENSE.dat并置于此文件夹下

4.在环境变量的用户环境变量一栏新建环境变量MGLS_LICENSE_FILE、LM_LICENSE_FILE指向LICENSE.dat

关于环境变量的配置:

右击计算机--》点属性--》左侧点‘高级系统设置’ --》点‘高级’

选项最下方的‘环境变量’

--》在‘系统环境变量’下方点‘新建’--》输入环境变量名和路径

即可,如下:

变量名:LM_LICENSE_FILE:

路径:自己的安装路径\win32aloem\LICENSE.dat

变量名:MGLS_LICENSE_FILE:

路径:自己的安装路径\win32aloem\LICENSE.dat。

在quartusII中用modelsim-altera仿真

在quartusII中用modelsim_altera做功能仿真1.设置modelsim_altera的执行路径(即其安装路径中的可执行文件的路径)(1)Tool→Options(2)打开如下图:(3)选择general →EDA Tool Options,在右侧的窗口中选择Modelsim_Altera,在Location of Executable中单击,用浏览的方式找到该软件的安装路径中的可执行文件路径,单击确定。

到此仿真软件的设置基本完成了。

2.项目仿真当我们建立一个新的项目时是需要对其中代码进行仿真的,整个过程需要三步:2.1首先,要预先设置仿真软件;下面介绍如何预设仿真软件。

1.Assignments→Settings…2.打开如下界面3选择“Simulation”,右侧设置按上图设置。

2.2其次,仿真之前需要编写测试平台,测试平台有两种的方法:●直接建立XX.v文件●在quartusII中自动生成测试平台模板文件,文件为XX.vt文件下面介绍如何自动生成测试平台模板文件。

1.Processing→Start→Start Test Bench Template Writer注意:要生成testbench模板的前提条件是为项目选择预用的仿真软件,然后模块必须编译成功。

Testbench模板生成后的默认路径为:项目目录\simulation\modelsim\项目名.vt(因为刚才在预设置仿真软件时的“Output Directory”选择的是默认的值simulation\modelsim)。

2.对于自动生成的测试平台模版需要打开修改测试激励信号,这里不做介绍,很简单的。

2.3改写完后要在项目里添加测试平台文件到项目里。

1.Assignments→Settings…2.在打开界面做如下操作:(1)选择“Compile test bench”,然后单击“Test Benches…”(2)打开下面的窗口(3)单击“New”打开下面的窗口,且按图中填写相关信息这个窗口是用来输入testbench的资料和选择testbench的路径的。

ModelSim-Altera使用方法.pdf[1]

![ModelSim-Altera使用方法.pdf[1]](https://img.taocdn.com/s3/m/2731177ba26925c52cc5bf90.png)

平台软件:ModelSim-Altera 6.5e (Quartus II 10.0) Starter Edition 内容1 设计流程使用ModelSim仿真的基本流程为:图1.1 使用ModelSim仿真的基本流程2 开始2.1 新建工程打开ModelSim后,其画面如图2.1所示。

图2.1 ModelSim画面1. 选择File>New>Preject创建一个新工程。

打开的Create Project对话框窗口,可以指定工程的名称、路径和缺省库名称。

一般情况下,设定Default Library Name 为work。

指定的名称用于创建一个位于工程文件夹内的工作库子文件夹。

该对话框如图2. 2所示,此外还允许通过选择.ini文件来映射库设置,或者将其直接拷贝至工程中。

图2.2 创建工程的对话框2. 按照图2.3所示,设置Project Name为LED_FLOW,Project Location为D: /led_flow。

图2.3 输入工程信息当单击OK按钮后,在主体窗口的下方将出现Project标签,如图2.4所示。

图2.4 Project标签3. 之后,将出现Add Items to the Project的对话框,如图2.5所示。

图2.5 在工程中,添加新项目2.2 在工程中,添加新项目在Add Items to the Project对话框中,包括以下选项:∙Create New File——使用源文件编辑器创建一个新的Verilog、VHDL、TCL 或文本文件∙Add Existing File——添加一个已存在的文件∙Create Simulation——创建指定源文件和仿真选项的仿真配置∙Create New Folder——创建一个新的组织文件夹1. 单击Create New File。

打开图2.6所示窗口。

图2.6 创建工程文件夹2. 输入文件名称:LED_FLOW,然后选择文件类型为Verilog。

在Modelsim中加入altera的仿真库

虽然这是个老话题了,但总会有刚入门的朋友不知道的。我在这里还是讲讲吧!问什么要这样做?

1、Quartus不支持Testbench

2、调用了megafunction或者lpm库之类的Altera的函数

3、时序仿真要在Modelsim下做仿真,

总会遇到上面这几个问题,因为需要在Modelsim中加入Quartus的仿真库。 Altera公司推荐的具体的做法是: 1、在Modelsim中,File->Change Directory,将工作目录改变到想要存放仿真库的地方,然后点击OK。将来产生的一大堆仿真库要用的文件就存放在这里。 2、Design->Create a New Library,建立一个新的库:Altera,点击OK。 3、Compile ..quartusedasim_lib下面的两个文件,220model.v和altera_mf.v,记得编译的时候上面的library一定是Altera。这样三步以后,就完成了在Modelsim中添加Altera的库!实际中,这样做不方便。我是这样做的。把220model.v和altera_mf.v拷贝到你要编译的文件所在的文件夹里。先编译这两个文件,等于是把Altera的器件加到了work这个library里。然后再在library下编译你要用的文件就可以了。这样方便些。

4 start compilation... ARTUS中调用Modelsim,verilog下,步骤如下,并作一说明。

1 将modelsim启动路径(如:c:modelsimmodeltechwin32;)加入到环境变量path中。

2 在quartus中建立project,并产生所用的testbench

在ModelSimSE中添加ALTERA仿真库的详细步骤

ModelSim学习笔记(二)在ModelSimSE中添加ALTERA仿真库的详细步骤黄俊April 2007以前用的是LATTICE的,ispLEVER有自带了一个OEM版的ModelSim。

要仿真时,不需要添加库,用起来比较方便,自己有点懒,所以就一直凑合着用。

现在转向用ALTERA 了,ALTERA也有OEM版的ModelSim,也不用添加库。

后来听说ModelSim SE的功能更强大,速度更快,所以就决定把ModelSim SE好好摸索一下,再多学习一点关于TestBench 技巧方面的知识。

我的学习资料主要是ModelSim SE自带的教程、ALTERA提供的资料以及edacn上面ModelSim专栏由网友们上传的资料。

因为是初学,加上看到英文资料一大堆,烦都烦死,而有些中文文档可能是有些步骤没有讲清楚,我实际按照文档上面说的一步一步做下来也老是完成不了,花了不少时间。

我于是就想自己摸清楚后,把步骤截图下来,整理清楚,做成笔记。

一方面加深自己的认识,另一方面对初学者也许会有些许用处。

我近期计划陆续整理出以下几个方面的学习笔记:初学ModelSimSE时被迷糊了几天的若干概念在ModelSimSE中添加ALTERA仿真库的详细步骤用ModelSimSE进行功能仿真和时序仿真的方法(ALTERA篇)ModelSimSE中常用到的几个命令及DO文件的学习笔记近来学到的几招TestBench的技巧MSN: paulhuang_sz@E-mail: huangjun5927@Blog: /index.php/2599在ModelSimSE中添加ALTERA仿真库的详细步骤装仿真库前要先了解几个概念1、装ModelSim之前,要先装QuartusII。

安装好QuartusII后,在其安装目录下…\quartus\eda\sim_lib里面存放了所有的仿真原型文件(simulation modelfiles)。

如何在modelsim中添加altera的仿真库

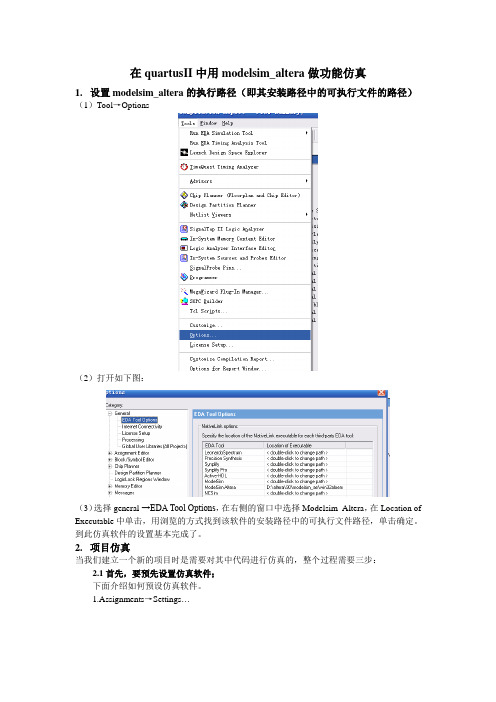

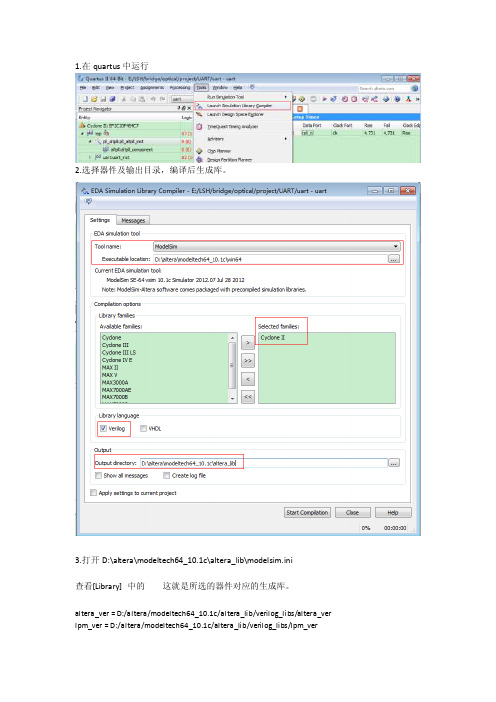

1.在quartus中运行2.选择器件及输出目录,编译后生成库。

3.打开D:\altera\modeltech64_10.1c\altera_lib\modelsim.ini查看[Library] 中的这就是所选的器件对应的生成库。

altera_ver = D:/altera/modeltech64_10.1c/altera_lib/verilog_libs/altera_ver lpm_ver = D:/altera/modeltech64_10.1c/altera_lib/verilog_libs/lpm_versgate_ver = D:/altera/modeltech64_10.1c/altera_lib/verilog_libs/sgate_veraltera_mf_ver = D:/altera/modeltech64_10.1c/altera_lib/verilog_libs/altera_mf_veraltera_lnsim_ver = D:/altera/modeltech64_10.1c/altera_lib/verilog_libs/altera_lnsim_vermaxii_ver = D:/altera/modeltech64_10.1c/altera_lib/verilog_libs/maxii_vercycloneii_ver = D:/altera/modeltech64_10.1c/altera_lib/verilog_libs/cycloneii_ver可以复制这些项存到D:\altera\modeltech64_10.1c\modelsim.ini即根目录下的modelsim.ini中的[Library] 注意修改只读属性; Altera library add by Sylaraltera_ver = $MODEL_TECH/../altera_lib/verilog_libs/altera_verlpm_ver = $MODEL_TECH/../altera_lib/verilog_libs/lpm_versgate_ver = $MODEL_TECH/../altera_lib/verilog_libs/sgate_veraltera_mf_ver = $MODEL_TECH/../altera_lib/verilog_libs/altera_mf_veraltera_lnsim_ver = $MODEL_TECH/../altera_lib/verilog_libs/altera_lnsim_vermaxii_ver = $MODEL_TECH/../altera_lib/verilog_libs/maxii_vercycloneii_ver = $MODEL_TECH/../altera_lib/verilog_libs/cycloneii_ver或者如何在modelsim中添加altera的仿真库上一篇/ 下一篇2009-07-31 14:36:17查看( 6137 ) / 评论( 1 ) / 评分( 0 / 0 )呵呵,这个问题纠结了我两天了,刚才又试了一下就通过了,其实网上的资料说的很清楚的,但是操作起来还真的容易失误,所以说不会的时候觉得怎么这么难搞,会了之后、发现怎么这么简单!首先为什么要在modelsim中加仿真库呢?我的理解是这样的,modelsim仿真功能强大,但是没有跟具体的器件相结合所以不能够进行时序仿真和后仿真。

ModelSim的使用(Altera官网)

About Using the ModelSim Software with theQuartus II SoftwareAuthor: Kerwin. XieModelSim-Altera Design Flow(For Altera Version)1.Set up the ModelSim-Altera working environment2.Set up a project with the ModelSim-Altera software3.Perform a functional simulation with the ModelSim-Altera software4.Perform a timing simulation with the ModelSim-Altera softwareModelSim PE/SE Design Flow(For PE/SE Version)1.Set up the ModelSim working environment2.Set up a project with the ModelSim softwarepile libraries and design files with the ModelSim software4.Perform a functional simulation with the ModelSim software5.Perform a timing simulation with the ModelSim software目录MODELSIM-ALTERA版本仿真流程 (3)1、建立M ODEL S IM-A LTERA工作环境 (3)2、用M ODEL S IM-A LTERA建立工程 (3)3、用M ODEL S IM-A LTERA执行功能仿真 (3)4、用M ODEL S IM-A LTERA执行时序仿真 (4)MODELSIM-PE/SE版本仿真流程 (6)P ERFORMING A F UNCTIONAL S IMULATION WITH THE M ODEL S IM S OFTWARE (6)P ERFORMING A T IMING S IMULATION WITH THE M ODEL S IM S OFTWARE (7)相关知识链接 (9)M ODEL S IM P RECOMPILED L IBRARIES(预编译库) (9)A LTERA F UNCTIONAL S IMULATION L IBRARIES(功能仿真库) (12)A LTERA P OST-F IT L IBRARIES(后适配库) (20)P ERFORMING P OWER A NALYSIS WITH THE Q UARTUS II S OFTWARE AND O THER EDA T OOLS (30)使用QUARTUSII自动运行MODELSIM仿真 (37)1、配置N ATIVE L INK (37)2、运行仿真 (39)3、产生T ESTBENCH (40)相关链接:ModelSim-Altera软件支持谢银坤Kerwin Xie2010年1月20日ModelSim-Altera版本仿真流程1、建立ModelSim-Altera工作环境1.1版本说明ModelSim-Altera(OEM)version 6.4aQuartusII version 9.0该ModelSim版本支持所有QuartusII支持的Altera器件。

modelsim使用教程

modelsim使用教程ModelSim是一款常用的硬件描述语言(HDL)仿真工具,本教程将向您介绍如何使用ModelSim进行仿真。

步骤1:安装ModelSim首先,您需要下载和安装ModelSim软件。

在您的电脑上找到安装程序并按照提示进行安装。

步骤2:创建工程打开ModelSim软件,点击"File"菜单中的"New",然后选择"Project"。

在弹出的对话框中,选择工程的存储位置,并为工程命名。

点击"OK"完成工程创建。

步骤3:添加设计文件在ModelSim的工程窗口中,右键点击"Design"文件夹,选择"Add Existing File"。

然后选择包含您的设计文件的目录,并将其添加到工程中。

步骤4:配置仿真设置在工程窗口中,右键点击"Design"文件夹,选择"Properties"。

在弹出的对话框中,选择"Simulation"选项卡。

在"Top level entity"字段中,选择您的设计的顶层模块。

点击"Apply"和"OK"保存设置。

步骤5:运行仿真在ModelSim的工具栏中,找到"Simulate"按钮,点击并选择"Start Simulation"。

这将打开仿真窗口。

在仿真窗口中,您可以使用不同的命令来控制和观察设计的行为。

步骤6:查看仿真结果您可以在仿真窗口中查看信号波形、调试设计并分析仿真结果。

在仿真窗口的菜单栏中,您可以找到一些常用的查看和分析工具,如波形浏览器、信号分析器等。

步骤7:结束仿真当您完成仿真时,可以选择在仿真窗口的菜单栏中找到"Simulate"按钮,并选择"End Simulation"以结束仿真。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

平台

软件:ModelSim-Altera 6.5e (Quartus II 10.0) Starter Edition 内容

1 设计流程

使用ModelSim仿真的基本流程为:

图1.1 使用ModelSim仿真的基本流程

2 开始

2.1 新建工程

打开ModelSim后,其画面如图2.1所示。

图2.1 ModelSim画面

1. 选择File>New>Preject创建一个新工程。

打开的Create Project对话框窗口,可以指定工程的名称、路径和缺省库名称。

一般情况下,设定Default Library Name 为work。

指定的名称用于创建一个位于工程文件夹内的工作库子文件夹。

该对话框如图

2. 2所示,此外还允许通过选择.ini文件来映射库设置,或者将其直接拷贝至工程中。

图2.2 创建工程的对话框

2. 按照图2.3所示,设置Project Name为LED_FLOW,Project Location为D: /led_flow。

图2.3 输入工程信息

当单击OK按钮后,在主体窗口的下方将出现Project标签,如图2.4所示。

图2.4 Project标签

3. 之后,将出现Add Items to the Project的对话框,如图2.5所示。

图2.5 在工程中,添加新项目

2.2 在工程中,添加新项目

在Add Items to the Project对话框中,包括以下选项:

∙Create New File——使用源文件编辑器创建一个新的Verilog、VHDL、TCL 或文本文件

∙Add Existing File——添加一个已存在的文件

∙Create Simulation——创建指定源文件和仿真选项的仿真配置

∙Create New Folder——创建一个新的组织文件夹

1. 单击Create New File。

打开图

2.6所示窗口。

图2.6 创建工程文件夹

2. 输入文件名称:LED_FLOW,然后选择文件类型为Verilog。

图2.7 输入工程文件信息

3. 单击OK,关闭本对话框。

新的工程文件将会在工程窗口显示。

单击Close,以关闭A dd Items to the Project。

图2.8 新的设计文件LED_FLOW.v

4. 双击打开LED_FLOW.v文件(注意:若是Verilog文件已经关联了其他的文本编辑器,则双击后在关联的文本编辑器中打开)。

图2.9 LED_FLOW代码输入窗口

在LED_FLOW.v输入下面的测试平台代码:

`timescale 1ns/1ns

module LED_FLOW;

reg CLOCK_50M;

reg RST_N;

wire [9:0] LED;

led led_inst

(

.clk_50M(CLOCK_50M),

.reset_n(RST_n),

.led(LED)

);

initial

begin

CLOCK_50M = 0;

while (1)

#10 CLOCK_50M = ~CLOCK_50M;

end

initial

begin

RST_N = 0;

while (1)

#10 RST_N = 1;

end

initial

begin

$display($time,"CLOCK_50M=%d RST_N=%d LED =%d", CLOCK_50M, RST_N, LED);

end

endmodule

录入完代码后,单击Save。

图2.10 输入testbench代码

5. 选择File>New>Source>Verilog,创建新的Verilog文件,如图2.11所示。

图2.11 创建新的Verilog文件

6. 录入下面的代码,录入画面如图2.12 所示。

`timescale 1ns/1ns

module led(

input clk_50M, // System clock 50MHz

input reset_n, // System reset

output reg [9:0] led // led

);

reg [13:0] counter = 0;

reg [3:0] state = 0;

always @ (posedge clk_50M, negedge reset_n) if (!reset_n)

counter <= 0;

else

counter <= counter + 1'b1;

always @ (posedge counter[13])

if (!reset_n)

state <= 0;

else

begin

if (state == 4'b1001)

state <= 0;

else

state <= state + 1'b1;

end

always @ (posedge clk_50M, negedge reset_n) if (!reset_n)

led <= 0;

else

begin

case (state)

4'b0000: led <= 10'b00000_00001;

4'b0001: led <= 10'b00000_00010;

4'b0010: led <= 10'b00000_00100;

4'b0011: led <= 10'b00000_01000;

4'b0100: led <= 10'b00000_10000;

4'b0101: led <= 10'b00001_00000;

4'b0110: led <= 10'b00010_00000;

4'b0111: led <= 10'b00100_00000;

4'b1000: led <= 10'b01000_00000;

4'b1001: led <= 10'b10000_00000;

default: led <= 10'b00000_00001;

endcase

end

endmodule

图2.12 录入新文件

7. 选择File>Save,输入文件名:led.v,单击Save,如图2.13所示。

图2.13 保存led.v

8. 选择Project>Add to Project>Existing File,如图2.14所示。

图2.14添加文件到工程中

9. 单击Browse,选择led.v,如图2.15 所示。

图2.15 选择待加入工程的文件

10. 单击打开,在Add file to the project窗口,单击OK。

2.3 编译文件

在Project标签下的Status列的问号,表示文件尚未编译进工程,或者在最后编译前,源文件有所改动。

欲编译文件,选择Compile<Compile ALL,或者右击Project标签,选择Compile>Compile All。

1. 倘若此处没有错误,编译成功的消息,就会在Transcript窗口如图

2.6所示。

图2.16 编译成功

3 仿真工程

3.1 开始仿真

1. 单击Library图标,选择work,单击+以展开选项,然后选择LED_FLOW。

单击右键,选择编译,如图3.1所示。

图3.1 单击Simulate

2. 单击Simulate,到达图

3.2所示画面。

图3.2 仿真窗口

4. 在图3.2中,单击LED_FLOW,单击右键,然后选择Add>To Wave>All Item s in region,然后单击左键。

出现图3.3所示画面。

图3.3 Add To Wave

3.2 仿真设置

1. 完成上述最后一步后,波形窗口出现。

图3.4 波形窗口

2. 在Run Length列输入仿真时间长度为10ms,如图

3.5所示。

图3.5 设置Run Length

3. 单击Run按钮,如图3.6所示。

图3.6 运行仿真

4. 运行若干秒后,将会如图3.9所示的仿真结果。

图3.7 显示仿真结果

5. 连续单击Zoom Out图标,可查看仿真的完整波形,如图3.8所示。

图3.8 波形窗口

6. 单击鼠标所指的+,展开LED_FLOW的波形,如图3.9所示。

图3.9 展开波形

通过放大/缩小波形,可以观察到LED的值在保持变化,即LED的时序效果。

若将其移植到Quartus II中,适当配置后,经过综合、时序分析、引脚分配、配置及下载等,即可实现跑马灯的效果。