基于FPGA的数码管的动态显示

基于FPGA的8段数码管动态显示IP核设计

基于FPGA的8段数码管动态显示IP核设计一、引言在数字系统设计中,数码管广泛用于显示数字和字符。

而使用可编程逻辑器件FPGA(Field Programmable Gate Array)来实现数码管的动态显示,可以灵活地实现不同的显示模式和动画效果。

本文将详细介绍如何设计一个基于FPGA的8段数码管动态显示IP核。

二、设计思路本设计的目标是实现一个可配置的8位数码管显示IP核,支持不同的显示模式和动画效果。

核心思路是使用时分复用技术,通过逐位扫描的方式显示不同的数字。

具体来说,设计主要包括以下几个部分:1.数据存储器:用于存储要显示的数字的编码值。

可以使用块RAM或寄存器数组来实现,存储器的大小足够存储所有要显示的数字。

2.数据选择器:根据当前显示的位数,从数据存储器中选择对应的数字编码值。

可以使用多路选择器来实现。

3.数码管驱动器:将选中的数字编码值转换成对应的数码管控制信号。

可以使用编码器和驱动逻辑来实现。

4.位选择器:控制数码管的位选信号,实现逐位扫描的显示效果。

可以使用计数器和位选择逻辑来实现。

基于以上思路,我们可以设计一个简单的状态机来实现整个显示过程。

状态机的状态包括显示位选择和显示数据选择两部分,每个状态对应一个显示周期。

通过控制状态机的时钟信号,可以实现数码管的动态显示。

三、具体实现1.数据存储器数据存储器可以使用FPGA中的块RAM或寄存器来实现。

以块RAM为例,可以将数字编码值作为地址输入,将对应的显示数据作为数据输入,通过写操作将数据写入块RAM。

读数据时,将当前显示位数作为地址输入,就可以得到对应的数字编码值。

2.数据选择器数据选择器可以使用多路选择器来实现。

将数据存储器的输出作为多路选择器的数据输入,将当前显示位数作为选择信号,就可以选择对应的数字编码值。

3.数码管驱动器数码管驱动器可以使用编码器和驱动逻辑来实现。

编码器将数字编码值转换成对应的数码管控制信号,驱动逻辑将控制信号输出到对应的数码管。

EDA实验指导 基于FPGA的动态扫描电路设计new

FPGA实验指导及记录实验三基于FPGA的数码管动态扫描电路设计1.实验目的:(1)掌握FPGA工作的基本原理、FPGA硬件平台的使用;(2)熟悉7段数码管显示译码电路的设计。

(3)掌握数码管动态扫描显示原理及动态扫描电路的设计。

2.实验任务:利用FPGA硬件平台上的6位数码管动态显示计数器输出数据。

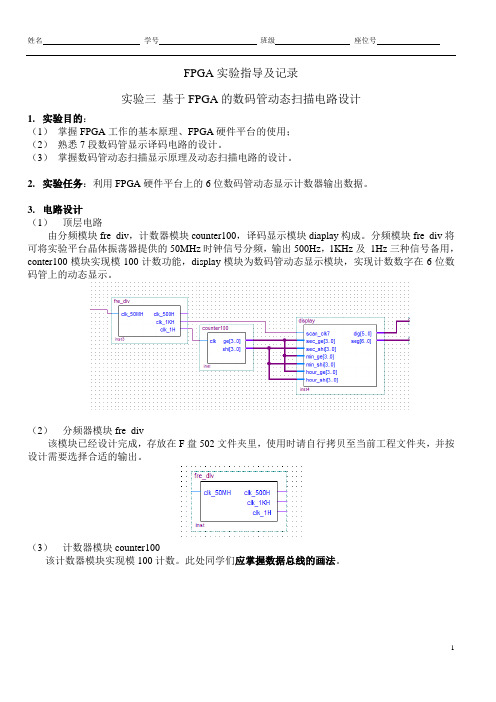

3.电路设计(1)顶层电路由分频模块fre_div,计数器模块counter100,译码显示模块diaplay构成。

分频模块fre_div将可将实验平台晶体振荡器提供的50MHz时钟信号分频,输出500Hz,1KHz及1Hz三种信号备用,conter100模块实现模100计数功能,display模块为数码管动态显示模块,实现计数数字在6位数码管上的动态显示。

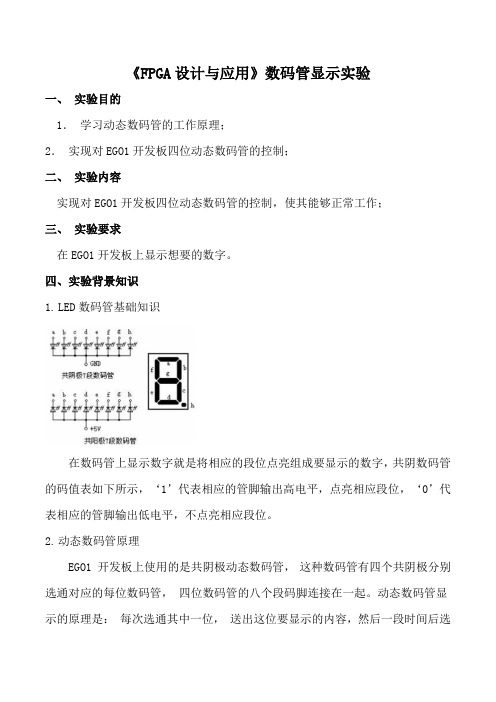

(2)分频器模块fre_div该模块已经设计完成,存放在F盘502文件夹里,使用时请自行拷贝至当前工程文件夹,并按设计需要选择合适的输出。

(3)计数器模块counter100该计数器模块实现模100计数。

此处同学们应掌握数据总线的画法。

(4)译码显示模块display该模块由counter6模块,dig_select模块,seg_select模块以及decoder模块构成,请同学们自行完成该模块总体设计,当display模块的输入信号scanclk频率为1KHz时,数码管扫描周期为36ms,每次扫描每位数码管显示时长6ms。

各子模块设计思路如下。

a)counter6模块该模块需使用74390设计一个模6的计数器。

请在空白处做预设计,画出电路图。

b)dig_select模块该模块用于选择6位数码管中的某一位显示相应字形。

74138为3-8译码器,功能表见附录。

c)decoder模块可将4位8421BCD码译为七段码,驱动数码管以十进制数形式显示数字。

7448为共阴极数码管译码器,功能表见附录。

d)seg_select模块该模块功能是从6组4bit信号中选择一组作输出。

基于FPGA的8段数码管动态显示IP核设计

基于FPGA的8段数码管动态显示IP核设计

引言数码管可显示简单的字符和数字,由于其价格低廉、性能稳定、显示清晰、亮度高、使用电压低、寿命长,在工业生产、交通运输、仪器仪表及家用电器等场合得到广泛应用。

然而,开发基于NiosⅡ的嵌入式系统时,Builder 开发工具中没有提供现成的数码管显示IP 核,这使设计者工作量增加。

这里把数码管控制器设计为一个共阴极(或共阳极)7 段数码管动态显示IP 核,并给出此核的一个参考驱动程序。

在系统设计中,可根据实际需求,把此核直接例化成1~8 个共阴极(或共阳极)数码管显示控制器,控制1~8 个共阴极(或共阳极)数码管工作,实现IP 核重用,减少电子设计者的工作量,从而提高设

计效率。

2 LED 数码管结构及驱动显示方式根据发光二极管的个数可将数码管分成7 段数码管和8 段数码管,8 段数码管比7 段数码管多一个用于显示小数点的发光二极管;根据内部连接形式可将数码管分成共阳数码管与共阴数码管,图1 为数码管的外形及其内部结构图。

常用的数码管显示驱动方式有静态驱动与动态驱动两种,静态驱动方式的

主要特点是,每个数码管都有相互独立的数据线,并且所有的数码管被同时点亮;而动态驱动方式则是所有数码管共用一组数据线,数码管依次被点亮,因此,动态驱动显示方式每个数码管都要有一个点亮控制输入端口。

为节省

I/O 端口,此设计采用动态显示方式,所有数码管动态显示控制时序,全部由FPGA 器件产生。

3 数码管动态显示IP 核设计根据数码管动态显示方式的工作原理,可把数码管动态显示控制器设计成IP 核,包括任务逻辑设计、寄存器文件设计和Avalon 接口设计3 部分。

3.1 任务逻辑设计任务逻辑实现IP 核的基本功能,。

《FPGA设计与应用》数码管显示实验

《FPGA设计与应用》数码管显示实验一、实验目的1.学习动态数码管的工作原理;2.实现对EGO1开发板四位动态数码管的控制;二、实验内容实现对EGO1开发板四位动态数码管的控制,使其能够正常工作;三、实验要求在EGO1开发板上显示想要的数字。

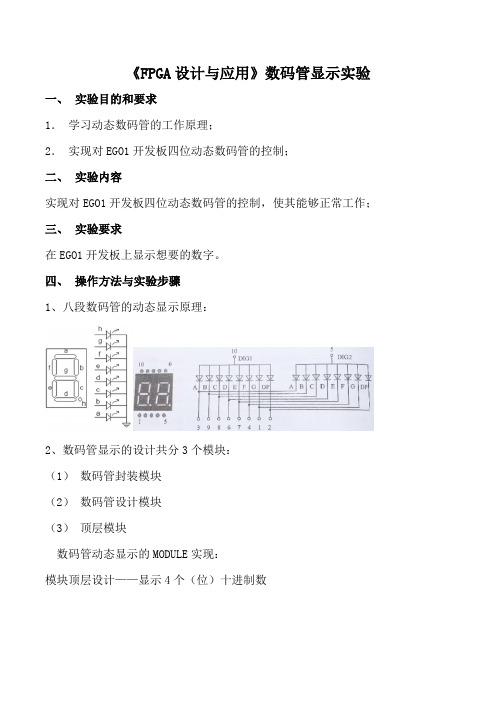

四、实验背景知识1.LED数码管基础知识在数码管上显示数字就是将相应的段位点亮组成要显示的数字,共阴数码管的码值表如下所示,‘1’代表相应的管脚输出高电平,点亮相应段位,‘0’代表相应的管脚输出低电平,不点亮相应段位。

2.动态数码管原理EGO1 开发板上使用的是共阴极动态数码管,这种数码管有四个共阴极分别选通对应的每位数码管,四位数码管的八个段码脚连接在一起。

动态数码管显示的原理是:每次选通其中一位,送出这位要显示的内容,然后一段时间后选通下一位送出对应数据,4 个数码管这样依次选通并送出相应的数据,结束后再重复进行。

这样只要选通时间选取的合适,由于人眼的视觉暂留,数码管看起来就是连续显示的。

五、实验方案及实现1、数码管显示的设计共分3个模块:(1)数码管封装模块(2)数码管设计模块(3)顶层模块数码管封装模块代码:module smg_ip_model(clk,data,sm_wei,sm_duan);input clk;input [15:0] data;output [3:0] sm_wei;output [7:0] sm_duan;integer clk_cnt;reg clk_400Hz;always @(posedge clk)if(clk_cnt==32'd100000)begin clk_cnt <= 1'b0; clk_400Hz <= ~clk_400Hz;endelseclk_cnt <= clk_cnt + 1'b1;reg [3:0]wei_ctrl=4'b1110;always @(posedge clk_400Hz)wei_ctrl <= {wei_ctrl[2:0],wei_ctrl[3]}; reg [3:0]duan_ctrl;always @(wei_ctrl)case(wei_ctrl)4'b1110:duan_ctrl=data[3:0];4'b1101:duan_ctrl=data[7:4];4'b1011:duan_ctrl=data[11:8];4'b0111:duan_ctrl=data[15:12];default:duan_ctrl=4'hf;endcasereg [7:0]duan;always @(duan_ctrl)case(duan_ctrl)4'h0:duan=8'b0011_1111;4'h1:duan=8'b0000_0110;4'h2:duan=8'b0101_1011;4'h3:duan=8'b0100_1111;4'h4:duan=8'b0110_0110;4'h5:duan=8'b0110_1101;4'h6:duan=8'b0111_1101;4'h7:duan=8'b0000_0111;4'h8:duan=8'b0111_1111;4'h9:duan=8'b0110_1111;4'ha:duan=8'b0111_0111;4'hb:duan=8'b0111_1100;4'hc:duan=8'b0011_1001;4'hd:duan=8'b0101_1110;4'he:duan=8'b0111_1000;4'hf:duan=8'b0111_0001;数码管设计模块module test(clk,data);input clk;output [15:0]data;reg clk_1Hz;integer clk_1Hz_cnt;always @(posedge clk)if(clk_1Hz_cnt==32'd2*******-1)begin clk_1Hz_cnt <= 1'b0; clk_1Hz <= ~clk_1Hz;end elseclk_1Hz_cnt <= clk_1Hz_cnt + 1'b1;reg [39:0]disp=40'h1234567890;reg [15:0]data;always @(posedge clk_1Hz)begindisp <= {disp[35:0],disp[39:36]};data <= disp[39:24];endEndmodule顶层模块module smg_ip(clk,sm_wei,sm_duan);input clk;output [3:0]sm_wei;output [7:0]sm_duan;wire [15:0]data;wire [3:0]sm_wei;wire [7:0]sm_duan;test U0 (.clk(clk),.data(data));smg_ip_model U1(.clk(clk),.data(data),.sm_wei(sm_wei),.sm_duan(sm_duan)); endmodule六、实验结果Vivado仿真:上实验板实操:七、实验心得次实验主要学习了利用vivado软件实现数码管的显示,利用编程来实现,并且还对动态数码管的原理进行了一定的学习,包括上次实验学习到的模块化设计,方便程序的调试,程序运行过程中并不顺利,一直没有创建出pin文件夹,最后还是在老师的帮助下完成了pin文件夹的创建,导入到板子后完成了本次实验的设计。

《FPGA设计与应用》数码管显示实验一

《FPGA设计与应用》数码管显示实验一、实验目的和要求

1.学习动态数码管的工作原理;

2.实现对EGO1开发板四位动态数码管的控制;

二、实验内容

实现对EGO1开发板四位动态数码管的控制,使其能够正常工作;

三、实验要求

在EGO1开发板上显示想要的数字。

四、操作方法与实验步骤

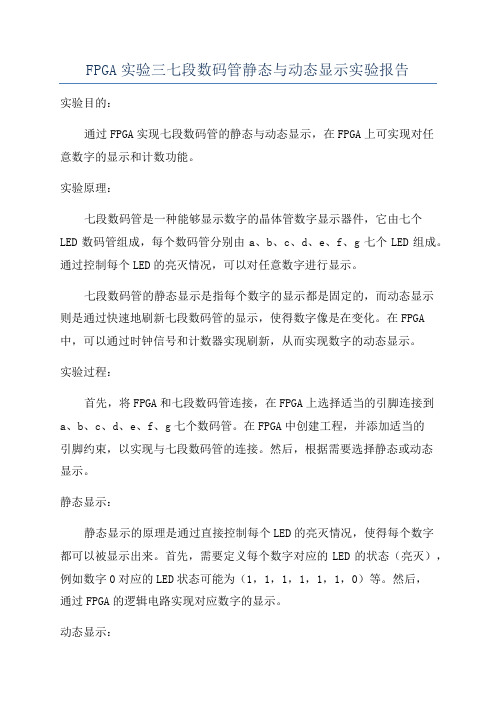

1、八段数码管的动态显示原理:

2、数码管显示的设计共分3个模块:

(1)数码管封装模块

(2)数码管设计模块

(3)顶层模块

数码管动态显示的MODULE实现:

模块顶层设计——显示4个(位)十进制数

逻辑实现:

确定当前显示的位

确定当前“位”需要显示的“数”:

将“数”翻译成相应的“段码”

仿真测试台代码编写与仿真测试定义时间标尺:

定义测试Moudle

实例化被测Moudle

定义激励信号与响应信号

构造激励信号:

五、实验数据记录和处理实验代码如下:

设计文件:(部分)

仿真文件:

约束文件:

六、实验结果与分析网表结构:

仿真图像:

实物图:

七、讨论和心得

通过这次实验,我学会了数码管的动态显示,每一个数码管共用一套电路,显示时只需控制哪一个数码管进行显示。

虽然一次只能控制单独一个数码管进行显示,但可以快速切换数码管显示,利用人眼的”视觉暂留"来“同步”进行显示。

最后我明白了我们不要遇到一点困难就退缩,就去向老师同学寻求帮助,自己是自己最好的老师,只有我们靠自己的不断修改出正确结果,才会对这个知识掌握的更加透彻。

FPGA实验三七段数码管静态与动态显示实验报告

FPGA实验三七段数码管静态与动态显示实验报告实验目的:通过FPGA实现七段数码管的静态与动态显示,在FPGA上可实现对任意数字的显示和计数功能。

实验原理:七段数码管是一种能够显示数字的晶体管数字显示器件,它由七个LED数码管组成,每个数码管分别由a、b、c、d、e、f、g七个LED组成。

通过控制每个LED的亮灭情况,可以对任意数字进行显示。

七段数码管的静态显示是指每个数字的显示都是固定的,而动态显示则是通过快速地刷新七段数码管的显示,使得数字像是在变化。

在FPGA 中,可以通过时钟信号和计数器实现刷新,从而实现数字的动态显示。

实验过程:首先,将FPGA和七段数码管连接,在FPGA上选择适当的引脚连接到a、b、c、d、e、f、g七个数码管。

在FPGA中创建工程,并添加适当的引脚约束,以实现与七段数码管的连接。

然后,根据需要选择静态或动态显示。

静态显示:静态显示的原理是通过直接控制每个LED的亮灭情况,使得每个数字都可以被显示出来。

首先,需要定义每个数字对应的LED的状态(亮灭),例如数字0对应的LED状态可能为(1,1,1,1,1,1,0)等。

然后,通过FPGA的逻辑电路实现对应数字的显示。

动态显示:动态显示的原理是通过快速地刷新显示,使得数字在若干个数码管中切换,从而造成数字变化的视觉效果。

这里需要使用时钟信号和计数器来控制刷新。

首先,需要设计一个计数器,它的计数范围应该与显示数字的个数相同。

然后,通过时钟信号让计数器开始计数,并根据计数器的值选择对应的数字显示在七段数码管上。

通过控制计数器的计数速度和刷新频率,可以实现数字的动态显示。

实验结果:经过实验,我们成功地实现了七段数码管的静态显示和动态显示。

在静态显示中,我们可以通过FPGA的逻辑电路对七段数码管的每个LED进行控制,从而实现任意数字的显示。

在动态显示中,我们通过时钟信号和计数器实现了刷新功能,使得数字在七段数码管中快速地切换,从而呈现出动态的显示效果。

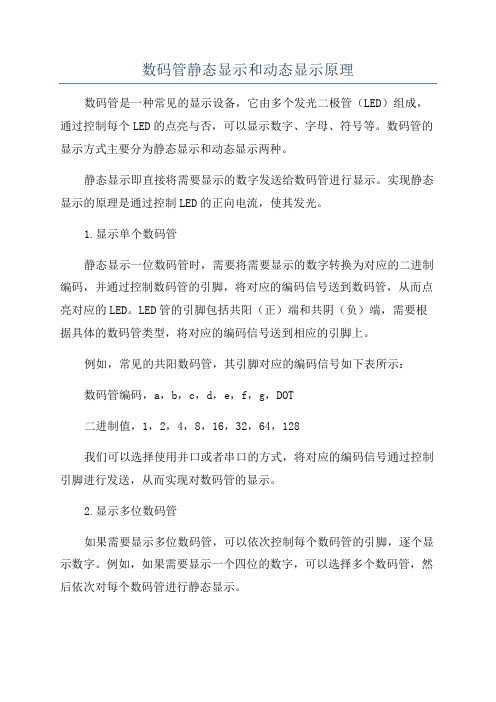

数码管静态显示和动态显示原理

数码管静态显示和动态显示原理数码管是一种常见的显示设备,它由多个发光二极管(LED)组成,通过控制每个LED的点亮与否,可以显示数字、字母、符号等。

数码管的显示方式主要分为静态显示和动态显示两种。

静态显示即直接将需要显示的数字发送给数码管进行显示。

实现静态显示的原理是通过控制LED的正向电流,使其发光。

1.显示单个数码管静态显示一位数码管时,需要将需要显示的数字转换为对应的二进制编码,并通过控制数码管的引脚,将对应的编码信号送到数码管,从而点亮对应的LED。

LED管的引脚包括共阳(正)端和共阴(负)端,需要根据具体的数码管类型,将对应的编码信号送到相应的引脚上。

例如,常见的共阳数码管,其引脚对应的编码信号如下表所示:数码管编码,a,b,c,d,e,f,g,DOT二进制值,1,2,4,8,16,32,64,128我们可以选择使用并口或者串口的方式,将对应的编码信号通过控制引脚进行发送,从而实现对数码管的显示。

2.显示多位数码管如果需要显示多位数码管,可以依次控制每个数码管的引脚,逐个显示数字。

例如,如果需要显示一个四位的数字,可以选择多个数码管,然后依次对每个数码管进行静态显示。

对于多位数码管,如果静态刷新频率较低,人眼会觉得显示闪烁。

因此,在静态显示中,通常需要使用较高的刷新频率,以使得显示效果更加稳定。

动态显示是指通过间歇性显示不同的位数,从而实现连续显示的效果。

动态显示的原理是通过快速的切换不同的位数,让人眼产生连续显示的错觉。

1.时分复用最常见的动态显示原理是时分复用技术,即通过快速的切换不同的位数,以使得数码管在较短的时间内完成多个位数的显示。

例如,对于一个四位数码管的显示,可以快速切换每个数码管的引脚,使得数码管按照一定的频率逐个显示不同的数字。

实现时分复用的关键是要保证刷新频率足够高,以至于人眼无法察觉到刷新的效果。

2.位数切换在时分复用中,需要对每个数码管进行位数的切换,以显示对应的数字。

基于FPGA的8段数码管动态显示IP核设计

基于FPGA的8段数码管动态显示IP核设计概述:数码管是一种常用的显示设备,常用于时钟、计数器、计时器等应用中。

为了简化在FPGA设计中使用数码管的流程,我们可以设计一个IP核来实现动态显示功能。

本文将详细介绍基于FPGA的8段数码管动态显示IP核的设计。

设计目标:设计一个可配置的IP核,支持多种模式的动态显示,包括数字显示、字符显示、滚动显示等。

同时,要保证设计的实时性和稳定性。

设计思路:1.分析需求:根据需求确定显示内容的种类和显示模式。

支持的显示内容包括数字和字符,支持的显示模式包括静态显示、滚动显示和循环显示。

2.硬件设计:设计数码管的驱动电路,将FPGA的输出信号转换为适合数码管的信号。

同时,设计时钟电路,用于控制数码管的刷新频率。

3.状态机设计:设计一个简单的状态机,用于控制数码管的显示内容和显示模式。

根据不同的状态,切换不同的显示内容和显示模式。

4.编码器设计:根据显示内容的种类,设计相应的编码器来将输入信号转换为适合数码管的显示信号。

对于数字显示,可以使用BCD码或者二进制码来编码;对于字符显示,可以使用ASCII码或者自定义的编码方式。

5.IP核封装:将硬件设计、状态机设计和编码器设计整合到一个IP核中,并添加一个可配置的接口,用于设置显示内容和显示模式。

IP核功能介绍:1.输入接口:包括显示内容的选择和显示模式的选择。

2.输出接口:控制数码管的驱动电路,实现动态显示功能。

3.配置接口:可以通过配置接口来设置显示内容和显示模式,包括数字和字符的选择、显示模式的选择等。

4.显示内容刷新:根据显示模式和显示内容的选择,周期性地刷新显示内容。

应用场景:1.时钟显示:将IP核连接到时钟电路和数码管上,通过配置接口设置显示模式为静态显示,显示内容为当前时间。

2.计数器显示:将IP核连接到计数器和数码管上,通过配置接口设置显示模式为滚动显示,显示内容为计数器的值。

总结:基于FPGA的8段数码管动态显示IP核设计可以简化在FPGA设计中使用数码管的流程,并且提供多种显示模式和显示内容的选择,方便实现各种应用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity seg_70 is

port (

beem : out std_logic;

rst :in std_logic;

clk :in std_logic;

en : out std_logic_vector(7 downto 0);

dataout :out std_logic_vector(7 downto 0)); end seg_70;

architecture arch of seg_70 is

signal cnt_scan:std_logic_vector(15 downto 0); signal data4:std_logic_vector(3 downto 0);

signal dataout_xhdl1:std_logic_vector(7 downto 0); signal en_xhdl:std_logic_vector(7 downto 0);

begin

dataout<=dataout_xhdl1;

en<=en_xhdl;

process(clk,rst)

begin

if(rst='0')then

cnt_scan<=cnt_scan+1;

end if;

end process;

process(cnt_scan(15 downto 0))

begin

case cnt_scan(15 downto 13) is

when"000"=>en_xhdl<="11111110"; when"001"=>en_xhdl<="11111101"; when"010"=>en_xhdl<="11111011"; when"011"=>en_xhdl<="11110111"; when"100"=>en_xhdl<="11101111"; when"101"=>en_xhdl<="11011111"; when"110"=>en_xhdl<="10111111"; when"111"=>en_xhdl<="01111111";

when others=>en_xhdl<="11111110";

end case;

end process;

process(en_xhdl)

begin

case en_xhdl is

when "11111110"=>data4<="0000";

when "11111101"=>data4<="0001";

when "11111011"=>data4<="0010";

when "11110111"=>data4<="0011";

when "11101111"=>data4<="0100";

when "11011111"=>data4<="0101";

when "10111111"=>data4<="0110";

when "01111111"=>data4<="0111";

when others =>data4<="1000";

end case;

end process;

process(data4)

begin

case data4 is

when "0000"=>

dataout_xhdl1<="00000011";

when "0001"=>

dataout_xhdl1<="10011111";

when "0010"=>

dataout_xhdl1<="00100101";

when "0011"=>

dataout_xhdl1<="00001101";

when "0100"=>

dataout_xhdl1<="10011001";

when "0101"=>

dataout_xhdl1<="01001001";

when "0110"=>

dataout_xhdl1<="01000001";

when "0111"=>

dataout_xhdl1<="00011111";

when others =>dataout_xhdl1<="11111101"; end case;

end process;

end arch;。