74LS160计数器

74LS160中文资料

个高电平脉冲,其宽度为 Q0 的高电平部分。

m 在不外加门电路的情况下,可级联成 N 位同步计数器。

对于 54/74LS160,在 CP 出现前,即使 CEP、CET、/MR 发生变化,

/ 电路的功能也不受影响。

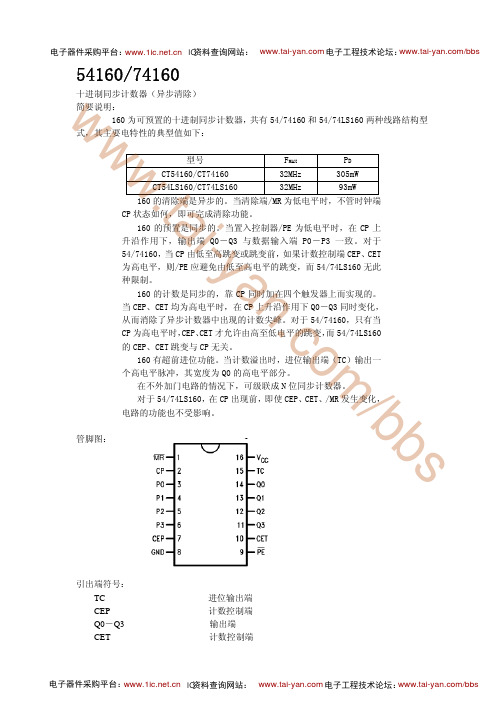

bbs 管脚图:

引出端符号: TC CEP Q0-Q3 CET

进位输出端 计数控制端 输出端 计数控制端

升沿作用下,输出端 Q0-Q3 与数据输入端 P0-P3 一致。对于

i- 54/74160,当 CP 由低至高跳变或跳变前,如果计数控制端 CEP、CET

y 为高电平,则/PE 应避免由低至高电平的跳变,而 54/74LS160 无此

种限制。

a 160 的计数是同步的,靠 CP 同时加在四个触发器上而实现的。

w 型号

FMAX

PD

w CT54160/CT74160

32MHz

305mW

CT54LS160/CT74LS160

32MHz

93mW

.160 的清除端是异步的。当清除端/MR 为低电平时,不管时钟端

tCP 状态如何,即可完成清除功能。

a 160 的预置是同步的。当置入控制器/PE 为低电平时,在 CP 上

80

40

40

40 μA

40

20

VIL 输 入 低电平电 流

CP,CET /PE

P0-P3,CEP,/MR

Vcc=最大

VIL=0.4V

-3.2

-0.8

-1.6

-0.8 mA

-1.6

-0.4

IOS 输出短路电流 IccH 输出高电平时电源电流

Vcc=最大

54 -20 -57 -20 -100 mA

电子技术 集成计数器74LS160

目录一参考资料························( 2 )二工作原理························( 7 )三引脚图························( 8 )四电路图························( 9 )一参考资料(一)74LS4874LS48的管脚排列如图(c)所示。

其真值表如表3所示。

该器件输入信号为BCD码,输出端为a、b、c、d、e、f、g共7线,另有3条控制线LE、RBI、BI/RBO。

LE端为测试端。

在BI端接高电平的条件下,当LE=0时,无论输入端A、B、C、D为何值,a~g输出全为高电平,使7段显示器件显示“8”字型,此功能用于测试器件。

RBI端为灭零输入端。

在LE=1,BI =1条件下,当输入A、B、C、D=0000时,输出a~g全为低电平,可使共阴LED显示器熄灭。

74ls160

十进制同步计数器(异步清除) 简要说明:

160 为可预置的十进制同步计数器,共有 54/74160 和 54/74LS160 两种线路结构型 式,其主要电特性的典型值如下:

型号

FMAX

PD

CT54160/CT74160

32MHz

305mW

CT54LS160/CT74LS160

32MHz

4.5 5 5.5

4.75 5 5.25 4.75 5 5.25

2

2

0.8

0.7

0.8

0.8

-800

-400

16

4

16

8

单位

V V V μA mA

0

25

0

25

MHz

25

25

ns

20

20

P0-P3、CEP

20

20

建立时间tset

ns

/PE

25

20

保持时间tH

0

0

ns

逻辑图

平,其余输入接低电平

74

101

【1】:测试条件中的“最大”和“最小”用推荐工作条件中的相应值。

31

32 mA

32

动态特性(TA=25℃)

参数【2】

测试条件

fmax

tPLH

CP->TC

tPHL

tPLH

CP->Q

Vcc=5V

tPHL

(/PE=H)

CL=15pF

tPLH

CP->Q

RL=400Ω

tPHL

(/PE=L)

管脚图:

引出端符号: TC CEP Q0-Q3 CET

74ls160芯片同步十进制计数器(直接清零)

74LS160 芯片同步十进制计数器(直接清零)·用于快速计数的内部超前进位·用于n 位级联的进位输出·同步可编程序·有置数控制线·二极管箝位输入·直接清零·同步计数本电路是由4 个主从触发器和用作除2计数器及计数周期长度为除5的3位2进制计数器所用的附加选通所组成。

有选通的零复位和置9输入。

为了利用本计数器的最大计数长度(十进制),可将B输入同QA 输出连接,输入计数脉冲可加到输入A上,此时输出就如相应的功能表上所要求的那样。

LS90可以获得对称的十分频计数,办法是将QD 输出接到A输入端,并把输入计数脉冲加到B输入端,在QA输出端处产生对称的十分频方波。

74160引脚图交流波形图:图1 时钟到输出延迟计数图2 主复位输出延迟,主复位时钟频率,脉冲宽度脉冲宽度,和主复位恢复时间状态图VHDL十进制计数器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity count10 isport (clk:in std_logic;f:buffer integer range 0 to 15;cout:out std_logic);end;architecture aa of count10 isbeginprocess(clk)beginif falling_edge(clk) thenif f=9 thenf<=0;cout<='1';elsef<=f+1;end if;elsenull;end if;end process;end;十进制计数器VHDLlibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;--**************实体*****************entity shijinzhi isport(clk: in std_logic;reset: in std_logic;s : out std_logic_vector(5 downto 0);out1: out std_logic_vector(7 downto 0));end shijinzhi;--*****************结构体***********************architecture one of shijinzhi issignal clk_500 : std_logic;--扫描时钟signal clk_1 : std_logic;--1s时钟begin--*************500Hz分频程序********************process(clk)variable cnt1 : integer range 0 to 200;variable cnt2 : integer range 0 to 250;beginif clk'event and clk='1' thenif cnt1=200 thencnt1:=0;if cnt2=250 thencnt2:=0;clk_500<=not clk_500;elsecnt2:=cnt2+1;end if;elsecnt1:=cnt1+1;end if;end if;end process;--***********1Hz分频程序和扫描信号产生********************process(clk_500)variable cnt3 : integer range 0 to 250;beginif clk_500'event and clk_500='1' thenif cnt3=250 thencnt3:=0;clk_1<=not clk_1;elsecnt3:=cnt3+1;end if;end if;end process;--****************************************process(clk_1,reset)variable count1:integer range 0 to 9;beginif reset='0' then count1:=0;elsif clk_1'event and clk_1='1' thenif count1=9 thencount1:=0;elsecount1:=count1+1;end if;end if;if clk_500='1' thencase count1 isWHEN 0 =>s<="111110";out1<="10111111";WHEN 1 =>s<="111110";out1<="10000110";WHEN 2 =>s<="111110";out1<="11011011";WHEN 3 =>s<="111110";out1<="11001111";WHEN 4 =>s<="111110";out1<="11100110";WHEN 5 =>s<="111110";out1<="11101101";WHEN 6 =>s<="111110";out1<="11111101";WHEN 7 =>s<="111110";out1<="10000111";WHEN 8 =>s<="111110";out1<="11111111"; WHEN 9 =>s<="111110";out1<="11101111";when others=>out1<="00000000";end case;end if;end process;end one;。

74ls160十进制计数器原理

74ls160十进制计数器原理

74LS160十进制计数器原理74LS160是一种常用的十进制计数器,它能够实现0至9的循环计数。

它的原理基于二进制计数和锁存器的结合。

该计数器由四个D触发器组成,每个触发器都能存储一个二进制位。

在计数过程中,每当一个触发器的输出从低电平变为高电平时,它会向高位触发器传递一个脉冲信号。

这样,当最低位的触发器计数到9时,它会向高位触发器传递一个脉冲信号,使得高位触发器加1,而最低位触发器归零。

为了实现循环计数,74LS160还包含一个复位功能。

当外部信号复位输入为低电平时,所有触发器的输出都会被清零,计数器重新从0开始计数。

除了计数功能,74LS160还具有一个使能输入。

当使能输入为低电平时,计数器将会被禁用,不再进行计数。

这个功能可以用于控制计数器的启动和停止。

总结起来,74LS160十进制计数器通过二进制计数和锁存器的结合,实现了0至9的循环计数。

它具有复位和使能功能,可以灵活控制计数器的启动和停止。

这使得它在很多应用中都有广泛的使用,如时钟、计时器、频率分析等。

74LS160置数

实

验

报

告

实验项目:74LS160置数

班级:电子111

指导老师:林梅

学生:刘欣琦

学号:

时间:2012年11月1日

74LS160组成进制计数器

●实验内容:

●掌握集成计数器的功能测试及应用。

●用异步清零端设计6进制计数器。

●用同步置0设计7进制计数器。

●仿真实验:

74LS160引脚图

逻辑图

74LS160 七进制计数器

74LS160 十进制计数器

74LS160 2-7计数器

异步74LS160 七进制计数器

异步74LS160 3-6进制计数器

两个74LS160 一百进制计数器

●实验总结:

●任意进制计数器的构成方法,只能用已有的芯片通过外电路的不同连接改变。

●若没法使之跳过(n-m)个状态,就可以得到m进制计数器了。

●其中方法有置零法(复位法)和置数法(置位法)。

●实验体会:

●感觉这些仿真实验挺容易的,比较喜欢。

●还是要好好了解芯片的功能。

●本次实验报告还是没有太完善,不太会。

74LS160计数器

实验九74LS160计数器

一、实验目的:

1. 了解计数器的基本原理。

2. 掌握集成计数器芯片74LS160工作原理及应用。

二、实验原理:

1、74LS160 为可预置的十进制同步计数器,其管脚图如图所示:

RCO 进位输出端

ENP 计数控制端

QA-QD 输出端

ENT 计数控制端

CLK 时钟输入端

CLR 异步清零端(低电平有效)

LOAD 同步并行置入端(低电平有效)

2、74LS160功能表:

三、实验内容:

1、利用同步十进制计数器74LS160接成同步七进制计数器。

设计思路:

列出七进制计数器的真值表:

计数顺序

电路状态等效

十进制

进位

输出

C Q3Q2Q1Q0

0000000

1000110

2001020

3001130

4010040

5010150

6011061

由真值表的逻辑函数式:

Y’= (Q’0Q1Q2Q’3)’

化简得:

Y= (Q1Q2)’

于是得设计电路:

2、试用同步十进制计数器74LS160接成16进制计数器。

设计思路:

74LS160是10进制计数器,要做成16进制计数器,先要做一个比16大的计时器。

这里用两片74LS160接成一个100进制计数器,再通过置0法实现16进制计数。

设计电路:

四、实验分析:

1、通过本实验,让我进一步了解74LS160计数器的基本原理。

基本掌握集成计数器芯片74LS160工作原理及应用。

2、设计电路时,注意思路清晰,结果简单易懂。

电子技术 集成计数器74LS160

-2- / 9

真诚为您提供优质参考资料,若有不当之处,请指正。

表 3 74LS48 七段显示译码器的真值表

(二)74LS00

四 2 输入与非门

(三)集成计数器 74LS160

VCC CO Q0 Q1 Q2 Q3 ET LD

16 15 14 13 12 11 10 9

② 保持:若 Vi2>1/3VCC 且 Vi1<2/3VCC,则 VTR=1,VTH=0,S = R =1, 基本 RS 触发器保持,VO 和 T 状态不变,这时称 555 定时器“保持”。

③ 高触发:若 Vi1>2/3VCC,则 VTH=1,比较器 C1 输出为低电平, 无论 C2 输出何种电平,基本 RS 触发器因 R =0,使 Q =1,经输出反相缓冲 器后,VO=0;T 导通。这时称 555 定时器“高触发”。

-1- / 9

真诚为您提供优质参考资料,若有不当之处,请指正。

一 参考资料 (一)74LS48

74LS48 的管脚排列如图(c)所示。其真值表如表 3 所示。该器件输入信号为 BCD 码, 输出端为 a、b、c、d、e、f、g 共 7 线,另有 3 条控制线 LE、RBI 、 BI/RBO 。 LE 端 为测试端。在 BI 端接高电平的条件下,当 LE =0 时,无论输入端 A、B、C、D 为何值, a~g 输出全为高电平,使 7 段显示器件显示“8”字型,此功能用于测试器件。 RBI 端为 灭零输入端。在 LE =1, BI =1 条件下,当输入 A、B、C、D=0000 时,输出 a~g 全为 低电平,可使共阴 LED 显示器熄灭。但当输入 A、B、C、D 不全为零时,仍能正常译码 输出,使显示器正常显示。 BI 端为消隐输入端。该输入端具有最高级别的控制权,当 该端为低电平时,不管其他输入端为何值,输出端 a~g 均为低电平,这可使共阴显示 器熄灭。另外,该端还有第二功能——灭零信号输出端,记为 RBO 。当该位输入的 A、 B、C、D=0000 且 RBI =0 时,此时 RBO 输出低电平;若该位输入的 A、B、C、D 不等于 零,则 RBO 输出高电平。若将 RBO 与 RBI 配合使用,很容易实现多位数码显示时的灭 零控制。例如对整数部分,将最高位的 RBI 接地,这样当最高位为零时“灭零”,同时该 位 RBO 输出低电平,使下一位的 RBI 为低电平,故也具有“灭零”功能;而对于小数部 分,应将最低位的 RBI 接地,个位的 RBI 端悬空或接高电平,低位的 RBO 接至高位的 RBI 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验九74LS160计数器

一、实验目的:

1. 了解计数器的基本原理。

2. 掌握集成计数器芯片74LS160工作原理及应用。

二、实验原理:

1、74LS160 为可预置的十进制同步计数器,其管脚图如图所示:RCO 进位输出端

ENP 计数控制端

QA-QD 输出端

ENT 计数控制端

CLK 时钟输入端

CLR 异步清零端(低电平有效)

LOAD 同步并行置入端(低电平有效)

2、74LS160功能表:

三、实验内容:

1、利用同步十进制计数器74LS160接成同步七进制计数器。

设计思路:

列出七进制计数器的真值表:

设计该电路要求在6时进位,即在输出为6时给输入端置0。

由真值表的逻辑函数式:

Y’= (Q’0Q1Q2Q’3)’

化简得:

Y= (Q1Q2)’

于是得设计电路:

2、试用同步十进制计数器74LS160接成16进制计数器。

设计思路:

74LS160是10进制计数器,要做成16进制计数器,先要做一个比16大的计时器。

这里用两片74LS160接成一个100进制计数器,再通过置0法实现16进制计数。

设计电路:

四、实验分析:

1、通过本实验,让我进一步了解74LS160计数器的基本原理。

基本掌握集成计数器芯片74LS160工作原理及应用。

2、设计电路时,注意思路清晰,结果简单易懂。