LSE_一种处理器体系结构软件仿真器开发工具

XilinxISE软件功能简介与IPCore(IP核)

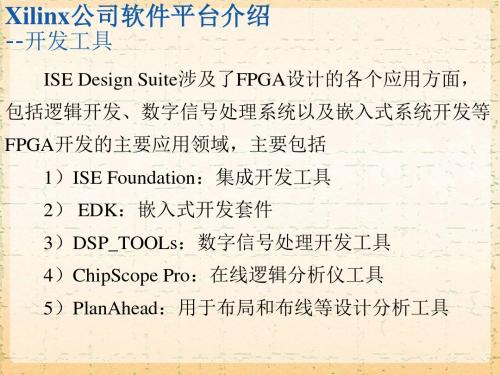

Xilinx ISE软件功能简介与IP Core(IP核)1 Xilinx ISE软件简要介绍Xilinx是全球领先的可编程逻辑完整解决方案的供应商,研发、制造并销售应用范围广泛的高级集成电路、软件设计工具以及定义系统级功能的IP (Intellectual Property)核长期以来一直推动着FPGA技术的发展。

Xilinx的开发工具也在不断升级,集成了FPGA开发需要的所有功能,其主要特点有:①包含了Xilinx新型Smart Compile技术,可以将实现时间缩减2.5倍,能在最短的时间内提供最高的性能,提供了一个功能强大的设计收敛环境;②全面支持最新FPGA系列器件;③集成式的时序收敛环境有助于快速、轻松地识别FPGA设计的瓶颈;④可以节省一个或多个速度等级的成本,并在逻辑设计中实现最低的总成本。

Foundation Series ISE具有界面友好、操作简单的特点,再加上Xilinx的FPGA芯片占有很大的市场,使其成为非常通用的FPGA工具软件。

ISE作为高效的EDA设计工具集合,与第三方软件扬长避短,使软件功能越来越强大,为用户提供了更加丰富的Xilinx平台[19]。

2 Xilinx ISE软件功能简介ISE 的主要功能包括设计输入、综合、仿真、实现和下载,涵盖了FPGA开发的全过程,从功能上讲,其工作流程无需借助任何第三方EDA软件。

设计输入:ISE提供的设计输入工具包括用于HDL代码输入和查看报告的ISE文本编辑器,用于原理图编辑的工具ECS,用于生成IP Core Generator,用于状态机设计的StateCAD以及用于约束文件编辑的Constraint Editor等。

综合:ISE的综合工具不但包含了Xilinx自身提供的综合工具XST,同时还可以内嵌Mentor Graphics公司的LeonardoSpectrum和Synplicity公司的Synplify,实现无缝链接。

proteus软件简介

DS18B20温度传感器:

阻、电容、二极管、 晶体管、 SCRs、 光耦合器、 运放、 555 定时 器等;74 系列TTL 和 4000 系列 CMOS 器件; 存储器:ROM、 RAM、EEPROM、I2C 器件等;微控制器支持的器件如I/O 口、 USART 等;

-

➢ 快捷选取/放置器件:通过模糊搜索可快速从器件

库中选取器件。

-

(3)PROTEUS是单片机课程设计、毕业设 计的创作园地

课程设计、毕业设计是学生走向就业的 重要实践环节。由于PROTEUS提供了实验 室无法相比的大量的元器件库,提供了修改 电路设计的灵活性、提供了实验室在数量、 质量上难以相比的虚拟仪器、仪表,因而也 提供了培养学生实践精神、创造精神的平台 。

-

Proteus

ISIS 原理图设计系统

ARES PCB设计系统

-

1、ISIS(智能原理图输入系统)

ISIS是整个Proteus的中心部分,是一个强 大的原理图绘制系统。

➢ 个性化的编辑环境:用户可自定义图形外观,包括线宽、填充类型、

字符等,也可以使用模板。

➢ 丰富的元器件库:包含超过6000 种器件模型:标准电子元件:电

-

本系统需要用到的元器件

AT89C52

DS18B20

BUZZER(蜂鸣 器)

12864液晶

RESPACK(排阻)PNP(三极管)

BUTTON按键 LED

POT(滑动变阻 器)

-

快速旋转元器件:

如上图所示,当液晶数据端口要与单片机P2口相连时,显 然把液晶旋转90度比较好连,有一种方法是鼠标右键单击 器件可以旋转旋转,快速的方法是设置一个快捷键,菜单 栏System Set Keyboard Map Object Context Command选择自己喜欢的快捷键

ISE软件使用说明(两篇)

引言:概述:ISE软件是由Xilinx公司开发的一款集成电路设计工具,使用该软件可以进行数字电路设计、仿真、验证以及实现等多个阶段的工作。

在设计阶段,ISE软件提供了丰富的组件库和设计工具,方便用户进行电路原理图的绘制和逻辑设计。

在验证阶段,ISE软件可以进行功能仿真和时序仿真,以确保设计的正确性和稳定性。

在实现阶段,ISE软件提供了先进的布局与布线工具,能够将设计转化为实际的电路板。

正文内容:1.安装与启动1.1ISE软件安装包1.2安装ISE软件1.3启动ISE软件2.项目管理2.1创建新项目2.2导入已有项目2.3添加设计文件2.4设定项目属性2.5保存和备份项目3.设计流程3.1电路原理图设计3.1.1组件选择3.1.2连接元件3.1.3设置元件属性3.2逻辑设计3.2.1设计约束3.2.2逻辑优化3.2.3时序约束3.3约束文件编辑3.3.1约束规则3.3.2约束语法3.3.3约束检查3.4时序仿真3.4.1创建仿真波形3.4.2设定初始状态3.4.3运行仿真3.5功能仿真3.5.1设置输入信号3.5.2运行仿真3.5.3分析仿真结果4.仿真与验证4.1时序分析4.1.1设定时钟4.1.2时序路径分析4.1.3时序优化4.2时序约束验证4.2.1满足约束4.2.2修复时序错误4.3灵敏度分析4.3.1设定输入敏感性4.3.2分析敏感性4.4逻辑分析4.4.1切换敏感性4.4.2分析逻辑状态5.布局与布线5.1物理约束5.1.1面积约束5.1.2信号完整性约束5.1.3电源与接地约束5.2布局5.2.1网表导入5.2.2管理物理资源5.2.3进行布局布线5.3时序优化5.3.1满足时序约束5.3.2缩短信号传输路径5.3.3优化时钟分配5.4布线5.4.1管理布线资源5.4.2进行布线5.4.3路由与优化5.5设计规约检查5.5.1检查布局布线规约5.5.2修复设计规约错误总结:引言概述:ISE软件是一款功能强大的集成开发环境工具,广泛应用于数字电路设计和实现。

PROTEUS的简介

PROTEUS 电子设计软件本章在介绍电子设计软件PROTEUS 结构和资源基础上,详细说明了软件的使用和参数的设置。

以典型示例讲述了基于PROTEUS ISIS 的电路设计方法、调试方法和基于PROTEUS ARS 的PCB 板设计方法,以及原理图模型创建和元器件封装的制作方法。

1.1 PROTEUS 电子设计软件1.1.1 PROTEUS 简介Proteus 是英国Labcenter 公司开发的电路分析与仿真软件。

该软件的特点是:①集原理图设计、仿真和PCB 设计于一体,真正实现从概念到产品的完整电子设计工具,②具有模拟电路、数字电路、单片机应用系统、嵌入式系统(不高于ARM7)设计与仿真功能,③具有全速、单步、设置断点等多种形式的调试功能,④具有各种信号源和电路分析所需的虚拟仪表,⑤支持Keil C51 uVision2、MPLAB 等第三方的软件编译和调试环境,⑥具有强大的原理图到PCB 板设计功能,可以输出多种格式的电路设计报表。

拥有PROTEUS 电子设计工具,就相当于拥有了一个电子设计和分析平台。

1.1.2 PROTEUS 组成Proteus 软件自 1989 年问世至今,经历了近20年的发展历史,功能得到了不断的完善,性能越来越好,全球的用户也越来越多。

PROTEUS 之所以在全球得到应用,原因是它具有自身的特点和结构。

PROTEUS 电子设计软件由原理图输入模块(简称ISIS )、混合模型仿真器、动态器件库、高级图形分析模块、处理器仿真模型及PCB 板设计编辑(简称ARES )六部分组成,如图1-1所示。

图1.1 PROTEUS 基本组成1.1.3产品传统设计方法与PROTEUS 设计比较1. 传统产品设计流程传统电子产品开发流程如图1.2所示。

图1.2 传统电子产品开发流程原理图输入ISIS混合模型仿真器动态器件库高级图形分析模块高级图形分析模块处理器仿真模型布线/编辑ARESPROTEUS传统电子产品开发的缺点:●没有物理原型就无法对系统进行测试。

PROTEUS仿真平台介绍-ISIS

输入关键字 原理图器件 预览

器件列表 器件分类目录 PCB封装 预览

4.Proteus元件库简介

搜索关键词 555

型号

类型

特性

元件分类

555

连接器.插头插座库 → 数据转换ADC.DAC → 调试工具库 → ←模拟集成电路库 ←电容库 ←CMOS4000库

个性化的编辑环境 快捷选取/放置器件 层次化设计 可视化设计浏览器 仿真日志 快捷的原理图连线 灵活多样的设计输出

ISIS 的特点

1、个性化的编辑环境:用户可自定义原理图外观, 包括线宽、线型、填充类型、字符等。还可以使用风 格模板。用户可以自己设置快捷键定义。

ISIS 的特点

主菜单

←点击鼠标:

编 辑 工 具

点击此键可取消左键的放置功能,但可编辑对象. ←选择元器件: 在元件表选中器件,在编辑窗中移动鼠标,点击左键放置器件. ←标注联接点: 当两条连线交叉时,放个接点表示连通. ←标志网络线标号:电路联线可用网络标号代替,相同标号的线是相同的. ←放置文本说明: 是对电路的说明,与电路仿真无关! ←放置总线: 当多线并行简化联线,用总线标示. ←放置子电路: 可将部分电路以子电路形式画在另一图纸上. ←放置器件引脚: 有普通.反相.正时钟.反时钟.短引脚.总线 ←放置图纸内部终端: 有普通.输入.输出.双向.电源.接地.总线.

原 理 图 调 试

设 计

预 览

生 成 光 绘 文 件

PCB 3D

PCB

PROTEUS构成

Proteus ISIS中文版软件界面

1. Proteus的主界面简介

LSE:一种处理器体系结构软件仿真器开发工具

LSE:一种处理器体系结构软件仿真器开发工具

喻之斌;金海

【期刊名称】《计算机科学》

【年(卷),期】2008(035)002

【摘要】在现代处理器体系结构设计中,利用软件仿真技术对设计结果进行验证是最重要的方面之一.然而,处理器体系结构仿真器的开发是一个非常困难的过程.主要的困难表现在三个方面:第一,目前用于处理器体系结构仿真器开发的编程语言如C 或C++语言都是串行执行的语言,而处理器的各部件是可以并行运行的,使用串行编程语言编程来模拟并行执行的部件需要长时间的、仔细的程序功能与部件功能的匹配工作,并且容易出错;第二,使用串行程序来模拟并行部件的运行,模拟速度很低,并且仿真速度低是处理器体系结构软件仿真器开发领域的瓶颈问题;最后,仿真器仿真结果的可信度低也是一个关键问题.本文首先介绍了一种新的处理器体系结构软件仿真器开发工具,然后深入分析了该开发工具的优点和缺点,最后对该仿真器开发环境提出了改进方案.

【总页数】4页(P282-285)

【作者】喻之斌;金海

【作者单位】华中科技大学计算机学院,武汉,430074;华中科技大学计算机学院,武汉,430074

【正文语种】中文

【中图分类】TP3

【相关文献】

1.IXP2350网络处理器硬软件体系结构及其软件设计 [J], 饶琛;徐展琦

2.用于Blackfin处理器体系结构的开发工具 [J],

3.虚拟现实系统的体系结构和软件开发工具 [J], 马小虎;潘志庚

4.一种异构多核处理器体系结构的软件仿真 [J], 黄志钢;陶旭东;潘振杰

5.ARM与英蓓特推出中国版RealView微控制器开发工具包加速基于ARM处理器的微控制器软件开发 [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

第十一章 单片机仿真软件-Proteus ISIS 软件介绍(可编辑)

第十一章单片机仿真软件-Proteus ISIS 软件介绍(可编辑)第十一章单片机仿真软件-Proteus ISIS 软件介绍 Proteus ISIS是英国Labcenter公司开发的电路分析与实物仿真软件。

可以仿真、分析 SPICE 各种模拟器件和集成电路,该软件的特点是: 实现了单片机仿真和SPICE电路仿真相结合。

具有模拟电路仿真、数字电路仿真、单片机及其外围电路组成的系统的仿真、RS232动态仿真、I2C调试器、SPI调试器、键盘和LCD系统仿真的功能;有各种虚拟仪器,如示波器、逻辑分析仪、信号发生器等。

支持主流单片机系统的仿真。

目前支持的单片机类型有:68000系列、8051系列、AVR系列、PIC12系列、PIC16系列、PIC18系列、Z80系列、HC11系列以及各种外围芯片。

提供软件调试功能。

在硬件仿真系统中具有全速、单步、设置断点等调试功能,同时可以观察各个变量、寄存器等的当前状态,因此在该软件仿真系统中,也必须具有这些功能;同时支持第三方的软件编译和调试环境,如Keil C51 uVision2等软件。

具有强大的原理图绘制功能。

用Proteus 软件虚拟单片机实验的优点: 1 内容全面实验的内容包括软件部分的汇编、C51 等语言的调试过程,也包括硬件接口电路中的大部分类型。

对同一类功能的接口电路,可以采用不同的硬件来搭建完成,可以扩展学生的思路和提高学生的学习兴趣。

2 硬件投入少,经济优势明显 Protues 所提供的元件库中,大部分可以直接用于接口电路的搭建,同时该软件所提供的仪表,不管在质量还是数量上,都是可靠和经济的。

如果在实验教学中投入这样的真实的仪器仪表,仅仪表的维护来讲,其工作量也是比较大的。

因此采用软件的方式进行教学,其经济优势是比较明显的。

3 学生可自行实验,锻炼解决实际工程问题的能力采用仿真软件后,学习的投入变得比较的小,而实际工程问题的研究,也可以先在软件环境中模拟通过,再进行硬件的投入,这样处理,不仅省时省力,也可以节省因方案不正确所造成的硬件投入的浪费。

Xilinx_ISE使用教程资料

Xilinx公司ISE10.1软件介绍

--脚本(transcript)子窗口

脚本子窗口有5个默认标签:Console,error,warnings , Tcl shell,find in file。 Console标签显示错误、警告和信息。X表示错误,! 表示警告。 Warning标签只显示警告消息。 Error标签只显示错误消息。 Tcl shell标签是与设计人员的交互控制台。除了显示错 误、警告和信息外,还允许输入ISE特定命令。 Find in file标签显示的是选择Edit>Find in File操作后的 查询结果。

Xilinx公司ISE10.1软件设计流程介绍

--打开ISE软件时的面板

当以前使用 过该软件时会默 认打开上一个工 程。

Xilinx公司ISE10.1软件设计流程介绍

--创建一个新工程

Xilinx公司ISE10.1软件设计流程介绍

--创建一个新工程

选择芯片 选择综合工具

选择仿真工具

选择代码语言

Xilinx公司软件平台介绍

--EDK软件

EDK是Xilinx公司推出的FPGA嵌入式开发工具,包 括嵌入式硬件平台开发工具(Platform Studio)、嵌入式 软件开发工具( Platform Studio SDK)、嵌入式IBM PowerPC硬件处理器核、Xilinx MicroBlaze软处理器核、 开发所需的技术文档和IP,为设计嵌入式可编程系统提供 了全面的解决方案。 EDK10.1版还包括了最新的IP内核以优化系统设计。 同时还包括了SPI、DDR2/DMA/PS2和支持SGMII的三模 式以太网MAC等外设,FlexrayTM外设选项,以及用于 DMA的PCI Express驱动支持。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

喻之斌 博士研究生,主要从事多核处理器体系结构、体系结构软件仿真技术研究;金 海 教授,博士生导师,主要从事计算机体系结构、并行分布式处理、集群与网格计算等方面的研究。

计算机科学2008Vol 135№12 LSE :一种处理器体系结构软件仿真器开发工具喻之斌 金 海(华中科技大学计算机学院 武汉430074)摘 要 在现代处理器体系结构设计中,利用软件仿真技术对设计结果进行验证是最重要的方面之一。

然而,处理器体系结构仿真器的开发是一个非常困难的过程。

主要的困难表现在三个方面:第一,目前用于处理器体系结构仿真器开发的编程语言如C 或C ++语言都是串行执行的语言,而处理器的各部件是可以并行运行的,使用串行编程语言编程来模拟并行执行的部件需要长时间的、仔细的程序功能与部件功能的匹配工作,并且容易出错;第二,使用串行程序来模拟并行部件的运行,模拟速度很低,并且仿真速度低是处理器体系结构软件仿真器开发领域的瓶颈问题;最后,仿真器仿真结果的可信度低也是一个关键问题。

本文首先介绍了一种新的处理器体系结构软件仿真器开发工具,然后深入分析了该开发工具的优点和缺点,最后对该仿真器开发环境提出了改进方案。

关键词 处理器,体系结构,仿真技术,L SE LSE :A Development Tool for Computer Architecture SimulatorYU Zhi 2Bin Jin 2Hai(School of Computer Science ,Huazhong University of Science and Technology ,Wuhan 430074)Abstract Software simulation is one of the most important aspects in modern processor architecture design ,which is used to verify design results.However ,it is very difficult to develop a processor architecture simulator.Three factors contribute to this difficulty.Firstly ,the programming languages such as C or C ++used for developing processor ar 2chitecture simulators are sequential while the components of a processor can run concurrently.The procedure mapping the sequential program to concurrently running components is time 2consuming ,difficult and error prone.Secondly ,the simulation speed of simulators which are developed by sequential programming languages is very low and this is the bot 2tle neck in processor architecture simulation stly ,the high error ratio of the results of a simulator is also a key issue.In this paper ,we firstly introduced a new development tool for computer architecture simulators.Then ,the ad 2vantages and disadvantages of this tool are deeply analyzed.In the end ,we come up with a proposal to ameliorate the development tool.K eyw ords Processor ,Architecture ,Simulation technology ,L SE 1 引言随着处理器体系结构复杂程度的不断提高,软件仿真技术在现代处理器体系结构研究和设计中成为越来越重要的一个方面。

在工业界,处理器体系结构设计师们使用软件仿真技术来验证他们的设计;在学术界,研究人员使用软件仿真技术来评估新的思想、算法以及新的体系结构。

通常,一款新的处理器在不使用软件仿真器的情况下,从其开始设计到最后测试成功一般需要耗费4~6年的时间[1]。

使用处理器体系结构软件仿真器,可以极大地缩短设计时间,并大大扩展处理器的设计空间。

因此,在计算机系统结构研究领域,人们十分重视体系结构软件仿真技术的研究和软件仿真器的开发。

从文[2]中可以看出,体系结构软件仿真器的开发已经经历了相当长的一段时间并取得了一定的进展。

然而,现代计算机体系结构变得越来越复杂,特别是多核处理器技术的出现,软件仿真器的开发越来越困难。

一方面,人们对处理器性能和功能要求越来越高,处理器厂商必须更快地制造出更新的、更多不同种类的处理器来满足人们的要求。

另一方面,利用软件仿真器来验证更新、更多不同种类的处理器设计是一项非常费时费力的工作。

更糟糕的是,在现有的技术条件下,不仅软件仿真器本身的开发非常困难,而且已有的软件仿真器存在着多方面的缺陷。

主要表现在以下几个方面:1)软件仿真器的开发周期非常长;2)软件仿真器的仿真速度非常慢;3)仿真结果的错误率较高,不能正确地指导处理器的设计。

本文首先介绍了一种新的处理器体系结构软件仿真器开发方法和软件仿真器开发工具。

然后对该方法和工具的特点、优点和缺点进行了分析,最后对该开发工具的进一步完善提出了建议方案。

2 LSE 介绍L SE 的全称是Liberty Simulation Environment ,它是由普林斯顿大学计算机系开发的一套用于处理器建模或仿真的开发工具。

该开发环境旨在对处理器的并行结构化部件进行建模,然后自动生成处理器仿真器。

在仿真器的开发过程中最大限度地重用已有的组件,从而降低仿真器开发的成本和难度。

利用L SE 的仿真器开发过程如图1[3]所示。

图1 利用L SE 的仿真器生成过程 在图1中,利用L SE 开发处理器体系结构软件仿真器的第一步是使用L SS 语言对拟仿真的处理器结构进行描述。

L SS (Liberty Structural Specification Language )是L SE 中定义的一种硬件描述语言,主要对处理器中的并行结构化部件,如处理器中的算术逻辑部件(AL U )、通用寄存器、状态寄存器、高速缓存及地质转换监视缓冲器(TLB )等进行静态描述[4]。

该描述以3.lss 文件保存,一个lss 文件就是一个某种抽象级别的处理器部件或处理器。

获得了lss 文件以后,需要使用L SE 提供的编译器对其进行解释。

解释的过程中,将调用L SE 组件库中的模块描述库(L SS Module Description )。

L SE 中的模块描述库有两种:一种是L SE 提供的核心模块库[5],另一种是仿真器开发者利用L SE 提供的模块定义机制自己开发的模块库。

经过L SE 编译器解释的L SS 文件只刻画了处理器各部件纯粹意义上的连接,各连接上的约束还没有加上,也还没有对这些约束进行合法性、一致性检查。

特别地,还没对同一连接的两个部件端口上数据类型的一致性进行检查。

因此,下一步就是利用L SE 提供的静态结构分析引擎(Static Analysis Engine )给连接加上约束并检查这些连接和约束的合法性、一致性。

如果lss 文件成功通过了静态结构分析引擎的分析,就得到了具有正确连接约束的处理器部件或处理器模型,并被称为具有连接类型约束的模型。

最后,L SE 代码生成器(Code G enerator )通过调用组件运行时行为库(Component Runtime Behavior )生成可执行的仿真器。

从图1中可以看出,L SE 由三部分组成:(1)Liberty 结构化硬件描述语言L SS ;(2)仿真器生成器;(3)核心模块库和运行时库。

其中L SS 是利用L SE 进行处理器仿真器开发的基础,它不仅是对处理器结构进行描述的工具,而且是仿真器开发人员创建扩展库的工具。

核心模块库提供了用于创建处理器模型的基本元素,如选择器、转换器、路由器等。

L SE 定义了两种类型的模块:一种称为叶子模块,另一种称为组合模块。

叶子模块是一种简单模块,它不能再被拆分为更简单的模块。

在申明叶子模块时,需要指出叶子模块的参数、信息接口以及与该模块对应的行为代码文件的位置。

图2中的代码示例了一个叶子模块的申明。

模块的行为代码就是模块的定义,它用一种类似C 语言的编程语言BSL (Behavior Specifica 2tion Language )来实现。

组合模块是由已经存在的模块组合而成的模块,参与组合的模块既可以是叶子模块,也可以是组合模块。

和叶子模块一样,申明组合模块必须指出其参数、信息接口。

与叶子模块不同的是,它不使用BSL 语言来定义它的行为,而是将内部子模块实例化并将子模块实例连接起来,如图3所示。

3 LSE 的主要特点L SE 是目前最优秀的处理器体系结构开发工具之一。

它的特点主要体现在以下几个方面:(1)提供了并行结构化建模机制;(2)提供了基于模块的重用机制;(3)静态模型分析;(4)L SE 可以作为一个处理器通用仿真器构建框架。

3.1 并行结构化建模通常并行结构化系统是由可并行执行的部件组成的。

每个部件都有一个或多个输入及输出端口,部件之间通过端口互相连接,构成一个网状模型。

运行时,部件间通过在预定义的网状模型上发送与接收数据进行通信。

计算机处理器系统是一个同步数字设备,其状态与一个统一的时钟同步,内部部件可以并行执行,因此,计算机处理器系统是一个典型的并行结构化模型。

L SE 通过核心模块库提供了数字设备所必需的基本元素,如转换器、选择器等。

另外,在L SE 中还可利用L SS 语言根据基本部件元素或已经定义的部件定义更复杂的部件。

因此,L SE 可以直接对处理器系统进行并行结构化建模,并使它们并行执行。

如每个处理器部件对应一个L SE 模块实例。

当然,根据抽象级别的不同,一个L SE 模块实例也可以对应一组处理器部件,但L SE 模块实例依然是可并行执行的。