逻辑综合synthesis(测试版)

组合逻辑电路的功能测试实验

组合逻辑电路的功能测试实验

一、实验目的

掌握组合逻辑电路的设计与测试方法

二、实验原理

1、使用中、小规模集成电路来设计组合电路是最常见的逻辑电

路。

设计

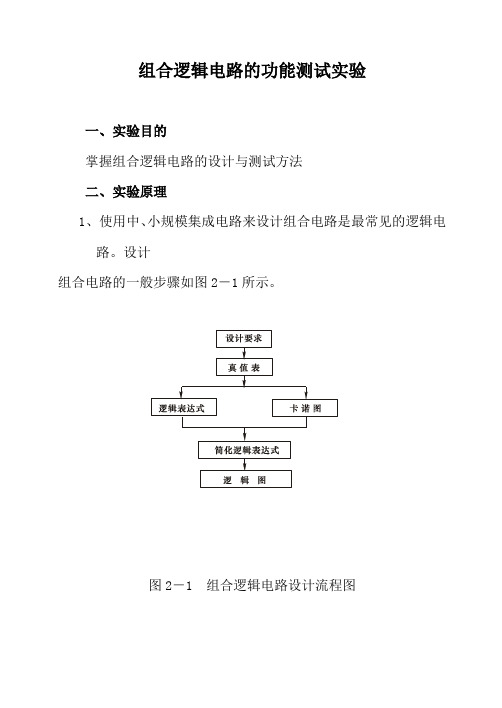

组合电路的一般步骤如图2-1所示。

图2-1 组合逻辑电路设计流程图

根据设计任务的要求建立输入、输出变量,并列出真值表。

然后用逻辑代数或卡诺图化简法求出简化的逻辑表达式。

并按实际选用逻辑门的类型修改逻辑表达式。

根据简化后的逻辑表达式,画出逻辑图,用标准器件构成逻辑电路。

最后,用实验来验证设计的正确性。

2、组合逻辑电路设计举例

用“与非”门设计一个表决电路。

当四个输入端中有三个或四个为“1”时,输出端才为“1”。

由卡诺图得出逻辑表达式,并演化成“与非”的形式

Z=ABC+BCD+ACD+ABD

根据逻辑表达式画出用“与非门”构成的逻辑电路如图2-2所示。

图2-2 表决电路逻辑图

三、实验设备与器件

1、数字电路试验箱

2、74LS00 74LS20 CC4030(74LS86)

四、实验内容

1、验证表决电路的逻辑功能,画出其真值表。

2、设计用与非门及用异或门组成的半加器电路。

3、设计一个一位全加器,要求用异或门及与非门组成。

五、实验报告

1、列写实验任务的设计过程,画出设计的电路图。

2、对所设计的电路进行实验测试,记录测试结果。

逻辑门电路与组合逻辑电路功能测试(共70页)

实验(shíyàn)一逻辑(luó jí)门电路与组合(zǔhé)逻辑电路功能测试一、实验(shíyàn)目的1.熟悉(shúxī)电子实验箱的功能及使用方法。

2.学习集成电路型号及引脚排列识别,使用电子实验箱完成逻辑门电路逻辑功能测试。

3.复习利用摩根定律实现五种逻辑函数表达式的转换。

4.学习如何写简单逻辑电路图的逻辑关系表达式及最简式。

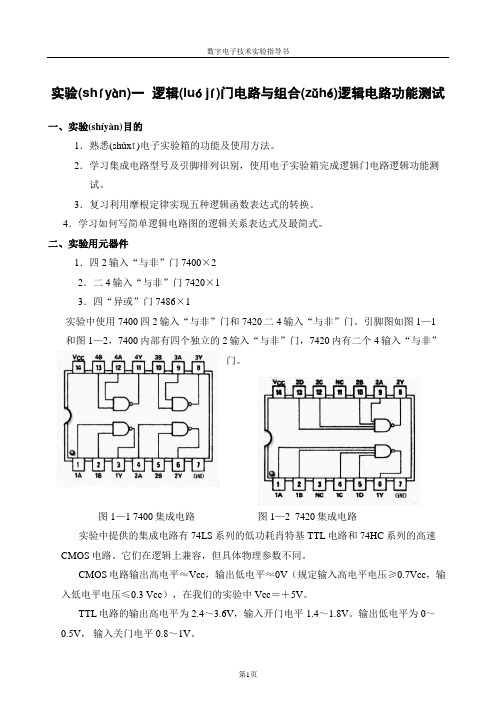

二、实验用元器件1.四2输入“与非”门7400×22.二4输入“与非”门7420×13.四“异或”门7486×1实验中使用7400四2输入“与非”门和7420二4输入“与非”门。

引脚图如图1—1和图1—2,7400内部有四个独立的2输入“与非”门,7420内有二个4输入“与非”门。

图1—1 7400集成电路图1—2 7420集成电路实验中提供的集成电路有74LS系列的低功耗肖特基TTL电路和74HC系列的高速CMOS电路。

它们在逻辑上兼容,但具体物理参数不同。

CMOS电路输出高电平≈Vcc,输出低电平≈0V(规定输入高电平电压≥0.7Vcc,输入低电平电压≤0.3 Vcc),在我们的实验中Vcc=+5V。

TTL电路的输出高电平为2.4~3.6V,输入开门电平1.4~1.8V。

输出低电平为0~0.5V,输入关门电平0.8~1V。

在实验(shíyàn)中采用同一电源,经实际测定可以直接联接,但有些条件下须要(xūyào)通过接口转接,用74LS门电路驱动(qū dònɡ)74HC门电路时,输出(shūchū)高电平电压应大于3.5V。

而74HC门电路驱动(qū dònɡ)74LS门电路时要加下拉电阻,扇出系数应小于10。

三、实验前准备工作及注意事项1.检查实验用具是否齐全:电源一个、电子实验箱一个、万用表一个(表笔两只)、实验线若干。

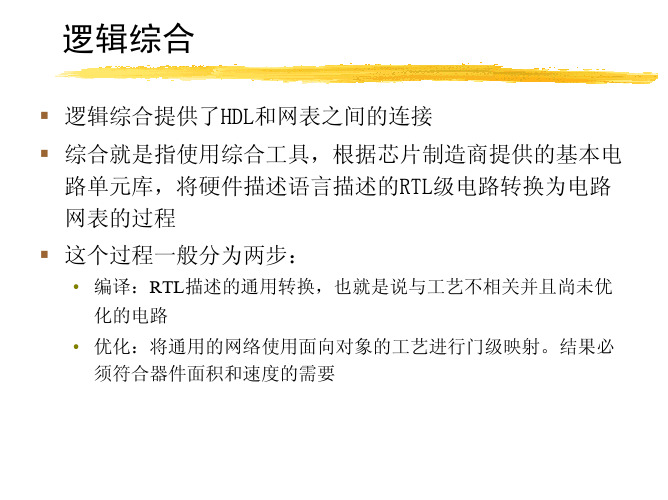

逻辑综合

逻辑综合

可逻辑综合的VHDL代码示例

• 异步复位D触发器

DFFA: PROCESS(clk, reset) BEGEN IF (reset = ‘0’) THEN data_out <= (OTHERS => ‘0’); ELSIF (clk’EVENT AND clk = ‘1’) THEN data_out <= data_in; END IF; END PROCESS DFFA;

3

4

5

6

7

8

逻辑综合

• 优化策略

数字电路的设计原则上是分 层次的。最高层(Top-Level) 通常是由互相联系的块组成 右图显示了从VHDL语言到目 标网表的步骤 优化策略包含两项:

• 平面化 • 结构化

technology: mapping netlist in target technology gate level: netlist logical level: boolean equations VHDL description flattening structuring

data_out <= (OTHERS => ‘0’); ELSIF (clk ‘EVENT AND clk = ‘1’) THEN data_out <= in1 XOR in2; END IF; END PROCESS SYNC;

逻辑综合

可逻辑综合的VHDL代码示例

• 带反馈回路的触发器

PROCESS (clk) BEGIN IF (clk ‘EVENT AND clk = ‘1’) THEN IF (ena = ‘1’) THEN data_out <= a; END IF; END IF; END PROCESS;

综合 Synthesis

综合步骤

综合步骤1:源文件准备

源文件的准备主要是检查 rtl的书写规范,时钟域划分是否 合理,一般有专业的工具进行检查

综合 Synthesis

刘海林

基本概述

概念:行为描述的电路、RTL级的电路 门级网表

综合的不同层次:逻辑级、RTL级、行为级

目的:决定电路门级结构、寻求时序和与面积的平衡、寻 求功耗与时序的平衡、增强电路的测试性

综合工具:Design Com程:Translation 、map 、optimization Translation是指把设计的HDL描述转化为GTECH库元件组 成的逻辑电路 Mapping 是指将 GTECH 库元件映射到某一特定的半导体 工艺库上,此时的电路网表包含了相关的工艺参数 Optimization是根据设计者设定的时延、面积、线负载模 型等综合约束条件对电路网表进一步优化的过程

实验三组合逻辑电路的功能测试

实验三组合逻辑电路的功能测试基本逻辑门测试:1.与门测试:在输入端口分别接入两个输入信号A、B,并将输出端口接入示波器。

通过输入不同的逻辑电平(0或1),观察输出信号。

当输入信号都为1时,输出信号应为1;其他情况下,输出信号应为0。

2.或门测试:与与门测试类似,在输入端口分别接入两个输入信号A、B,并将输出端口接入示波器。

通过输入不同的逻辑电平(0或1),观察输出信号。

当输入信号都为0时,输出信号应为0;其他情况下,输出信号应为13.非门测试:在输入端口接入输入信号A,并将输出端口接入示波器。

通过输入不同的逻辑电平(0或1),观察输出信号。

当输入信号为0时,输出信号应为1;当输入信号为1时,输出信号应为0。

4.异或门测试:在输入端口分别接入两个输入信号A、B,并将输出端口接入示波器。

通过输入不同的逻辑电平(0或1),观察输出信号。

当输入信号相同(均为0或均为1)时,输出信号应为0;当输入信号不同(一个为0,一个为1)时,输出信号应为1组合逻辑电路测试:1.与门与非门的组合测试:在输入端口分别接入两个输入信号A、B,并将输出端口接入示波器。

通过输入不同的逻辑电平(0或1),观察输出信号。

当输入信号都为1时,输出信号应为0;其他情况下,输出信号应为12.或门与非门的组合测试:与与门与非门的组合测试类似,只需将与门替换为或门,测试结果应与与门与非门的组合测试相反。

3.封装后的组合逻辑电路测试:使用封装后的组合逻辑电路实现具体的逻辑功能,如加法器、选择器等。

通过输入不同的逻辑电平(0或1),观察输出信号,验证实现的逻辑功能是否正确。

在进行功能测试时,需要注意输入信号的切换时间、输出信号的稳定时间,确保电路能够正常工作。

此外,还可以通过逻辑表或真值表对测试结果进行验证,确保组合逻辑电路的正确性。

总结:实验三组合逻辑电路的功能测试是通过对基本逻辑门和组合逻辑电路进行输入输出信号的观察和测试,验证其功能正确性。

逻辑综合中的基本概念

1. 逻辑综合 (Logic Synthesis)EDA工具把数字电路的功能描述(或结构描述)转化为电路的结构描述。

实现上述转换的同时要满足用户给定的约束条件,即速度、功耗、成本等方面的要求。

2. 逻辑电路(Logic Circuit)逻辑电路又称数字电路,在没有特别说明的情况下指的是二值逻辑电路。

其电平在某个阈值之上时看作高电平,在该阈值之下时看作低电平。

通常把高电平看作逻辑值1;把低电平看作逻辑值0。

3. 约束(restriction)设计者给EDA工具提出的附加条件,对逻辑综合而言,约束条件一般包括速度、功耗、成本等方面的要求。

4. 真值表(Truth Table)布尔函数的表格描述形式,描述输入变量每一种组合情况下函数的取值。

输入变量组合以最小项形式表示,函数的取值为真或假(1 或0)。

5. 卡诺图(Karnaugh Map)布尔函数的图形描述形式,图中最小方格和最小项对应,两个相邻的最小方格所对应的最小项只有一个变量的取值不同。

卡诺图适合于用观察法化简布尔函数,但是当变量的个数大于4时,卡诺图的绘制和观察都变得很困难。

6. 单输出函数(Single-output Function)一个布尔函数的单独描述。

7. 多输出函数(Multiple-output Function)输入变量相同的多个布尔函数的统一描述。

8. 最小项(Minterm)设a1,a2,…ai,…an是n个布尔变量,p为n个因子的乘积。

如果在p中每一变量都以原变量ai或反变量的形式作为因子出现一次且仅出现一次,则称p为n 个变量的一个最小项。

最小项在卡诺图中对应于最小的方格;在立方体表示中对应于顶点。

9. 蕴涵项(Implicant)布尔函数f的"与-或"表达式中的每一乘积项都叫作f的蕴涵项。

例如:f=+中的乘积项和都是函数f的蕴涵项。

蕴涵项对应于立方体表示法中的立方体。

10.质蕴涵项(Prime Implicant,PI)设函数f有多个蕴涵项,若某个蕴涵项i所包含的最小项集合不是任何别的蕴涵项所包含的最小项集合的子集的话,则称i为函数f的质蕴涵项。

第5章 逻辑综合

第5章逻辑综合5.1 逻辑综合(Synthesis)的概念逻辑综合是指将硬件描述语言描述的RTL级的代码转换为由芯片制造商(Foundry)提供的基本单元电路实现的门级网表的过程。

逻辑综合是由综合工具完成的,但设计者必须提供对芯片的时序、面积、功耗等方面的约束。

综合过程可以分为三个步骤:(1)翻译(Translation)将硬件描述语言翻译为符合综合工具内部规定的逻辑方程,不做任何逻辑优化,与具体工艺无关。

(2)优化(Optimization)根据时序和面积约束,对逻辑方程进行重组和优化。

(3)映射(Mapping)根据时序和面积约束,从目标工艺库(Target Technology)中搜索适当的单元来实现实际电路。

芯片制造商(Foundry)提供的工艺库中,有各种基本单元,如各种逻辑门、触发器、数据选择器等。

在工艺库中,对这些基本单元电路的特性有完整的描述,如面积、输入端电容、输出端的驱动能力等等。

综合的目标就是用工艺库中的这些单元实现RTL代码描述的逻辑功能,并满足设计者提出的面积和时序要求。

逻辑综合将生成门级网表文件、标准延迟文件(SDF)和各种报告。

面向ASIC的主流综合工具是Synopsys公司的Design Compiler。

本章主要介绍用基于的Design Compiler逻辑综合方法。

5.2 Design Compiler 简介5.2.1 Linux Red Hat 7.2 基本操作Design Compiler有Unix和Linux两种平台下的版本,Linux下的版本必须使用Linux Red Hat 7.2操作系统。

软件安装参见本章附录。

以下介绍Linux文件系统的基本思想和基本操作命令。

●基本思想初学Linux要适应文件系统基本思想,Linux将整个计算机中的各种软件、硬件都理解为文件,以统一的文件系统方式组织。

其中/ 为最上层的根目录,其它都是根目录下的子目录。

Linux的文件路径分为绝对路径和相对路径。

逻辑综合

13

设计读入

读入设计有多种方法,DC支持读入Verilog,VHDL,可以是RTL级代码,也 可以是门级网表,也可是ddc格式的文件。综合前的设计不需用RTL格式(虽 然也有其它格式)输入到DC中。 可以用以下命令读入设计: 1.analyze和elaborate命令:这是两个不同的命令,它使得设计人员可以在 建立设计通用逻辑之前先对设计进行语法错误和RTL转换分析。 2.read_file命令:如: read_file –format verilog sd_clk.v 3.read_verilog或read_vhdl命令,这些是从read_file中分离出来的命令, 如: read_verilog sd_clk.v 读入代码后用命令current_design和link将读入的设计和综合库连接起来。

2

3

综合过程中时序与面积的关系 从下图中可以看出面积与延迟的折衷关系,综合工具以约束为指导,在满足时 序的情况下获得最小面积。如果不施加约束,综合工具会产生非优化的网表, 而这是不能满足要求的网表。所以约束对于综合来说是必不可少的。

4

综合的基本流程 1.准备RTL代码:RTL代码经过前端仿真后才能用于综合。 2.定义库:设定好所需要用到的综合库等多种库。 3.读入设计:综合工具读入RTL代码并进行分析。 4.定义设计环境:设定设计的工作环境、端口的驱动和负载,线负载模型等 5.设置设计约束:这是综合的一个极其重要的环节,设定好正确的约束才能 得到正确的综合结果。约束要适当,不能过紧或过松。主要是定义时钟和I/O 的约束。 6.设置综合策略:有top-down和bottom-up两种策略,各有所长,对于不同的 设计要具体分析。 7.优化设计:综合工具可以根据约束对电路进行优化,也可以人为地加入命 令,改变优化方法。 8.分析和解决设计的问题:在设计综合(compile)后,根据报告来分析设计 中出现的问题,进而修订所出现的问题。 9.保存设计数据:综合完成后,保存各种数据,以供后续的布局布线使用( 需先通过验证)。 5

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

综合复习资料(综合测试版)一、名词解释1、Synthesis:synthesis is the transformation of an idea into a manufacturable device to carry out an intended function.2、SOLD(Synopsys On-Line Documentation): It is a website to provide answers.3、STA(Static Timing Analysis): A method for determining of a circuit meets timing constraints without having to simulate clock cycles.4、Clock skew:To account for varying delays between the clock network branches.5、Jitter:Because some uncertain factors,which leads to the clock happen drift.6、RTL(Register Transfer Level):It is a coding style means describing the register architecture, the circuit topology, and the functionality between registers.7、TCL(Tool Command Language): It is an “open”, industry-standard language, developed at UCA Berkeley.8、PVT: STA scales each cell and net delay based on Process, Voltage, and Temperature variations.9、CTS(Clock Tree Synthesis):Buffer clock timing device in the right place, and avoid the CLOCK to SKEW.10、BDD(Binary Decision Diagram):The binary decision diagram is used to represent the data structure of the Boolean functions.二、填空1、Design objects: Design、Cell、Reference、Port、Pin、Net、Clock2、The advantages of synthesis: reusability、verifiable、portability、prestige、productivity、abstraction、design tricks3、Synthesis is Constraint-Driven, is Path-Based.4、Synthesis=translation + optimization + mapping5、GTECH has nothing to do with technology.三、简答1、Cell-BaBehavioral Level答:1.Behavioral level 2.RTL Level 3.Logic Synthesis 4.Logic Level Design 5.Circuit Level Design yout Level Design 7.Post Verificationsed-Flow2、Logic Synthesis Overview答:1.RTL Design 2.HDLCompiler3.DesignCompiler4.OptimizedGate-level Netlist3、What .synopsys_dc.setup defined答:link_librarytarget_librarysymbol_librarysearch_pathsynthetic_library4、what is .synopsys_dc.setup?答:启动文件(startup files)DC : .synopsys_dc.setupDefined process path to the library and the other for the logic synthesis parameters.定义工艺库的路径和其他用于逻辑综合的参数。

Three distinct files are read and executed when DCis invoked1st. system-wide (do not modify):(e.g. $SYNOPSYS/admin/setup/)2nd. User’s home directory (e.g. ~ccyang/)3rd. User’s current working directory (e.g. ~ccyang/dc/)5、Static Timing Analysis (Design Time)答:A method for determining if a circuit meets timingconstraints without having to simulate clock cycles.1.Designs are broken down into sets of timing paths2.The delay of each path is calculated3.All path delays are checked to see if timing constraintshave been met6、Timing GroupsHow to organize timing paths into group?答:7、Timing Path Exercise答:How many timing paths do you see? 11How many path groups are there? 38、HDL Coding Style for Synthesis答:1.Synthesizable Verilog HDL2.Some tricks in Verilog HDL3.Designware library9、Design Constraints Setting答:1.Setting Design Environment2.Setting Design Constraint10、operating environment答:The operating environment affects the components selected from target library and timing through your design.11、Operating Condition/Input Drive Impedance12、Wire Load Model答:1.Wire load model estimates wire capaon chip area & cell fanout.2.Setting this information during compmodel the design more accurately .13、Sequential Circuit - Specify Clock答:1.Select clock port2.Attributes/Clocks/Specifycreate_clock : define your clock’s waveform &respect the set-up time requirements of all clockedflip-flopsdc_shell>create_clock “clk” -period 50 -waveform {0 25}set_fix_hold : respect the hold time requirementof all clocked flip-flopsdc_shell>set_fix_holdclkset_dont_touch_network : do not re-buffer theclock networkdc_shell>set_dont_touch_networkclk14、group FSM答:To group FSM, use the following dc_shellcommanddc_shell>set_fsm_state_vector {present_State[2],present_State[1], present_State[0]}dc_shell>group -fsm -design_namefsm_name15、What is Setup Time and Hold Time?答:Setup Time: The length of time that data must stabilize before the clock transition. The maximum data path is used to determine if setup constraint is met. Hold Time: The length of time that data must remain stable at the input pin after the active clock transition. The minimum data path is used to determine if hold time is met.16、What is the name of library and what are the functions of library?答:1.Link_library: the library used for interpreting input description.2.Target_library: the ASIC technology that the design is mapped to.3.Symbol_library: used during schematic generation.4.Synthetic_library: designware library to be used.17、Why partition a design?答:Partitioning is driven by many (often competing) needs:1.Separate distinct functions.2.Achieve workable size and complexity.3.Manage project in team environment.4.Design reuse.5.Meet physical constraints.18、How to Partitioning?19、How to constraint ?答:set_max_area 100create_clock–period 10 [get_portsclk]set_dont_touch_network [get_clocksclk]set_input_delay–max 4 –clock clk [get_ports A]set_output_delay–max 5.4 –clock clk [get_port B]20、Timing path答:Design Time breaks designs into sets of signal paths, each path has a startpoint and an endpoint.Startpoints: input ports clock pins of sequential devicesEndpoints: output ports data inputs pins of sequential device21、Set_driving_cell and Set_load答:Set_driving_cell allows the user to specify a realistic external cell driving the input ports.syntax:set_driving_cell–lib_cell and2a0 \ [get_ports IN1]Set_load allows the user to specify the external capacitive load on ports.syntax: set_load 5 [get_ports OUT1]22、Time BudgetingBudget:40% of clock period23、What are virtual clocks?答:Clocks in the environment of the design to be synthesized that:Are defined clock objects within Design Compiler’s memoryDo not clock any sequential devices within the current_designServe as references for input or output delays24、How do I create a virtual clock?答:It is the same as defining a clock, but do not specify a clock pin or port Example: create_clock–name vTEMP_CLK–period 2025、Why to use virtual clocks?Timing Goals for Multiple Clock DesignsMethod is the same as that for single clock designs:1. Define the clock(s), using virtual clocks if necessary2. Specify I/O delays relative to the clock(s)26、Optimization can occur at each of three levels: Architectural、Logic-Level、Gate-Level27、RTL Block Synthesis28、The method to describe a circuit:BDD(二叉决判决图)、HDL(硬件描述语言)、Schematic(电路图)、Netlist(网表)、Boolean expression(布尔表达式)、Gate-level Schematic(门级电路图)、Layout(版图)、Transistor-level schematic(晶体管级电路图)、PCB(PrintedCircuitBoard,印制电路板)29、自己画综合结果答:1.有关阻塞与非阻塞的一个Verilog程序综合2.异步复位与同步复位30、写一段Verilog程序SR锁存器moduleSR_latch(Q,Qbar,Sbar,Rbar); outputQ,Qbar;inputSbar,Rbar;nand n1(Q,Sbar,Qbar);nand n2(Q,Rbar,Q);endmoduleD触发器module DFF(CLK,RST,DFF_DI,DFF_DO); inputCLK,RST,DFF_DI;output DFF_DO;reg DFF_DO;always @ (posedgeCLK or negedge RST) beginif(!RST)DFF_DO<= 0;elseDFF_DO<= DFF_DI;endendmoduleT触发器module TFF( C LK,RST,TFF_DI,TFF_DO);inputCLK,RST,TFF_DI;outputTFF_DO;reg TFF_DO;always @ (posedge CLK or negedge RST)beginif(!RST)TFF_DO <= 0;elseTFF_DO <= TFF_DO_N;endassign TFF_DO_N = (TFF_DI) ? (~TFF_DO) : (TFF_DO); endmodule3-8译码器module DECODE_3_8(CODE, DATA);input [2:0] CODE;output [7:0] DATA;reg [7:0] DATA;always @ (*)begincase(CODE)3'h0 : DATA = 8'b0000_0001;3'h1 : DATA = 8'b0000_0010;3'h2 : DATA = 8'b0000_0100;3'h3 : DATA = 8'b0000_1000;3'h4 : DATA = 8'b0001_0000;3'h5 : DATA = 8'b0010_0000;3'h6 : DATA = 8'b0100_0000;3'h7 : DATA = 8'b1000_0000;default : DATA = 8'bz;endcaseendendmodule加法器module adder(din1,din2,clk,ci,rst_n,dout,co);input din1,din2,inputclk,input ci,inputrst_n,outputregdout,outputreg coalways @ (posedgeclk or negedgerst_n)beginif(!rst_n) {co,dout}<=2'b0;else {co,dout}<=din1+din2+ci;endendmodule由于时间仓促,答案可能存在纰缪之处,如经发现请与作者联系7.3日小开献上。